Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                            |

| Number of I/O              | 15                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                      |

| Data Converters            | A/D 15x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-VFQFN Exposed Pad                                             |

| Supplier Device Package    | -                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f851-c-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F85x-86x

| 8.2.1. Internal RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 8.2.2. External RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| 8.2.3. Special Function Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 9. Special Function Register Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 56                                                                                                                             |

| 10. Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 61                                                                                                                             |

| 10.1. Security Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

| 10.2. Programming the Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 63                                                                                                                             |

| 10.2.1. Flash Lock and Key Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 63                                                                                                                             |

| 10.2.2. Flash Erase Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 63                                                                                                                             |

| 10.2.3. Flash Write Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63                                                                                                                               |

| 10.3. Non-Volatile Data Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 64                                                                                                                             |

| 10.4. Flash Write and Erase Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 64                                                                                                                             |

| 10.4.1. Voltage Supply Maintenance and the Supply Monitor                                                                                                                                                                                                                                                                                                                                                                                                                             | . 64                                                                                                                             |

| 10.4.2. PSWE Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| 10.4.3. System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 65                                                                                                                             |

| 10.5. Flash Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 66                                                                                                                             |

| 11. Device Identification and Unique Identifier                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| 11.1. Device Identification Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 69                                                                                                                             |

| 12. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 72                                                                                                                             |

| 12.1. MCU Interrupt Sources and Vectors                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 72                                                                                                                             |

| 12.1.1. Interrupt Priorities                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

| 12.1.2. Interrupt Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 72                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| 12.2. Interrupt Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 75                                                                                                                             |

| 12.2. Interrupt Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| <ul> <li>12.2. Interrupt Control Registers</li> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                             | . 82                                                                                                                             |

| 13. Power Management and Internal Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>82</b><br>82                                                                                                                  |

| <b>13. Power Management and Internal Regulator</b> 13.1. Power Modes.                                                                                                                                                                                                                                                                                                                                                                                                                 | 82<br>82<br>82                                                                                                                   |

| <b>13. Power Management and Internal Regulator</b><br>13.1. Power Modes<br>13.1.1. Idle Mode<br>13.1.2. Stop Mode                                                                                                                                                                                                                                                                                                                                                                     | 82<br>82<br>82<br>82<br>83                                                                                                       |

| <b>13. Power Management and Internal Regulator</b> 13.1. Power Modes.         13.1.1. Idle Mode                                                                                                                                                                                                                                                                                                                                                                                       | <b>82</b><br>82<br>82<br>83<br>83<br>83                                                                                          |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>82</b><br>82<br>82<br>83<br>83<br>83<br>83                                                                                    |

| <ul> <li>13. Power Management and Internal Regulator</li> <li>13.1. Power Modes</li> <li>13.1.1. Idle Mode</li> <li>13.1.2. Stop Mode</li> <li>13.2. LDO Regulator</li> <li>13.3. Power Control Registers</li> <li>13.4. LDO Control Registers</li> </ul>                                                                                                                                                                                                                             | . 82<br>. 82<br>. 82<br>. 83<br>. 83<br>. 83<br>. 83                                                                             |

| <ul> <li>13. Power Management and Internal Regulator</li> <li>13.1. Power Modes</li> <li>13.1.1. Idle Mode</li> <li>13.1.2. Stop Mode</li> <li>13.2. LDO Regulator</li> <li>13.3. Power Control Registers</li> </ul>                                                                                                                                                                                                                                                                  | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>84<br>85                                                                         |

| <ul> <li>13. Power Management and Internal Regulator</li> <li>13.1. Power Modes</li> <li>13.1.1. Idle Mode</li> <li>13.1.2. Stop Mode</li> <li>13.2. LDO Regulator</li> <li>13.3. Power Control Registers</li> <li>13.4. LDO Control Registers</li> <li>13.4. LDO Control Registers</li> <li>14.1. ADC0 Analog Multiplexer</li> </ul>                                                                                                                                                 | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>84<br>84<br>85<br>86                                                             |

| <ul> <li>13. Power Management and Internal Regulator</li> <li>13.1. Power Modes</li> <li>13.1.1. Idle Mode</li> <li>13.1.2. Stop Mode</li> <li>13.2. LDO Regulator</li> <li>13.3. Power Control Registers</li> <li>13.4. LDO Control Registers</li> <li>13.4. LDO Control Registers</li> <li>14.1. ADC0 Analog Multiplexer</li> <li>14.2. ADC Operation</li> </ul>                                                                                                                    | <b>82</b><br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>85<br>86<br>88                                    |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>82</b><br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>84<br>85<br>88<br>88<br>88<br>88                              |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>88<br>88<br>88<br>88                                           |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>85<br>86<br>88<br>88<br>88<br>88<br>88<br>88<br>88                   |

| <ul> <li>13. Power Management and Internal Regulator</li> <li>13.1. Power Modes</li> <li>13.1.1. Idle Mode</li> <li>13.1.2. Stop Mode</li> <li>13.2. LDO Regulator</li> <li>13.3. Power Control Registers</li> <li>13.4. LDO Control Registers</li> <li>13.4. LDO Control Registers</li> <li>14.1. ADC0 Analog Multiplexer</li> <li>14.2. ADC Operation</li> <li>14.2.1. Starting a Conversion</li> <li>14.2.2. Tracking Modes</li> <li>14.2.4. Settling Time Requirements</li> </ul> | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>84<br>85<br>88<br>88<br>88<br>88<br>88<br>88<br>88<br>90                   |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>88<br>88<br>88<br>88                                           |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>88<br>88<br>88<br>88                                           |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>84<br>88<br>88<br>88<br>88<br>88<br>88<br>88<br>90<br>91<br>91<br>91 |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>88<br>88<br>88<br>88                                           |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>88<br>88<br>88<br>88                                           |

| <ul> <li>13. Power Management and Internal Regulator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | 82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>88<br>88<br>88                                           |

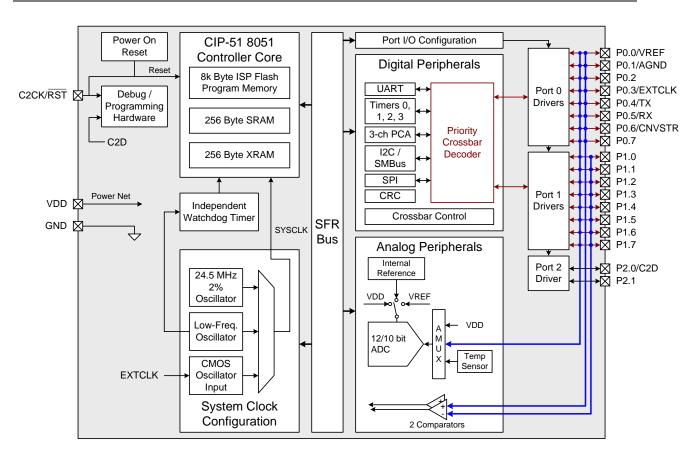

Figure 2.1. C8051F85x/86x Family Block Diagram (QSOP-24 Shown)

| Pin Name      | Туре                            | Pin Numbers | Crossbar Capability | Additional Digital Functions | Analog Functions            |

|---------------|---------------------------------|-------------|---------------------|------------------------------|-----------------------------|

| P1.1          | Standard I/O                    | 10          | Yes                 | P1MAT.1                      | ADC0.9<br>CP1P.3<br>CP1N.3  |

| P1.2          | Standard I/O                    | 9           | Yes                 | P1MAT.2                      | ADC0.10<br>CP1P.4<br>CP1N.4 |

| P1.3          | Standard I/O                    | 8           | Yes                 | P1MAT.3                      | ADC0.11<br>CP1P.5<br>CP1N.5 |

| P2.0 /<br>C2D | Standard I/O /<br>C2 Debug Data | 7           |                     |                              |                             |

#### Table 3.3. Pin Definitions for C8051F860/1/2/3/4/5-GS and C8051F860/1/2/3/4/5-IS

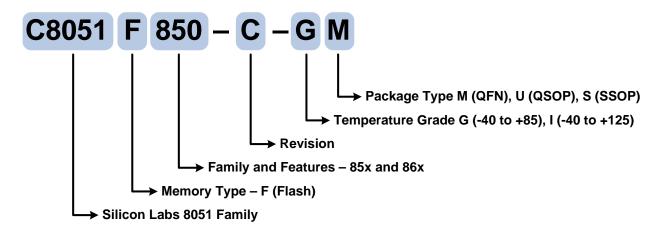

# 4. Ordering Information

#### Figure 4.1. C8051F85x/86x Part Numbering

All C8051F85x/86x family members have the following features:

- CIP-51 Core running up to 25 MHz

- Two Internal Oscillators (24.5 MHz and 80 kHz)

- I2C/SMBus

- SPI

- UART

- 3-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- 4 16-bit Timers

- 2 Analog Comparators

- 16-bit CRC Unit

In addition to these features, each part number in the C8051F85x/86x family has a set of features that vary across the product line. The product selection guide in Table 4.1 shows the features available on each family member.

All devices in Table 4.1 are also available in an industrial version. For the industrial version, the -G in the ordering part number is replaced with -I. For example, the industrial version of the C8051F850-C-GM is the C8051F850-C-IM.

# C8051F85x/86x

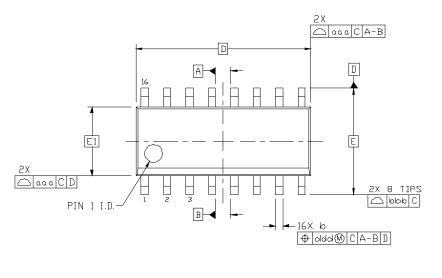

# 7. SOIC-16 Package Specifications

GAUGE PLANE

[[2]

Figure 7.1. SOIC-16 Package Drawing

|           |          |          |      |   | -         |          |      |      |

|-----------|----------|----------|------|---|-----------|----------|------|------|

| Dimension | Min      | Nom      | Max  | ] | Dimension | Min      | Nom  | Max  |

| А         | —        |          | 1.75 |   | L         | 0.40     |      | 1.27 |

| A1        | 0.10     |          | 0.25 |   | L2        | 0.25 BSC |      |      |

| A2        | 1.25     |          |      |   | h         | 0.25     |      | 0.50 |

| b         | 0.31     |          | 0.51 |   | θ         | 0°       |      | 8º   |

| С         | 0.17     |          | 0.25 |   | aaa       | 0.10     |      |      |

| D         |          | 9.90 BSC |      |   | bbb       |          | 0.20 |      |

| Е         | 6.00 BSC |          |      |   | CCC       | 0.10     |      |      |

| E1        | 3.90 BSC |          |      |   | ddd       |          | 0.25 |      |

| е         |          | 1.27 BSC |      |   |           |          |      |      |

#### Table 7.1. SOIC-16 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MS-012, Variation AC.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| Register | Address | Register Description     | Page |

|----------|---------|--------------------------|------|

| SPIODAT  | 0xA3    | SPI0 Data                | 232  |

| TCON     | 0x88    | Timer 0/1 Control        | 271  |

| TH0      | 0x8C    | Timer 0 High Byte        | 275  |

| TH1      | 0x8D    | Timer 1 High Byte        | 276  |

| TL0      | 0x8A    | Timer 0 Low Byte         | 273  |

| TL1      | 0x8B    | Timer 1 Low Byte         | 274  |

| TMOD     | 0x89    | Timer 0/1 Mode           | 272  |

| TMR2CN   | 0xC8    | Timer 2 Control          | 277  |

| TMR2H    | 0xCD    | Timer 2 High Byte        | 282  |

| TMR2L    | 0xCC    | Timer 2 Low Byte         | 281  |

| TMR2RLH  | 0xCB    | Timer 2 Reload High Byte | 280  |

| TMR2RLL  | 0xCA    | Timer 2 Reload Low Byte  | 279  |

| TMR3CN   | 0x91    | Timer 3 Control          | 283  |

| TMR3H    | 0x95    | Timer 3 High Byte        | 288  |

| TMR3L    | 0x94    | Timer 3 Low Byte         | 287  |

| TMR3RLH  | 0x93    | Timer 3 Reload High Byte | 286  |

| TMR3RLL  | 0x92    | Timer 3 Reload Low Byte  | 285  |

| VDM0CN   | 0xFF    | Supply Monitor Control   | 216  |

| WDTCN    | 0x97    | Watchdog Timer Control   | 300  |

| XBR0     | 0xE1    | Port I/O Crossbar 0      | 193  |

| XBR1     | 0xE2    | Port I/O Crossbar 1      | 194  |

| XBR2     | 0xE3    | Port I/O Crossbar 2      | 195  |

## Register 14.13. ADC0MX: ADC0 Multiplexer Selection

| Bit   | 7 | 6        | 5 | 4      | 3 | 2 | 1 | 0 |  |

|-------|---|----------|---|--------|---|---|---|---|--|

| Name  |   | Reserved |   | ADC0MX |   |   |   |   |  |

| Туре  | R |          |   | R RW   |   |   |   |   |  |

| Reset | 0 | 0        | 0 | 1      | 1 | 1 | 1 | 1 |  |

## Table 14.16. ADC0MX Register Bit Descriptions

| Bit | Name     | Function                                                                                |

|-----|----------|-----------------------------------------------------------------------------------------|

| 7:5 | Reserved | Must write reset value.                                                                 |

| 4:0 | ADC0MX   | AMUX0 Positive Input Selection.                                                         |

|     |          | Selects the positive input channel for ADC0. For reserved bit combinations, no input is |

|     |          | selected.                                                                               |

|     |          | 00000: ADC0.0                                                                           |

|     |          | 00001: ADC0.1                                                                           |

|     |          | 00010: ADC0.2                                                                           |

|     |          | 00011: ADC0.3                                                                           |

|     |          | 00100: ADC0.4                                                                           |

|     |          | 00101: ADC0.5                                                                           |

|     |          | 00110: ADC0.6                                                                           |

|     |          | 00111: ADC0.7                                                                           |

|     |          | 01000: ADC0.8                                                                           |

|     |          | 01001: ADC0.9                                                                           |

|     |          | 01010: ADC0.10                                                                          |

|     |          | 01011: ADC0.11                                                                          |

|     |          | 01100: ADC0.12                                                                          |

|     |          | 01101: ADC0.13                                                                          |

|     |          | 01110: ADC0.14                                                                          |

|     |          | 01111: ADC0.15                                                                          |

|     |          | 10000: Temperature sensor.                                                              |

|     |          | 10001: Internal LDO regulator output.                                                   |

|     |          | 10010: VDD                                                                              |

|     |          | 10011: GND                                                                              |

|     |          | 10100-11111: Reserved.                                                                  |

## Register 17.5. CPT1MD: Comparator 1 Mode

| Bit     | 7                 | 6        | 5     | 4     | 3        | 2 | 1    | 0 |  |  |

|---------|-------------------|----------|-------|-------|----------|---|------|---|--|--|

| Name    | CPLOUT            | Reserved | CPRIE | CPFIE | Reserved |   | CPMD |   |  |  |

| Туре    | RW                | R        | RW    | RW    | R        |   | RW   |   |  |  |

| Reset   | 0                 | 0        | 0     | 0     | 0        | 0 | 1    | 0 |  |  |

| SFR Add | SFR Address: 0xAB |          |       |       |          |   |      |   |  |  |

# Table 17.9. CPT1MD Register Bit Descriptions

| Bit | Name     | Function                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------|

| 7   | CPLOUT   | Comparator 1 Latched Output Flag.                                                        |

|     |          | This bit represents the comparator output value at the most recent PCA counter overflow. |

|     |          | 0: Comparator output was logic low at last PCA overflow.                                 |

|     |          | 1: Comparator output was logic high at last PCA overflow.                                |

| 6   | Reserved | Must write reset value.                                                                  |

| 5   | CPRIE    | Comparator 1 Rising-Edge Interrupt Enable.                                               |

|     |          | 0: Comparator Rising-Edge interrupt disabled.                                            |

|     |          | 1: Comparator Rising-Edge interrupt enabled.                                             |

| 4   | CPFIE    | Comparator 1 Falling-Edge Interrupt Enable.                                              |

|     |          | 0: Comparator Falling-Edge interrupt disabled.                                           |

|     |          | 1: Comparator Falling-Edge interrupt enabled.                                            |

| 3:2 | Reserved | Must write reset value.                                                                  |

| 1:0 | CPMD     | Comparator 1 Mode Select.                                                                |

|     |          | These bits affect the response time and power consumption of the comparator.             |

|     |          | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)                            |

|     |          | 01: Mode 1                                                                               |

|     |          | 10: Mode 2                                                                               |

|     |          | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)                             |

## Register 18.2. CRC0IN: CRC0 Data Input

| Bit     | 7                 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------------|-----------------|---|---|---|---|---|---|--|--|

| Name    |                   | CRC0IN          |   |   |   |   |   |   |  |  |

| Туре    | RW                |                 |   |   |   |   |   |   |  |  |

| Reset   | 0                 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

| SFR Add | SFR Address: 0xDD |                 |   |   |   |   |   |   |  |  |

## Table 18.3. CRC0IN Register Bit Descriptions

| Bit | Name   | Function                                                                                                                    |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0IN | CRC Data Input.                                                                                                             |

|     |        | Each write to CRCIN results in the written data being computed into the existing CRC result according to the CRC algorithm. |

## Register 18.4. CRC0AUTO: CRC0 Automatic Control

| Bit   | 7           | 6        | 5     | 4           | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|----------|-------|-------------|---|---|---|---|--|--|

| Name  | AUTOEN      | Reserved | CRCST |             |   |   |   |   |  |  |

| Туре  | RW          | R        |       | RW          |   |   |   |   |  |  |

| Reset | 0           | 0        | 0     | 0 0 0 0 0 0 |   |   |   |   |  |  |

|       | dress: 0xD2 | U        | U     | U           | U | U | U |   |  |  |

## Table 18.5. CRC0AUTO Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                 |  |  |  |  |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | AUTOEN   | Automatic CRC Calculation Enable.                                                                                                                                                                                        |  |  |  |  |

|     |          | When AUTOEN is set to 1, any write to CRC0CN will initiate an automatic CRC starting at flash sector CRCST and continuing for CRCCNT sectors.                                                                            |  |  |  |  |

| 6   | Reserved | Must write reset value.                                                                                                                                                                                                  |  |  |  |  |

| 5:0 | CRCST    | Automatic CRC Calculation Starting Block.                                                                                                                                                                                |  |  |  |  |

|     |          | These bits specify the flash block to start the automatic CRC calculation. The starting address of the first flash block included in the automatic CRC calculation is CRCST x block_size, where block_size is 256 bytes. |  |  |  |  |

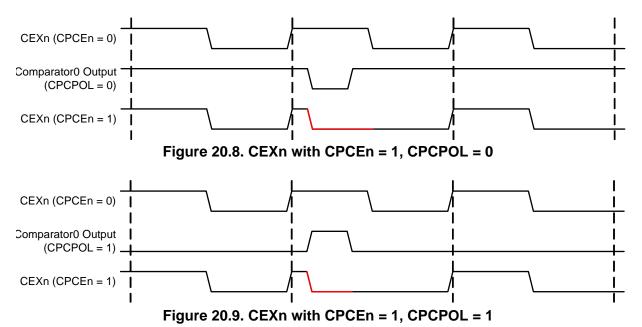

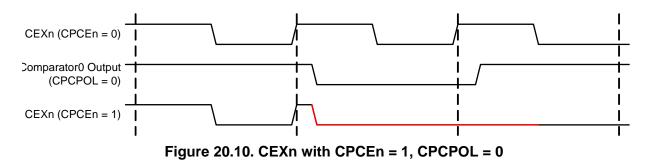

#### 20.5. Comparator Clear Function

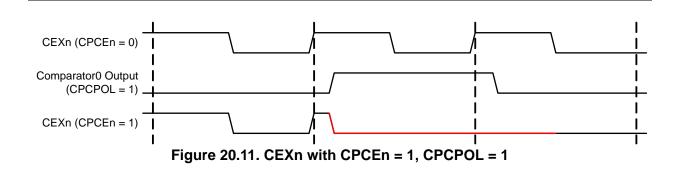

In 8/9/10/11/16-bit PWM modes, the comparator clear function utilizes the Comparator0 output synchronized to the system clock to clear CEXn to logic low for the current PWM cycle. This comparator clear function can be enabled for each PWM channel by setting the CPCEn bits to 1 in the PCA0CLR SFR. When the comparator clear function is disabled, CEXn is unaffected.

The asynchronous Comparator 0 output is logic high when the voltage of CP0+ is greater than CP0- and logic low when the voltage of CP0+ is less than CP0-. The polarity of the Comparator 0 output is used to clear CEXn as follows: when CPCPOL = 0, CEXn is cleared on the falling edge of the Comparator0 output (see Figure 20.8); when CPCPOL = 1, CEXn is cleared on the rising edge of the Comparator0 output (see Figure 20.9).

In the PWM cycle following the current cycle, should the Comparator 0 output remain logic low when CPCPOL = 0 or logic high when CPCPOL = 1, CEXn will continue to be cleared. See Figure 20.10 and Figure 20.11.

#### 21.1. General Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O crossbar using the Port Skip registers (PnSKIP).

- 4. Assign port pins to desired peripherals.

- 5. Enable the crossbar (XBARE = '1').

All port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a '1' indicates a digital input, and a '0' indicates an analog input. All pins default to digital inputs on reset.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMDOUT). Each port output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is '0', a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a '0' to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR2 to '1' enables the crossbar. Until the crossbar is enabled, the external pins remain as standard port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, Silicon Labs provides configuration utility software to determine the port I/O pin-assignments based on the crossbar register settings.

The crossbar must be enabled to use port pins as standard port I/O in output mode. Port output drivers of all crossbar pins are disabled whenever the crossbar is disabled.

| Bit                                                                                                                                                                                                                            | Name  | Function                                                                                                                                                                                                                                                   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0                                                                                                                                                                                                                              | RXBMT | Receive Buffer Empty (valid in slave mode only).                                                                                                                                                                                                           |  |  |  |  |

|                                                                                                                                                                                                                                |       | This bit will be set to logic 1 when the receive buffer has been read and contains no new information. If there is new information available in the receive buffer that has not been read, this bit will return to logic 0. RXBMT = 1 when in Master Mode. |  |  |  |  |

| <b>Note:</b> In slave mode, data on MOSI is sampled in the center of each data bit. In master mode, data on MISO is sampled one SYSCLK before the end of each data bit, to provide maximum settling time for the slave device. |       |                                                                                                                                                                                                                                                            |  |  |  |  |

#### Table 23.2. SPI0CFG Register Bit Descriptions

## Register 23.3. SPI0CKR: SPI0 Clock Rate

| Bit               | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|-----------------|---|---|---|---|---|---|---|

| Name              | SPIOCKR         |   |   |   |   |   |   |   |

| Туре              | RW              |   |   |   |   |   |   |   |

| Reset             | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

| SFR Address: 0xA2 |                 |   |   |   |   |   |   |   |

## Table 23.4. SPI0CKR Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                        |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0CKR | SPI0 Clock Rate.                                                                                                                                                                                                                                                                                                                                |

|     |         | These bits determine the frequency of the SCK output when the SPI0 module is config-<br>ured for master mode operation. The SCK clock frequency is a divided version of the<br>system clock, and is given in the following equation, where SYSCLK is the system clock<br>frequency and SPI0CKR is the 8-bit value held in the SPI0CKR register. |

|     |         | $f_{SCK} = \frac{SYSCLK}{2 \times (SPIOCKR + 1)}$                                                                                                                                                                                                                                                                                               |

|     |         | for 0 <= SPI0CKR <= 255                                                                                                                                                                                                                                                                                                                         |

## Register 25.7. TH1: Timer 1 High Byte

| Bit               | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------------|-----------------|---|---|---|---|---|---|---|--|

| Name              | TH1             |   |   |   |   |   |   |   |  |

| Туре              | RW              |   |   |   |   |   |   |   |  |

| Reset             | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |  |

| SFR Address: 0x8D |                 |   |   |   |   |   |   |   |  |

## Table 25.9. TH1 Register Bit Descriptions

| Bit | Name | Function                                                |  |  |

|-----|------|---------------------------------------------------------|--|--|

| 7:0 | TH1  | Timer 1 High Byte.                                      |  |  |

|     |      | he TH1 register is the high byte of the 16-bit Timer 1. |  |  |

#### 26.2. Operational Modes

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit in register SCON.

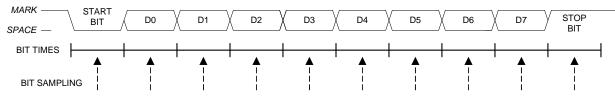

#### 26.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX pin and received at the RX pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB8 in the SCON register.

Data transmission begins when software writes a data byte to the SBUF0 register. The TI Transmit Interrupt Flag is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI must be logic 0, and if MCE is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB8 and the RI flag is set. If these conditions are not met, SBUF0 and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI is set.

Figure 26.3. 8-Bit UART Timing Diagram

#### 26.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE bit of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB8 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE bits set and do not generate interrupts on the reception of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 26.5. UART Multi-Processor Mode Interconnect Diagram

## 28.2. Temperature Sensor Offset and Slope

The temperature sensor slope and offset characteristics of Revision B devices are different than the slope and offset characteristics of Revision C devices. The differences are:

| Parameter  | Symbol           | Test Condition        | Min | Тур  | Max | Unit  |  |

|------------|------------------|-----------------------|-----|------|-----|-------|--|

| Revision B |                  |                       |     |      |     |       |  |

| Offset     | V <sub>OFF</sub> | T <sub>A</sub> = 0 °C | _   | 713  | _   | mV    |  |

| Slope      | М                |                       | _   | 2.67 | _   | mV/°C |  |

| Revision C |                  |                       |     |      |     |       |  |

| Offset     | V <sub>OFF</sub> | $T_A = 0 \ ^{\circ}C$ | _   | 757  | _   | mV    |  |

| Slope      | М                |                       | _   | 2.85 | _   | mV/°C |  |

Firmware that uses the slope and offset of the temperature sensor to calculate the temperature from the sensor ADC reading can detect the revision of the device by reading the REVID register and adjust the slope and offset calculations based on the result. A REVID value of 0x01 indicates a Revision B device, and a REVID value of 0x02 indicates a Revision C device.

#### 28.3. Flash Endurance

The flash endurance, or number of times the flash may be written and erased, on some Revision B devices may be lower than expected. Table 1.4 specifies a minimum Endurance (Write/Erase Cycles) as 20000, but some Revision B devices may support a minimum of ~5000 cycles.

#### 28.4. Latch-Up Performance

Pulling the device pins below ground and drawing significant current (~3.5 mA) can cause a Power-On Reset event with Revision B devices. Some pins, like P0.0 and P0.1, are more susceptible to this behavior than others. This behavior is outside normal operating parameters and would typically be seen during latch-up or ESD performance testing.

#### 28.5. Unique Identifier

Revision B devices do not implement the unique identifier described in "Device Identification and Unique Identifier" on page 68.

## 29. C2 Interface

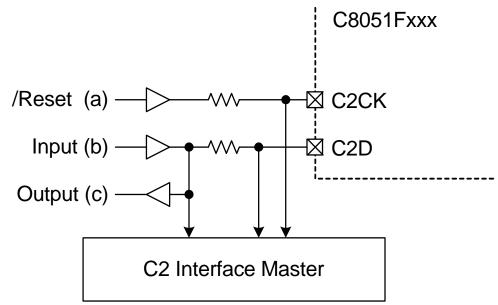

C8051F85x/86x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. Details on the C2 protocol can be found in the C2 Interface Specification.

## 29.1. C2 Pin Sharing

The C2 protocol allows the C2 pins to be shared with user functions so that in-system debugging and flash programming may be performed. C2CK is shared with the RST pin, while the C2D signal is shared with a port I/O pin. This is possible because C2 communication is typically performed when the device is in the halt state, where all on-chip peripherals and user software are stalled. In this halted state, the C2 interface can safely 'borrow' the C2CK and C2D pins. In most applications, external resistors are required to isolate C2 interface traffic from the user application. A typical isolation configuration is shown in Figure 29.1.

#### Figure 29.1. Typical C2 Pin Sharing

The configuration in Figure 29.1 assumes the following:

- 1. The user input (b) cannot change state while the target device is halted.

- 2. The  $\overline{\text{RST}}$  pin on the target device is used as an input only.

Additional resistors may be necessary depending on the specific application.