Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 15                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | A/D 15x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                              |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f851-c-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1.7. ADC

| Parameter                       | Parameter Symbol Test Condition |                                                                     | Min | Тур  | Мах                                     | Unit |

|---------------------------------|---------------------------------|---------------------------------------------------------------------|-----|------|-----------------------------------------|------|

| Resolution                      | N <sub>bits</sub>               | 12 Bit Mode                                                         |     | 12   |                                         | Bits |

|                                 |                                 | 10 Bit Mode                                                         | 10  |      |                                         | Bits |

| Throughput Rate                 | f <sub>S</sub>                  | 12 Bit Mode                                                         | _   | _    | 200                                     | ksps |

| (High Speed Mode)               |                                 | 10 Bit Mode                                                         | _   | _    | 800                                     | ksps |

| Throughput Rate                 | f <sub>S</sub>                  | 12 Bit Mode                                                         |     | _    | 62.5                                    | ksps |

| (Low Power Mode)                | -                               | 10 Bit Mode                                                         | _   | _    | 250                                     | ksps |

| Tracking Time                   | t <sub>TRK</sub>                | High Speed Mode                                                     | 230 | _    |                                         | ns   |

|                                 | -                               | Low Power Mode                                                      | 450 | _    |                                         | ns   |

| Power-On Time                   | t <sub>PWR</sub>                |                                                                     | 1.2 | _    | _                                       | μs   |

| SAR Clock Frequency             | f <sub>SAR</sub>                | High Speed Mode,<br>Reference is 2.4 V internal                     | _   | _    | 6.25                                    | MHz  |

|                                 |                                 | High Speed Mode,<br>Reference is not 2.4 V internal                 | —   | —    | 12.5                                    | MHz  |

|                                 |                                 | Low Power Mode                                                      | _   | _    | 4                                       | MHz  |

| Conversion Time                 | t <sub>CNV</sub>                | 10-Bit Conversion,1.1SAR Clock = 12.25 MHz,System Clock = 24.5 MHz. |     |      | μs                                      |      |

| Sample/Hold Capacitor           | C <sub>SAR</sub>                | Gain = 1                                                            | _   | 5    |                                         | pF   |

|                                 |                                 | Gain = 0.5                                                          | _   | 2.5  |                                         | pF   |

| Input Pin Capacitance           | C <sub>IN</sub>                 |                                                                     | _   | 20   |                                         | pF   |

| Input Mux Impedance             | R <sub>MUX</sub>                |                                                                     | _   | 550  |                                         | Ω    |

| Voltage Reference Range         | V <sub>REF</sub>                |                                                                     | 1   | _    | V <sub>DD</sub>                         | V    |

| Input Voltage Range*            | V <sub>IN</sub>                 | Gain = 1                                                            | 0   | _    | V <sub>REF</sub>                        | V    |

|                                 |                                 | Gain = 0.5                                                          | 0   |      | $2xV_{REF}$                             | V    |

| Power Supply Rejection<br>Ratio | PSRR <sub>ADC</sub>             |                                                                     | —   | 70   | —                                       | dB   |

| DC Performance                  |                                 |                                                                     |     |      |                                         |      |

| Integral Nonlinearity           | INL                             | 12 Bit Mode                                                         | _   | ±1   | ±2.3                                    | LSB  |

|                                 |                                 | 10 Bit Mode                                                         | _   | ±0.2 | ±0.6                                    | LSB  |

| Differential Nonlinearity       | DNL                             | 12 Bit Mode                                                         | -1  | ±0.7 | 1.9                                     | LSB  |

| (Guaranteed Monotonic)          |                                 | 10 Bit Mode                                                         | _   | ±0.2 | ±0.6                                    | LSB  |

| *Note: Absolute input pin volta | age is limited by               | the V <sub>DD</sub> supply.                                         |     |      | ı — — — — — — — — — — — — — — — — — — — |      |

| Pin Name         | Туре                                        | Pin Numbers | Crossbar Capability | Additional Digital Functions          | Analog Functions           |

|------------------|---------------------------------------------|-------------|---------------------|---------------------------------------|----------------------------|

| P0.1             | Standard I/O                                | 2           | Yes                 | POMAT.1<br>INT0.1<br>INT1.1           | ADC0.1<br>CP0P.1<br>CP0N.1 |

| P0.2             | Standard I/O                                | 1           | Yes                 | POMAT.2<br>INT0.2<br>INT1.2           | ADC0.2<br>CP0P.2<br>CP0N.2 |

| P0.3 /<br>EXTCLK | Standard I/O /<br>External CMOS Clock Input | 16          | Yes                 | POMAT.3<br>EXTCLK<br>INT0.3<br>INT1.3 | ADC0.3<br>CP0P.3<br>CP0N.3 |

| P0.4             | Standard I/O                                | 15          | Yes                 | POMAT.4<br>INT0.4<br>INT1.4           | ADC0.4<br>CP0P.4<br>CP0N.4 |

| P0.5             | Standard I/O                                | 14          | Yes                 | P0MAT.5<br>INT0.5<br>INT1.5           | ADC0.5<br>CP0P.5<br>CP0N.5 |

| P0.6             | Standard I/O                                | 13          | Yes                 | POMAT.6<br>CNVSTR<br>INT0.6<br>INT1.6 | ADC0.6<br>CP1P.0<br>CP1N.0 |

| P0.7             | Standard I/O                                | 12          | Yes                 | POMAT.7<br>INT0.7<br>INT1.7           | ADC0.7<br>CP1P.1<br>CP1N.1 |

| P1.0             | Standard I/O                                | 11          | Yes                 | P1MAT.0                               | ADC0.8<br>CP1P.2<br>CP1N.2 |

### Table 3.3. Pin Definitions for C8051F860/1/2/3/4/5-GS and C8051F860/1/2/3/4/5-IS

# C8051F85x/86x

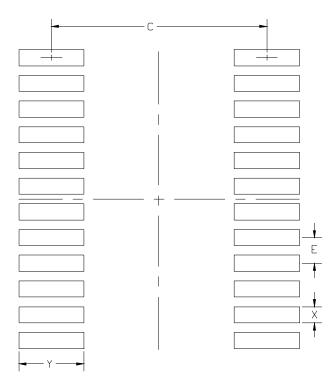

### Figure 5.2. QSOP-24 PCB Land Pattern

### Table 5.2. QSOP-24 PCB Land Pattern Dimensions

| Dimension | Min  | Max  |

|-----------|------|------|

| С         | 5.20 | 5.30 |

| E 0.      |      | BSC  |

| X         | 0.30 | 0.40 |

| Y         | 1.50 | 1.60 |

| Notes:    |      |      |

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on the IPC-7351 guidelines.

#### Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### Card Assembly

- 7. A No-Clean, Type-3 solder paste is recommended.

- **8.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 14.10. ADC Control Registers

### Register 14.1. ADC0CN0: ADC0 Control 0

| Bit   | 7    | 6      | 5     | 4      | 3      | 2    | 1 | 0 |

|-------|------|--------|-------|--------|--------|------|---|---|

| Name  | ADEN | ADBMEN | ADINT | ADBUSY | ADWINT | ADCM |   |   |

| Туре  | RW   | RW     | RW    | RW     | RW     | RW   |   |   |

| Reset | 0    | 0      | 0     | 0      | 0      | 0    | 0 | 0 |

#### SFR Address: 0xE8 (bit-addressable)

# Table 14.4. ADC0CN0 Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                                                    |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ADEN   | Enable.                                                                                                                                                                                                                     |

|     |        | 0: ADC0 Disabled (low-power shutdown).                                                                                                                                                                                      |

|     |        | 1: ADC0 Enabled (active and ready for data conversions).                                                                                                                                                                    |

| 6   | ADBMEN | Burst Mode Enable.                                                                                                                                                                                                          |

|     |        | 0: ADC0 Burst Mode Disabled.                                                                                                                                                                                                |

|     |        | 1: ADC0 Burst Mode Enabled.                                                                                                                                                                                                 |

| 5   | ADINT  | Conversion Complete Interrupt Flag.                                                                                                                                                                                         |

|     |        | Set by hardware upon completion of a data conversion (ADBMEN=0), or a burst of conversions (ADBMEN=1). Can trigger an interrupt. Must be cleared by software.                                                               |

| 4   | ADBUSY | ADC Busy.                                                                                                                                                                                                                   |

|     |        | Writing 1 to this bit initiates an ADC conversion when ADC0CM = 000. This bit should not be polled to indicate when a conversion is complete. Instead, the ADINT bit should be used when polling for conversion completion. |

| 3   | ADWINT | Window Compare Interrupt Flag.                                                                                                                                                                                              |

|     |        | Set by hardware when the contents of ADC0H:ADC0L fall within the window specified by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL. Can trigger an interrupt. Must be cleared by software.                                            |

| 2:0 | ADCM   | Start of Conversion Mode Select.                                                                                                                                                                                            |

|     |        | Specifies the ADC0 start of conversion source. All remaining bit combinations are reserved.                                                                                                                                 |

|     |        | 000: ADC0 conversion initiated on write of 1 to ADBUSY.                                                                                                                                                                     |

|     |        | 001: ADC0 conversion initiated on overflow of Timer 0.<br>010: ADC0 conversion initiated on overflow of Timer 2.                                                                                                            |

|     |        | 011: ADC0 conversion initiated on overflow of Timer 3.                                                                                                                                                                      |

|     |        | 100: ADC0 conversion initiated on rising edge of CNVSTR.                                                                                                                                                                    |

|     |        | 101-111: Reserved.                                                                                                                                                                                                          |

# Register 14.14. REF0CN: Voltage Reference Control

| Bit     | 7                 | 6        | 5     | 4                   | 3 | 2     | 1 | 0 |

|---------|-------------------|----------|-------|---------------------|---|-------|---|---|

| Name    | IREFLVL           | Reserved | GNDSL | REFSL TEMPE Reserve |   | erved |   |   |

| Туре    | RW                | R        | RW    | RW                  |   | RW    | R |   |

| Reset   | 0                 | 0        | 0     | 1                   | 1 | 0     | 0 | 0 |

| SFR Add | SFR Address: 0xD1 |          |       |                     |   |       |   |   |

# Table 14.17. REF0CN Register Bit Descriptions

| Bit | Name     | Function                                                                     |

|-----|----------|------------------------------------------------------------------------------|

| 7   | IREFLVL  | Internal Voltage Reference Level.                                            |

|     |          | Sets the voltage level for the internal reference source.                    |

|     |          | 0: The internal reference operates at 1.65 V nominal.                        |

|     |          | 1: The internal reference operates at 2.4 V nominal.                         |

| 6   | Reserved | Must write reset value.                                                      |

| 5   | GNDSL    | Analog Ground Reference.                                                     |

|     |          | Selects the ADC0 ground reference.                                           |

|     |          | 0: The ADC0 ground reference is the GND pin.                                 |

|     |          | 1: The ADC0 ground reference is the AGND pin.                                |

| 4:3 | REFSL    | Voltage Reference Select.                                                    |

|     |          | Selects the ADC0 voltage reference.                                          |

|     |          | 00: The ADC0 voltage reference is the VREF pin.                              |

|     |          | 01: The ADC0 voltage reference is the VDD pin.                               |

|     |          | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage. |

|     |          | 11: The ADC0 voltage reference is the internal voltage reference.            |

| 2   | TEMPE    | Temperature Sensor Enable.                                                   |

|     |          | Enables/Disables the internal temperature sensor.                            |

|     |          | 0: Temperature Sensor Disabled.                                              |

|     |          | 1: Temperature Sensor Enabled.                                               |

| 1:0 | Reserved | Must write reset value.                                                      |

# Register 17.3. CPT0MX: Comparator 0 Multiplexer Selection

| Bit   | 7               | 6  | 5  | 4 | 3    | 2 | 1 | 0 |

|-------|-----------------|----|----|---|------|---|---|---|

| Name  |                 | СМ | XN |   | СМХР |   |   |   |

| Туре  | RW              |    |    |   | RW   |   |   |   |

| Reset | 1 1 1 1 1 1 1 1 |    |    |   |      |   |   |   |

# Table 17.7. CPT0MX Register Bit Descriptions

| Bit | Name | Function                                   |

|-----|------|--------------------------------------------|

| 7:4 | CMXN | Comparator 0 Negative Input MUX Selection. |

|     |      | 0000: External pin CP0N.0                  |

|     |      | 0001: External pin CP0N.1                  |

|     |      | 0010: External pin CP0N.2                  |

|     |      | 0011: External pin CP0N.3                  |

|     |      | 0100: External pin CP0N.4                  |

|     |      | 0101: External pin CP0N.5                  |

|     |      | 0110: External pin CP0N.6                  |

|     |      | 0111: External pin CP0N.7                  |

|     |      | 1000: GND                                  |

|     |      | 1001-1111: Reserved.                       |

| 3:0 | CMXP | Comparator 0 Positive Input MUX Selection. |

|     |      | 0000: External pin CP0P.0                  |

|     |      | 0001: External pin CP0P.1                  |

|     |      | 0010: External pin CP0P.2                  |

|     |      | 0011: External pin CP0P.3                  |

|     |      | 0100: External pin CP0P.4                  |

|     |      | 0101: External pin CP0P.5                  |

|     |      | 0110: External pin CP0P.6                  |

|     |      | 0111: External pin CP0P.7                  |

|     |      | 1000: Internal LDO output                  |

|     |      | 1001-1111: Reserved.                       |

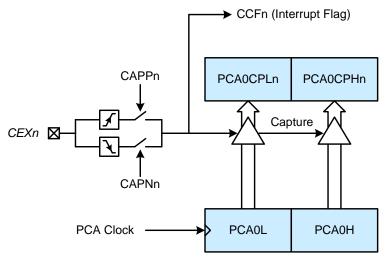

#### 20.3.2. Edge-Triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/ timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 20.2. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

# Register 21.5. P0MASK: Port 0 Mask

| Bit               | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|--------|---|---|---|---|---|---|---|

| Name              | POMASK |   |   |   |   |   |   |   |

| Туре              | RW     |   |   |   |   |   |   |   |

| Reset             | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0xFE |        |   |   |   |   |   |   |   |

# Table 21.8. P0MASK Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MASK | Port 0 Mask Value.                                                                                                                                                                                |

|     |        | Selects P0 pins to be compared to the corresponding bits in P0MAT.<br>0: P0.x pin logic value is ignored and will cause a port mismatch event.<br>1: P0.x pin logic value is compared to P0MAT.x. |

# Register 21.6. P0MAT: Port 0 Match

| Bit     | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

|---------|-----------------|--|--|--|--|--|--|--|

| Name    | POMAT           |  |  |  |  |  |  |  |

| Туре    | RW              |  |  |  |  |  |  |  |

| Reset   | 1 1 1 1 1 1 1 1 |  |  |  |  |  |  |  |

| SFR Add | Address: 0xFD   |  |  |  |  |  |  |  |

# Table 21.9. POMAT Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                     |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | POMAT | Port 0 Match Value.                                                                                                                                                                          |

|     |       | Match comparison value used on P0 pins for bits in P0MASK which are set to 1.<br>0: P0.x pin logic value is compared with logic LOW.<br>1: P0.x pin logic value is compared with logic HIGH. |

# Register 21.16. P1SKIP: Port 1 Skip

| Bit   | 7  | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|-------|----|---|---|-----|-----|---|---|---|

| Name  | ·  |   |   | P1S | KIP |   |   |   |

| Туре  | RW |   |   |     |     |   |   |   |

| Reset | 0  | 0 | 0 | 0   | 0   | 0 | 0 | 0 |

# Table 21.19. P1SKIP Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                        |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP | Port 1 Skip.                                                                                                                                    |

|     |        | These bits select port pins to be skipped by the crossbar decoder. Port pins used for ana-<br>log, special functions or GPIO should be skipped. |

|     |        | 0: Corresponding P1.x pin is not skipped by the crossbar.                                                                                       |

|     |        | 1: Corresponding P1.x pin is skipped by the crossbar.                                                                                           |

|     |        | <sup>3</sup> bits (P1.0-P1.7) on QSOP24 packages and 7 bits (P1.0-P1.6) on QFN20 packages and 4 bits IIC16 packages.                            |

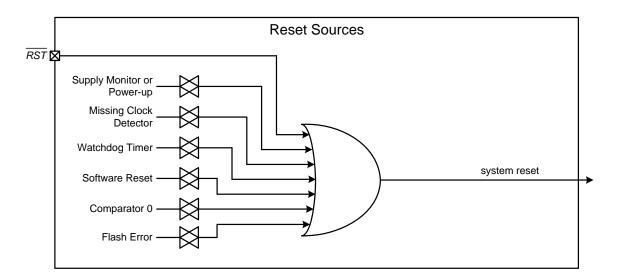

# 22. Reset Sources and Supply Monitor

Reset circuitry allows the controller to be easily placed in a predefined default condition. Upon entering this reset state, the following events occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External port pins are placed in a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain, low-drive mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the RST pin is driven low until the device exits the reset state. Note that during a power-on event, there may be a short delay before the POR circuitry fires and the RST pin is driven low. During that time, the RST pin will be weakly pulled to the  $V_{DD}$  supply pin.

On exit from the reset state, the program counter (PC) is reset, the Watchdog Timer is enabled and the system clock defaults to the internal oscillator. Program execution begins at location 0x0000.

Figure 22.1. Reset Sources

| Bit | Name  | Function                                                                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SMBCS | SMBus0 Clock Source Selection.                                                                                                                                                                                                                                                 |

|     |       | These two bits select the SMBus0 clock source, which is used to generate the SMBus0<br>bit rate. See the SMBus clock timing section for additional details.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow |

# Table 24.7. SMB0CF Register Bit Descriptions

### 25.1. Timer 0 and Timer 1

Timer 0 and Timer 1 are each implemented as a16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register. Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register. Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently for the operating modes described below.

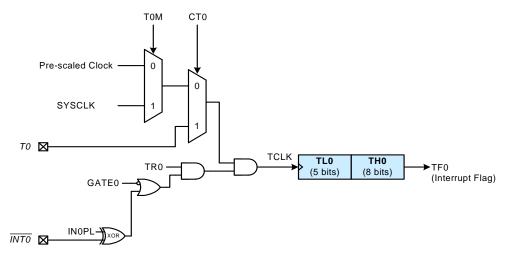

#### 25.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 in TCON is set and an interrupt will occur if Timer 0 interrupts are enabled.

The CT0 bit in the TMOD register selects the counter/timer's clock source. When CT0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register. Clearing CT selects the clock defined by the TOM bit in register CKCON. When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON.

Setting the TR0 bit enables the timer when either GATE0 in the TMOD register is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF. Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0, facilitating pulse width measurements.

| TR0                  | GATE0 | INT0 | Counter/Timer |  |  |  |

|----------------------|-------|------|---------------|--|--|--|

| 0                    | Х     | Х    | Disabled      |  |  |  |

| 1                    | 0     | Х    | Enabled       |  |  |  |

| 1                    | 1     | 0    | Disabled      |  |  |  |

| 1                    | 1     | 1    | Enabled       |  |  |  |

| Note: X = Don't Care |       |      |               |  |  |  |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT1 is used with Timer 1; the /INT1 polarity is defined by bit IN1PL in register IT01CF.

Figure 25.1. T0 Mode 0 Block Diagram

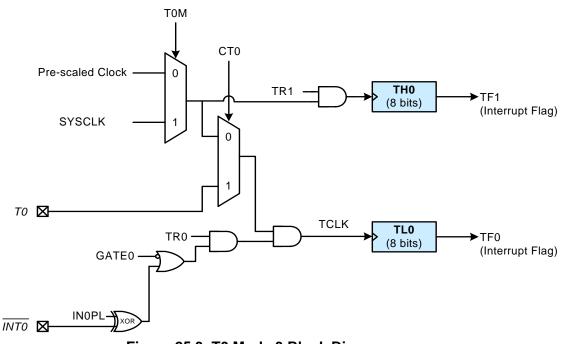

#### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/ timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, CT0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 25.3. T0 Mode 3 Block Diagram

# Table 25.3. CKCON Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                                                                       |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SCA  | Timer 0/1 Prescale Bits.                                                                                                                                                                                                       |

|     |      | These bits control the Timer 0/1 Clock Prescaler:<br>00: System clock divided by 12<br>01: System clock divided by 4<br>10: System clock divided by 48<br>11: External clock divided by 8 (synchronized with the system clock) |

|                    |                              |                      | Fre                            | equency: 49 MI        | Hz                                              |                  |                                  |

|--------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                    | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                    | 230400                       | -0.32%               | 106                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |

|                    | 115200                       | -0.32%               | 212                            | SYSCLK                | XX                                              | 1                | 0x96                             |

| from<br>Osc.       | 57600                        | 0.15%                | 426                            | SYSCLK                | XX                                              | 1                | 0x2B                             |

| A fr<br>al O       | 28800                        | -0.32%               | 848                            | SYSCLK/4              | 01                                              | 0                | 0x96                             |

| SYSCLK<br>Internal | 14400                        | 0.15%                | 1704                           | SYSCLK/12             | 00                                              | 0                | 0xB9                             |

| SYS(<br>Inter      | 9600                         | -0.32%               | 2544                           | SYSCLK/12             | 00                                              | 0                | 0x96                             |

|                    | 2400                         | -0.32%               | 10176                          | SYSCLK/48             | 10                                              | 0                | 0x96                             |

|                    | 1200                         | 0.15%                | 20448                          | SYSCLK/48             | 10                                              | 0                | 0x2B                             |

| Notes:             | -                            | •                    |                                | ·                     |                                                 |                  |                                  |

Table 26.1. Timer Settings for Standard Baud Rates Using the Internal 24.5 MHz Oscillator

1. SCA1–SCA0 and T1M bit definitions can be found in Timer1 chapter.

**2.** X = Don't care.

# 28. Revision-Specific Behavior

C8051F85x/86x Revision B devices have differences from Revision C devices:

- Temperature Sensor offset and slope

- Flash endurance

- Latch-up performance

- Unique Identifier

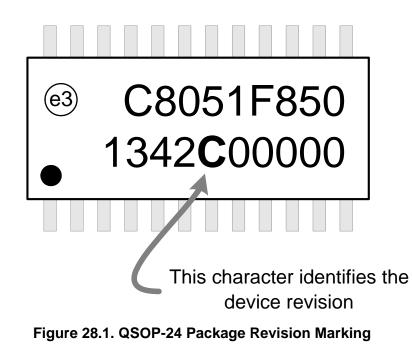

### 28.1. Revision Identification

The Lot ID Code on the top side of the device package can be used for decoding device revision information. Figure 28.1, Figure 28.2, and Figure 28.3 show how to find the Lot ID Code on the top side of the device package.

Firmware can distinguish between a Revision B and Revision C device using the value of the REVID register described in "Device Identification and Unique Identifier" on page 68.

## 29.2. C2 Interface Registers

The following describes the C2 registers necessary to perform flash programming through the C2 interface. All C2 registers are accessed through the C2 interface, and are not available in the SFR map for firmware access.

### Register 29.1. C2ADD: C2 Address

| Bit       | 7 6 5 4 3 2 1 0                           |  |  |  |  |  |  |

|-----------|-------------------------------------------|--|--|--|--|--|--|

| Name      | C2ADD                                     |  |  |  |  |  |  |

| Туре      | RW                                        |  |  |  |  |  |  |

| Reset     | 0 0 0 0 0 0 0 0                           |  |  |  |  |  |  |

| This regi | This register is part of the C2 protocol. |  |  |  |  |  |  |

### Table 29.1. C2ADD Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | C2ADD | C2 Address.                                                                                                                                                                                                                    |

|     |       | The C2ADD register is accessed via the C2 interface. The value written to C2ADD selects the target data register for C2 Data Read and Data Write commands.<br>0x00: C2DEVID<br>0x01: C2REVID<br>0x02: C2FPCTL<br>0xB4: C2FPDAT |