# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | A/D 16x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f851-c-gur |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1.11. Port I/O

| Parameter                                                           | Symbol          | Test Condition                                                   | Min                   | Тур | Max | Unit |

|---------------------------------------------------------------------|-----------------|------------------------------------------------------------------|-----------------------|-----|-----|------|

| Output High Voltage (High Drive)                                    | V <sub>OH</sub> | I <sub>OH</sub> = -3 mA                                          | V <sub>DD</sub> – 0.7 |     |     | V    |

| Output Low Voltage (High Drive)                                     | V <sub>OL</sub> | I <sub>OL</sub> = 8.5 mA                                         | _                     |     | 0.6 | V    |

| Output High Voltage (Low Drive)                                     | V <sub>OH</sub> | I <sub>OH</sub> = -1 mA                                          | V <sub>DD</sub> – 0.7 |     |     | V    |

| Output Low Voltage (Low Drive)                                      | V <sub>OL</sub> | I <sub>OL</sub> = 1.4 mA                                         | _                     |     | 0.6 | V    |

| Input High Voltage                                                  | V <sub>IH</sub> |                                                                  | V <sub>DD</sub> – 0.6 |     |     | V    |

| Input Low Voltage                                                   | V <sub>IL</sub> |                                                                  | _                     |     | 0.6 | V    |

| Pin Capacitance                                                     | C <sub>IO</sub> |                                                                  | _                     | 7   |     | pF   |

| Weak Pull-Up Current<br>(V <sub>IN</sub> = 0 V)                     | I <sub>PU</sub> | V <sub>DD</sub> = 3.6                                            | -30                   | -20 | -10 | μA   |

| Input Leakage<br>(Pullups off or Analog)                            | I <sub>LK</sub> | $\text{GND} \leq \text{V}_{\text{IN}} \leq \text{V}_{\text{DD}}$ | -1.1                  |     | 1.1 | μA   |

| Input Leakage Current with V <sub>IN</sub><br>above V <sub>DD</sub> | I <sub>LK</sub> | $V_{DD} < V_{IN} < V_{DD}$ +2.0 V                                | 0                     | 5   | 150 | μA   |

#### 2.1.3.1. Normal Mode

Normal mode encompasses the typical full-speed operation. The power consumption of the device in this mode will vary depending on the system clock speed and any analog peripherals that are enabled.

#### 2.1.3.2. Idle Mode

Setting the IDLE bit in PCON causes the hardware to halt the CPU and enter idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the IDLE bit to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

#### 2.1.3.3. Stop Mode (Regulator On)

Setting the STOP bit in PCON when STOPCF in REGOCN is clear causes the controller core to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the internal oscillator, CPU, and all digital peripherals are stopped. Each analog peripheral may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset.

#### 2.1.3.4. Shutdown Mode (Regulator Off)

Shutdown mode is an extension of the normal stop mode operation. Setting the STOP bit in PCON when STOPCF in REGOCN is also set causes the controller core to enter shutdown mode as soon as the instruction that sets the bit completes execution, and then the internal regulator is powered down. In shutdown mode, all core functions, memories and peripherals are powered off. An external pin reset or power-on reset is required to exit shutdown mode.

#### 2.2. I/O

#### 2.2.1. General Features

The C8051F85x/86x ports have the following features:

- Push-pull or open-drain output modes and analog or digital modes.

- Port Match allows the device to recognize a change on a port pin value and wake from idle mode or generate an interrupt.

- Internal pull-up resistors can be globally enabled or disabled.

- Two external interrupts provide unique interrupt vectors for monitoring time-critical events.

- Above-rail tolerance allows 5 V interface when device is powered.

#### 2.2.2. Crossbar

The C8051F85x/86x devices have a digital peripheral crossbar with the following features:

- Flexible peripheral assignment to port pins.

- Pins can be individually skipped to move peripherals as needed for design or layout considerations.

The crossbar has a fixed priority for each I/O function and assigns these functions to the port pins. When a digital resource is selected, the least-significant unassigned port pin is assigned to that resource. If a port pin is assigned, the crossbar skips that pin when assigning the next selected resource. Additionally, the crossbar will skip port pins whose associated bits in the PnSKIP registers are set. This provides some flexibility when designing a system: pins involved with sensitive analog measurements can be moved away from digital I/O and peripherals can be moved around the chip as needed to ease layout constraints.

## 8.1. Program Memory

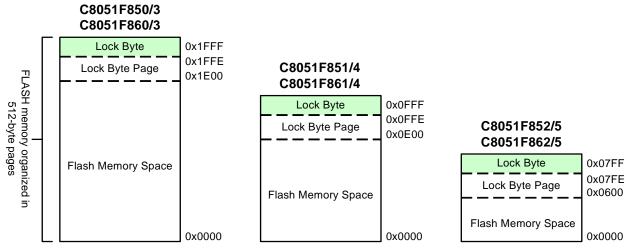

The CIP-51 core has a 64 kB program memory space. The C8051F85x/86x family implements 8 kB, 4 kB or 2 kB of this program memory space as in-system, re-programmable flash memory. The last address in the flash block (0x1FFF on 8 kB devices, 0x0FFF on 4 kB devices and 0x07FF on 2 kB devices) serves as a security lock byte for the device, and provides read, write and erase protection. Addresses above the lock byte within the 64 kB address space are reserved.

Figure 8.2. Flash Program Memory Map

#### 8.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F85x/86x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip flash memory space. MOVC instructions are always used to read flash memory, while MOVX write instructions are used to erase and write flash. This flash access feature provides a mechanism for the C8051F85x/86x to update program code and use the program memory space for non-volatile data storage. Refer to Section "10. Flash Memory" on page 61 for further details.

#### 8.2. Data Memory

The C8051F85x/86x device family includes up to 512 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. On devices with 512 bytes total RAM, 256 additional bytes of memory are available as on-chip "external" memory. The data memory map is shown in Figure 8.1 for reference.

#### 8.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

# 10. Flash Memory

On-chip, re-programmable flash memory is included for program code and non-volatile data storage. The flash memory is organized in 512-byte pages. It can be erased and written through the C2 interface or from firmware by overloading the MOVX instruction. Any individual byte in flash memory must only be written once between page erase operations.

## **10.1. Security Options**

The CIP-51 provides security options to protect the flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the flash memory from accidental modification by software. PSWE must be explicitly set to '1' before software can modify the flash memory; both PSWE and PSEE must be set to '1' before software can erase flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located in flash user space offers protection of the flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. See Section "8. Memory Organization" on page 52 for the location of the security byte. The flash security mechanism allows the user to lock *n* 512-byte flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where *n* is the 1's complement number represented by the Security Lock Byte. Note that the page containing the flash Security Lock Byte is unlocked when no other flash pages are locked (all bits of the Lock Byte are '1') and locked when any other flash pages are locked (any bit of the Lock Byte is '0'). An example is shown in Figure 10.1.

| Security Lock Byte: | 11111101b                                  |

|---------------------|--------------------------------------------|

| 1s Complement:      | 00000010b                                  |

| Flash pages locked: | 3 (First two flash pages + Lock Byte Page) |

#### Figure 10.1. Security Byte Decoding

The level of flash security depends on the flash access method. The three flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 10.1 summarizes the flash security features of the C8051F85x/86x devices.

| Action                                                             | C2 Debug      | User Firmware executing from: |               |  |

|--------------------------------------------------------------------|---------------|-------------------------------|---------------|--|

|                                                                    | Interface     | an unlocked page              | a locked page |  |

| Read, Write or Erase unlocked pages (except page with Lock Byte)   | Permitted     | Permitted                     | Permitted     |  |

| Read, Write or Erase locked pages (except page with Lock Byte)     | Not Permitted | Flash Error Reset             | Permitted     |  |

| Read or Write page containing Lock Byte (if no pages are locked)   | Permitted     | Permitted                     | N/A           |  |

| Read or Write page containing Lock Byte<br>(if any page is locked) | Not Permitted | Flash Error Reset             | Permitted     |  |

#### Table 10.1. Flash Security Summary

Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 10.4.2. PSWE Maintenance

- 7. Reduce the number of places in code where the PSWE bit (in register PSCTL) is set to a 1. There should be exactly one routine in code that sets PSWE to a '1' to write flash bytes and one routine in code that sets PSWE and PSEE both to a '1' to erase flash pages.

- 8. Minimize the number of variable accesses while PSWE is set to a 1. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash From Firmware", available from the Silicon Laboratories web site.

- 9. Disable interrupts prior to setting PSWE to a '1' and leave them disabled until after PSWE has been reset to 0. Any interrupts posted during the flash write or erase operation will be serviced in priority order after the flash operation has been completed and interrupts have been re-enabled by software.

- 10. Make certain that the flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 11. Add address bounds checking to the routines that write or erase flash memory to ensure that a routine called with an illegal address does not result in modification of the flash.

#### 10.4.3. System Clock

- 12. If operating from an external crystal-based source, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 13. If operating from the external oscillator, switch to the internal oscillator during flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the flash operation has completed.

Additional flash recommendations and example code can be found in "AN201: Writing to Flash From Firmware", available from the Silicon Laboratories website.

# Register 14.10. ADC0GTL: ADC0 Greater-Than Low Byte

|                                                            | • |  |  |  |  |  |  |  |  |

|------------------------------------------------------------|---|--|--|--|--|--|--|--|--|

|                                                            |   |  |  |  |  |  |  |  |  |

| RW                                                         |   |  |  |  |  |  |  |  |  |

| 1 1 1 1 1 1 1 1                                            |   |  |  |  |  |  |  |  |  |

| RW       1     1     1     1     1     1       dress: 0xC3 |   |  |  |  |  |  |  |  |  |

## Table 14.13. ADC0GTL Register Bit Descriptions

| Bit      | Name                                                      | Function                                                                   |  |  |  |  |  |  |

|----------|-----------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0      | ADC0GTL                                                   | Greater-Than Low Byte.                                                     |  |  |  |  |  |  |

|          |                                                           | Least Significant Byte of the 16-bit Greater-Than window compare register. |  |  |  |  |  |  |

| Note: In | Note: In 8-bit mode, this register should be set to 0x00. |                                                                            |  |  |  |  |  |  |

# 16.6. Low Frequency Oscillator Control Registers

| Bit     | 7                 | 6       | 5 | 4  | 3   | 2   | 1 | 0 |  |  |

|---------|-------------------|---------|---|----|-----|-----|---|---|--|--|

| Name    | OSCLEN            | OSCLRDY |   | OS | OSC | CLD |   |   |  |  |

| Туре    | RW                | R       |   | RW |     |     |   | W |  |  |

| Reset   | 0                 | 0       | Х | Х  | 0   | 0   |   |   |  |  |

| SFR Add | SFR Address: 0xB1 |         |   |    |     |     |   |   |  |  |

# Table 16.2. OSCLCN Register Bit Descriptions

| Bit      | Name           | Function                                                                                                                                                                                                                                                                                                                                                               |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7        | OSCLEN         | <ul> <li>Internal L-F Oscillator Enable.</li> <li>This bit enables the internal low-frequency oscillator. Note that the low-frequency oscillator is automatically enabled when the watchdog timer is active.</li> <li>0: Internal L-F Oscillator Disabled.</li> <li>1: Internal L-F Oscillator Enabled.</li> </ul>                                                     |

| 6        | OSCLRDY        | Internal L-F Oscillator Ready.<br>0: Internal L-F Oscillator frequency not stabilized.<br>1: Internal L-F Oscillator frequency stabilized.                                                                                                                                                                                                                             |

| 5:2      | OSCLF          | Internal L-F Oscillator Frequency Control Bits.<br>Fine-tune control bits for the Internal L-F oscillator frequency. When set to 0000b, the L-F oscillator operates at its fastest setting. When set to 1111b, the L-F oscillator operates at its slowest setting. The OSCLF bits should only be changed by firmware when the L-F oscillator is disabled (OSCLEN = 0). |

| 1:0      | OSCLD          | Internal L-F Oscillator Divider Select.<br>00: Divide by 8 selected.<br>01: Divide by 4 selected.<br>10: Divide by 2 selected.<br>11: Divide by 1 selected.                                                                                                                                                                                                            |

| Note: OS | SCLRDY is only | set back to 0 in the event of a device reset or a change to the OSCLD bits.                                                                                                                                                                                                                                                                                            |

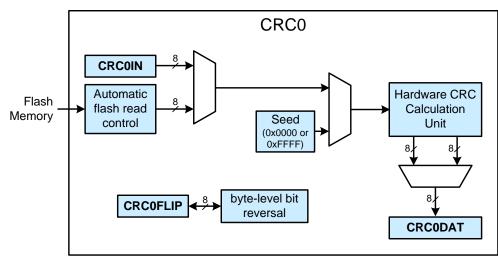

# 18. Cyclic Redundancy Check Unit (CRC0)

C8051F85x/86x devices include a cyclic redundancy check unit (CRC0) that can perform a CRC using a 16-bit polynomial. CRC0 accepts a stream of 8-bit data written to the CRC0IN register. CRC0 posts the 16-bit result to an internal register. The internal result register may be accessed indirectly using the CRCPNT bits and CRC0DAT register, as shown in Figure 18.1. CRC0 also has a bit reverse register for quick data manipulation.

Figure 18.1. CRC0 Block Diagram

## 18.1. CRC Algorithm

The CRC unit generates a CRC result equivalent to the following algorithm:

- 1. XOR the input with the most-significant bits of the current CRC result. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x0000 or 0xFFFF).

- 2a. If the MSB of the CRC result is set, shift the CRC result and XOR the result with the selected polynomial.

- 2b. If the MSB of the CRC result is not set, shift the CRC result.

Repeat Steps 2a/2b for the number of input bits (8). The algorithm is also described in the following example.

## Register 20.12. PCA0CPM1: PCA Capture/Compare Mode

| Bit     | 7           | 6    | 5    | 4    | 3   | 2   | 1   | 0    |

|---------|-------------|------|------|------|-----|-----|-----|------|

| Name    | PWM16       | ECOM | CAPP | CAPN | MAT | TOG | PWM | ECCF |

| Туре    | RW          | RW   | RW   | RW   | RW  | RW  | RW  | RW   |

| Reset   | 0           | 0    | 0    | 0    | 0   | 0   | 0   | 0    |

| SFR Add | lress: 0xDB |      |      |      |     |     |     |      |

## Table 20.14. PCA0CPM1 Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWM16 | 16-bit Pulse Width Modulation Enable.                                                                                                                                                                                                                                             |

|     |       | This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.<br>0: 8 to 11-bit PWM selected.                                                                                                                                                                         |

|     |       | 1: 16-bit PWM selected.                                                                                                                                                                                                                                                           |

| 6   | ECOM  | Comparator Function Enable.                                                                                                                                                                                                                                                       |

|     |       | This bit enables the comparator function.                                                                                                                                                                                                                                         |

| 5   | CAPP  | Capture Positive Function Enable.                                                                                                                                                                                                                                                 |

|     |       | This bit enables the positive edge capture capability.                                                                                                                                                                                                                            |

| 4   | CAPN  | Capture Negative Function Enable.                                                                                                                                                                                                                                                 |

|     |       | This bit enables the negative edge capture capability.                                                                                                                                                                                                                            |

| 3   | MAT   | Match Function Enable.                                                                                                                                                                                                                                                            |

|     |       | This bit enables the match function. When enabled, matches of the PCA counter with a module's capture/compare register cause the CCF1 bit in the PCA0MD register to be set to logic 1.                                                                                            |

| 2   | TOG   | Toggle Function Enable.                                                                                                                                                                                                                                                           |

|     |       | This bit enables the toggle function. When enabled, matches of the PCA counter with the capture/compare register cause the logic level on the CEX1 pin to toggle. If the PWM bit is also set to logic 1, the module operates in Frequency Output Mode.                            |

| 1   | PWM   | Pulse Width Modulation Mode Enable.                                                                                                                                                                                                                                               |

|     |       | This bit enables the PWM function. When enabled, a pulse width modulated signal is output on the CEX1 pin. 8 to 11-bit PWM is used if PWM16 is cleared; 16-bit mode is used if PWM16 is set to logic 1. If the TOG bit is also set, the module operates in Frequency Output Mode. |

| 0   | ECCF  | Capture/Compare Flag Interrupt Enable.                                                                                                                                                                                                                                            |

|     |       | This bit sets the masking of the Capture/Compare Flag (CCF1) interrupt.<br>0: Disable CCF1 interrupts.                                                                                                                                                                            |

|     |       | 1: Enable a Capture/Compare Flag interrupt request when CCF1 is set.                                                                                                                                                                                                              |

# 21. Port I/O (Port 0, Port 1, Port 2, Crossbar, and Port Match)

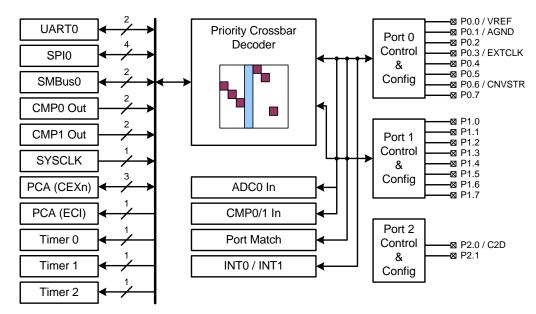

Digital and analog resources on the C8051F85x/86x family are externally available on the device's multipurpose I/O pins. Port pins P0.0-P1.7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources through the crossbar, or assigned to an analog function. Port pins P2.0 and P2.1 can be used as GPIO. Port pin P2.0 is shared with the C2 Interface Data signal (C2D). The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a priority crossbar decoder. Note that the state of a port I/O pin can always be read in the corresponding port latch, regardless of the crossbar settings.

The crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 21.2 and Figure 21.3). The registers XBR0, XBR1 and XBR2 are used to select internal digital functions.

The port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Additionally, each bank of port pins (P0, P1, and P2) has two selectable drive strength settings.

Figure 21.1. Port I/O Functional Block Diagram

## 21.1. General Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O crossbar using the Port Skip registers (PnSKIP).

- 4. Assign port pins to desired peripherals.

- 5. Enable the crossbar (XBARE = '1').

All port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a '1' indicates a digital input, and a '0' indicates an analog input. All pins default to digital inputs on reset.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMDOUT). Each port output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is '0', a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a '0' to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR2 to '1' enables the crossbar. Until the crossbar is enabled, the external pins remain as standard port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, Silicon Labs provides configuration utility software to determine the port I/O pin-assignments based on the crossbar register settings.

The crossbar must be enabled to use port pins as standard port I/O in output mode. Port output drivers of all crossbar pins are disabled whenever the crossbar is disabled.

# Register 21.5. P0MASK: Port 0 Mask

| Bit               | 7      | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|--------|-----------------|---|---|---|---|---|---|--|--|

| Name              | POMASK |                 |   |   |   |   |   |   |  |  |

| Туре              | RW     |                 |   |   |   |   |   |   |  |  |

| Reset             | 0      | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

| SFR Address: 0xFE |        |                 |   |   |   |   |   |   |  |  |

## Table 21.8. P0MASK Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MASK | Port 0 Mask Value.                                                                                                                                                                                |

|     |        | Selects P0 pins to be compared to the corresponding bits in P0MAT.<br>0: P0.x pin logic value is ignored and will cause a port mismatch event.<br>1: P0.x pin logic value is compared to P0MAT.x. |

## 22.11. Supply Monitor Control Registers

| Bit   | 7     | 6       | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---------|----------|---|---|---|---|---|

| Name  | VDMEN | VDDSTAT | Reserved |   |   |   |   |   |

| Туре  | RW    | R       |          | R |   |   |   |   |

| Reset | Х     | Х       | Х        | Х | Х | Х | Х | Х |

## Register 22.2. VDM0CN: Supply Monitor Control

SFR Address: 0xFF

# Table 22.2. VDM0CN Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN    | Supply Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |          | This bit turns the supply monitor circuit on/off. The supply monitor cannot generate sys-<br>tem resets until it is also selected as a reset source in register RSTSRC. Selecting the<br>supply monitor as a reset source before it has stabilized may generate a system reset. In<br>systems where this reset would be undesirable, a delay should be introduced between<br>enabling the supply monitor and selecting it as a reset source.<br>0: Supply Monitor Disabled.<br>1: Supply Monitor Enabled. |

| 6   | VDDSTAT  | Supply Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          | <ul> <li>This bit indicates the current power supply status (supply monitor output).</li> <li>0: V<sub>DD</sub> is at or below the supply monitor threshold.</li> <li>1: V<sub>DD</sub> is above the supply monitor threshold.</li> </ul>                                                                                                                                                                                                                                                                 |

| 5:0 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bit     | Set by Hardware When:                                                                                                                                                                                                                                                                                            | Cleared by Hardware When:                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed (only when<br/>hardware ACK is not enabled).</li> </ul>                                                                                                                                                                                | <ul> <li>After each ACK cycle.</li> </ul>                                 |

| ARBLOST | <ul> <li>A repeated START is detected as a<br/>MASTER when STA is low (unwanted<br/>repeated START).</li> <li>SCL is sensed low while attempting to<br/>generate a STOP or repeated START<br/>condition.</li> <li>SDA is sensed low while transmitting a 1</li> </ul>                                            | <ul> <li>Each time SIn is cleared.</li> </ul>                             |

| ACK     | <ul> <li>(excluding ACK bits).</li> <li>The incoming ACK value is low<br/>(ACKNOWLEDGE).</li> </ul>                                                                                                                                                                                                              | <ul> <li>The incoming ACK value is high<br/>(NOT ACKNOWLEDGE).</li> </ul> |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an ACK/<br/>NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a<br/>slave address + R/W has been received.</li> <li>A STOP has been received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                          |

#### Table 24.3. Sources for Hardware Changes to SMB0CN (Continued)

#### 24.4.5. Hardware Slave Address Recognition

The SMBus hardware has the capability to automatically recognize incoming slave addresses and send an ACK without software intervention. Automatic slave address recognition is enabled by setting the EHACK bit in register SMB0ADM to 1. This will enable both automatic slave address recognition and automatic hardware ACK generation for received bytes (as a master or slave). More detail on automatic hardware ACK generation can be found in Section 24.4.4.2.

The registers used to define which address(es) are recognized by the hardware are the SMBus Slave Address register and the SMBus Slave Address Mask register. A single address or range of addresses (including the General Call Address 0x00) can be specified using these two registers. The most-significant seven bits of the two registers are used to define which addresses will be ACKed. A 1 in a bit of the slave address mask SLVM enables a comparison between the received slave address and the hardware's slave address SLV for that bit. A 0 in a bit of the slave address mask means that bit will be treated as a "don't care" for comparison purposes. In this case, either a 1 or a 0 value are acceptable on the incoming slave address. Additionally, if the GC bit in register SMB0ADR is set to 1, hardware will recognize the General Call Address (0x00). Table 24.4 shows some example parameter settings and the slave addresses that will be recognized by hardware under those conditions.

| Hardware Slave Address<br>SLV | Slave Address Mask<br>SLVM | GC bit | Slave Addresses Recognized by Hardware |

|-------------------------------|----------------------------|--------|----------------------------------------|

| 0x34                          | 0x7F                       | 0      | 0x34                                   |

| 0x34                          | 0x7F                       | 1      | 0x34, 0x00 (General Call)              |

| 0x34                          | 0x7E                       | 0      | 0x34, 0x35                             |

#### Table 24.4. Hardware Address Recognition Examples (EHACK = 1)

|                   | Valu             | es F  | Rea     | d   |                                                                                       |                                                        |     | lues<br>Vrite |                                                                  | tus<br>ected                                               |   |                                                       |                                                            |      |   |   |      |

|-------------------|------------------|-------|---------|-----|---------------------------------------------------------------------------------------|--------------------------------------------------------|-----|---------------|------------------------------------------------------------------|------------------------------------------------------------|---|-------------------------------------------------------|------------------------------------------------------------|------|---|---|------|

| Mode              | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                                   | Typical Response Options                               | STA | STO           | ACK                                                              | Next Status<br>Vector Expected                             |   |                                                       |                                                            |      |   |   |      |

| -                 |                  | 0     | 0       | 0   | A slave byte was transmitted; NACK received.                                          | No action required (expecting STOP condition).         | 0   | 0             | Х                                                                | 0001                                                       |   |                                                       |                                                            |      |   |   |      |

| smitte            | 0100             | 0     | 0       | 1   | A slave byte was transmitted; ACK Load SMB0DAT with next data byte to transmit.       |                                                        |     |               |                                                                  | 0100                                                       |   |                                                       |                                                            |      |   |   |      |

| Slave Transmitter |                  | 0     | 1       | х   | A Slave byte was transmitted; error detected.                                         | No action required (expecting Master to end transfer). | 0   | 0             | Х                                                                | 0001                                                       |   |                                                       |                                                            |      |   |   |      |

| Slav              | 0101             | 0     | х       | х   | An illegal STOP or bus error was detected while a Slave Transmission was in progress. | 0                                                      | 0   | Х             | —                                                                |                                                            |   |                                                       |                                                            |      |   |   |      |

|                   |                  |       |         |     |                                                                                       | If Write, Acknowledge received address                 | 0   | 0             | 1                                                                | 0000                                                       |   |                                                       |                                                            |      |   |   |      |

|                   |                  | 1 0 X |         | х   | Х                                                                                     | Х                                                      | Х   | Х             | Х                                                                | х                                                          | X | A slave address + R/W was received;<br>ACK requested. | If Read, Load SMB0DAT with data byte; ACK received address | 0    | 0 | 1 | 0100 |

|                   |                  |       |         |     |                                                                                       | NACK received address.                                 | 0   | 0             | 0                                                                | _                                                          |   |                                                       |                                                            |      |   |   |      |

|                   | 0010             |       |         |     |                                                                                       | If Write, Acknowledge received address                 | 0   | 0             | 1                                                                | 0000                                                       |   |                                                       |                                                            |      |   |   |      |

| iver              |                  | 1     | 1 X     |     | 1 X                                                                                   | 1                                                      | 1   | x             | Lost arbitration as master; slave<br>address + R/W received; ACK | If Read, Load SMB0DAT with data byte; ACK received address | 0 | 0                                                     | 1                                                          | 0100 |   |   |      |

| sece              |                  |       |         |     |                                                                                       | NACK received address.                                 | 0   | 0             | 0                                                                | _                                                          |   |                                                       |                                                            |      |   |   |      |

| Slave Receiver    |                  |       |         |     |                                                                                       | Reschedule failed transfer;<br>NACK received address.  | 1   | 0             | 0                                                                | 1110                                                       |   |                                                       |                                                            |      |   |   |      |

|                   | 0001             | 0     | 0       | х   | A STOP was detected while addressed<br>as a Slave Transmitter or Slave<br>Receiver.   | Clear STO.                                             | 0   | 0             | Х                                                                |                                                            |   |                                                       |                                                            |      |   |   |      |

|                   |                  | 1     | 1       | х   | Lost arbitration while attempting a STOP.                                             | No action required (transfer complete/aborted).        | 0   | 0             | 0                                                                | —                                                          |   |                                                       |                                                            |      |   |   |      |

|                   | 0000             | 1     | 0       | x   | A slave byte was received; ACK requested.                                             | Acknowledge received byte;<br>Read SMB0DAT.            | 0   | 0             | 1                                                                | 0000                                                       |   |                                                       |                                                            |      |   |   |      |

|                   |                  |       |         |     |                                                                                       | NACK received byte.                                    | 0   | 0             | 0                                                                | -                                                          |   |                                                       |                                                            |      |   |   |      |

## Table 24.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (Continued)

| Bit | Name  | Function                                                                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SMBCS | SMBus0 Clock Source Selection.                                                                                                                                                                                                                                                 |

|     |       | These two bits select the SMBus0 clock source, which is used to generate the SMBus0<br>bit rate. See the SMBus clock timing section for additional details.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow |

## Table 24.7. SMB0CF Register Bit Descriptions

# Register 25.3. TMOD: Timer 0/1 Mode

| Bit   | 7     | 6   | 5  | 4  | 3     | 2   | 1   | 0 |

|-------|-------|-----|----|----|-------|-----|-----|---|

| Name  | GATE1 | CT1 | T1 | IM | GATE0 | CT0 | ТОМ |   |

| Туре  | RW    | RW  | RW |    | RW    | RW  | R   | W |

| Reset | 0     | 0   | 0  | 0  | 0     | 0   | 0   | 0 |

# Table 25.5. TMOD Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE1 | Timer 1 Gate Control.0: Timer 1 enabled when TR1 = 1 irrespective of INT1 logic level.1: Timer 1 enabled only when TR1 = 1 and INT1 is active as defined by bit IN1PL in register IT01CF.                                                  |

| 6   | CT1   | Counter/Timer 1 Select.0: Timer Mode. Timer 1 increments on the clock defined by T1M in the CKCON register.1: Counter Mode. Timer 1 increments on high-to-low transitions of an external pin (T1).                                         |

| 5:4 | T1M   | Timer 1 Mode Select.These bits select the Timer 1 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Timer 1 Inactive                              |

| 3   | GATE0 | Timer 0 Gate Control.0: Timer 0 enabled when TR0 = 1 irrespective of INT0 logic level.1: Timer 0 enabled only when TR0 = 1 and INT0 is active as defined by bit IN0PL in register IT01CF.                                                  |

| 2   | СТО   | <ul> <li>Counter/Timer 0 Select.</li> <li>0: Timer Mode. Timer 0 increments on the clock defined by T0M in the CKCON register.</li> <li>1: Counter Mode. Timer 0 increments on high-to-low transitions of an external pin (T0).</li> </ul> |

| 1:0 | ТОМ   | Timer 0 Mode Select.These bits select the Timer 0 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Two 8-bit Counter/Timers                      |

## Table 25.10. TMR2CN Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | T2XCLK | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |        | <ul> <li>This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.</li> <li>0: Timer 2 clock is the system clock divided by 12.</li> <li>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK).</li> </ul> |

# Register 25.14. TMR3RLL: Timer 3 Reload Low Byte

| Bit               | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|---------|---|---|---|---|---|---|---|

| Name              | TMR3RLL |   |   |   |   |   |   |   |

| Туре              | RW      |   |   |   |   |   |   |   |

| Reset             | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0x92 |         |   |   |   |   |   |   |   |

## Table 25.16. TMR3RLL Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3RLL | Timer 3 Reload Low Byte.                                                                                                                                                                    |

|     |         | When operating in one of the auto-reload modes, TMR3RLL holds the reload value for the low byte of Timer 3 (TMR3L). When operating in capture mode, TMR3RLL is the captured value of TMR3L. |

## 28.2. Temperature Sensor Offset and Slope

The temperature sensor slope and offset characteristics of Revision B devices are different than the slope and offset characteristics of Revision C devices. The differences are:

| Parameter  | Symbol           | Test Condition        | Min | Тур  | Max | Unit  |

|------------|------------------|-----------------------|-----|------|-----|-------|

| Revision B |                  |                       |     |      |     |       |

| Offset     | V <sub>OFF</sub> | T <sub>A</sub> = 0 °C | _   | 713  | —   | mV    |

| Slope      | М                |                       |     | 2.67 |     | mV/°C |

| Revision C |                  |                       |     |      |     |       |

| Offset     | V <sub>OFF</sub> | $T_A = 0 \ ^{\circ}C$ | _   | 757  | _   | mV    |

| Slope      | М                |                       |     | 2.85 |     | mV/°C |

Firmware that uses the slope and offset of the temperature sensor to calculate the temperature from the sensor ADC reading can detect the revision of the device by reading the REVID register and adjust the slope and offset calculations based on the result. A REVID value of 0x01 indicates a Revision B device, and a REVID value of 0x02 indicates a Revision C device.

#### 28.3. Flash Endurance

The flash endurance, or number of times the flash may be written and erased, on some Revision B devices may be lower than expected. Table 1.4 specifies a minimum Endurance (Write/Erase Cycles) as 20000, but some Revision B devices may support a minimum of ~5000 cycles.

#### 28.4. Latch-Up Performance

Pulling the device pins below ground and drawing significant current (~3.5 mA) can cause a Power-On Reset event with Revision B devices. Some pins, like P0.0 and P0.1, are more susceptible to this behavior than others. This behavior is outside normal operating parameters and would typically be seen during latch-up or ESD performance testing.

#### 28.5. Unique Identifier

Revision B devices do not implement the unique identifier described in "Device Identification and Unique Identifier" on page 68.