Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 15                                                                |

| Program Memory Size        | 2KB (2K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | A/D 15x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                              |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f852-c-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

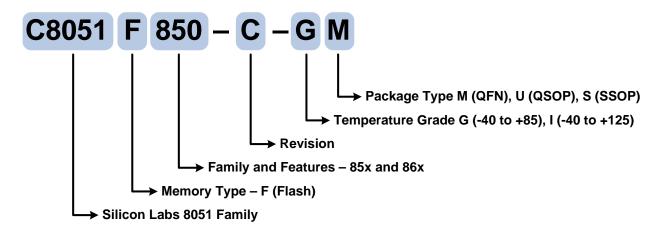

# 4. Ordering Information

#### Figure 4.1. C8051F85x/86x Part Numbering

All C8051F85x/86x family members have the following features:

- CIP-51 Core running up to 25 MHz

- Two Internal Oscillators (24.5 MHz and 80 kHz)

- I2C/SMBus

- SPI

- UART

- 3-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- 4 16-bit Timers

- 2 Analog Comparators

- 16-bit CRC Unit

In addition to these features, each part number in the C8051F85x/86x family has a set of features that vary across the product line. The product selection guide in Table 4.1 shows the features available on each family member.

All devices in Table 4.1 are also available in an industrial version. For the industrial version, the -G in the ordering part number is replaced with -I. For example, the industrial version of the C8051F850-C-GM is the C8051F850-C-IM.

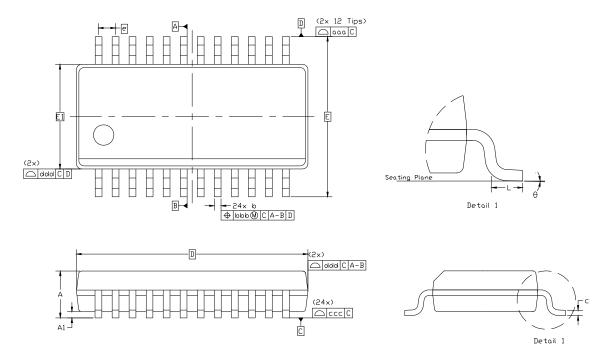

## 5. **QSOP-24** Package Specifications

Figure 5.1. QSOP-24 Package Drawing

| Min      | Mana     |      |  |           |           |      |      |

|----------|----------|------|--|-----------|-----------|------|------|

|          | Nom      | Max  |  | Dimension | Min       | Nom  | Мах  |

| _        | _        | 1.75 |  | е         | 0.635 BSC |      |      |

| 0.10     | _        | 0.25 |  | L         | 0.40      |      | 1.27 |

| 0.20     | _        | 0.30 |  | θ         | 0°        |      | 8º   |

| 0.10     | _        | 0.25 |  | aaa       | 0.20      |      |      |

|          | 8.65 BSC |      |  | bbb       |           | 0.18 |      |

| 6.00 BSC |          |      |  | CCC       |           | 0.10 |      |

| 3.90 BSC |          |      |  | ddd       |           | 0.10 |      |

|          |          |      |  |           |           |      |      |

### Table 5.1. QSOP-24 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| Symbol | Millim   | neters | Symbol | Millim | neters |

|--------|----------|--------|--------|--------|--------|

|        | Min      | Max    |        | Min    | Max    |

| D      | 2.71     | REF    | GE     | 2.10   | _      |

| D2     | 1.60     | 1.80   | W      | _      | 0.34   |

| е      | 0.50     | BSC    | Х      | —      | 0.28   |

| E      | 2.71     | REF    | Y      | 0.61   | REF    |

| E2     | 1.60     | 1.80   | ZE     | —      | 3.31   |

| f      | 2.53 BSC |        | ZD     | —      | 3.31   |

| GD     | 2.10     | —      |        |        |        |

#### Table 6.2. QFN-20 Landing Diagram Dimensions

#### Notes: General

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Notes: Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Notes: Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- **4.** A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides approximately 70% solder paste coverage on the pad, which is optimum to assure correct component stand-off.

#### Notes: Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 10. Flash Memory

On-chip, re-programmable flash memory is included for program code and non-volatile data storage. The flash memory is organized in 512-byte pages. It can be erased and written through the C2 interface or from firmware by overloading the MOVX instruction. Any individual byte in flash memory must only be written once between page erase operations.

### **10.1. Security Options**

The CIP-51 provides security options to protect the flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the flash memory from accidental modification by software. PSWE must be explicitly set to '1' before software can modify the flash memory; both PSWE and PSEE must be set to '1' before software can erase flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located in flash user space offers protection of the flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. See Section "8. Memory Organization" on page 52 for the location of the security byte. The flash security mechanism allows the user to lock *n* 512-byte flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where *n* is the 1's complement number represented by the Security Lock Byte. Note that the page containing the flash Security Lock Byte is unlocked when no other flash pages are locked (all bits of the Lock Byte are '1') and locked when any other flash pages are locked (any bit of the Lock Byte is '0'). An example is shown in Figure 10.1.

| Security Lock Byte: | 11111101b                                  |

|---------------------|--------------------------------------------|

| 1s Complement:      | 00000010b                                  |

| Flash pages locked: | 3 (First two flash pages + Lock Byte Page) |

#### Figure 10.1. Security Byte Decoding

The level of flash security depends on the flash access method. The three flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 10.1 summarizes the flash security features of the C8051F85x/86x devices.

| Action                                                             | C2 Debug      | User Firmware executing from: |               |  |

|--------------------------------------------------------------------|---------------|-------------------------------|---------------|--|

|                                                                    | Interface     | an unlocked page              | a locked page |  |

| Read, Write or Erase unlocked pages (except page with Lock Byte)   | Permitted     | Permitted                     | Permitted     |  |

| Read, Write or Erase locked pages (except page with Lock Byte)     | Not Permitted | Flash Error Reset             | Permitted     |  |

| Read or Write page containing Lock Byte (if no pages are locked)   | Permitted     | Permitted                     | N/A           |  |

| Read or Write page containing Lock Byte<br>(if any page is locked) | Not Permitted | Flash Error Reset             | Permitted     |  |

#### Table 10.1. Flash Security Summary

# 11. Device Identification and Unique Identifier

The C8051F85x/86x has SFRs that identify the device family, derivative, and revision. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically change functionality to suit the capabilities of that MCU.

In addition to the device identification registers, a 32-bit unique identifier (UID) is pre-programmed into all Revision C and later devices. The UID resides in the last four bytes of XRAM (C8051F850/1/3/4 and C8051F860/1/3/4) or RAM (C8051F852/5 and C8051F862/5). For devices with the UID in RAM, the UID can be read by firmware using indirect data accesses. For devices with the UID in XRAM, the UID can be read by firmware using MOVX instructions. The UID can also be read through the debug port for all devices.

Firmware can overwrite the UID during normal operation, and the bytes in memory will be automatically reinitialized with the UID value after any device reset. Firmware using this area of memory should always initialize the memory to a known value, as any previous data stored at these locations will be overwritten and not retained through a reset.

| Device                 | Memory Segment | Addresses                                  |  |  |  |

|------------------------|----------------|--------------------------------------------|--|--|--|

| C8051F850<br>C8051F851 |                |                                            |  |  |  |

| C8051F853              |                |                                            |  |  |  |

| C8051F854<br>C8051F860 | XRAM           | (MSB) 0x00FF, 0x00FE, 0x00FD, 0x00FC (LSB) |  |  |  |

| C8051F861<br>C8051F863 |                |                                            |  |  |  |

| C8051F864              |                |                                            |  |  |  |

| C8051F852              |                |                                            |  |  |  |

| C8051F855<br>C8051F862 | RAM (indirect) | (MSB) 0xFF, 0xFE, 0xFD, 0xFC (LSB)         |  |  |  |

| C8051F865              |                |                                            |  |  |  |

Table 11.1. UID Implementation Information

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flags                                                              | Bit addressable? | Cleared by HW? | Enable Flag     |

|-------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|-----------------|

| Reset                         | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always Enabled  |

| External Interrupt 0 (INT0)   | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)      |

| Timer 0 Overflow              | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)      |

| External Interrupt 1 (INT1)   | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)      |

| Timer 1 Overflow              | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)      |

| UART0                         | 0x0023              | 4                 | RI (SCON0.0)<br>TI (SCON0.1)                                               | Y                | Ν              | ES0 (IE.4)      |

| Timer 2 Overflow              | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | Ν              | ET2 (IE.5)      |

| SPI0                          | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0 (IE.6)    |

| SMB0                          | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | Ν              | ESMB0 (EIE1.0)  |

| Port Match                    | 0x0043              | 8                 | None                                                                       | N/A              | N/A            | EMAT (EIE1.1)   |

| ADC0 Window Compare           | 0x004B              | 9                 | ADWINT (ADC0CN.3)                                                          | Y                | Ν              | EWADC0 (EIE1.2) |

| ADC0 Conversion Complete      | 0x0053              | 10                | ADINT (ADC0CN.5)                                                           | Y                | Ν              | EADC0 (EIE1.3)  |

| Programmable Counter<br>Array | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y                | N              | EPCA0 (EIE1.4)  |

| Comparator0                   | 0x0063              | 12                | CPFIF (CPT0CN.4)<br>CPRIF (CPT0CN.5)                                       | Ν                | Ν              | ECP0 (EIE1.5)   |

| Comparator1                   | 0x006B              | 13                | CPFIF (CPT1CN.4)<br>CPRIF (CPT1CN.5)                                       | N                | N              | ECP1 (EIE1.6)   |

| Timer 3 Overflow              | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3 (EIE1.7)    |

Table 12.1. Interrupt Summary

## Register 12.3. EIE1: Extended Interrupt Enable 1

| Bit               | 7   | 6    | 5    | 4     | 3     | 2      | 1    | 0     |  |  |

|-------------------|-----|------|------|-------|-------|--------|------|-------|--|--|

| Name              | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | EMAT | ESMB0 |  |  |

| Туре              | RW  | RW   | RW   | RW    | RW    | RW     | RW   | RW    |  |  |

| Reset             | 0   | 0    | 0    | 0     | 0     | 0      | 0    | 0     |  |  |

| SFR Address: 0xE6 |     |      |      |       |       |        |      |       |  |  |

## Table 12.4. EIE1 Register Bit Descriptions

| Bit | Name   | Function                                                                                                                              |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ET3    | Enable Timer 3 Interrupt.                                                                                                             |

|     |        | This bit sets the masking of the Timer 3 interrupt.                                                                                   |

|     |        | 0: Disable Timer 3 interrupts.                                                                                                        |

|     |        | 1: Enable interrupt requests generated by the TF3L or TF3H flags.                                                                     |

| 6   | ECP1   | Enable Comparator1 (CP1) Interrupt.                                                                                                   |

|     |        | This bit sets the masking of the CP1 interrupt.                                                                                       |

|     |        | 0: Disable CP1 interrupts.                                                                                                            |

|     |        | 1: Enable interrupt requests generated by the comparator 1 CPRIF or CPFIF flags.                                                      |

| 5   | ECP0   | Enable Comparator0 (CP0) Interrupt.                                                                                                   |

|     |        | This bit sets the masking of the CP0 interrupt.                                                                                       |

|     |        | <ul><li>0: Disable CP0 interrupts.</li><li>1: Enable interrupt requests generated by the comparator 0 CPRIF or CPFIF flags.</li></ul> |

|     |        |                                                                                                                                       |

| 4   | EPCA0  | Enable Programmable Counter Array (PCA0) Interrupt.                                                                                   |

|     |        | This bit sets the masking of the PCA0 interrupts.<br>0: Disable all PCA0 interrupts.                                                  |

|     |        | 1: Enable interrupt requests generated by PCA0.                                                                                       |

| 3   | EADC0  | Enable ADC0 Conversion Complete Interrupt.                                                                                            |

| 3   | EADCO  | This bit sets the masking of the ADC0 Conversion Complete interrupt.                                                                  |

|     |        | 0: Disable ADC0 Conversion Complete interrupt.                                                                                        |

|     |        | 1: Enable interrupt requests generated by the ADINT flag.                                                                             |

| 2   | EWADC0 | Enable Window Comparison ADC0 Interrupt.                                                                                              |

|     |        | This bit sets the masking of ADC0 Window Comparison interrupt.                                                                        |

|     |        | 0: Disable ADC0 Window Comparison interrupt.                                                                                          |

|     |        | 1: Enable interrupt requests generated by ADC0 Window Compare flag (ADWINT).                                                          |

| 1   | EMAT   | Enable Port Match Interrupts.                                                                                                         |

|     |        | This bit sets the masking of the Port Match Event interrupt.                                                                          |

|     |        | 0: Disable all Port Match interrupts.                                                                                                 |

|     |        | 1: Enable interrupt requests generated by a Port Match.                                                                               |

## Register 14.12. ADC0LTL: ADC0 Less-Than Low Byte

| Bit     | 7                 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------------|-----------------|---|---|---|---|---|---|--|--|

| Name    | ADCOLTL           |                 |   |   |   |   |   |   |  |  |

| Туре    | RW                |                 |   |   |   |   |   |   |  |  |

| Reset   | 0                 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

| SFR Add | SFR Address: 0xC5 |                 |   |   |   |   |   |   |  |  |

### Table 14.15. ADC0LTL Register Bit Descriptions

| Bit      | Name                                                      | Function                                                                |  |  |  |  |  |

|----------|-----------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| 7:0      | ADC0LTL                                                   | Less-Than Low Byte.                                                     |  |  |  |  |  |

|          |                                                           | Least Significant Byte of the 16-bit Less-Than window compare register. |  |  |  |  |  |

| Note: In | Note: In 8-bit mode, this register should be set to 0x00. |                                                                         |  |  |  |  |  |

## Register 18.5. CRC0CNT: CRC0 Automatic Flash Sector Count

| Bit               | 7     | 6    | 5     | 4         | 3 | 2  | 1 | 0 |  |  |

|-------------------|-------|------|-------|-----------|---|----|---|---|--|--|

| Name              | CRCDN | Rese | erved | CRCCNT    |   |    |   |   |  |  |

| Туре              | R     | F    | २     |           |   | RW |   |   |  |  |

| Reset             | 1     | 0    | 0     | 0 0 0 0 0 |   |    |   |   |  |  |

| SFR Address: 0xD3 |       |      |       |           |   |    |   |   |  |  |

### Table 18.6. CRC0CNT Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                            |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CRCDN    | Automatic CRC Calculation Complete.                                                                                                                                                                                                                 |

|     |          | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                            |

| 6:5 | Reserved | Must write reset value.                                                                                                                                                                                                                             |

| 4:0 | CRCCNT   | Automatic CRC Calculation Block Count.                                                                                                                                                                                                              |

|     |          | These bits specify the number of flash blocks to include in an automatic CRC calculation.<br>The last address of the last flash block included in the automatic CRC calculation is<br>(CRCST+CRCCNT) x Block Size - 1. The block size is 256 bytes. |

## Register 20.5. PCA0CPM0: PCA Capture/Compare Mode

| Bit     | 7                 | 6    | 5    | 4    | 3   | 2   | 1   | 0    |

|---------|-------------------|------|------|------|-----|-----|-----|------|

| Name    | PWM16             | ECOM | CAPP | CAPN | MAT | TOG | PWM | ECCF |

| Туре    | RW                | RW   | RW   | RW   | RW  | RW  | RW  | RW   |

| Reset   | 0                 | 0    | 0    | 0    | 0   | 0   | 0   | 0    |

| SFR Add | SFR Address: 0xDA |      |      |      |     |     |     |      |

#### Table 20.7. PCA0CPM0 Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWM16 | 16-bit Pulse Width Modulation Enable.                                                                                                                                                                                                                                             |

|     |       | <ul><li>This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.</li><li>0: 8 to 11-bit PWM selected.</li><li>1: 16-bit PWM selected.</li></ul>                                                                                                                  |

| 6   | ECOM  | Comparator Function Enable.                                                                                                                                                                                                                                                       |

|     |       | This bit enables the comparator function.                                                                                                                                                                                                                                         |

| 5   | CAPP  | Capture Positive Function Enable.                                                                                                                                                                                                                                                 |

|     |       | This bit enables the positive edge capture capability.                                                                                                                                                                                                                            |

| 4   | CAPN  | Capture Negative Function Enable.                                                                                                                                                                                                                                                 |

|     |       | This bit enables the negative edge capture capability.                                                                                                                                                                                                                            |

| 3   | MAT   | Match Function Enable.                                                                                                                                                                                                                                                            |

|     |       | This bit enables the match function. When enabled, matches of the PCA counter with a module's capture/compare register cause the CCF0 bit in the PCA0MD register to be set to logic 1.                                                                                            |

| 2   | TOG   | Toggle Function Enable.                                                                                                                                                                                                                                                           |

|     |       | This bit enables the toggle function. When enabled, matches of the PCA counter with the capture/compare register cause the logic level on the CEX0 pin to toggle. If the PWM bit is also set to logic 1, the module operates in Frequency Output Mode.                            |

| 1   | PWM   | Pulse Width Modulation Mode Enable.                                                                                                                                                                                                                                               |

|     |       | This bit enables the PWM function. When enabled, a pulse width modulated signal is output on the CEX0 pin. 8 to 11-bit PWM is used if PWM16 is cleared; 16-bit mode is used if PWM16 is set to logic 1. If the TOG bit is also set, the module operates in Frequency Output Mode. |

| 0   | ECCF  | Capture/Compare Flag Interrupt Enable.                                                                                                                                                                                                                                            |

|     |       | This bit sets the masking of the Capture/Compare Flag (CCF0) interrupt.<br>0: Disable CCF0 interrupts.                                                                                                                                                                            |

|     |       | 1: Enable a Capture/Compare Flag interrupt request when CCF0 is set.                                                                                                                                                                                                              |

## Register 21.7. P0: Port 0 Pin Latch

| Bit   | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|---|---|---|---|---|---|---|

| Name  | P0 |   |   |   |   |   |   |   |

| Туре  | RW |   |   |   |   |   |   |   |

| Reset | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

### Table 21.10. P0 Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                                                                     |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0   | Port 0 Data.                                                                                                                                                                                                                 |

|     |      | Writing this register sets the port latch logic value for the associated I/O pins configured as digital I/O.<br>Reading this register returns the logic value at the pin, regardless if it is configured as output or input. |

## Register 21.11. P1MASK: Port 1 Mask

| Bit     | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-------------------|---|---|---|---|---|---|---|

| Name    | P1MASK            |   |   |   |   |   |   |   |

| Туре    | RW                |   |   |   |   |   |   |   |

| Reset   | 0                 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Add | SFR Address: 0xEE |   |   |   |   |   |   |   |

### Table 21.14. P1MASK Register Bit Descriptions

| Bit | Name                                                                                                                                               | Function                                                                                                                                                                                          |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0 | P1MASK                                                                                                                                             | Port 1 Mask Value.                                                                                                                                                                                |  |  |  |  |

|     |                                                                                                                                                    | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.x pin logic value is ignored and will cause a port mismatch event.<br>1: P1.x pin logic value is compared to P1MAT.x. |  |  |  |  |

|     | Note: Port 1 consists of 8 bits (P1.0-P1.7) on QSOP24 packages and 7 bits (P1.0-P1.6) on QFN20 packages and 4 bits (P1.0-P1.3) on SOIC16 packages. |                                                                                                                                                                                                   |  |  |  |  |

### 22.11. Supply Monitor Control Registers

| Bit   | 7     | 6       | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---------|----------|---|---|---|---|---|

| Name  | VDMEN | VDDSTAT | Reserved |   |   |   |   |   |

| Туре  | RW    | R       | R        |   |   |   |   |   |

| Reset | Х     | Х       | Х        | Х | Х | Х | Х | Х |

### Register 22.2. VDM0CN: Supply Monitor Control

SFR Address: 0xFF

# Table 22.2. VDM0CN Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN    | Supply Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |          | This bit turns the supply monitor circuit on/off. The supply monitor cannot generate sys-<br>tem resets until it is also selected as a reset source in register RSTSRC. Selecting the<br>supply monitor as a reset source before it has stabilized may generate a system reset. In<br>systems where this reset would be undesirable, a delay should be introduced between<br>enabling the supply monitor and selecting it as a reset source.<br>0: Supply Monitor Disabled.<br>1: Supply Monitor Enabled. |

| 6   | VDDSTAT  | Supply Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          | <ul> <li>This bit indicates the current power supply status (supply monitor output).</li> <li>0: V<sub>DD</sub> is at or below the supply monitor threshold.</li> <li>1: V<sub>DD</sub> is above the supply monitor threshold.</li> </ul>                                                                                                                                                                                                                                                                 |

| 5:0 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

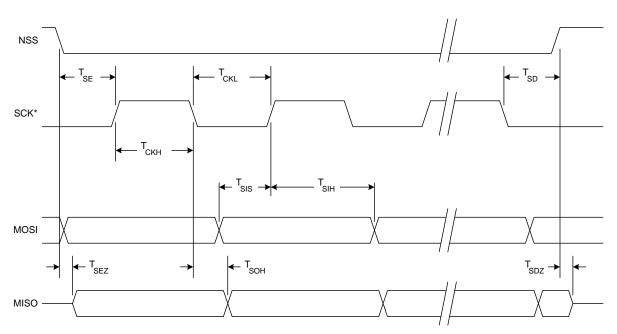

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 23.10. SPI Slave Timing (CKPHA = 0)

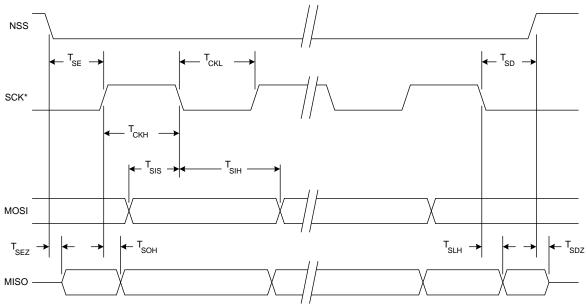

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

#### Figure 23.11. SPI Slave Timing (CKPHA = 1)

minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary for SMBus compliance when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                                | Minimum SDA Setup Time                                                              | Minimum SDA Hold Time |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                      | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup> | 3 system clocks       |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                      | 11 system clocks                                                                    | 12 system clocks      |  |  |  |

| Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgment, the s/<br>w delay occurs between the time SMB0DAT or ACK is written and when SI0 is cleared. Note that if SI is cleared in the<br>same write that defines the outgoing ACK value, s/w delay is zero. |                                                                                     |                       |  |  |  |

#### Table 24.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "24.3.4. SCL Low Timeout" on page 235). The SMBus interface will force the associated timer to reload while SCL is high, and allow the timer to count when SCL is low. The timer interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 24.4).

#### 24.4.2. SMBus Pin Swap

The SMBus peripheral is assigned to pins using the priority crossbar decoder. By default, the SMBus signals are assigned to port pins starting with SDA on the lower-numbered pin, and SCL on the next available pin. The SWAP bit in the SMBTC register can be set to 1 to reverse the order in which the SMBus signals are assigned.

#### 24.4.3. SMBus Timing Control

The SDD field in the SMBTC register is used to restrict the detection of a START condition under certain circumstances. In some systems where there is significant mismatch between the impedance or the capacitance on the SDA and SCL lines, it may be possible for SCL to fall after SDA during an address or data transfer. Such an event can cause a false START detection on the bus. These kind of events are not expected in a standard SMBus or I2C-compliant system. In most systems this parameter should not be adjusted, and it is recommended that it be left at its default value.

By default, if the SCL falling edge is detected after the falling edge of SDA (i.e. one SYSCLK cycle or more), the device will detect this as a START condition. The SDD field is used to increase the amount of hold time that is required between SDA and SCL falling before a START is recognized. An additional 2, 4, or 8 SYSCLKs can be added to prevent false START detection in systems where the bus conditions warrant this.

#### 24.4.4. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information. The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

| Bit | Name  | Function                                                                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SMBCS | SMBus0 Clock Source Selection.                                                                                                                                                                                                                                                 |

|     |       | These two bits select the SMBus0 clock source, which is used to generate the SMBus0<br>bit rate. See the SMBus clock timing section for additional details.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow |

### Table 24.7. SMB0CF Register Bit Descriptions

# 25. Timers (Timer0, Timer1, Timer2 and Timer3)

Each MCU in the C8051F85x/86x family includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timers for timing peripherals or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 are also identical and offer both 16-bit and split 8-bit timer functionality with auto-reload capabilities. Timer 2 and Timer 3 both offer a capture function, but are different in their system-level connections. Timer 2 is capable of performing a capture function on an external signal input routed through the crossbar, while the Timer 3 capture is dedicated to the low-frequency oscillator output. Table 25.1 summarizes the modes available to each timer.

| Timer 0 and Timer 1 Modes                  | Timer 2 Modes                     | Timer 3 Modes                     |

|--------------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                       | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                       | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |

| 8-bit counter/timer with auto-reload       | Input pin capture                 | Low-frequency oscillator capture  |

| Two 8-bit counter/timers<br>(Timer 0 only) |                                   |                                   |

#### Table 25.1. Timer Modes

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked.

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it must be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

All four timers are capable of clocking other peripherals and triggering events in the system. The individual peripherals select which timer to use for their respective functions. Table 25.2 summarizes the peripheral connections for each timer. Note that the Timer 2 and Timer 3 high overflows apply to the full timer when operating in 16-bit mode or the high-byte timer when operating in 8-bit split mode.

| Table 25.2. Timer Peripheral | Clocking / Event Triggering |

|------------------------------|-----------------------------|

|------------------------------|-----------------------------|

| Function               | T0<br>Overflow | T1<br>Overflow | T2 High<br>Overflow | T2 Low<br>Overflow | T3 High<br>Overflow | T3 Low<br>Overflow |

|------------------------|----------------|----------------|---------------------|--------------------|---------------------|--------------------|

| UART0 Baud Rate        |                | Х              |                     |                    |                     |                    |

| SMBus0 Clock Rate      | Х              | Х              | Х                   | Х                  |                     |                    |

| SMBus0 SCL Low Timeout |                |                |                     |                    | Х                   |                    |

| PCA0 Clock             | Х              |                |                     |                    |                     |                    |

## Register 25.7. TH1: Timer 1 High Byte

| Bit               | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|-----|---|---|---|---|---|---|---|

| Name              | TH1 |   |   |   |   |   |   |   |

| Туре              | RW  |   |   |   |   |   |   |   |

| Reset             | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0x8D |     |   |   |   |   |   |   |   |

## Table 25.9. TH1 Register Bit Descriptions

| Bit | Name | Function                                                 |  |  |  |

|-----|------|----------------------------------------------------------|--|--|--|

| 7:0 | TH1  | Timer 1 High Byte.                                       |  |  |  |

|     |      | The TH1 register is the high byte of the 16-bit Timer 1. |  |  |  |

## Register 25.12. TMR2H: Timer 2 High Byte

| Bit               | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|-------|---|---|---|---|---|---|---|

| Name              | TMR2H |   |   |   |   |   |   |   |

| Туре              | RW    |   |   |   |   |   |   |   |

| Reset             | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0xCD |       |   |   |   |   |   |   |   |

### Table 25.14. TMR2H Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                        |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H | Timer 2 High Byte.                                                                                                                              |

|     |       | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-bit mode, TMR2H contains the 8-bit high byte timer value. |

## 28. Revision-Specific Behavior

C8051F85x/86x Revision B devices have differences from Revision C devices:

- Temperature Sensor offset and slope

- Flash endurance

- Latch-up performance

- Unique Identifier

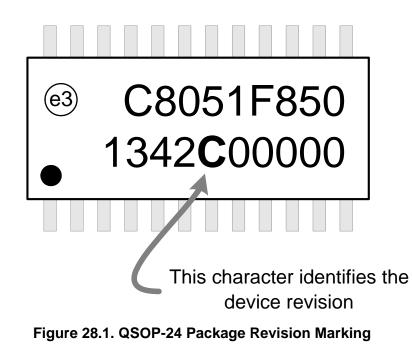

#### 28.1. Revision Identification

The Lot ID Code on the top side of the device package can be used for decoding device revision information. Figure 28.1, Figure 28.2, and Figure 28.3 show how to find the Lot ID Code on the top side of the device package.

Firmware can distinguish between a Revision B and Revision C device using the value of the REVID register described in "Device Identification and Unique Identifier" on page 68.