# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status     Active       Core Processor     8051                        |  |

|--------------------------------------------------------------------------------|--|

| Core Processor 8051                                                            |  |

|                                                                                |  |

| Core Size 8-Bit                                                                |  |

| Speed 25MHz                                                                    |  |

| Connectivity I <sup>2</sup> C, SPI, UART/USART                                 |  |

| Peripherals Brown-out Detect/Reset, POR, PWM, WDT                              |  |

| Number of I/O 16                                                               |  |

| Program Memory Size 2KB (2K x 8)                                               |  |

| Program Memory Type FLASH                                                      |  |

| EEPROM Size -                                                                  |  |

| RAM Size 256 x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd)2.2V ~ 3.6V                                          |  |

| Data Converters A/D 16x12b                                                     |  |

| Oscillator Type Internal                                                       |  |

| Operating Temperature -40°C ~ 85°C (TA)                                        |  |

| Mounting Type Surface Mount                                                    |  |

| Package / Case24-SSOP (0.154", 3.90mm Width)                                   |  |

| Supplier Device Package 24-QSOP                                                |  |

| Purchase URL https://www.e-xfl.com/product-detail/silicon-labs/c8051f852-c-gur |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Туре          | Pin Numbers   | Crossbar Capability | Additional Digital Functions | Analog Functions |

|----------|---------------|---------------|---------------------|------------------------------|------------------|

| N/C      | No Connection | 1<br>13<br>24 |                     |                              |                  |

### Table 3.1. Pin Definitions for C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU

# 3.2. C8051F850/1/2/3/4/5 QFN20 Pin Definitions

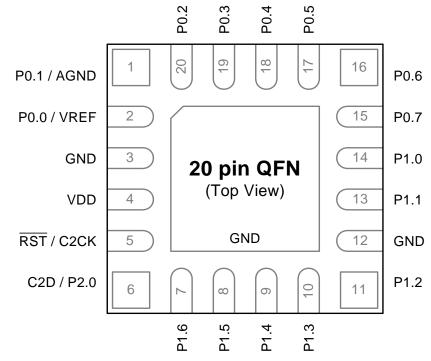

Figure 3.2. C8051F850/1/2/3/4/5-GM and C8051F850/1/2/3/4/5-IM Pinout

| Pin Name      | Туре                                 | Pin Numbers       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|--------------------------------------|-------------------|---------------------|------------------------------|------------------|

| GND           | Ground                               | Center<br>3<br>12 |                     |                              |                  |

| VDD           | Power                                | 4                 |                     |                              |                  |

| RST /<br>C2CK | Active-low Reset /<br>C2 Debug Clock | 5                 |                     |                              |                  |

| Pin Name      | Туре                            | Pin Numbers | Crossbar Capability | Additional Digital Functions | Analog Functions            |

|---------------|---------------------------------|-------------|---------------------|------------------------------|-----------------------------|

| P1.1          | Standard I/O                    | 10          | Yes                 | P1MAT.1                      | ADC0.9<br>CP1P.3<br>CP1N.3  |

| P1.2          | Standard I/O                    | 9           | Yes                 | P1MAT.2                      | ADC0.10<br>CP1P.4<br>CP1N.4 |

| P1.3          | Standard I/O                    | 8           | Yes                 | P1MAT.3                      | ADC0.11<br>CP1P.5<br>CP1N.5 |

| P2.0 /<br>C2D | Standard I/O /<br>C2 Debug Data | 7           |                     |                              |                             |

### Table 3.3. Pin Definitions for C8051F860/1/2/3/4/5-GS and C8051F860/1/2/3/4/5-IS

# 4. Ordering Information

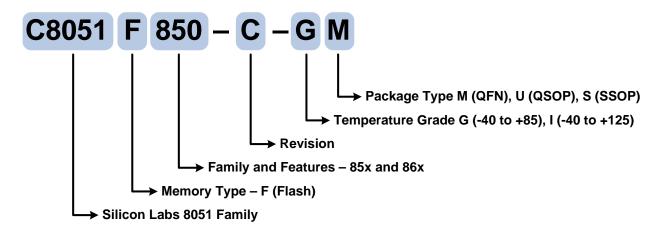

### Figure 4.1. C8051F85x/86x Part Numbering

All C8051F85x/86x family members have the following features:

- CIP-51 Core running up to 25 MHz

- Two Internal Oscillators (24.5 MHz and 80 kHz)

- I2C/SMBus

- SPI

- UART

- 3-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- 4 16-bit Timers

- 2 Analog Comparators

- 16-bit CRC Unit

In addition to these features, each part number in the C8051F85x/86x family has a set of features that vary across the product line. The product selection guide in Table 4.1 shows the features available on each family member.

All devices in Table 4.1 are also available in an industrial version. For the industrial version, the -G in the ordering part number is replaced with -I. For example, the industrial version of the C8051F850-C-GM is the C8051F850-C-IM.

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted               | Permitted         | N/A               |

|--------------------------------------------------------------------------|-------------------------|-------------------|-------------------|

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted           | Flash Error Reset | Permitted         |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted               | Permitted         | N/A               |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | C2 Device Erase<br>Only | Flash Error Reset | Flash Error Reset |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted           | Flash Error Reset | Flash Error Reset |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted           | Flash Error Reset | Flash Error Reset |

| Read, Write or Erase Reserved Area                                       | Not Permitted           | Flash Error Reset | Flash Error Reset |

### Table 10.1. Flash Security Summary (Continued)

C2 Device Erase—Erases all flash pages including the page containing the Lock Byte.

Flash Error Reset — Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

| Bit | Name  | Function                                                                                                                               |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0   | ESMB0 | Enable SMBus (SMB0) Interrupt.                                                                                                         |

|     |       | This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0. |

# Table 12.4. EIE1 Register Bit Descriptions

needed, it is recommended that AD12SM be set to 1 and ADTK to 0x3F, and that the ADC be placed in always-on mode (ADEN = 1). For sample rates under 180 ksps, or when accumulating multiple samples, AD12SM should normally be cleared to 0, and ADTK should be configured to provide the appropriate settling time for the subsequent conversions.

# 14.5. Power Considerations

The ADC has several power-saving features which can help the user optimize power consumption according to the needs of the application. The most efficient way to use the ADC for slower sample rates is by using burst mode. Burst mode dynamically controls power to the ADC and (if used) the internal voltage reference. By completely powering off these circuits when the ADC is not tracking or converting, the average supply current required for lower sampling rates is reduced significantly.

The ADC also provides low power options that allow reduction in operating current when operating at low SAR clock frequencies or with longer tracking times. The internal common-mode buffer can be configured for low power mode by setting the ADLPM bit in ADCOPWR to 1. Two other fields in the ADCOPWR register (ADBIAS and ADMXLP) may be used together to adjust the power consumed by the ADC and its multiplexer and reference buffers, respectively. In general, these options are used together, when operating with a SAR conversion clock frequency of 4 MHz.

| Required<br>Throughput | Reference Source | Mode Configuration                     | SAR Clock Speed         | Other Register Field<br>Settings             |

|------------------------|------------------|----------------------------------------|-------------------------|----------------------------------------------|

| 325-800 ksps           | Any              | Always-On<br>(ADEN = 1<br>ADBMEN = 0)  | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x40<br>ADC0TK = N/A<br>ADRPT = 0  |

| 0-325 ksps             | External         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1) | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x44<br>ADC0TK = 0x3A<br>ADRPT = 0 |

| 250-325 ksps           | Internal         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1) | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x44<br>ADC0TK = 0x3A<br>ADRPT = 0 |

| 200-250 ksps           | Internal         | Always-On<br>(ADEN = 1<br>ADBMEN = 0)  | 4.08 MHz<br>(ADSC = 5)  | ADC0PWR = 0xF0<br>ADC0TK = N/A<br>ADRPT = 0  |

| 0-200 ksps             | Internal         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1) | 4.08 MHz<br>(ADSC = 5)  | ADC0PWR = 0xF4<br>ADC0TK = 0x34<br>ADRPT = 0 |

Table 14.2. ADC0 Optimal Power Configuration (8- and 10-bit Mode)

Notes:

1. For always-on configuration, ADSC settings assume SYSCLK is the internal 24.5 MHz high-frequency oscillator. Adjust ADSC as needed if using a different source for SYSCLK.

2. ADRPT reflects the minimum setting for this bit field. When using the ADC in Burst Mode, up to 64 samples may be auto-accumulated per conversion start by adjusting ADRPT.

# 14.8. Voltage and Ground Reference Options

The voltage reference multiplexer is configurable to use an externally connected voltage reference, the internal voltage reference, or one of two power supply voltages. The ground reference mux allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (AGND).

The voltage and ground reference options are configured using the REF0CN register.

**Important Note About the VREF and AGND Inputs:** Port pins are used as the external VREF and AGND inputs. When using an external voltage reference, VREF should be configured as an analog input and skipped by the digital crossbar. When using AGND as the ground reference to ADC0, AGND should be configured as an analog input and skipped by the Digital Crossbar.

### 14.8.1. External Voltage Reference

To use an external voltage reference, REFSL should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference. If the manufacturer does not provide recommendations, a 4.7uF in parallel with a 0.1uF capacitor is recommended.

### 14.8.2. Internal Voltage Reference

For applications requiring the maximum number of port I/O pins, or very short VREF turn-on time, the highspeed reference will be the best internal reference option to choose. The internal reference is selected by setting REFSL to 11. When selected, the internal reference will be automatically enabled/disabled on an as-needed basis by the ADC. The reference can be set to one of two voltage values: 1.65 V or 2.4 V, depending on the value of the IREFLVL bit.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide the ADC with added dynamic range at the cost of reduced power supply noise rejection. To use the external supply pin (VDD) or the 1.8 V regulated digital supply voltage as the reference source, REFSL should be set to 01 or 10, respectively.

Internal reference sources are not routed to the VREF pin, and do not require external capacitors. The electrical specifications tables detail SAR clock and throughput limitations for each reference source.

#### 14.8.3. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for the ADC during both the tracking/sampling and the conversion periods is taken from the AGND pin. Any external sensors sampled by the ADC should be referenced to the AGND pin. If an external voltage reference is used, the AGND pin should be connected to the ground of the external reference and its associated decoupling capacitor. The separate analog ground reference option is enabled by setting GNDSL to 1. Note that when sampling the internal temperature sensor, the internal chip ground is always used for the sampling operation, regardless of the setting of the GNDSL bit. Similarly, whenever the internal 1.65 V high-speed reference is selected, the internal chip ground is always used during the conversion period, regardless of the setting of the GNDSL bit.

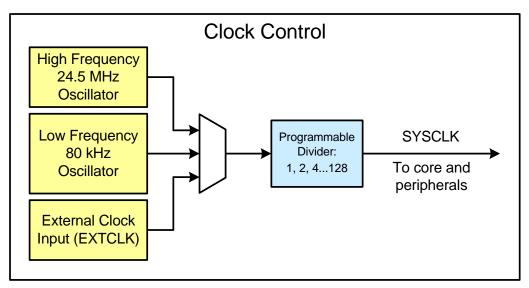

# 16. Clock Sources and Selection (HFOSC0, LFOSC0, and EXTCLK)

The C8051F85x/86x devices can be clocked from the internal low power 24.5 MHz oscillator, the internal low-frequency 80 kHz oscillator, or an external CMOS clock signal at the EXTCLK pin. An adjustable clock divider allows the selected clock source to be post-scaled by powers of 2, up to a factor of 128. By default, the system clock comes up as the 24.5 MHz oscillator divided by 8.

Figure 16.1. Clocking Options

# 16.1. Programmable High-Frequency Oscillator

All C8051F85x/86x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The oscillator is automatically enabled when it is requested. The internal oscillator period can be adjusted via the OSCICL register. On C8051F85x/86x devices, OSCICL is factory calibrated to obtain a 24.5 MHz base frequency.

# 16.2. Programmable Low-Frequency Oscillator

A programmable low-frequency internal oscillator is also included. The low-frequency oscillator is calibrated to a nominal frequency of 80 kHz. A divider at the oscillator output is capable of dividing the output clock of the module by 1, 2, 4, or 8, using the OSCLD bits in the OSCLCN register. Additionally, the OSCLF bits can be used to coarsely adjust the oscillator's output frequency.

### 16.2.1. Calibrating the Internal L-F Oscillator

Timer 3 includes a capture function that can be used to capture the oscillator frequency, when running from a known time base. When Timer 3 is configured for L-F Oscillator Capture Mode, a rising edge of the low-frequency oscillator's output will cause a capture event on the corresponding timer. As a capture event occurs, the current timer value (TMR3H:TMR3L) is copied into the timer reload registers (TMR3RLH:TMR3RLL). By recording the difference between two successive timer capture values, the low-frequency oscillator's period can be calculated. The OSCLF bits can then be adjusted to produce the desired oscillator frequency.

# 16.3. External Clock

An external CMOS clock source is also supported by the C8051F85x/86x family. The EXTCLK pin on the device serves as the external clock input when running in this mode. The EXTCLK input may also be used to clock some of the digital peripherals (e.g., Timers, PCA, etc.) while SYSCLK runs from one of the internal oscillator sources. When not selected as the SYSCLK source, the EXTCLK input is always resynchronized to SYSCLK.

### 16.4. Clock Selection

The CLKSEL register is used to select the clock source for the system. The CLKSL field selects which oscillator source is used as the system clock, while CLKDIV controls the programmable divider. CLKSL must be set to 01b for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. In these cases, the external oscillator source is synchronized to the SYSCLK source. The system clock may be switched on-the-fly between any of the oscillator sources so long as the selected clock source is enabled and has settled, and CLKDIV may be changed at any time.

The internal high-frequency and low-frequency oscillators require little start-up time and may be selected as the system clock immediately following the register write which enables the oscillator. When selecting the EXTCLK pin as a clock input source, the pin should be skipped in the crossbar and configured as a digital input. Firmware should ensure that the external clock source is present or enable the missing clock detector before switching the CLKSL field.

# Register 18.5. CRC0CNT: CRC0 Automatic Flash Sector Count

| Bit               | 7     | 6    | 5     | 4      | 3 | 2 | 1 | 0 |

|-------------------|-------|------|-------|--------|---|---|---|---|

| Name              | CRCDN | Rese | erved | CRCCNT |   |   |   |   |

| Туре              | R     | F    | २     | RW     |   |   |   |   |

| Reset             | 1     | 0    | 0     | 0      | 0 | 0 | 0 | 0 |

| SFR Address: 0xD3 |       |      |       |        |   |   |   |   |

# Table 18.6. CRC0CNT Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                            |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CRCDN    | Automatic CRC Calculation Complete.                                                                                                                                                                                                                 |

|     |          | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                            |

| 6:5 | Reserved | Must write reset value.                                                                                                                                                                                                                             |

| 4:0 | CRCCNT   | Automatic CRC Calculation Block Count.                                                                                                                                                                                                              |

|     |          | These bits specify the number of flash blocks to include in an automatic CRC calculation.<br>The last address of the last flash block included in the automatic CRC calculation is<br>(CRCST+CRCCNT) x Block Size - 1. The block size is 256 bytes. |

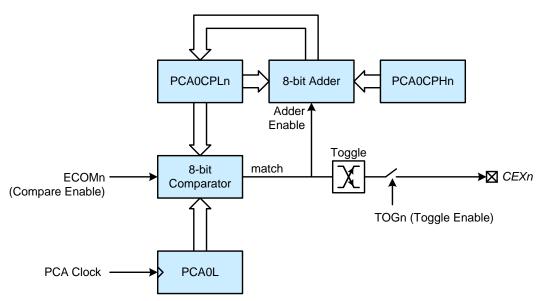

### 20.3.5. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 20.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

### Equation 20.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, n is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

Figure 20.5. PCA Frequency Output Mode

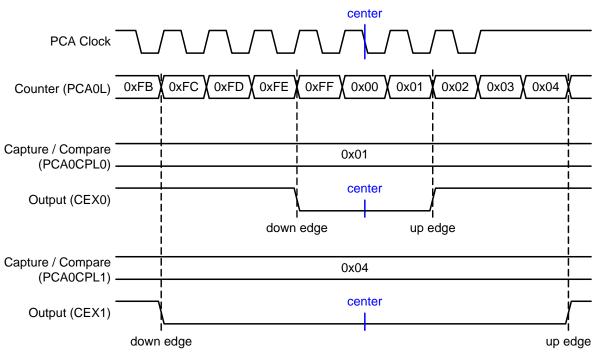

### 20.4.2. Center Aligned PWM

When configured for center-aligned mode, a module will generate an edge transition at two points for every  $2^{(N+1)}$  PCA clock cycles, where N is the selected PWM resolution in bits. In center-aligned mode, these two edges are referred to as the "up" and "down" edges. The polarity at the output pin is selectable, and can be inverted by setting the appropriate channel bit to '1' in the PCA0POL register.

The generated waveforms are centered about the points where the lower N bits of the PCA0 counter are zero. The  $(N+1)^{th}$  bit in the PCA0 counter acts as a selection between up and down edges. In 16-bit mode, a special 17th bit is implemented internally for this purpose. At the center point, the (non-inverted) channel output will be low when the  $(N+1)^{th}$  bit is '0' and high when the  $(N+1)^{th}$  bit is '1', except for cases of 0% and 100% duty cycle. Prior to inversion, an up edge sets the channel to logic high, and a down edge clears the channel to logic low.

Down edges occur when the (N+1)<sup>th</sup> bit in the PCA0 counter is one, and a logical inversion of the value in the module's PCA0CPn register matches the main PCA0 counter register for the lowest N bits. For example, with 10-bit PWM, the down edge will occur when the one's complement of bits 9-0 of the PCA0CPn register match bits 9-0 of the PCA0 counter, and bit 10 of the PCA0 counter is '1'.

Up edges occur when the (N+1)<sup>th</sup> bit in the PCA0 counter is zero, and the lowest N bits of the module's PCA0CPn register match the value of (PCA0 - 1). For example, with 10-bit PWM, the up edge will occur when bits 9-0 of the PCA0CPn register are one less than bits 9-0 of the PCA0 counter, and bit 10 of the PCA0 counter is '0'.

An example of the PWM timing in center-aligned mode for two channels is shown in Figure 20.7. In this example, the CEX0POL and CEX1POL bits are cleared to 0.

Figure 20.7. Center-Aligned PWM Timing

# Register 20.2. PCA0MD: PCA Mode

| Bit     | 7           | 6        | 5 | 4 | 3   | 2  | 1 | 0   |

|---------|-------------|----------|---|---|-----|----|---|-----|

| Name    | CIDL        | Reserved |   |   | CPS |    |   | ECF |

| Туре    | RW          | R        |   |   |     | RW |   | RW  |

| Reset   | 0           | 0        | 0 | 0 | 0   | 0  | 0 | 0   |

| SFR Add | lress: 0xD9 |          |   |   |     |    |   |     |

# Table 20.4. PCA0MD Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CIDL     | <ul> <li>PCA Counter/Timer Idle Control.</li> <li>Specifies PCA behavior when CPU is in Idle Mode.</li> <li>0: PCA continues to function normally while the system controller is in Idle Mode.</li> <li>1: PCA operation is suspended while the system controller is in Idle Mode.</li> </ul>                                                                                                                                                                                               |

| 6:4 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3:1 | CPS      | PCA Counter/Timer Pulse Select.         These bits select the timebase source for the PCA counter.         000: System clock divided by 12.         001: System clock divided by 4.         010: Timer 0 overflow.         011: High-to-low transitions on ECI (max rate = system clock divided by 4).         100: System clock.         101: External clock divided by 8 (synchronized with the system clock).         110: Low frequency oscillator divided by 8.         111: Reserved. |

| 0   | ECF      | <ul> <li>PCA Counter/Timer Overflow Interrupt Enable.</li> <li>This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.</li> <li>0: Disable the CF interrupt.</li> <li>1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.</li> </ul>                                                                                                                                                                                                    |

# Register 20.3. PCA0PWM: PCA PWM Configuration

| Bit     | 7                 | 6    | 5    | 4 3  |       | 2  | 1     | 0 |  |

|---------|-------------------|------|------|------|-------|----|-------|---|--|

| Name    | ARSEL             | ECOV | COVF | Rese | erved |    | CLSEL |   |  |

| Туре    | RW                | RW   | RW   | F    | २     | RW |       |   |  |

| Reset   | set 0 0 0 0       |      | 0    | 0    | 0     | 0  |       |   |  |

| SFR Add | SFR Address: 0xF7 |      |      |      |       |    |       |   |  |

# Table 20.5. PCA0PWM Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ARSEL    | Auto-Reload Register Select.<br>This bit selects whether to read and write the normal PCA capture/compare registers<br>(PCA0CPn), or the Auto-Reload registers at the same SFR addresses. This function is<br>used to define the reload value for 9 to 11-bit PWM modes. In all other modes, the Auto-<br>Reload registers have no function.<br>0: Read/Write Capture/Compare Registers at PCA0CPHn and PCA0CPLn.                                                              |

| 6   | ECOV     | <ol> <li>Read/Write Auto-Reload Registers at PCA0CPHn and PCA0CPLn.</li> <li>Cycle Overflow Interrupt Enable.</li> <li>This bit sets the masking of the Cycle Overflow Flag (COVF) interrupt.</li> <li>COVF will not generate PCA interrupts.</li> <li>A PCA interrupt will be generated when COVF is set.</li> </ol>                                                                                                                                                          |

| 5   | COVF     | <ul> <li>Cycle Overflow Flag.</li> <li>This bit indicates an overflow of the 8th to 11th bit of the main PCA counter (PCA0). The specific bit used for this flag depends on the setting of the Cycle Length Select bits. The bit can be set by hardware or software, but must be cleared by software.</li> <li>0: No overflow has occurred since the last time this bit was cleared.</li> <li>1: An overflow has occurred since the last time this bit was cleared.</li> </ul> |

| 4:3 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2:0 | CLSEL    | Cycle Length Select.<br>When 16-bit PWM mode is not selected, these bits select the length of the PWM cycle.<br>This affects all channels configured for PWM which are not using 16-bit PWM mode.<br>These bits are ignored for individual channels configured to16-bit PWM mode.<br>000: 8 bits.<br>001: 9 bits.<br>010: 10 bits.<br>011: 11 bits.<br>100-111: Reserved.                                                                                                      |

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 24.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

### 24.4.4.1. Software ACK Generation

When the EHACK bit in register SMB0ADM is cleared to 0, the firmware on the device must detect incoming slave addresses and ACK or NACK the slave address and incoming data bytes. As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

### 24.4.4.2. Hardware ACK Generation

When the EHACK bit in register SMB0ADM is set to 1, automatic slave address recognition and ACK generation is enabled. More detail about automatic slave address recognition can be found in Section 24.4.5. As a receiver, the value currently specified by the ACK bit will be automatically sent on the bus during the ACK cycle of an incoming data byte. As a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. The ACKRQ bit is not used when hardware ACK generation is enabled. If a received slave address is NACKed by hardware, further slave events will be ignored until the next START is detected, and no interrupt will be generated.

Table 24.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 24.5 for SMBus status decoding using the SMB0CN register.

| Bit    | Set by Hardware When:                                                    | Cleared by Hardware When:                                                          |

|--------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| MASTER | <ul> <li>A START is generated.</li> </ul>                                | <ul> <li>A STOP is generated.</li> </ul>                                           |

| WASTER |                                                                          | <ul> <li>Arbitration is lost.</li> </ul>                                           |

|        | <ul> <li>START is generated.</li> </ul>                                  | <ul> <li>A START is detected.</li> </ul>                                           |

| TXMODE | <ul> <li>SMB0DAT is written before the start of an</li> </ul>            | <ul> <li>Arbitration is lost.</li> </ul>                                           |

| TAMODE | SMBus frame.                                                             | <ul> <li>SMB0DAT is not written before the<br/>start of an SMBus frame.</li> </ul> |

| STA    | <ul> <li>A START followed by an address byte is<br/>received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                                   |

| STO    | <ul> <li>A STOP is detected while addressed as a<br/>slave.</li> </ul>   | <ul> <li>A pending STOP is generated.</li> </ul>                                   |

|        | <ul> <li>Arbitration is lost due to a detected STOP.</li> </ul>          |                                                                                    |

### Table 24.3. Sources for Hardware Changes to SMB0CN

|                   | Val              | lue | es F | Rea                                                                            | d |                                                                                         |                                                                                |      | lues<br>Vrit |     | itus<br>ected                  |

|-------------------|------------------|-----|------|--------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|--------------|-----|--------------------------------|

| Mode              | Status<br>Vector |     |      |                                                                                |   |                                                                                         | Typical Response Options                                                       | STA  | STO          | ACK | Next Status<br>Vector Expected |

|                   |                  |     |      |                                                                                |   |                                                                                         | Set ACK for next data byte;<br>Read SMB0DAT.                                   | 0    | 0            | 1   | 1000                           |

|                   |                  |     | 0    | 0                                                                              | 1 | A master data byte was received; ACK sent.                                              | Set NACK to indicate next data<br>byte as the last data byte;<br>Read SMB0DAT. | 0    | 0            | 0   | 1000                           |

| ř                 |                  |     |      |                                                                                |   | Sent.                                                                                   | Initiate repeated START.                                                       | 1    | 0            | 0   | 1110                           |

| Master Receiver   | 1000             |     |      | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI). | 0 | 0                                                                                       | Х                                                                              | 1100 |              |     |                                |

| aste              |                  | ſ   |      |                                                                                |   |                                                                                         | Read SMB0DAT; send STOP.                                                       | 0    | 1            | 0   | —                              |

| Ξ                 |                  |     |      |                                                                                |   | A master data byte was received;                                                        | Read SMB0DAT; Send STOP followed by START.                                     | 1    | 1            | 0   | 1110                           |

|                   |                  |     | 0    | 0                                                                              | 0 | NACK sent (last byte).                                                                  | Initiate repeated START.                                                       | 1    | 0            | 0   | 1110                           |

|                   |                  |     |      |                                                                                |   |                                                                                         | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI). | 0    | 0            | Х   | 1100                           |

| er.               |                  |     | 0    | 0                                                                              | 0 | A slave byte was transmitted; NACK received.                                            | No action required (expecting STOP condition).                                 | 0    | 0            | Х   | 0001                           |

| smitte            | 0100             | 5   | 0    | 0                                                                              | 1 | A slave byte was transmitted; ACK received. Load SMB0DAT with next of byte to transmit. |                                                                                | 0    | 0            | Х   | 0100                           |

| Slave Transmitter |                  |     | 0    | 1                                                                              | Х | A Slave byte was transmitted; error detected.                                           | No action required (expecting Master to end transfer).                         | 0    | 0            | Х   | 0001                           |

| Slav              | 0101             | 1   | 0    | х                                                                              | х | An illegal STOP or bus error was detected while a Slave Transmission was in progress.   | Clear STO.                                                                     | 0    | 0            | Х   |                                |

# Table 24.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1) (Continued)

# Register 25.8. TMR2CN: Timer 2 Control

| 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 5      | 6    | 7    | Bit  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|------|------|------|--|--|

| TF2LEN TF2CEN T2SPLIT TR2 Reserved T2XCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Т | TF2LEN | TF2L | TF2H | Name |  |  |

| RW RW RW R RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | RW     | RW   | RW   | Туре |  |  |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 |   |        |      |      |      |  |  |

| 0 0 0 0 0 0 able)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |        |      |      |      |  |  |

# Table 25.10. TMR2CN Register Bit Descriptions

| Name     | Function                                                                                                                                                                                                                                                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TF2H     | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                    |

|          | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware. |

| TF2L     | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                     |

|          | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                              |

| TF2LEN   | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                  |

|          | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                         |

| TF2CEN   | Timer 2 Capture Enable.                                                                                                                                                                                                                                                                                                             |

|          | When set to 1, this bit enables Timer 2 Capture Mode. If TF2CEN is set and Timer 2 interrupts are enabled, an interrupt will be generated on a falling edge of the selected T2 input pin, and the current 16-bit timer value in TMR2H:TMR2L will be copied to TMR2RLH:TMR2RLL.                                                      |

| T2SPLIT  | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                          |

|          | <ul><li>When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.</li><li>0: Timer 2 operates in 16-bit auto-reload mode.</li><li>1: Timer 2 operates as two 8-bit auto-reload timers.</li></ul>                                                                                                                 |

| TR2      | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                |

|          | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                            |

| Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                             |

|          | TF2H<br>TF2L<br>TF2LEN<br>TF2CEN<br>TF2CEN<br>T2SPLIT<br>TR2                                                                                                                                                                                                                                                                        |

# 27.5. Watchdog Timer Control Registers

# Register 27.1. WDTCN: Watchdog Timer Control

| Bit     | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------------------|---|---|---|---|---|---|---|--|

| Name    | WDTCN             |   |   |   |   |   |   |   |  |

| Туре    | RW                |   |   |   |   |   |   |   |  |

| Reset   | 0 0 0 1 0 1 1 1   |   |   |   |   |   |   |   |  |

| SFR Add | SFR Address: 0x97 |   |   |   |   |   |   |   |  |

### Table 27.1. WDTCN Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                       |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | WDTCN | WDT Control.                                                                                                                                   |

|     |       | The WDT control field has different behavior for reads and writes.                                                                             |

|     |       | Read:                                                                                                                                          |

|     |       | When reading the WDTCN register, the lower three bits (WDTCN[2:0]) indicate the cur-                                                           |

|     |       | rent timeout interval. Bit WDTCN.4 indicates whether the WDT is active (logic 1) or inac-                                                      |

|     |       | tive (logic 0).                                                                                                                                |

|     |       | Write:                                                                                                                                         |

|     |       | Writing the WDTCN register can set the timeout interval, enable the WDT, disable the WDT, reset the WDT, or lock the WDT to prevent disabling. |

|     |       | Writing to WDTCN with the MSB (WDTCN.7) cleared to 0 will set the timeout interval to                                                          |

|     |       | the value in bits WDTCN[2:0].                                                                                                                  |

|     |       | Writing 0xA5 both enables and reloads the WDT.                                                                                                 |

|     |       | Writing 0xDE followed within 4 system clocks by 0xAD disables the WDT.                                                                         |

|     |       | Writing 0xFF locks out the disable feature until the next device reset.                                                                        |

# Register 29.4. C2FPCTL: C2 Flash Programming Control

| Bit              | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|-------------------|---|---|---|---|---|---|---|

| Name             | C2FPCTL           |   |   |   |   |   |   |   |

| Туре             | RW                |   |   |   |   |   |   |   |

| Reset            | 0 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

| C2 Address: 0x02 |                   |   |   |   |   |   |   |   |

# Table 29.4. C2FPCTL Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | C2FPCTL | Flash Programming Control Register.                                                                                                                                                                                                                                         |

|     |         | This register is used to enable flash programming via the C2 interface. To enable C2 flash programming, the following codes must be written in order: 0x02, 0x01. Note that once C2 flash programming is enabled, a system reset must be issued to resume normal operation. |