Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                            |

| Number of I/O              | 15                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                      |

| Data Converters            | A/D 15x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-VFQFN Exposed Pad                                             |

| Supplier Device Package    | -                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f852-c-im |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 1.7. ADC

| Parameter                       | Symbol              | Test Condition                                                           | Min         | Тур  | Max                                     | Unit |

|---------------------------------|---------------------|--------------------------------------------------------------------------|-------------|------|-----------------------------------------|------|

| Resolution                      | N <sub>bits</sub>   | 12 Bit Mode                                                              | 12          |      |                                         | Bits |

|                                 |                     | 10 Bit Mode                                                              | Bit Mode 10 |      |                                         | Bits |

| Throughput Rate                 | f <sub>S</sub>      | 12 Bit Mode                                                              | _           | _    | 200                                     | ksps |

| (High Speed Mode)               |                     | 10 Bit Mode                                                              | _           | _    | 800                                     | ksps |

| Throughput Rate                 | f <sub>S</sub>      | 12 Bit Mode                                                              | _           | _    | 62.5                                    | ksps |

| (Low Power Mode)                | -                   | 10 Bit Mode                                                              | _           | _    | 250                                     | ksps |

| Tracking Time                   | t <sub>TRK</sub>    | High Speed Mode                                                          | 230         | _    |                                         | ns   |

|                                 | -                   | Low Power Mode                                                           | 450         | _    |                                         | ns   |

| Power-On Time                   | t <sub>PWR</sub>    |                                                                          | 1.2         | _    | _                                       | μs   |

| SAR Clock Frequency             | f <sub>SAR</sub>    | High Speed Mode,<br>Reference is 2.4 V internal                          | _           | _    | 6.25                                    | MHz  |

|                                 |                     | High Speed Mode,<br>Reference is not 2.4 V internal                      |             | —    | 12.5                                    | MHz  |

|                                 |                     | Low Power Mode                                                           | _           | _    | 4                                       | MHz  |

| Conversion Time                 | t <sub>CNV</sub>    | 10-Bit Conversion,<br>SAR Clock = 12.25 MHz,<br>System Clock = 24.5 MHz. |             | 1.1  |                                         | μs   |

| Sample/Hold Capacitor           | C <sub>SAR</sub>    | Gain = 1                                                                 | _           | 5    |                                         | pF   |

|                                 |                     | Gain = 0.5                                                               | _           | 2.5  |                                         | pF   |

| Input Pin Capacitance           | C <sub>IN</sub>     |                                                                          | _           | 20   |                                         | pF   |

| Input Mux Impedance             | R <sub>MUX</sub>    |                                                                          | _           | 550  |                                         | Ω    |

| Voltage Reference Range         | V <sub>REF</sub>    |                                                                          | 1           | _    | V <sub>DD</sub>                         | V    |

| Input Voltage Range*            | V <sub>IN</sub>     | Gain = 1                                                                 | 0           | _    | V <sub>REF</sub>                        | V    |

|                                 |                     | Gain = 0.5                                                               | 0           |      | $2xV_{REF}$                             | V    |

| Power Supply Rejection<br>Ratio | PSRR <sub>ADC</sub> |                                                                          | —           | 70   | —                                       | dB   |

| DC Performance                  |                     |                                                                          |             |      |                                         |      |

| Integral Nonlinearity           | INL                 | 12 Bit Mode                                                              | _           | ±1   | ±2.3                                    | LSB  |

|                                 |                     | 10 Bit Mode                                                              |             | ±0.2 | ±0.6                                    | LSB  |

| Differential Nonlinearity       | DNL                 | 12 Bit Mode                                                              | -1          | ±0.7 | 1.9                                     | LSB  |

| (Guaranteed Monotonic)          |                     | 10 Bit Mode                                                              | _           | ±0.2 | ±0.6                                    | LSB  |

| *Note: Absolute input pin volta | age is limited by   | the V <sub>DD</sub> supply.                                              |             |      | ı — — — — — — — — — — — — — — — — — — — |      |

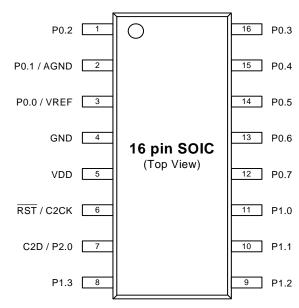

#### 3.3. C8051F860/1/2/3/4/5 SOIC16 Pin Definitions

Figure 3.3. C8051F860/1/2/3/4/5-GS and C8051F860/1/2/3/4/5-IS Pinout

| Pin Name      | Туре                                 | Pin Numbers | Crossbar Capability | Additional Digital Functions | Analog Functions           |

|---------------|--------------------------------------|-------------|---------------------|------------------------------|----------------------------|

| GND           | Ground                               | 4           |                     |                              |                            |

| VDD           | Power                                | 5           |                     |                              |                            |

| RST /<br>C2CK | Active-low Reset /<br>C2 Debug Clock | 6           |                     |                              |                            |

| P0.0          | Standard I/O                         | 3           | Yes                 | POMAT.0<br>INT0.0<br>INT1.0  | ADC0.0<br>CP0P.0<br>CP0N.0 |

| Symbol | Millim | neters | Symbol | Millim | neters |

|--------|--------|--------|--------|--------|--------|

|        | Min    | Max    |        | Min    | Max    |

| D      | 2.71   | REF    | GE     | 2.10   | _      |

| D2     | 1.60   | 1.80   | W      | _      | 0.34   |

| е      | 0.50   | BSC    | Х      | —      | 0.28   |

| E      | 2.71   | REF    | Y      | 0.61   | REF    |

| E2     | 1.60   | 1.80   | ZE     | —      | 3.31   |

| f      | 2.53   | BSC    | ZD     | —      | 3.31   |

| GD     | 2.10   | —      |        |        |        |

#### Table 6.2. QFN-20 Landing Diagram Dimensions

#### Notes: General

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Notes: Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Notes: Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- **4.** A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides approximately 70% solder paste coverage on the pad, which is optimum to assure correct component stand-off.

#### Notes: Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

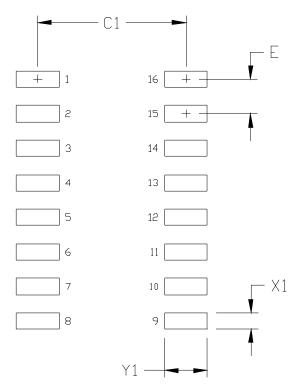

| Dimension         | Feature            | (mm) |  |  |

|-------------------|--------------------|------|--|--|

| C1                | Pad Column Spacing | 5.40 |  |  |

| Е                 | Pad Row Pitch      | 1.27 |  |  |

| X1                | Pad Width          | 0.60 |  |  |

| Y1                | Pad Length         | 1.55 |  |  |

| Notes:<br>General |                    |      |  |  |

$\label{eq:linear} \textbf{1.} \hspace{0.1 cm} \text{All dimensions shown are in millimeters (mm) unless otherwise noted.}$

2. This Land Pattern Design is based on IPC-7351 pattern SOIC127P600X165-16N for Density Level B (Median Land Protrusion).

**3.** All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.

cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction. If more than one interrupt is pending when the CPU exits an ISR, the CPU will service the next highest priority interrupt that is pending.

# Register 14.8. ADC0L: ADC0 Data Word Low Byte

| Bit     | 7                 | 6     | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------------------|-------|---|---|---|---|---|---|--|

| Name    |                   | ADCOL |   |   |   |   |   |   |  |

| Туре    |                   | RW    |   |   |   |   |   |   |  |

| Reset   | 0                 | 0     | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Add | SFR Address: 0xBD |       |   |   |   |   |   |   |  |

# Table 14.11. ADC0L Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0L | Data Word Low Byte.                                                                                                                                                                                                                        |

|     |       | When read, this register returns the least significant byte of the 16-bit ADC0 accumula-<br>tor, formatted according to the settings in ADSJST. The register may also be written, to<br>set the lower byte of the 16-bit ADC0 accumulator. |

|     |       | ting is enabled, the most significant bits of the value read will be zeros. This register should not be YNC bit is set to 1.                                                                                                               |

# Register 14.13. ADC0MX: ADC0 Multiplexer Selection

| Bit   | 7                    | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|-------|----------------------|---|---|---|---|----|---|---|

| Name  | lame Reserved ADC0MX |   |   |   |   |    |   |   |

| Туре  |                      | R |   |   |   | RW |   |   |

| Reset | 0                    | 0 | 0 | 1 | 1 | 1  | 1 | 1 |

### Table 14.16. ADC0MX Register Bit Descriptions

| Bit | Name     | Function                                                                                |

|-----|----------|-----------------------------------------------------------------------------------------|

| 7:5 | Reserved | Must write reset value.                                                                 |

| 4:0 | ADC0MX   | AMUX0 Positive Input Selection.                                                         |

|     |          | Selects the positive input channel for ADC0. For reserved bit combinations, no input is |

|     |          | selected.                                                                               |

|     |          | 00000: ADC0.0                                                                           |

|     |          | 00001: ADC0.1                                                                           |

|     |          | 00010: ADC0.2                                                                           |

|     |          | 00011: ADC0.3                                                                           |

|     |          | 00100: ADC0.4                                                                           |

|     |          | 00101: ADC0.5                                                                           |

|     |          | 00110: ADC0.6                                                                           |

|     |          | 00111: ADC0.7                                                                           |

|     |          | 01000: ADC0.8                                                                           |

|     |          | 01001: ADC0.9                                                                           |

|     |          | 01010: ADC0.10                                                                          |

|     |          | 01011: ADC0.11                                                                          |

|     |          | 01100: ADC0.12                                                                          |

|     |          | 01101: ADC0.13                                                                          |

|     |          | 01110: ADC0.14                                                                          |

|     |          | 01111: ADC0.15                                                                          |

|     |          | 10000: Temperature sensor.                                                              |

|     |          | 10001: Internal LDO regulator output.                                                   |

|     |          | 10010: VDD                                                                              |

|     |          | 10011: GND                                                                              |

|     |          | 10100-11111: Reserved.                                                                  |

# Register 15.4. ACC: Accumulator

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------------|---|---|---|---|---|---|---|--|

| Name  | ACC             |   |   |   |   |   |   |   |  |

| Туре  | RW              |   |   |   |   |   |   |   |  |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |  |

# Table 15.5. ACC Register Bit Descriptions

| Bit | Name | Function                                                    |

|-----|------|-------------------------------------------------------------|

| 7:0 | ACC  | Accumulator.                                                |

|     |      | This register is the accumulator for arithmetic operations. |

### Register 17.2. CPT0MD: Comparator 0 Mode

| Bit     | 7                 | 6        | 5     | 4     | 3        | 2 | 1    | 0 |  |

|---------|-------------------|----------|-------|-------|----------|---|------|---|--|

| Name    | CPLOUT            | Reserved | CPRIE | CPFIE | Reserved |   | CPMD |   |  |

| Туре    | RW                | R        | RW    | RW    | R        |   | RW   |   |  |

| Reset   | 0                 | 0        | 0     | 0     | 0        | 0 | 1    | 0 |  |

| SFR Add | SFR Address: 0x9D |          |       |       |          |   |      |   |  |

# Table 17.6. CPT0MD Register Bit Descriptions

| Bit | Name     | Function                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------|

| 7   | CPLOUT   | Comparator 0 Latched Output Flag.                                                        |

|     |          | This bit represents the comparator output value at the most recent PCA counter overflow. |

|     |          | 0: Comparator output was logic low at last PCA overflow.                                 |

|     |          | 1: Comparator output was logic high at last PCA overflow.                                |

| 6   | Reserved | Must write reset value.                                                                  |

| 5   | CPRIE    | Comparator 0 Rising-Edge Interrupt Enable.                                               |

|     |          | 0: Comparator Rising-Edge interrupt disabled.                                            |

|     |          | 1: Comparator Rising-Edge interrupt enabled.                                             |

| 4   | CPFIE    | Comparator 0 Falling-Edge Interrupt Enable.                                              |

|     |          | 0: Comparator Falling-Edge interrupt disabled.                                           |

|     |          | 1: Comparator Falling-Edge interrupt enabled.                                            |

| 3:2 | Reserved | Must write reset value.                                                                  |

| 1:0 | CPMD     | Comparator 0 Mode Select.                                                                |

|     |          | These bits affect the response time and power consumption of the comparator.             |

|     |          | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)                            |

|     |          | 01: Mode 1                                                                               |

|     |          | 10: Mode 2                                                                               |

|     |          | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)                             |

#### 20.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte of the 16-bit counter/timer and PCA0L is the low byte. Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2–CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 20.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2      | CPS1       | CPS0        | Timebase                                                               |

|-----------|------------|-------------|------------------------------------------------------------------------|

| 0         | 0          | 0           | System clock divided by 12                                             |

| 0         | 0          | 1           | System clock divided by 4                                              |

| 0         | 1          | 0           | Timer 0 overflow                                                       |

| 0         | 1          | 1           | High-to-low transitions on ECI (max rate = system clock divided by 4)* |

| 1         | 0          | 0           | System clock                                                           |

| 1         | 0          | 1           | External oscillator source divided by 8 <sup>*</sup>                   |

| 1         | 1          | 0           | Low frequency oscillator divided by 8 <sup>*</sup>                     |

| 1         | 1          | 1           | Reserved                                                               |

| *Note: Sy | nchronized | with the sy | stem clock.                                                            |

#### Table 20.1. PCA Timebase Input Options

. . .

#### 20.2. PCA0 Interrupt Sources

The PCA0 module shares one interrupt vector among all of its modules. There are several event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th - 11th bit of the PCA0 counter, and the individual flags for each PCA channel (CCFn), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

### Register 20.15. PCA0CPH1: PCA Capture Module High Byte

| Bit     | 7                 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

|---------|-------------------|---|---|------|------|---|---|---|

| Name    |                   |   |   | PCA0 | CPH1 |   |   |   |

| Туре    | RW                |   |   |      |      |   |   |   |

| Reset   | 0 0 0 0 0 0 0 0 0 |   |   |      |      |   |   |   |

| SFR Add | SFR Address: 0xEA |   |   |      |      |   |   |   |

### Table 20.17. PCA0CPH1 Register Bit Descriptions

| Bit     | Name                                                                 | Function                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:0     | PCA0CPH1                                                             | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|         |                                                                      | The PCA0CPH1 register holds the high byte (MSB) of the 16-bit capture module. This register address also allows access to the high byte of the corresponding PCA channels auto-reload value for 9 to 11-bit PWM mode. The ARSEL bit in register PCA0PWM controls which register is accessed. |  |  |  |  |  |  |  |

| Note: A | Note: A write to this register will set the modules ECOM bit to a 1. |                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

### Register 21.8. P0MDIN: Port 0 Input Mode

| Bit               | 7  | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|----|-----------------|---|---|---|---|---|---|

| Name              |    | POMDIN          |   |   |   |   |   |   |

| Туре              | RW |                 |   |   |   |   |   |   |

| Reset             | 1  | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |

| SFR Address: 0xF1 |    |                 |   |   |   |   |   |   |

# Table 21.11. POMDIN Register Bit Descriptions

| Bit | Name   | Function                                                                                                    |

|-----|--------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN | Port 0 Input Mode.                                                                                          |

|     |        | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |        | 0: Corresponding P0.x pin is configured for analog mode.                                                    |

|     |        | 1: Corresponding P0.x pin is configured for digital mode.                                                   |

# 23. Serial Peripheral Interface (SPI0)

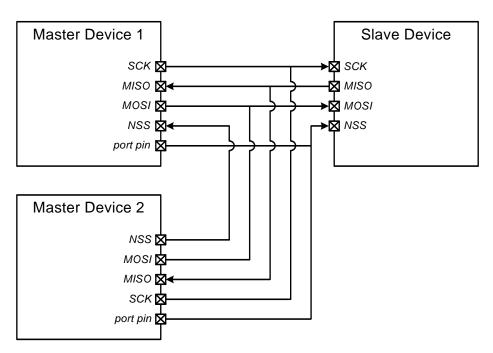

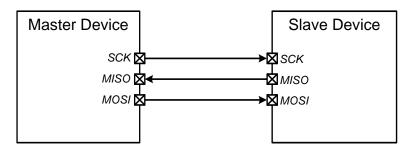

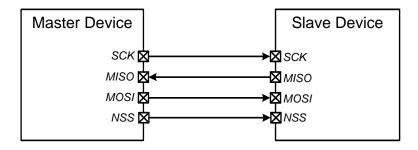

The serial peripheral interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

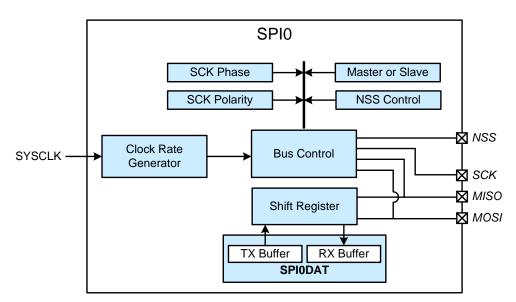

Figure 23.1. SPI0 Block Diagram

Figure 23.2. Multiple-Master Mode Connection Diagram

Figure 23.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

Figure 23.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram

| Bit | Name  | Function                                                                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SMBCS | SMBus0 Clock Source Selection.                                                                                                                                                                                                                                                 |

|     |       | These two bits select the SMBus0 clock source, which is used to generate the SMBus0<br>bit rate. See the SMBus clock timing section for additional details.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow |

### Table 24.7. SMB0CF Register Bit Descriptions

# 25. Timers (Timer0, Timer1, Timer2 and Timer3)

Each MCU in the C8051F85x/86x family includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timers for timing peripherals or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 are also identical and offer both 16-bit and split 8-bit timer functionality with auto-reload capabilities. Timer 2 and Timer 3 both offer a capture function, but are different in their system-level connections. Timer 2 is capable of performing a capture function on an external signal input routed through the crossbar, while the Timer 3 capture is dedicated to the low-frequency oscillator output. Table 25.1 summarizes the modes available to each timer.

| Timer 0 and Timer 1 Modes                  | Timer 2 Modes                     | Timer 3 Modes                     |

|--------------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                       | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                       | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |

| 8-bit counter/timer with auto-reload       | Input pin capture                 | Low-frequency oscillator capture  |

| Two 8-bit counter/timers<br>(Timer 0 only) |                                   |                                   |

#### Table 25.1. Timer Modes

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked.

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it must be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

All four timers are capable of clocking other peripherals and triggering events in the system. The individual peripherals select which timer to use for their respective functions. Table 25.2 summarizes the peripheral connections for each timer. Note that the Timer 2 and Timer 3 high overflows apply to the full timer when operating in 16-bit mode or the high-byte timer when operating in 8-bit split mode.

| Table 25.2. Timer Peripheral | Clocking / Event Triggering |

|------------------------------|-----------------------------|

|------------------------------|-----------------------------|

| Function               | T0<br>Overflow | T1<br>Overflow | T2 High<br>Overflow | T2 Low<br>Overflow | T3 High<br>Overflow | T3 Low<br>Overflow |

|------------------------|----------------|----------------|---------------------|--------------------|---------------------|--------------------|

| UART0 Baud Rate        |                | Х              |                     |                    |                     |                    |

| SMBus0 Clock Rate      | Х              | Х              | Х                   | Х                  |                     |                    |

| SMBus0 SCL Low Timeout |                |                |                     |                    | Х                   |                    |

| PCA0 Clock             | Х              |                |                     |                    |                     |                    |

# Register 25.3. TMOD: Timer 0/1 Mode

| Bit   | 7     | 6   | 5   | 4 | 3     | 2   | 1   | 0 |

|-------|-------|-----|-----|---|-------|-----|-----|---|

| Name  | GATE1 | CT1 | T1M |   | GATE0 | CT0 | ТОМ |   |

| Туре  | RW    | RW  | RW  |   | RW    | RW  | RW  |   |

| Reset | 0     | 0   | 0   | 0 | 0     | 0   | 0   | 0 |

# Table 25.5. TMOD Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE1 | Timer 1 Gate Control.0: Timer 1 enabled when TR1 = 1 irrespective of INT1 logic level.1: Timer 1 enabled only when TR1 = 1 and INT1 is active as defined by bit IN1PL in register IT01CF.                                                  |

| 6   | CT1   | Counter/Timer 1 Select.0: Timer Mode. Timer 1 increments on the clock defined by T1M in the CKCON register.1: Counter Mode. Timer 1 increments on high-to-low transitions of an external pin (T1).                                         |

| 5:4 | T1M   | Timer 1 Mode Select.These bits select the Timer 1 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Timer 1 Inactive                              |

| 3   | GATE0 | Timer 0 Gate Control.0: Timer 0 enabled when TR0 = 1 irrespective of INT0 logic level.1: Timer 0 enabled only when TR0 = 1 and INT0 is active as defined by bit IN0PL in register IT01CF.                                                  |

| 2   | СТО   | <ul> <li>Counter/Timer 0 Select.</li> <li>0: Timer Mode. Timer 0 increments on the clock defined by T0M in the CKCON register.</li> <li>1: Counter Mode. Timer 0 increments on high-to-low transitions of an external pin (T0).</li> </ul> |

| 1:0 | ТОМ   | Timer 0 Mode Select.These bits select the Timer 0 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Two 8-bit Counter/Timers                      |

# Register 25.8. TMR2CN: Timer 2 Control

| 5 4 3 2 1 0                               |   | 5      | 6    | 7    | Bit   |

|-------------------------------------------|---|--------|------|------|-------|

| TF2LEN TF2CEN T2SPLIT TR2 Reserved T2XCLK | Т | TF2LEN | TF2L | TF2H | Name  |

| RW RW RW R RW                             |   | RW     | RW   | RW   | Туре  |

| 0 0 0 0 0 0                               |   | 0      | 0    | 0    | Reset |

| 0 0 0 0 0 0 able)                         |   |        |      |      |       |

### Table 25.10. TMR2CN Register Bit Descriptions

| Name     | Function                                                                                                                                                                                                                                                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TF2H     | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                    |

|          | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware. |

| TF2L     | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                     |

|          | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                              |

| TF2LEN   | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                  |

|          | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                         |

| TF2CEN   | Timer 2 Capture Enable.                                                                                                                                                                                                                                                                                                             |

|          | When set to 1, this bit enables Timer 2 Capture Mode. If TF2CEN is set and Timer 2 interrupts are enabled, an interrupt will be generated on a falling edge of the selected T2 input pin, and the current 16-bit timer value in TMR2H:TMR2L will be copied to TMR2RLH:TMR2RLL.                                                      |

| T2SPLIT  | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                          |

|          | <ul> <li>When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.</li> <li>0: Timer 2 operates in 16-bit auto-reload mode.</li> <li>1: Timer 2 operates as two 8-bit auto-reload timers.</li> </ul>                                                                                                             |

| TR2      | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                |

|          | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                            |

| Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                             |

|          | TF2H<br>TF2L<br>TF2LEN<br>TF2CEN<br>TF2CEN<br>T2SPLIT<br>TR2                                                                                                                                                                                                                                                                        |

# Register 25.14. TMR3RLL: Timer 3 Reload Low Byte

| Bit   | 7          | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|-------|------------|---|---|-----|------|---|---|---|

| Name  |            |   | · | TMR | 3RLL |   |   |   |

| Туре  | RW         |   |   |     |      |   |   |   |

| Reset | 0          | 0 | 0 | 0   | 0    | 0 | 0 | 0 |

|       | ress: 0x92 | Ŭ | Ŭ | Ŭ   | Ŭ    | Ŭ | 0 |   |

### Table 25.16. TMR3RLL Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3RLL | Timer 3 Reload Low Byte.                                                                                                                                                                    |

|     |         | When operating in one of the auto-reload modes, TMR3RLL holds the reload value for the low byte of Timer 3 (TMR3L). When operating in capture mode, TMR3RLL is the captured value of TMR3L. |

#### 29.2. C2 Interface Registers

The following describes the C2 registers necessary to perform flash programming through the C2 interface. All C2 registers are accessed through the C2 interface, and are not available in the SFR map for firmware access.

#### Register 29.1. C2ADD: C2 Address

| Bit       | 7                                         | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|-------------------------------------------|-------|---|---|---|---|---|---|

| Name      |                                           | C2ADD |   |   |   |   |   |   |

| Туре      | RW                                        |       |   |   |   |   |   |   |

| Reset     | 0                                         | 0     | 0 | 0 | 0 | 0 | 0 | 0 |

| This regi | This register is part of the C2 protocol. |       |   |   |   |   |   |   |

#### Table 29.1. C2ADD Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | C2ADD | C2 Address.                                                                                                                                                                                                                    |

|     |       | The C2ADD register is accessed via the C2 interface. The value written to C2ADD selects the target data register for C2 Data Read and Data Write commands.<br>0x00: C2DEVID<br>0x01: C2REVID<br>0x02: C2FPCTL<br>0xB4: C2FPDAT |