Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 15                                                                |

| Program Memory Size        | 2KB (2K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | A/D 15x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                              |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f852-c-imr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 20.4.2. Center Aligned PWM                                      | 161 |

|-----------------------------------------------------------------|-----|

| 20.4.3. 8 to11-bit Pulse Width Modulator Modes                  |     |

| 20.4.4. 16-Bit Pulse Width Modulator Mode                       |     |

| 20.5. Comparator Clear Function                                 |     |

| 20.6. PCA Control Registers                                     |     |

| 21. Port I/O (Port 0, Port 1, Port 2, Crossbar, and Port Match) |     |

| 21.1. General Port I/O Initialization.                          |     |

| 21.2. Assigning Port I/O Pins to Analog and Digital Functions   |     |

| 21.2.1. Assigning Port I/O Pins to Analog Functions             |     |

| 21.2.2. Assigning Port I/O Pins to Digital Functions            |     |

| 21.2.3. Assigning Port I/O Pins to Fixed Digital Functions      |     |

| 21.3. Priority Crossbar Decoder                                 |     |

| 21.4. Port I/O Modes of Operation                               |     |

| 21.4.1. Configuring Port Pins For Analog Modes                  |     |

| 21.4.2. Configuring Port Pins For Digital Modes                 |     |

| 21.4.3. Port Drive Strength                                     |     |

| 21.5. Port Match                                                |     |

| 21.6. Direct Read/Write Access to Port I/O Pins                 |     |

| 21.7. Port I/O and Pin Configuration Control Registers          |     |

| 22. Reset Sources and Supply Monitor                            | 211 |

| 22.1. Power-On Reset                                            |     |

| 22.2. Power-Fail Reset / Supply Monitor                         |     |

| 22.3. Enabling the VDD Monitor                                  |     |

| 22.4. External Reset                                            |     |

| 22.5. Missing Clock Detector Reset                              |     |

| 22.6. Comparator0 Reset                                         |     |

| 22.7. Watchdog Timer Reset                                      |     |

| 22.8. Flash Error Reset                                         |     |

| 22.9. Software Reset                                            |     |

| 22.10. Reset Sources Control Registers                          | 215 |

| 22.11. Supply Monitor Control Registers                         |     |

| 23. Serial Peripheral Interface (SPI0)                          | 217 |

| 23.1. Signal Descriptions                                       |     |

| 23.1.1. Master Out, Slave In (MOSI)                             |     |

| 23.1.2. Master In, Slave Out (MISO)                             | 218 |

| 23.1.3. Serial Clock (SCK)                                      | 218 |

| 23.1.4. Slave Select (NSS)                                      | 218 |

| 23.2. SPI0 Master Mode Operation                                | 219 |

| 23.3. SPI0 Slave Mode Operation                                 | 221 |

| 23.4. SPI0 Interrupt Sources                                    | 221 |

| 23.5. Serial Clock Phase and Polarity                           | 221 |

| 23.6. SPI Special Function Registers                            | 223 |

| 23.7. SPI Control Registers                                     |     |

| 24. System Management Bus / I2C (SMBus0)                        |     |

| 24.1. Supporting Documents                                      | 234 |

| Pin Name | Туре          | Pin Numbers   | Crossbar Capability | Additional Digital Functions | Analog Functions |

|----------|---------------|---------------|---------------------|------------------------------|------------------|

| N/C      | No Connection | 1<br>13<br>24 |                     |                              |                  |

### Table 3.1. Pin Definitions for C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU

| Pin Name      | Туре                            | Pin Numbers | Crossbar Capability | Additional Digital Functions | Analog Functions            |

|---------------|---------------------------------|-------------|---------------------|------------------------------|-----------------------------|

| P1.1          | Standard I/O                    | 10          | Yes                 | P1MAT.1                      | ADC0.9<br>CP1P.3<br>CP1N.3  |

| P1.2          | Standard I/O                    | 9           | Yes                 | P1MAT.2                      | ADC0.10<br>CP1P.4<br>CP1N.4 |

| P1.3          | Standard I/O                    | 8           | Yes                 | P1MAT.3                      | ADC0.11<br>CP1P.5<br>CP1N.5 |

| P2.0 /<br>C2D | Standard I/O /<br>C2 Debug Data | 7           |                     |                              |                             |

# Table 3.3. Pin Definitions for C8051F860/1/2/3/4/5-GS and C8051F860/1/2/3/4/5-IS

| Ordering Part Number | Flash Memory (kB) | RAM (Bytes) | Digital Port I/Os (Total) | Number of ADC0 Channels | I/O with Comparator 0/1 Inputs | Pb-free (RoHS Compliant) | AEC-Q100 Qualified | Temperature Range | Package |

|----------------------|-------------------|-------------|---------------------------|-------------------------|--------------------------------|--------------------------|--------------------|-------------------|---------|

| C8051F850-C-GM       | 8                 | 512         | 16                        | 15                      | 15                             | $\checkmark$             | $\checkmark$       | -40 to 85 °C      | QFN-20  |

| C8051F850-C-GU       | 8                 | 512         | 18                        | 16                      | 16                             | ~                        | $\checkmark$       | -40 to 85 °C      | QSOP-24 |

| C8051F851-C-GM       | 4                 | 512         | 16                        | 15                      | 15                             | ~                        | ~                  | -40 to 85 °C      | QFN-20  |

| C8051F851-C-GU       | 4                 | 512         | 18                        | 16                      | 16                             | $\checkmark$             | $\checkmark$       | -40 to 85 °C      | QSOP-24 |

| C8051F852-C-GM       | 2                 | 256         | 16                        | 15                      | 15                             | $\checkmark$             | $\checkmark$       | -40 to 85 °C      | QFN-20  |

| C8051F852-C-GU       | 2                 | 256         | 18                        | 16                      | 16                             | $\checkmark$             | $\checkmark$       | -40 to 85 °C      | QSOP-24 |

| C8051F853-C-GM       | 8                 | 512         | 16                        |                         | 15                             | $\checkmark$             | $\checkmark$       | -40 to 85 °C      | QFN-20  |

| C8051F853-C-GU       | 8                 | 512         | 18                        | —                       | 16                             | ~                        | ~                  | -40 to 85 °C      | QSOP-24 |

| C8051F854-C-GM       | 4                 | 512         | 16                        | —                       | 15                             | ~                        | ~                  | -40 to 85 °C      | QFN-20  |

| C8051F854-C-GU       | 4                 | 512         | 18                        |                         | 16                             | ~                        | ~                  | -40 to 85 °C      | QSOP-24 |

| C8051F855-C-GM       | 2                 | 256         | 16                        |                         | 15                             | ~                        | ~                  | -40 to 85 °C      | QFN-20  |

| C8051F855-C-GU       | 2                 | 256         | 18                        |                         | 16                             | ~                        | ~                  | -40 to 85 °C      | QSOP-24 |

| C8051F860-C-GS       | 8                 | 512         | 13                        | 12                      | 12                             | ~                        | $\checkmark$       | -40 to 85 °C      | SOIC-16 |

| C8051F861-C-GS       | 4                 | 512         | 13                        | 12                      | 12                             | $\checkmark$             | ~                  | -40 to 85 °C      | SOIC-16 |

| C8051F862-C-GS       | 2                 | 256         | 13                        | 12                      | 12                             | $\checkmark$             | ~                  | -40 to 85 °C      | SOIC-16 |

| C8051F863-C-GS       | 8                 | 512         | 13                        |                         | 12                             | $\checkmark$             | ~                  | -40 to 85 °C      | SOIC-16 |

| C8051F864-C-GS       | 4                 | 512         | 13                        |                         | 12                             | $\checkmark$             | $\checkmark$       | -40 to 85 °C      | SOIC-16 |

| C8051F865-C-GS       | 2                 | 256         | 13                        | _                       | 12                             | $\checkmark$             | $\checkmark$       | -40 to 85 °C      | SOIC-16 |

Table 4.1. Product Selection Guide

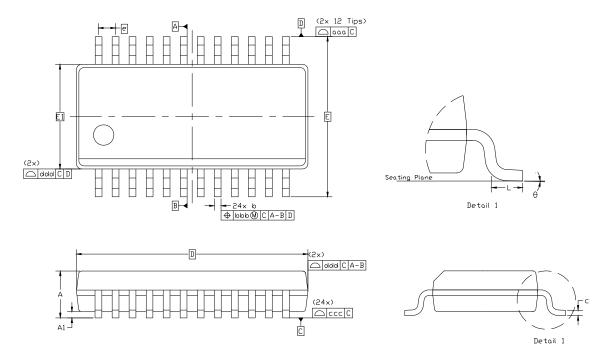

# 5. **QSOP-24** Package Specifications

Figure 5.1. QSOP-24 Package Drawing

| Min      | Mana     |      |           |           |      |      |

|----------|----------|------|-----------|-----------|------|------|

|          | Nom      | Max  | Dimension | Min       | Nom  | Мах  |

| _        | _        | 1.75 | е         | 0.635 BSC |      |      |

| 0.10     | _        | 0.25 | L         | 0.40      |      | 1.27 |

| 0.20     | _        | 0.30 | θ         | 0°        |      | 8º   |

| 0.10     | _        | 0.25 | aaa       | 0.20      |      |      |

| 8.65 BSC |          |      | bbb       |           | 0.18 |      |

| 6.00 BSC |          |      | CCC       |           | 0.10 |      |

|          | 3.90 BSC |      | ddd       |           | 0.10 |      |

|          |          |      |           |           |      |      |

# Table 5.1. QSOP-24 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# C8051F85x/86x

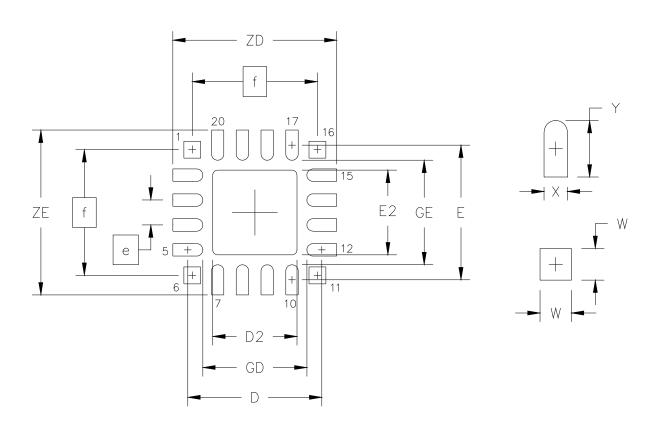

Figure 6.2. QFN-20 Landing Diagram

| Register | Address | Register Description     | Page |

|----------|---------|--------------------------|------|

| SPIODAT  | 0xA3    | SPI0 Data                | 232  |

| TCON     | 0x88    | Timer 0/1 Control        | 271  |

| TH0      | 0x8C    | Timer 0 High Byte        | 275  |

| TH1      | 0x8D    | Timer 1 High Byte        | 276  |

| TL0      | 0x8A    | Timer 0 Low Byte         | 273  |

| TL1      | 0x8B    | Timer 1 Low Byte         | 274  |

| TMOD     | 0x89    | Timer 0/1 Mode           | 272  |

| TMR2CN   | 0xC8    | Timer 2 Control          | 277  |

| TMR2H    | 0xCD    | Timer 2 High Byte        | 282  |

| TMR2L    | 0xCC    | Timer 2 Low Byte         | 281  |

| TMR2RLH  | 0xCB    | Timer 2 Reload High Byte | 280  |

| TMR2RLL  | 0xCA    | Timer 2 Reload Low Byte  | 279  |

| TMR3CN   | 0x91    | Timer 3 Control          | 283  |

| TMR3H    | 0x95    | Timer 3 High Byte        | 288  |

| TMR3L    | 0x94    | Timer 3 Low Byte         | 287  |

| TMR3RLH  | 0x93    | Timer 3 Reload High Byte | 286  |

| TMR3RLL  | 0x92    | Timer 3 Reload Low Byte  | 285  |

| VDM0CN   | 0xFF    | Supply Monitor Control   | 216  |

| WDTCN    | 0x97    | Watchdog Timer Control   | 300  |

| XBR0     | 0xE1    | Port I/O Crossbar 0      | 193  |

| XBR1     | 0xE2    | Port I/O Crossbar 1      | 194  |

| XBR2     | 0xE3    | Port I/O Crossbar 2      | 195  |

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted               | Permitted         | N/A               |

|--------------------------------------------------------------------------|-------------------------|-------------------|-------------------|

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted           | Flash Error Reset | Permitted         |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted               | Permitted         | N/A               |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | C2 Device Erase<br>Only | Flash Error Reset | Flash Error Reset |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted           | Flash Error Reset | Flash Error Reset |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted           | Flash Error Reset | Flash Error Reset |

| Read, Write or Erase Reserved Area                                       | Not Permitted           | Flash Error Reset | Flash Error Reset |

# Table 10.1. Flash Security Summary (Continued)

C2 Device Erase—Erases all flash pages including the page containing the Lock Byte.

Flash Error Reset — Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

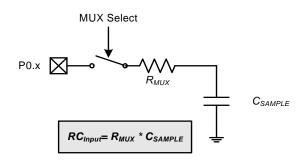

*n* is the ADC resolution in bits (8/10/12).

**Note:** The value of CSAMPLE depends on the PGA Gain. See electrical specifications for details.

# Figure 14.4. ADC0 Equivalent Input Circuits

#### 14.2.5. Gain Setting

The ADC has gain settings of 1x and 0.5x. In 1x mode, the full scale reading of the ADC is determined directly by VREF. In 0.5x mode, the full-scale reading of the ADC occurs when the input voltage is VREF x 2. The 0.5x gain setting can be useful to obtain a higher input voltage range when using a small VREF voltage, or to measure input voltages that are between VREF and VDD. Gain settings for the ADC are controlled by the ADGN bit in register ADC0CF. Note that even with a gain setting of 0.5, voltages above the supply rail cannot be measured directly by the ADC.

# 14.3. 8-Bit Mode

Setting the ADC08BE bit in register ADC0CF to 1 will put the ADC in 8-bit mode. In 8-bit mode, only the 8 MSBs of data are converted, allowing the conversion to be completed in fewer SAR clock cycles than a 10-bit conversion. The two LSBs of a conversion are always 00 in this mode, and the ADC0L register will always read back 0x00.

# 14.4. 12-Bit Mode

When configured for 12-bit conversions, the ADC performs four 10-bit conversions using four different reference voltages and combines the results into a single 12-bit value. Unlike simple averaging techniques, this method provides true 12-bit resolution of AC or DC input signals without depending on noise to provide dithering. The converter also employs a hardware dynamic element matching algorithm that reconfigures the largest elements of the internal DAC for each of the four 10-bit conversions. This reconfiguration cancels any matching errors and enables the converter to achieve 12-bit linearity performance to go along with its 12-bit resolution.

The 12-bit mode is enabled by setting the AD12BE bit in register ADC0AC to logic 1 and configuring the ADC in burst mode (ADBMEN = 1) for four or more conversions. The conversion can be initiated using any of the conversion start sources, and the 12-bit result will appear in the ADC0H and ADC0L registers. Since the 12-bit result is formed from a combination of four 10-bit results, the maximum output value is 4 x (1023) = 4092, rather than the max value of  $(2^{12} - 1) = 4095$  that is produced by a traditional 12-bit converter. To further increase resolution, the burst mode repeat value may be configured to any multiple of four conversions. For example, if a repeat value of 16 is selected, the ADC0 output will be a 14-bit number (sum of four 12-bit numbers) with 13 effective bits of resolution.

The AD12SM bit in register ADC0TK controls when the ADC will track and sample the input signal. When AD12SM is set to 1, the selected input signal will be tracked before the first conversion of a set and held internally during all four conversions. When AD12SM is cleared to 0, the ADC will track and sample the selected input before each of the four conversions in a set. When maximum throughput (180-200 ksps) is

| Number of Instructions | 26 | 50 | 5 | 14 | 7 | 3 | 1 | 2 | 1 |

|------------------------|----|----|---|----|---|---|---|---|---|

|------------------------|----|----|---|----|---|---|---|---|---|

# **15.2.** Programming and Debugging Support

In-system programming of the flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

# 15.3. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 15.3.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 15.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

Rev. 1.0

# **17.3. Comparator Control Registers**

| Bit   | 7    | 6     | 5     | 4     | 3     | 2 | 1     | 0 |

|-------|------|-------|-------|-------|-------|---|-------|---|

| Name  | CPEN | CPOUT | CPRIF | CPFIF | СРНҮР |   | CPHYN |   |

| Туре  | RW   | R     | RW    | RW    | RW    |   | R     | W |

| Reset | 0    | 0     | 0     | 0     | 0     | 0 | 0     | 0 |

# Register 17.1. CPT0CN: Comparator 0 Control

# Table 17.5. CPT0CN Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                 |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CPEN  | Comparator 0 Enable Bit.         0: Comparator Disabled.         1: Comparator Enabled.                                                                                                                                  |

| 6   | CPOUT | Comparator 0 Output State Flag.0: Voltage on CP0P < CP0N.                                                                                                                                                                |

| 5   | CPRIF | <ul> <li>Comparator 0 Rising-Edge Flag. Must be cleared by software.</li> <li>0: No Comparator Rising Edge has occurred since this flag was last cleared.</li> <li>1: Comparator Rising Edge has occurred.</li> </ul>    |

| 4   | CPFIF | <ul> <li>Comparator 0 Falling-Edge Flag. Must be cleared by software.</li> <li>0: No Comparator Falling-Edge has occurred since this flag was last cleared.</li> <li>1: Comparator Falling-Edge has occurred.</li> </ul> |

| 3:2 | СРНҮР | Comparator 0 Positive Hysteresis Control Bits.00: Positive Hysteresis Disabled.01: Positive Hysteresis = 5 mV.10: Positive Hysteresis = 10 mV.11: Positive Hysteresis = 20 mV.                                           |

| 1:0 | CPHYN | Comparator 0 Negative Hysteresis Control Bits.00: Negative Hysteresis Disabled.01: Negative Hysteresis = 5 mV.10: Negative Hysteresis = 10 mV.11: Negative Hysteresis = 20 mV.                                           |

# 20. Programmable Counter Array (PCA0)

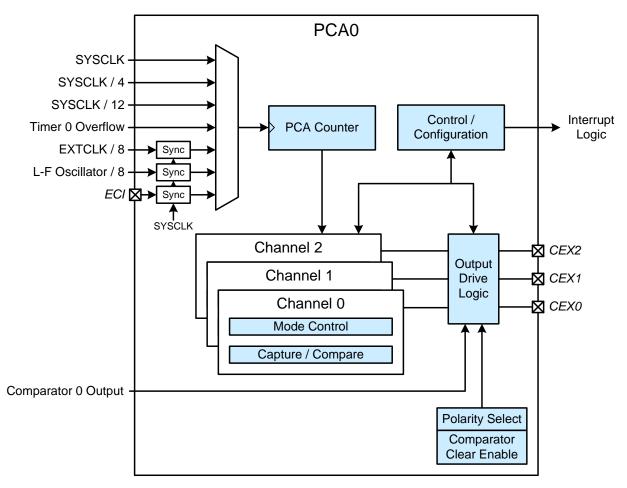

The Programmable Counter Array (PCA0) provides three channels of enhanced timer and PWM functionality while requiring less CPU intervention than standard counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. The counter/timer is driven by a programmable timebase that can select between seven sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, low frequency oscillator divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM. Additionally, all PWM modes support both center and edge-aligned operation. The external oscillator and LFO oscillator drives the system clock. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the crossbar to port I/O when enabled. The I/O signals have programmable polarity and Comparator 0 can optionally be used to perform a cycle-by-cycle kill operation on the PCA outputs. A PCA block diagram is shown in Figure 20.1

Figure 20.1. PCA0 Block Diagram

### 21.2.3. Assigning Port I/O Pins to Fixed Digital Functions

Fixed digital functions include external clock input as well as external event trigger functions, which can be used to trigger events such as an ADC conversion, fire an interrupt or wake the device from idle mode when a transition occurs on a digital I/O pin. The fixed digital functions do not require dedicated pins and will function on both GPIO pins and pins in use by the crossbar. Fixed digital functions cannot be used on pins configured for analog I/O. Table 21.3 shows all available fixed digital functions and the potential mapping of port I/O to each function.

| Function                      | Potentially Assignable Port Pins | SFR(s) used for<br>Assignment  |

|-------------------------------|----------------------------------|--------------------------------|

| External Interrupt 0          | P0.0 - P0.7                      | IT01CF                         |

| External Interrupt 1          | P0.0 - P0.7                      | IT01CF                         |

| Conversion Start (CNVSTR)     | P0.6                             | ADCOCN                         |

| External Clock Input (EXTCLK) | P0.3                             | OSCXCN                         |

| Port Match                    | P0.0 - P1.7                      | POMASK, POMAT<br>P1MASK, P1MAT |

# Table 21.3. Port I/O Assignment for Fixed Digital Functions

# 22.10. Reset Sources Control Registers

| Bit     | 7        | 6      | 5      | 4     | 3      | 2      | 1     | 0      |  |  |  |

|---------|----------|--------|--------|-------|--------|--------|-------|--------|--|--|--|

| Name    | Reserved | FERROR | CORSEF | SWRSF | WDTRSF | MCDRSF | PORSF | PINRSF |  |  |  |

| Туре    | R        | R      | RW     | RW    | R      | RW     | RW    | R      |  |  |  |

| Reset   | 0        | Х      | Х      | Х     | Х      | Х      | Х     | Х      |  |  |  |

| SEB Add |          |        |        |       |        |        |       |        |  |  |  |

#### Register 22.1. RSTSRC: Reset Source

R Address: 0xEl

#### Table 22.1. RSTSRC Register Bit Descriptions

| Bit | Name     | Function                                                                                                                              |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Must write reset value.                                                                                                               |

| 6   | FERROR   | Flash Error Reset Flag.                                                                                                               |

|     |          | This read-only bit is set to 1 if a flash read/write/erase error caused the last reset.                                               |

| 5   | CORSEF   | Comparator0 Reset Enable and Flag.                                                                                                    |

|     |          | Read: This bit reads 1 if Comparator0 caused the last reset.                                                                          |

|     |          | Write: Writing a 1 to this bit enables Comparator0 (active-low) as a reset source.                                                    |

| 4   | SWRSF    | Software Reset Force and Flag.                                                                                                        |

|     |          | Read: This bit reads 1 if last reset was caused by a write to SWRSF.                                                                  |

|     |          | Write: Writing a 1 to this bit forces a system reset.                                                                                 |

| 3   | WDTRSF   | Watchdog Timer Reset Flag.                                                                                                            |

|     |          | This read-only bit is set to 1 if a watchdog timer overflow caused the last reset.                                                    |

| 2   | MCDRSF   | Missing Clock Detector Enable and Flag.                                                                                               |

|     |          | Read: This bit reads 1 if a missing clock detector timeout caused the last reset.                                                     |

|     |          | Write: Writing a 1 to this bit enables the missing clock detector. The MCD triggers a reset if a missing clock condition is detected. |

| 1   | PORSF    | Power-On / Supply Monitor Reset Flag, and Supply Monitor Reset Enable.                                                                |

|     |          | Read: This bit reads 1 anytime a power-on or supply monitor reset has occurred.                                                       |

|     |          | Write: Writing a 1 to this bit enables the supply monitor as a reset source.                                                          |

| 0   | PINRSF   | HW Pin Reset Flag.                                                                                                                    |

|     |          | This read-only bit is set to 1 if the RST pin caused the last reset.                                                                  |

1. Reads and writes of the RSTSRC register access different logic in the device. Reading the register always returns status information to indicate the source of the most recent reset. Writing to the register activates certain options as reset sources. It is recommended to not use any kind of read-modify-write operation on this register.

2. When the PORSF bit reads back 1 all other RSTSRC flags are indeterminate.

3. Writing 1 to the PORSF bit when the supply monitor is not enabled and stabilized may cause a system reset.

# 22.11. Supply Monitor Control Registers

| Bit   | 7     | 6       | 5           | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------|---------|-------------|---|---|---|---|---|--|

| Name  | VDMEN | VDDSTAT | Reserved    |   |   |   |   |   |  |

| Туре  | RW    | R       |             | R |   |   |   |   |  |

| Reset | Х     | Х       | X X X X X X |   |   |   |   |   |  |

# Register 22.2. VDM0CN: Supply Monitor Control

SFR Address: 0xFF

# Table 22.2. VDM0CN Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN    | Supply Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |          | This bit turns the supply monitor circuit on/off. The supply monitor cannot generate sys-<br>tem resets until it is also selected as a reset source in register RSTSRC. Selecting the<br>supply monitor as a reset source before it has stabilized may generate a system reset. In<br>systems where this reset would be undesirable, a delay should be introduced between<br>enabling the supply monitor and selecting it as a reset source.<br>0: Supply Monitor Disabled.<br>1: Supply Monitor Enabled. |

| 6   | VDDSTAT  | Supply Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          | <ul> <li>This bit indicates the current power supply status (supply monitor output).</li> <li>0: V<sub>DD</sub> is at or below the supply monitor threshold.</li> <li>1: V<sub>DD</sub> is above the supply monitor threshold.</li> </ul>                                                                                                                                                                                                                                                                 |

| 5:0 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

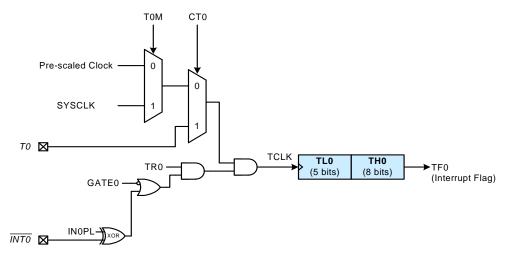

#### 25.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 in TCON is set and an interrupt will occur if Timer 0 interrupts are enabled.

The CT0 bit in the TMOD register selects the counter/timer's clock source. When CT0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register. Clearing CT selects the clock defined by the TOM bit in register CKCON. When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON.

Setting the TR0 bit enables the timer when either GATE0 in the TMOD register is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF. Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0, facilitating pulse width measurements.

| TR0                  | GATE0 | INT0 | Counter/Timer |  |  |  |  |

|----------------------|-------|------|---------------|--|--|--|--|

| 0                    | Х     | Х    | Disabled      |  |  |  |  |

| 1                    | 0     | Х    | Enabled       |  |  |  |  |

| 1                    | 1     | 0    | Disabled      |  |  |  |  |

| 1                    | 1     | 1    | Enabled       |  |  |  |  |

| Note: X = Don't Care |       |      |               |  |  |  |  |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT1 is used with Timer 1; the /INT1 polarity is defined by bit IN1PL in register IT01CF.

Figure 25.1. T0 Mode 0 Block Diagram

# Register 25.2. TCON: Timer 0/1 Control

| Bit                                 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Name                                | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |  |

| Туре                                | RW  |  |

| Reset                               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| SFR Address: 0x88 (bit-addressable) |     |     |     |     |     |     |     |     |  |

# Table 25.4. TCON Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                                                                                                        |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag.                                                                                                                                                                                                                                          |

|     |      | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                   |

| 6   | TR1  | Timer 1 Run Control.                                                                                                                                                                                                                                            |

|     |      | Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                                                    |

| 5   | TF0  | Timer 0 Overflow Flag.                                                                                                                                                                                                                                          |

|     |      | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                   |

| 4   | TR0  | Timer 0 Run Control.                                                                                                                                                                                                                                            |

|     |      | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                    |

| 3   | IE1  | External Interrupt 1.                                                                                                                                                                                                                                           |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                         |

| 2   | IT1  | Interrupt 1 Type Select.                                                                                                                                                                                                                                        |

|     |      | <ul> <li>This bit selects whether the configured INT1 interrupt will be edge or level sensitive. INT1 is configured active low or high by the IN1PL bit in register IT01CF.</li> <li>0: INT1 is level triggered.</li> <li>1: INT1 is edge triggered.</li> </ul> |

| 1   | IE0  | External Interrupt 0.                                                                                                                                                                                                                                           |

|     |      | This flag is set by hardware when an edge/level of type defined by IT0 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                         |

| 0   | IT0  | Interrupt 0 Type Select.                                                                                                                                                                                                                                        |

|     |      | <ul><li>This bit selects whether the configured INT0 interrupt will be edge or level sensitive. INT0 is configured active low or high by the IN0PL bit in register IT01CF.</li><li>0: INT0 is level triggered.</li><li>1: INT0 is edge triggered.</li></ul>     |

# Table 25.10. TMR2CN Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | T2XCLK | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |        | <ul> <li>This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.</li> <li>0: Timer 2 clock is the system clock divided by 12.</li> <li>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK).</li> </ul> |

# Register 25.15. TMR3RLH: Timer 3 Reload High Byte

| Bit               | 7       | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------------|---------|-----------------|---|---|---|---|---|---|--|

| Name              | TMR3RLH |                 |   |   |   |   |   |   |  |

| Туре              | RW      |                 |   |   |   |   |   |   |  |

| Reset             | 0       | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

| SFR Address: 0x93 |         |                 |   |   |   |   |   |   |  |

# Table 25.17. TMR3RLH Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                     |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3RLH | Timer 3 Reload High Byte.                                                                                                                                                                    |

|     |         | When operating in one of the auto-reload modes, TMR3RLH holds the reload value for the high byte of Timer 3 (TMR3H). When oeprating in capture mode, TMR3RLH is the captured value of TMR3H. |

# 28.2. Temperature Sensor Offset and Slope

The temperature sensor slope and offset characteristics of Revision B devices are different than the slope and offset characteristics of Revision C devices. The differences are:

| Parameter  | Symbol           | Test Condition        | Min | Тур  | Max | Unit  |

|------------|------------------|-----------------------|-----|------|-----|-------|

| Revision B |                  |                       |     |      |     |       |

| Offset     | V <sub>OFF</sub> | T <sub>A</sub> = 0 °C | _   | 713  | _   | mV    |

| Slope      | М                |                       |     | 2.67 | _   | mV/°C |

| Revision C |                  |                       |     |      |     |       |

| Offset     | V <sub>OFF</sub> | $T_A = 0 \ ^{\circ}C$ | _   | 757  | _   | mV    |

| Slope      | М                |                       |     | 2.85 | _   | mV/°C |

Firmware that uses the slope and offset of the temperature sensor to calculate the temperature from the sensor ADC reading can detect the revision of the device by reading the REVID register and adjust the slope and offset calculations based on the result. A REVID value of 0x01 indicates a Revision B device, and a REVID value of 0x02 indicates a Revision C device.

# 28.3. Flash Endurance

The flash endurance, or number of times the flash may be written and erased, on some Revision B devices may be lower than expected. Table 1.4 specifies a minimum Endurance (Write/Erase Cycles) as 20000, but some Revision B devices may support a minimum of ~5000 cycles.

# 28.4. Latch-Up Performance

Pulling the device pins below ground and drawing significant current (~3.5 mA) can cause a Power-On Reset event with Revision B devices. Some pins, like P0.0 and P0.1, are more susceptible to this behavior than others. This behavior is outside normal operating parameters and would typically be seen during latch-up or ESD performance testing.

# 28.5. Unique Identifier

Revision B devices do not implement the unique identifier described in "Device Identification and Unique Identifier" on page 68.