Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 15                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                              |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f853-c-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1.2. Power Consumption (Continued |

|-----------------------------------------|

|-----------------------------------------|

| Parameter                                | Symbol             | Test Condition                                                                                                     | Min | Тур  | Max  | Unit |

|------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| Digital Core Supply Current (            | (–Ix Device        | s, -40°C to +125°C)                                                                                                | ı   |      | 1    |      |

| Normal Mode—Full speed                   | I <sub>DD</sub>    | F <sub>SYSCLK</sub> = 24.5 MHz <sup>2</sup>                                                                        |     | 4.45 | 5.25 | mA   |

| with code executing from flash           |                    | F <sub>SYSCLK</sub> = 1.53 MHz <sup>2</sup>                                                                        |     | 915  | 1600 | μA   |

|                                          |                    | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup> , T <sub>A</sub> = 25 °C                                                 |     | 250  | 290  | μA   |

|                                          |                    | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup>                                                                          |     | 250  | 725  | μA   |

| Idle Mode—Core halted with               | I <sub>DD</sub>    | F <sub>SYSCLK</sub> = 24.5 MHz <sup>2</sup>                                                                        |     | 2.05 | 2.6  | mA   |

| peripherals running                      |                    | F <sub>SYSCLK</sub> = 1.53 MHz <sup>2</sup>                                                                        |     | 550  | 1000 | μA   |

|                                          |                    | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup> , T <sub>A</sub> = 25 °C                                                 |     | 125  | 130  | μA   |

|                                          |                    | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup>                                                                          | _   | 125  | 550  | μA   |

| Stop Mode—Core halted and                | I <sub>DD</sub>    | Internal LDO ON, T <sub>A</sub> = 25 °C                                                                            | _   | 105  | 120  | μA   |

| all clocks stopped, Supply monitor off.  |                    | Internal LDO ON                                                                                                    | _   | 105  | 270  | μA   |

|                                          |                    | Internal LDO OFF                                                                                                   | _   | 0.2  | _    | μA   |

| Analog Peripheral Supply Cu              | irrents (Bo        | th –Gx and –Ix Devices)                                                                                            |     |      | I    |      |

| High-Frequency Oscillator                | I <sub>HFOSC</sub> | Operating at 24.5 MHz,<br>T <sub>A</sub> = 25 °C                                                                   | _   | 155  | _    | μA   |

| Low-Frequency Oscillator                 | I <sub>LFOSC</sub> | Operating at 80 kHz,<br>T <sub>A</sub> = 25 °C                                                                     | _   | 3.5  | _    | μA   |

| ADC0 Always-on <sup>4</sup>              | I <sub>ADC</sub>   | 800 ksps, 10-bit conversions or<br>200 ksps, 12-bit conversions<br>Normal bias settings<br>V <sub>DD</sub> = 3.0 V | _   | 845  | 1200 | μA   |

|                                          |                    | 250 ksps, 10-bit conversions or<br>62.5 ksps 12-bit conversions<br>Low power bias settings<br>$V_{DD} = 3.0 V$     | _   | 425  | 580  | μA   |

| ADC0 Burst Mode, 10-bit sin-             | I <sub>ADC</sub>   | 200 ksps, V <sub>DD</sub> = 3.0 V                                                                                  |     | 370  |      | μA   |

| gle conversions, external ref-<br>erence |                    | 100 ksps, V <sub>DD</sub> = 3.0 V                                                                                  | —   | 185  |      | μA   |

|                                          |                    | 10 ksps, V <sub>DD</sub> = 3.0 V                                                                                   | _   | 19   | _    | μA   |

Notes:

1. Currents are additive. For example, where  $I_{DD}$  is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

2. Includes supply current from internal regulator, supply monitor, and High Frequency Oscillator.

3. Includes supply current from internal regulator, supply monitor, and Low Frequency Oscillator.

4. ADC0 always-on power excludes internal reference supply current.

5. The internal reference is enabled as-needed when operating the ADC in burst mode to save power.

### Table 1.3. Reset and Supply Monitor

| Parameter                                                            | Symbol            | Test Condition                                                | Min  | Тур   | Max  | Unit |

|----------------------------------------------------------------------|-------------------|---------------------------------------------------------------|------|-------|------|------|

| V <sub>DD</sub> Supply Monitor Threshold                             | V <sub>VDDM</sub> |                                                               | 1.85 | 1.95  | 2.1  | V    |

| Power-On Reset (POR) Threshold                                       | V <sub>POR</sub>  | Rising Voltage on V <sub>DD</sub>                             | —    | 1.4   |      | V    |

|                                                                      |                   | Falling Voltage on $V_{DD}$                                   | 0.75 | —     | 1.36 | V    |

| V <sub>DD</sub> Ramp Time                                            | t <sub>RMP</sub>  | Time to $V_{DD} \ge 2.2 \text{ V}$                            | 10   | —     |      | μs   |

| Reset Delay from POR                                                 | t <sub>POR</sub>  | Relative to V <sub>DD</sub> ≥<br>V <sub>POR</sub>             | 3    | 10    | 31   | ms   |

| Reset Delay from non-POR source                                      | t <sub>RST</sub>  | Time between release<br>of reset source and<br>code execution | _    | 39    | _    | μs   |

| RST Low Time to Generate Reset                                       | t <sub>RSTL</sub> |                                                               | 15   | _     |      | μs   |

| Missing Clock Detector Response<br>Time (final rising edge to reset) | t <sub>MCD</sub>  | F <sub>SYSCLK</sub> > 1 MHz                                   |      | 0.625 | 1.2  | ms   |

| Missing Clock Detector Trigger<br>Frequency                          | F <sub>MCD</sub>  |                                                               | _    | 7.5   | 13.5 | kHz  |

| $V_{DD}$ Supply Monitor Turn-On Time                                 | t <sub>MON</sub>  |                                                               | _    | 2     |      | μs   |

### Table 1.4. Flash Memory

| Parameter                                               | Symbol             | Test Condition                              | Min | Тур  | Max | Units  |

|---------------------------------------------------------|--------------------|---------------------------------------------|-----|------|-----|--------|

| Write Time <sup>1,2</sup>                               | t <sub>WRITE</sub> | One Byte,<br>F <sub>SYSCLK</sub> = 24.5 MHz | 19  | 20   | 21  | μs     |

| Erase Time <sup>1,2</sup>                               | t <sub>ERASE</sub> | One Page,<br>F <sub>SYSCLK</sub> = 24.5 MHz | 5.2 | 5.35 | 5.5 | ms     |

| V <sub>DD</sub> Voltage During Programming <sup>3</sup> | V <sub>PROG</sub>  |                                             | 2.2 | _    | 3.6 | V      |

| Endurance (Write/Erase Cycles)                          | N <sub>WE</sub>    |                                             | 20k | 100k | —   | Cycles |

Notes:

1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

2. The internal High-Frequency Oscillator has a programmable output frequency using the OSCICL register, which is factory programmed to 24.5 MHz. If user firmware adjusts the oscillator speed, it must be between 22 and 25 MHz during any flash write or erase operation. It is recommended to write the OSCICL register back to its reset value when writing or erasing flash.

3. Flash can be safely programmed at any voltage above the supply monitor threshold ( $V_{VDDM}$ ).

4. Data Retention Information is published in the Quarterly Quality and Reliability Report.

### 2.1.3.1. Normal Mode

Normal mode encompasses the typical full-speed operation. The power consumption of the device in this mode will vary depending on the system clock speed and any analog peripherals that are enabled.

#### 2.1.3.2. Idle Mode

Setting the IDLE bit in PCON causes the hardware to halt the CPU and enter idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the IDLE bit to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

#### 2.1.3.3. Stop Mode (Regulator On)

Setting the STOP bit in PCON when STOPCF in REGOCN is clear causes the controller core to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the internal oscillator, CPU, and all digital peripherals are stopped. Each analog peripheral may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset.

### 2.1.3.4. Shutdown Mode (Regulator Off)

Shutdown mode is an extension of the normal stop mode operation. Setting the STOP bit in PCON when STOPCF in REGOCN is also set causes the controller core to enter shutdown mode as soon as the instruction that sets the bit completes execution, and then the internal regulator is powered down. In shutdown mode, all core functions, memories and peripherals are powered off. An external pin reset or power-on reset is required to exit shutdown mode.

### 2.2. I/O

#### 2.2.1. General Features

The C8051F85x/86x ports have the following features:

- Push-pull or open-drain output modes and analog or digital modes.

- Port Match allows the device to recognize a change on a port pin value and wake from idle mode or generate an interrupt.

- Internal pull-up resistors can be globally enabled or disabled.

- Two external interrupts provide unique interrupt vectors for monitoring time-critical events.

- Above-rail tolerance allows 5 V interface when device is powered.

#### 2.2.2. Crossbar

The C8051F85x/86x devices have a digital peripheral crossbar with the following features:

- Flexible peripheral assignment to port pins.

- Pins can be individually skipped to move peripherals as needed for design or layout considerations.

The crossbar has a fixed priority for each I/O function and assigns these functions to the port pins. When a digital resource is selected, the least-significant unassigned port pin is assigned to that resource. If a port pin is assigned, the crossbar skips that pin when assigning the next selected resource. Additionally, the crossbar will skip port pins whose associated bits in the PnSKIP registers are set. This provides some flexibility when designing a system: pins involved with sensitive analog measurements can be moved away from digital I/O and peripherals can be moved around the chip as needed to ease layout constraints.

| Symbol | Millimeters |      | Symbol | Millim | neters |

|--------|-------------|------|--------|--------|--------|

|        | Min         | Max  |        | Min    | Max    |

| D      | 2.71 REF    |      | GE     | 2.10   | _      |

| D2     | 1.60        | 1.80 | W      | _      | 0.34   |

| е      | 0.50 BSC    |      | Х      | —      | 0.28   |

| E      | 2.71 REF    |      | Y      | 0.61   | REF    |

| E2     | 1.60        | 1.80 | ZE     | —      | 3.31   |

| f      | 2.53 BSC    |      | ZD     | —      | 3.31   |

| GD     | 2.10        | —    |        |        |        |

### Table 6.2. QFN-20 Landing Diagram Dimensions

#### Notes: General

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Notes: Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Notes: Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- **4.** A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides approximately 70% solder paste coverage on the pad, which is optimum to assure correct component stand-off.

#### Notes: Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# Register 10.2. FLKEY: Flash Lock and Key

|                 |       | · · · |   |   | • |   |                 |       |  |  |  |

|-----------------|-------|-------|---|---|---|---|-----------------|-------|--|--|--|

|                 | FLKEY |       |   |   |   |   |                 |       |  |  |  |

| RW              |       |       |   |   |   |   |                 |       |  |  |  |

| 0 0 0 0 0 0 0 0 |       |       |   |   |   |   |                 | Reset |  |  |  |

|                 | 0     | 0     | 0 | 0 | 0 | 0 | 0<br>ress: 0xB7 |       |  |  |  |

# Table 10.3. FLKEY Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |       | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |       | This register provides a lock and key function for flash erasures and writes. Flash writes<br>and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY register. Flash<br>writes and erases are automatically disabled after the next write or erase is complete. If<br>any writes to FLKEY are performed incorrectly, or if a flash write or erase operation is<br>attempted while these operations are disabled, the flash will be permanently locked from<br>writes or erasures until the next device reset. If an application never writes to flash, it can<br>intentionally lock the flash by writing a non-0xA5 value to FLKEY from software.<br>Read:<br>When read, bits 1-0 indicate the current flash lock state.<br>00: Flash is write/erase locked.<br>01: The first key code has been written (0xA5).<br>10: Flash is unlocked (writes/erases allowed).<br>11: Flash writes/erases are disabled until the next reset. |

# Register 14.5. ADC0PWR: ADC0 Power Control

| Bit               | 7   | 6    | 5      | 4     | 3       | 2 | 1 | 0 |  |  |

|-------------------|-----|------|--------|-------|---------|---|---|---|--|--|

| Name              | ADE | BIAS | ADMXLP | ADLPM | ADPWR   |   |   |   |  |  |

| Туре              | R   | W    | RW     | RW    | RW      |   |   |   |  |  |

| Reset             | 0   | 0    | 0      | 0     | 1 1 1 1 |   |   | 1 |  |  |

| SFR Address: 0xDF |     |      |        |       |         |   |   |   |  |  |

# Table 14.8. ADC0PWR Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | ADBIAS | Bias Power Select.                                                                                                                                                                         |

|     |        | This field can be used to adjust the ADC's power consumption based on the conversion speed. Higher bias currents allow for faster conversion times.                                        |

|     |        | 00: Select bias current mode 0. Recommended to use modes 1, 2, or 3.                                                                                                                       |

|     |        | 01: Select bias current mode 1 (SARCLK <= 16 MHz).<br>10: Select bias current mode 2.                                                                                                      |

|     |        | 11: Select bias current mode 3 (SARCLK <= 4 MHz).                                                                                                                                          |

| 5   | ADMXLP | Mux and Reference Low Power Mode Enable.                                                                                                                                                   |

|     |        | Enables low power mode operation for the multiplexer and voltage reference buffers.                                                                                                        |

|     |        | 0: Low power mode disabled.                                                                                                                                                                |

|     |        | 1: Low power mode enabled (SAR clock < 4 MHz).                                                                                                                                             |

| 4   | ADLPM  | Low Power Mode Enable.                                                                                                                                                                     |

|     |        | This bit can be used to reduce power to the ADC's internal common mode buffer. It can be set to 1 to reduce power when tracking times in the application are longer (slower sample rates). |

|     |        | 0: Disable low power mode.                                                                                                                                                                 |

|     |        | 1: Enable low power mode (requires extended tracking time).                                                                                                                                |

| 3:0 | ADPWR  | Burst Mode Power Up Time.                                                                                                                                                                  |

|     |        | This field sets the time delay allowed for the ADC to power up from a low power state.<br>When ADTM is set, an additional 4 SARCLKs are added to this time.                                |

|     |        |                                                                                                                                                                                            |

|     |        | $T_{PWRTIME} = \frac{8 \times ADPWR}{F_{HFOSC}}$                                                                                                                                           |

|     |        |                                                                                                                                                                                            |

## Table 15.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic         | Description                                |   | Clock<br>Cycles |

|------------------|--------------------------------------------|---|-----------------|

| DJNZ direct, rel | Decrement direct byte and jump if not zero | 3 | 3/4             |

| NOP              | No operation                               | 1 | 1               |

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

bit—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

# Register 15.3. SP: Stack Pointer

| Bit               | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|----|---|---|---|---|---|---|---|--|--|

| Name              | SP |   |   |   |   |   |   |   |  |  |

| Туре              | RW |   |   |   |   |   |   |   |  |  |

| Reset             | 0  | 0 | 0 | 0 | 0 | 1 | 1 | 1 |  |  |

| SFR Address: 0x81 |    |   |   |   |   |   |   |   |  |  |

# Table 15.4. SP Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                       |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP   | Stack Pointer.                                                                                                                                                                 |

|     |      | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

| CMXP Setting in<br>Register CPT1MX | Signal Name | QSOP24 Pin Name           | QFN20 Pin Name | SOIC16 Pin Name |  |  |

|------------------------------------|-------------|---------------------------|----------------|-----------------|--|--|

| 0000                               | CP1P.0      | P1.0                      | P1.0           | P0.6            |  |  |

| 0001                               | CP1P.1      | P1.1                      | P1.1           | P0.7            |  |  |

| 0010                               | CP1P.2      | P1.2                      | P1.2           | P1.0            |  |  |

| 0011                               | CP1P.3      | P1.3                      | P1.3           | P1.1            |  |  |

| 0100                               | CP1P.4      | P1.4                      | P1.4           | P1.2            |  |  |

| 0101                               | CP1P.5      | P1.5                      | P1.5           | P1.3            |  |  |

| 0110                               | CP1P.6      | P1.6                      | P1.6           | Reserved        |  |  |

| 0111                               | CP1P.7      | P1.7 Reserved             |                | Reserved        |  |  |

| 1000                               | LDO         | Internal 1.8 V LDO Output |                |                 |  |  |

| 1001-1111                          | None        | No connection             |                |                 |  |  |

Table 17.3. CMP1 Positive Input Multiplexer Channels

Table 17.4. CMP1 Negative Input Multiplexer Channels

| CMXN Setting in<br>Register CPT1MX | Signal Name | QSOP24 Pin Name | QFN20 Pin Name | SOIC16 Pin Name |  |  |

|------------------------------------|-------------|-----------------|----------------|-----------------|--|--|

| 0000                               | CP1N.0      | P1.0            | P1.0           | P0.6            |  |  |

| 0001                               | CP1N.1      | P1.1            | P1.1           | P0.7            |  |  |

| 0010                               | CP1N.2      | P1.2            | P1.2           | P1.0            |  |  |

| 0011                               | CP1N.3      | P1.3            | P1.3           | P1.1            |  |  |

| 0100                               | CP1N.4      | P1.4            | P1.4           | P1.2            |  |  |

| 0101                               | CP1N.5      | P1.5            | P1.5           | P1.3            |  |  |

| 0110                               | CP1N.6      | P1.6            | P1.6           | Reserved        |  |  |

| 0111                               | CP1N.7      | P1.7            | Reserved       | Reserved        |  |  |

| 1000                               | GND         |                 | GND            |                 |  |  |

| 1001-1111                          | None        | No connection   |                |                 |  |  |

## **17.2.** Functional Description

The comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the port pins: a synchronous "latched" output (CPn), or an asynchronous "raw" output (CPnA). The asynchronous CPnA signal is available even when the system clock is not active. This allows the comparator to operate and generate an output with the device in STOP mode.

When disabled, the comparator output (if assigned to a port I/O pin via the crossbar) defaults to the logic low state, and the power supply to the comparator is turned off.

The comparator response time may be configured in software via the CPTnMD register. Selecting a longer response time reduces the comparator supply current.

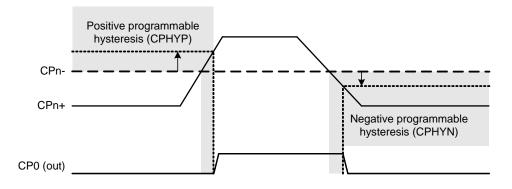

#### Figure 17.2. Comparator Hysteresis Plot

The comparator hysteresis is software-programmable via its Comparator Control register CPTnCN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The comparator hysteresis is programmable using the CPHYN and CPHYP fields in the Comparator Control Register CPTnCN. The amount of negative hysteresis voltage is determined by the settings of the CPHYN bits. As shown in Figure 17.2, settings of 20, 10, or 5 mV (nominal) of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. The CPFIF flag is set to logic 1 upon a comparator falling-edge occurrence, and the CPRIF flag is set to logic 1 upon the comparator rising-edge occurrence. Once set, these bits remain set until cleared by software. The comparator rising-edge interrupt mask is enabled by setting CPRIE to a logic 1. The comparator falling-edge interrupt mask is enabled by setting CPFIE to a logic 1.

The output state of the comparator can be obtained at any time by reading the CPOUT bit. The comparator is enabled by setting the CPEN bit to logic 1, and is disabled by clearing this bit to logic 0.

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed, before enabling comparator interrupts.

# Register 17.2. CPT0MD: Comparator 0 Mode

| Bit     | 7                 | 6        | 5     | 4     | 3        | 2 | 1    | 0 |  |  |

|---------|-------------------|----------|-------|-------|----------|---|------|---|--|--|

| Name    | CPLOUT            | Reserved | CPRIE | CPFIE | Reserved |   | CPMD |   |  |  |

| Туре    | RW                | R        | RW    | RW    | R        |   | RW   |   |  |  |

| Reset   | 0                 | 0        | 0     | 0     | 0        | 0 | 1    | 0 |  |  |

| SFR Add | SFR Address: 0x9D |          |       |       |          |   |      |   |  |  |

# Table 17.6. CPT0MD Register Bit Descriptions

| Bit | Name     | Function                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------|

| 7   | CPLOUT   | Comparator 0 Latched Output Flag.                                                        |

|     |          | This bit represents the comparator output value at the most recent PCA counter overflow. |

|     |          | 0: Comparator output was logic low at last PCA overflow.                                 |

|     |          | 1: Comparator output was logic high at last PCA overflow.                                |

| 6   | Reserved | Must write reset value.                                                                  |

| 5   | CPRIE    | Comparator 0 Rising-Edge Interrupt Enable.                                               |

|     |          | 0: Comparator Rising-Edge interrupt disabled.                                            |

|     |          | 1: Comparator Rising-Edge interrupt enabled.                                             |

| 4   | CPFIE    | Comparator 0 Falling-Edge Interrupt Enable.                                              |

|     |          | 0: Comparator Falling-Edge interrupt disabled.                                           |

|     |          | 1: Comparator Falling-Edge interrupt enabled.                                            |

| 3:2 | Reserved | Must write reset value.                                                                  |

| 1:0 | CPMD     | Comparator 0 Mode Select.                                                                |

|     |          | These bits affect the response time and power consumption of the comparator.             |

|     |          | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)                            |

|     |          | 01: Mode 1                                                                               |

|     |          | 10: Mode 2                                                                               |

|     |          | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)                             |

# Register 20.9. PCA0CPH0: PCA Capture Module High Byte

| Bit     | 7                 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------------------|----------|---|---|---|---|---|---|--|

| Name    |                   | PCA0CPH0 |   |   |   |   |   |   |  |

| Туре    | RW                |          |   |   |   |   |   |   |  |

| Reset   | 0                 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Add | SFR Address: 0xFC |          |   |   |   |   |   |   |  |

# Table 20.11. PCA0CPH0 Register Bit Descriptions

| Bit     | Name                                                                  | Function                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0     | PCA0CPH0                                                              | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                |  |  |  |  |  |

|         |                                                                       | The PCA0CPH0 register holds the high byte (MSB) of the 16-bit capture module. This register address also allows access to the high byte of the corresponding PCA channels auto-reload value for 9 to 11-bit PWM mode. The ARSEL bit in register PCA0PWM controls which register is accessed. |  |  |  |  |  |

| Note: A | Note: A write to this register will set the module's ECOM bit to a 1. |                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

# Register 20.15. PCA0CPH1: PCA Capture Module High Byte

| Bit     | 7                 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------------------|----------|---|---|---|---|---|---|--|

| Name    |                   | PCA0CPH1 |   |   |   |   |   |   |  |

| Туре    | RW                |          |   |   |   |   |   |   |  |

| Reset   | 0                 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Add | SFR Address: 0xEA |          |   |   |   |   |   |   |  |

# Table 20.17. PCA0CPH1 Register Bit Descriptions

| Bit     | Name                                                                 | Function                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0     | PCA0CPH1                                                             | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                |  |  |  |  |  |

|         |                                                                      | The PCA0CPH1 register holds the high byte (MSB) of the 16-bit capture module. This register address also allows access to the high byte of the corresponding PCA channels auto-reload value for 9 to 11-bit PWM mode. The ARSEL bit in register PCA0PWM controls which register is accessed. |  |  |  |  |  |

| Note: A | Note: A write to this register will set the modules ECOM bit to a 1. |                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

# Register 21.5. P0MASK: Port 0 Mask

| Bit               | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|--------|---|---|---|---|---|---|---|

| Name              | POMASK |   |   |   |   |   |   |   |

| Туре              | RW     |   |   |   |   |   |   |   |

| Reset             | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0xFE |        |   |   |   |   |   |   |   |

# Table 21.8. P0MASK Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MASK | Port 0 Mask Value.                                                                                                                                                                                |

|     |        | Selects P0 pins to be compared to the corresponding bits in P0MAT.<br>0: P0.x pin logic value is ignored and will cause a port mismatch event.<br>1: P0.x pin logic value is compared to P0MAT.x. |

## 23.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 23.2 shows a connection diagram between two master devices and a single slave in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 23.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 23.4 shows a connection diagram for a master device and a slave device in 4-wire mode.

| Parameter                | Description                                                         | Min                          | Max                     | Units |

|--------------------------|---------------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mod               | e Timing (See Figure 23.8 and Figure 23.9)                          |                              |                         |       |

| Т <sub>МСКН</sub>        | SCK High Time                                                       | 1 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>MCKL</sub>        | SCK Low Time                                                        | 1 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                                        | 1 x T <sub>SYSCLK</sub> + 20 | —                       | ns    |

| T <sub>MIH</sub>         | SCK Shift Edge to MISO Change                                       | 0                            | _                       | ns    |

| Slave Mode               | Timing (See Figure 23.10 and Figure 23.11)                          |                              |                         |       |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                                       | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                                         | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                                           | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                                           | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| Т <sub>СКН</sub>         | SCK High Time                                                       | 5 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>CKL</sub>         | SCK Low Time                                                        | 5 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                                       | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                                      | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| Т <sub>SOH</sub>         | SCK Shift Edge to MISO Change                                       | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)                    | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| Note: T <sub>SYSCI</sub> | $_{\rm K}$ is equal to one period of the device system clock (SYSCL | K).                          | 1                       |       |

# Table 23.1. SPI Slave Timing Parameters

|                    | Value            | es F  | Rea     | d   |                                                 |                                                                                                |     | lues<br>Vrit                                              | itus<br>bected |                                                 |   |      |   |

|--------------------|------------------|-------|---------|-----|-------------------------------------------------|------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------|----------------|-------------------------------------------------|---|------|---|

| Mode               | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                             | Typical Response Options                                                                       | STA | STO                                                       | ACK            | Next Status<br>Vector Expected                  |   |      |   |

|                    | 1110             | 0     | 0       | Х   | A master START was generated.                   | Load slave address + R/W into SMB0DAT.                                                         | 0   | 0                                                         | Х              | 1100                                            |   |      |   |

|                    |                  | 0     | 0       | 0   | A master data or address byte was               | Set STA to restart transfer.                                                                   | 1   | 0                                                         | Х              | 1110                                            |   |      |   |

| er                 |                  | •     | •       | •   | transmitted; NACK received.                     | Abort transfer.                                                                                | 0   | 1                                                         | Х              | —                                               |   |      |   |

| nsmitt             |                  |       |         |     | Load next data by DAT.                          | Load next data byte into SMB0-<br>DAT.                                                         | 0   | 0                                                         | Х              | 1100                                            |   |      |   |

| Tra                | 44.00            |       |         |     |                                                 | End transfer with STOP.                                                                        | 0   | 1                                                         | Х              |                                                 |   |      |   |

| Master Transmitter | 1100             | 0     | 0       | 1   | transmitted; ACK received.                      | End transfer with STOP and start another transfer.                                             | 1   | 1                                                         | Х              |                                                 |   |      |   |

|                    |                  |       |         |     |                                                 | Send repeated START.                                                                           | 1   | 0                                                         | Х              | 1110                                            |   |      |   |

|                    |                  |       |         |     |                                                 | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT).           | 0   | 0                                                         | Х              | 1000                                            |   |      |   |

| /er                |                  |       |         |     | Acknowledge receive<br>Read SMB0DAT.            | Acknowledge received byte;<br>Read SMB0DAT.                                                    | 0   | 0                                                         | 1              | 1000                                            |   |      |   |

|                    |                  |       |         |     |                                                 |                                                                                                |     |                                                           |                | Send NACK to indicate last byte, and send STOP. | 0 | 1    | 0 |

|                    |                  |       |         |     |                                                 | Send NACK to indicate last byte,<br>and send STOP followed by<br>START.                        | 1   | 1                                                         | 0              | 1110                                            |   |      |   |

| aster Receiver     | 1000             | 1     | 0       | х   | A master data byte was received; ACK requested. | Send ACK followed by repeated START.                                                           | 1   | 0                                                         | 1              | 1110                                            |   |      |   |

| Master             |                  |       |         |     |                                                 |                                                                                                |     | Send NACK to indicate last byte, and send repeated START. | 1              | 0                                               | 0 | 1110 |   |

|                    |                  |       |         |     |                                                 | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI).    | 0   | 0                                                         | 1              | 1100                                            |   |      |   |

|                    |                  |       |         |     |                                                 | Send NACK and switch to Mas-<br>ter Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0   | 0                                                         | 0              | 1100                                            |   |      |   |

# Table 24.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0)

# Register 24.3. SMB0CN: SMBus0 Control

| Bit                                 | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0  |

|-------------------------------------|--------|--------|-----|-----|-------|---------|-----|----|

| Name                                | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI |

| Туре                                | R      | R      | RW  | RW  | R     | R       | RW  | RW |

| Reset                               | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0  |

| SFR Address: 0xC0 (bit-addressable) |        |        |     |     |       |         |     |    |

# Table 24.9. SMB0CN Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | <ul> <li>SMBus0 Master/Slave Indicator.</li> <li>This read-only bit indicates when the SMBus0 is operating as a master.</li> <li>0: SMBus0 operating in slave mode.</li> <li>1: SMBus0 operating in master mode.</li> </ul>                                                                                                                                                                            |

| 6   | TXMODE  | <ul> <li>SMBus0 Transmit Mode Indicator.</li> <li>This read-only bit indicates when the SMBus0 is operating as a transmitter.</li> <li>0: SMBus0 in Receiver Mode.</li> <li>1: SMBus0 in Transmitter Mode.</li> </ul>                                                                                                                                                                                  |

| 5   | STA     | <b>SMBus0 Start Flag.</b><br>When reading STA, a 1 indicates that a start or repeated start condition was detected on the bus.<br>Writing a 1 to the STA bit initiates a start or repeated start on the bus.                                                                                                                                                                                           |

| 4   | STO     | <ul> <li>SMBus0 Stop Flag.</li> <li>When reading STO, a 1 indicates that a stop condition was detected on the bus (in slave mode) or is pending (in master mode).</li> <li>When acting as a master, writing a 1 to the STO bit initiates a stop condition on the bus. This bit is cleared by hardware.</li> </ul>                                                                                      |

| 3   | ACKRQ   | SMBus0 Acknowledge Request.         0: No ACK requested.         1: ACK requested.                                                                                                                                                                                                                                                                                                                     |

| 2   | ARBLOST | SMBus0 Arbitration Lost Indicator.0: No arbitration error.1: Arbitration error occurred.                                                                                                                                                                                                                                                                                                               |

| 1   | ACK     | <ul> <li>SMBus0 Acknowledge.</li> <li>When read as a master, the ACK bit indicates whether an ACK (1) or NACK (0) is received during the most recent byte transfer.</li> <li>As a slave, this bit should be written to send an ACK (1) or NACK (0) to a master request. Note that the logic level of the ACK bit on the SMBus interface is inverted from the logic of the register ACK bit.</li> </ul> |

# 25. Timers (Timer0, Timer1, Timer2 and Timer3)

Each MCU in the C8051F85x/86x family includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timers for timing peripherals or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 are also identical and offer both 16-bit and split 8-bit timer functionality with auto-reload capabilities. Timer 2 and Timer 3 both offer a capture function, but are different in their system-level connections. Timer 2 is capable of performing a capture function on an external signal input routed through the crossbar, while the Timer 3 capture is dedicated to the low-frequency oscillator output. Table 25.1 summarizes the modes available to each timer.

| Timer 0 and Timer 1 Modes                  | Timer 2 Modes                     | Timer 3 Modes                     |

|--------------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                       | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                       | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |

| 8-bit counter/timer with auto-reload       | Input pin capture                 | Low-frequency oscillator capture  |

| Two 8-bit counter/timers<br>(Timer 0 only) |                                   |                                   |

### Table 25.1. Timer Modes

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked.

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it must be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

All four timers are capable of clocking other peripherals and triggering events in the system. The individual peripherals select which timer to use for their respective functions. Table 25.2 summarizes the peripheral connections for each timer. Note that the Timer 2 and Timer 3 high overflows apply to the full timer when operating in 16-bit mode or the high-byte timer when operating in 8-bit split mode.

| Table 25.2. Timer Peripheral | Clocking / Event Triggering |

|------------------------------|-----------------------------|

|------------------------------|-----------------------------|

| Function               | T0<br>Overflow | T1<br>Overflow | T2 High<br>Overflow | T2 Low<br>Overflow | T3 High<br>Overflow | T3 Low<br>Overflow |

|------------------------|----------------|----------------|---------------------|--------------------|---------------------|--------------------|

| UART0 Baud Rate        |                | Х              |                     |                    |                     |                    |

| SMBus0 Clock Rate      | Х              | Х              | Х                   | Х                  |                     |                    |

| SMBus0 SCL Low Timeout |                |                |                     |                    | Х                   |                    |

| PCA0 Clock             | Х              |                |                     |                    |                     |                    |

# Register 25.2. TCON: Timer 0/1 Control

| Bit                                 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name                                | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| Туре                                | RW  |

| Reset                               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| SFR Address: 0x88 (bit-addressable) |     |     |     |     |     |     |     |     |

# Table 25.4. TCON Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                                                                                                        |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag.                                                                                                                                                                                                                                          |

|     |      | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                   |

| 6   | TR1  | Timer 1 Run Control.                                                                                                                                                                                                                                            |

|     |      | Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                                                    |

| 5   | TF0  | Timer 0 Overflow Flag.                                                                                                                                                                                                                                          |

|     |      | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                   |

| 4   | TR0  | Timer 0 Run Control.                                                                                                                                                                                                                                            |

|     |      | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                    |

| 3   | IE1  | External Interrupt 1.                                                                                                                                                                                                                                           |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                         |

| 2   | IT1  | Interrupt 1 Type Select.                                                                                                                                                                                                                                        |

|     |      | <ul> <li>This bit selects whether the configured INT1 interrupt will be edge or level sensitive. INT1 is configured active low or high by the IN1PL bit in register IT01CF.</li> <li>0: INT1 is level triggered.</li> <li>1: INT1 is edge triggered.</li> </ul> |

| 1   | IE0  | External Interrupt 0.                                                                                                                                                                                                                                           |

|     |      | This flag is set by hardware when an edge/level of type defined by IT0 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                         |

| 0   | IT0  | Interrupt 0 Type Select.                                                                                                                                                                                                                                        |

|     |      | <ul><li>This bit selects whether the configured INT0 interrupt will be edge or level sensitive. INT0 is configured active low or high by the IN0PL bit in register IT01CF.</li><li>0: INT0 is level triggered.</li><li>1: INT0 is edge triggered.</li></ul>     |