Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 15                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                              |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f853-c-imr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1.7. ADC (Continued)

| Parameter                        | Symbol            | Test Condition                    | Min      | Тур       | Max     | Unit   |

|----------------------------------|-------------------|-----------------------------------|----------|-----------|---------|--------|

| Offset Error                     | E <sub>OFF</sub>  | 12 Bit Mode, VREF = 1.65 V        | -3       | 0         | 3       | LSB    |

|                                  | -                 | 10 Bit Mode, VREF = 1.65 V        | -2       | 0         | 2       | LSB    |

| Offset Temperature Coefficient   | TC <sub>OFF</sub> |                                   | _        | 0.004     | _       | LSB/°C |

| Slope Error                      | E <sub>M</sub>    | 12 Bit Mode                       |          | ±0.02     | ±0.1    | %      |

|                                  | -                 | 10 Bit Mode                       |          | ±0.06     | ±0.24   | %      |

| Dynamic Performance 10 k         | Hz Sine Wa        | ve Input 1dB below full scale, Ma | x throug | ghput, us | sing AG | ND pin |

| Signal-to-Noise                  | SNR               | 12 Bit Mode                       | 61       | 66        |         | dB     |

|                                  | -                 | 10 Bit Mode                       | 53       | 60        |         | dB     |

| Signal-to-Noise Plus Distor-     | SNDR              | 12 Bit Mode                       | 61       | 66        |         | dB     |

| tion                             | -                 | 10 Bit Mode                       | 53       | 60        |         | dB     |

| Total Harmonic Distortion        | THD               | 12 Bit Mode                       | —        | 71        | _       | dB     |

| (Up to 5th Harmonic)             | -                 | 10 Bit Mode                       | _        | 70        | _       | dB     |

| Spurious-Free Dynamic            | SFDR              | 12 Bit Mode                       | _        | -79       | _       | dB     |

| Range                            | -                 | 10 Bit Mode                       |          | -74       |         | dB     |

| *Note: Absolute input pin voltag | ge is limited by  | r the V <sub>DD</sub> supply.     | 1        | 1         | 1       | 1      |

| Pin Name         | Туре                                        | Pin Numbers | Crossbar Capability | Additional Digital Functions          | Analog Functions                   |

|------------------|---------------------------------------------|-------------|---------------------|---------------------------------------|------------------------------------|

| P0.0             | Standard I/O                                | 4           | Yes                 | POMAT.0<br>INT0.0<br>INT1.0           | ADC0.0<br>CP0P.0<br>CP0N.0<br>VREF |

| P0.1             | Standard I/O                                | 3           | Yes                 | POMAT.1<br>INT0.1<br>INT1.1           | ADC0.1<br>CP0P.1<br>CP0N.1<br>AGND |

| P0.2             | Standard I/O                                | 2           | Yes                 | POMAT.2<br>INT0.2<br>INT1.2           | ADC0.2<br>CP0P.2<br>CP0N.2         |

| P0.3 /<br>EXTCLK | Standard I/O /<br>External CMOS Clock Input | 23          | Yes                 | P0MAT.3<br>EXTCLK<br>INT0.3<br>INT1.3 | ADC0.3<br>CP0P.3<br>CP0N.3         |

| P0.4             | Standard I/O                                | 22          | Yes                 | POMAT.4<br>INT0.4<br>INT1.4           | ADC0.4<br>CP0P.4<br>CP0N.4         |

| P0.5             | Standard I/O                                | 21          | Yes                 | P0MAT.5<br>INT0.5<br>INT1.5           | ADC0.5<br>CP0P.5<br>CP0N.5         |

| P0.6             | Standard I/O                                | 20          | Yes                 | P0MAT.6<br>CNVSTR<br>INT0.6<br>INT1.6 | ADC0.6<br>CP0P.6<br>CP0N.6         |

| P0.7             | Standard I/O                                | 19          | Yes                 | POMAT.7<br>INT0.7<br>INT1.7           | ADC0.7<br>CP0P.7<br>CP0N.7         |

### Table 3.1. Pin Definitions for C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU

| Pin Name      | Туре                            | Pin Numbers | Crossbar Capability | Additional Digital Functions | Analog Functions            |

|---------------|---------------------------------|-------------|---------------------|------------------------------|-----------------------------|

| P1.0          | Standard I/O                    | 18          | Yes                 | P1MAT.0                      | ADC0.8<br>CP1P.0<br>CP1N.0  |

| P1.1          | Standard I/O                    | 17          | Yes                 | P1MAT.1                      | ADC0.9<br>CP1P.1<br>CP1N.1  |

| P1.2          | Standard I/O                    | 16          | Yes                 | P1MAT.2                      | ADC0.10<br>CP1P.2<br>CP1N.2 |

| P1.3          | Standard I/O                    | 15          | Yes                 | P1MAT.3                      | ADC0.11<br>CP1P.3<br>CP1N.3 |

| P1.4          | Standard I/O                    | 14          | Yes                 | P1MAT.4                      | ADC0.12<br>CP1P.4<br>CP1N.4 |

| P1.5          | Standard I/O                    | 11          | Yes                 | P1MAT.5                      | ADC0.13<br>CP1P.5<br>CP1N.5 |

| P1.6          | Standard I/O                    | 10          | Yes                 | P1MAT.6                      | ADC0.14<br>CP1P.6<br>CP1N.6 |

| P1.7          | Standard I/O                    | 9           | Yes                 | P1MAT.7                      | ADC0.15<br>CP1P.7<br>CP1N.7 |

| P2.0 /<br>C2D | Standard I/O /<br>C2 Debug Data | 8           |                     |                              |                             |

| P2.1          | Standard I/O                    | 12          |                     |                              |                             |

### Table 3.1. Pin Definitions for C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU

| Pin Name | Туре          | Pin Numbers   | Crossbar Capability | Additional Digital Functions | Analog Functions |

|----------|---------------|---------------|---------------------|------------------------------|------------------|

| N/C      | No Connection | 1<br>13<br>24 |                     |                              |                  |

### Table 3.1. Pin Definitions for C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU

#### 8.2.3. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the CIP-51's resources and peripherals. The CIP-51 duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the MCU. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided.

## **12.2. Interrupt Control Registers**

| Bit   | 7  | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | RW | RW    | RW  | RW  | RW  | RW  | RW  | RW  |

| Reset | 0  | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

|       |    |       |     |     |     |     |     |     |

### Register 12.1. IE: Interrupt Enable

#### SFR Address: 0xA8 (bit-addressable)

### Table 12.2. IE Register Bit Descriptions

| Bit | Name  | Function                                                                                                                    |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <b>Enable All Interrupts.</b><br>Globally enables/disables all interrupts and overrides individual interrupt mask settings. |

|     |       | 0: Disable all interrupt sources.<br>1: Enable each interrupt according to its individual mask setting.                     |

| 6   | ESPI0 | Enable SPI0 Interrupt.                                                                                                      |

|     |       | This bit sets the masking of the SPI0 interrupts.                                                                           |

|     |       | 0: Disable all SPI0 interrupts.                                                                                             |

|     |       | 1: Enable interrupt requests generated by SPI0.                                                                             |

| 5   | ET2   | Enable Timer 2 Interrupt.                                                                                                   |

|     |       | This bit sets the masking of the Timer 2 interrupt.                                                                         |

|     |       | <ul><li>0: Disable Timer 2 interrupt.</li><li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li></ul>   |

|     |       |                                                                                                                             |

| 4   | ES0   | Enable UARTO Interrupt.                                                                                                     |

|     |       | This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.                                            |

|     |       | 1: Enable UART0 interrupt.                                                                                                  |

| 3   | ET1   | Enable Timer 1 Interrupt.                                                                                                   |

|     |       | This bit sets the masking of the Timer 1 interrupt.                                                                         |

|     |       | 0: Disable all Timer 1 interrupt.                                                                                           |

|     |       | 1: Enable interrupt requests generated by the TF1 flag.                                                                     |

| 2   | EX1   | Enable External Interrupt 1.                                                                                                |

|     |       | This bit sets the masking of External Interrupt 1.                                                                          |

|     |       | 0: Disable external interrupt 1.                                                                                            |

|     |       | 1: Enable interrupt requests generated by the INT1 input.                                                                   |

| 1   | ET0   | Enable Timer 0 Interrupt.                                                                                                   |

|     |       | This bit sets the masking of the Timer 0 interrupt.                                                                         |

|     |       | 0: Disable all Timer 0 interrupt.                                                                                           |

|     |       | 1: Enable interrupt requests generated by the TF0 flag.                                                                     |

| Bit | Name  | Function                                                                                                                                           |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | PSMB0 | SMBus (SMB0) Interrupt Priority Control.                                                                                                           |

|     |       | This bit sets the priority of the SMB0 interrupt.<br>0: SMB0 interrupt set to low priority level.<br>1: SMB0 interrupt set to high priority level. |

## Table 12.5. EIP1 Register Bit Descriptions

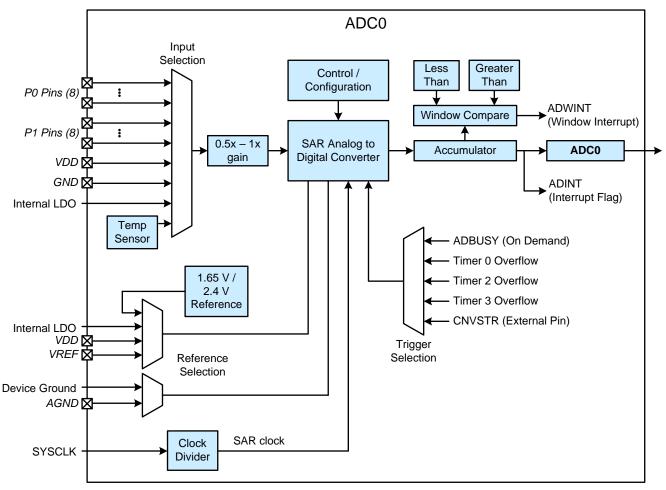

# 14. Analog-to-Digital Converter (ADC0)

The ADC is a successive-approximation-register (SAR) ADC with 12-, 10-, and 8-bit modes, integrated track-and-hold and a programmable window detector. These different modes allow the user to trade off speed for resolution. ADC0 also has an autonomous low-power burst mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results.

The ADC is fully configurable under software control via several registers. The ADC0 operates in singleended mode and may be configured to measure different signals using the analog multiplexer. The voltage reference for the ADC is selectable between internal and external reference sources.

Figure 14.1. ADC0 Functional Block Diagram

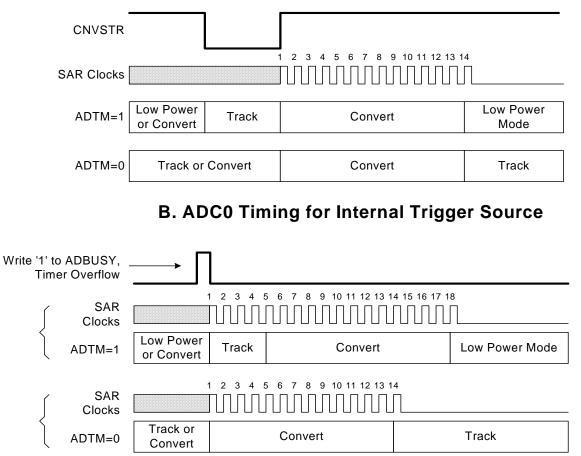

## A. ADC0 Timing for External Trigger Source

Figure 14.2. 10-Bit ADC Track and Conversion Example Timing (ADBMEN = 0)

#### 14.2.3. Burst Mode

Burst Mode is a power saving feature that allows ADC0 to remain in a low power state between conversions. When Burst Mode is enabled, ADC0 wakes from a low power state, accumulates 1, 4, 8, 16, 32, or 64 samples using the internal low-power high-frequency oscillator, then re-enters a low power state. Since the Burst Mode clock is independent of the system clock, ADC0 can perform multiple conversions then enter a low power state within a single system clock cycle, even if the system clock is slow (e.g. 80 kHz).

Burst Mode is enabled by setting ADBMEN to logic 1. When in Burst Mode, ADEN controls the ADC0 idle power state (i.e. the state ADC0 enters when not tracking or performing conversions). If ADEN is set to logic 0, ADC0 is powered down after each burst. If ADEN is set to logic 1, ADC0 remains enabled after each burst. On each convert start signal, ADC0 is awakened from its Idle Power State. If ADC0 is powered down, it will automatically power up and wait the programmable Power-Up Time controlled by the ADPWR bits. Otherwise, ADC0 will start tracking and converting immediately. Figure 14.3 shows an example of Burst Mode Operation with a slow system clock and a repeat count of 4.

When Burst Mode is enabled, a single convert start will initiate a number of conversions equal to the repeat count. When Burst Mode is disabled, a convert start is required to initiate each conversion. In both modes, the ADC0 End of Conversion Interrupt Flag (ADINT) will be set after "repeat count" conversions have been accumulated. Similarly, the Window Comparator will not compare the result to the greater-than and less-than registers until "repeat count" conversions have been accumulated.

## 14.10. ADC Control Registers

### Register 14.1. ADC0CN0: ADC0 Control 0

| Bit   | 7    | 6      | 5     | 4      | 3      | 2    | 1 | 0 |

|-------|------|--------|-------|--------|--------|------|---|---|

| Name  | ADEN | ADBMEN | ADINT | ADBUSY | ADWINT | ADCM |   |   |

| Туре  | RW   | RW     | RW    | RW     | RW     | RW   |   |   |

| Reset | 0    | 0      | 0     | 0      | 0      | 0    | 0 | 0 |

#### SFR Address: 0xE8 (bit-addressable)

## Table 14.4. ADC0CN0 Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                                                    |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ADEN   | Enable.                                                                                                                                                                                                                     |

|     |        | 0: ADC0 Disabled (low-power shutdown).                                                                                                                                                                                      |

|     |        | 1: ADC0 Enabled (active and ready for data conversions).                                                                                                                                                                    |

| 6   | ADBMEN | Burst Mode Enable.                                                                                                                                                                                                          |

|     |        | 0: ADC0 Burst Mode Disabled.                                                                                                                                                                                                |

|     |        | 1: ADC0 Burst Mode Enabled.                                                                                                                                                                                                 |

| 5   | ADINT  | Conversion Complete Interrupt Flag.                                                                                                                                                                                         |

|     |        | Set by hardware upon completion of a data conversion (ADBMEN=0), or a burst of conversions (ADBMEN=1). Can trigger an interrupt. Must be cleared by software.                                                               |

| 4   | ADBUSY | ADC Busy.                                                                                                                                                                                                                   |

|     |        | Writing 1 to this bit initiates an ADC conversion when ADC0CM = 000. This bit should not be polled to indicate when a conversion is complete. Instead, the ADINT bit should be used when polling for conversion completion. |

| 3   | ADWINT | Window Compare Interrupt Flag.                                                                                                                                                                                              |

|     |        | Set by hardware when the contents of ADC0H:ADC0L fall within the window specified by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL. Can trigger an interrupt. Must be cleared by software.                                            |

| 2:0 | ADCM   | Start of Conversion Mode Select.                                                                                                                                                                                            |

|     |        | Specifies the ADC0 start of conversion source. All remaining bit combinations are reserved.                                                                                                                                 |

|     |        | 000: ADC0 conversion initiated on write of 1 to ADBUSY.                                                                                                                                                                     |

|     |        | 001: ADC0 conversion initiated on overflow of Timer 0.<br>010: ADC0 conversion initiated on overflow of Timer 2.                                                                                                            |

|     |        | 011: ADC0 conversion initiated on overflow of Timer 3.                                                                                                                                                                      |

|     |        | 100: ADC0 conversion initiated on rising edge of CNVSTR.                                                                                                                                                                    |

|     |        | 101-111: Reserved.                                                                                                                                                                                                          |

## Register 14.8. ADC0L: ADC0 Data Word Low Byte

| Bit               | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|-------|---|---|---|---|---|---|---|

| Name              | ADCOL |   |   |   |   |   |   |   |

| Туре              | RW    |   |   |   |   |   |   |   |

| Reset             | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0xBD |       |   |   |   |   |   |   |   |

## Table 14.11. ADC0L Register Bit Descriptions

| Bit | Name                                                                                                                                                                                        | Function                                                                                                                                                                                                                                   |  |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | ADC0L                                                                                                                                                                                       | Data Word Low Byte.                                                                                                                                                                                                                        |  |  |  |  |  |

|     |                                                                                                                                                                                             | When read, this register returns the least significant byte of the 16-bit ADC0 accumula-<br>tor, formatted according to the settings in ADSJST. The register may also be written, to<br>set the lower byte of the 16-bit ADC0 accumulator. |  |  |  |  |  |

|     | <ul> <li>Note: If Accumulator shifting is enabled, the most significant bits of the value read will be zeros. This register should not be written when the SYNC bit is set to 1.</li> </ul> |                                                                                                                                                                                                                                            |  |  |  |  |  |

### **17.2.** Functional Description

The comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the port pins: a synchronous "latched" output (CPn), or an asynchronous "raw" output (CPnA). The asynchronous CPnA signal is available even when the system clock is not active. This allows the comparator to operate and generate an output with the device in STOP mode.

When disabled, the comparator output (if assigned to a port I/O pin via the crossbar) defaults to the logic low state, and the power supply to the comparator is turned off.

The comparator response time may be configured in software via the CPTnMD register. Selecting a longer response time reduces the comparator supply current.

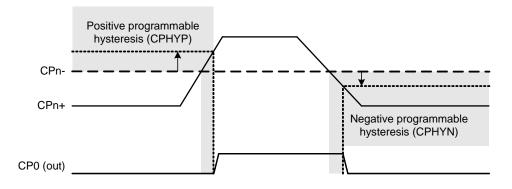

#### Figure 17.2. Comparator Hysteresis Plot

The comparator hysteresis is software-programmable via its Comparator Control register CPTnCN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The comparator hysteresis is programmable using the CPHYN and CPHYP fields in the Comparator Control Register CPTnCN. The amount of negative hysteresis voltage is determined by the settings of the CPHYN bits. As shown in Figure 17.2, settings of 20, 10, or 5 mV (nominal) of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. The CPFIF flag is set to logic 1 upon a comparator falling-edge occurrence, and the CPRIF flag is set to logic 1 upon the comparator rising-edge occurrence. Once set, these bits remain set until cleared by software. The comparator rising-edge interrupt mask is enabled by setting CPRIE to a logic 1. The comparator falling-edge interrupt mask is enabled by setting CPFIE to a logic 1.

The output state of the comparator can be obtained at any time by reading the CPOUT bit. The comparator is enabled by setting the CPEN bit to logic 1, and is disabled by clearing this bit to logic 0.

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed, before enabling comparator interrupts.

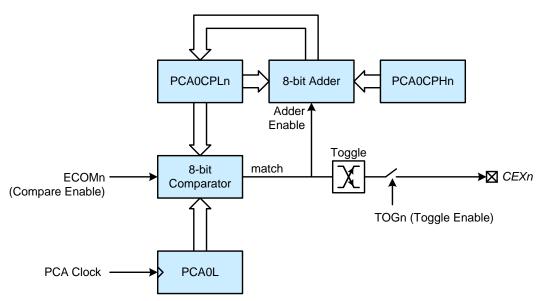

#### 20.3.5. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 20.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 20.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, n is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

Figure 20.5. PCA Frequency Output Mode

## Register 20.2. PCA0MD: PCA Mode

| Bit     | 7                 | 6        | 5 | 4 | 3   | 2 | 1 | 0   |

|---------|-------------------|----------|---|---|-----|---|---|-----|

| Name    | CIDL              | Reserved |   |   | CPS |   |   | ECF |

| Туре    | RW                | R        |   |   | RW  |   |   | RW  |

| Reset   | 0                 | 0        | 0 | 0 | 0   | 0 | 0 | 0   |

| SFR Add | SFR Address: 0xD9 |          |   |   |     |   |   |     |

# Table 20.4. PCA0MD Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CIDL     | <ul> <li>PCA Counter/Timer Idle Control.</li> <li>Specifies PCA behavior when CPU is in Idle Mode.</li> <li>0: PCA continues to function normally while the system controller is in Idle Mode.</li> <li>1: PCA operation is suspended while the system controller is in Idle Mode.</li> </ul>                                                                                                              |

| 6:4 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                    |

| 3:1 | CPS      | PCA Counter/Timer Pulse Select.These bits select the timebase source for the PCA counter.000: System clock divided by 12.001: System clock divided by 4.010: Timer 0 overflow.011: High-to-low transitions on ECI (max rate = system clock divided by 4).100: System clock.101: External clock divided by 8 (synchronized with the system clock).110: Low frequency oscillator divided by 8.111: Reserved. |

| 0   | ECF      | <ul> <li>PCA Counter/Timer Overflow Interrupt Enable.</li> <li>This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.</li> <li>0: Disable the CF interrupt.</li> <li>1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.</li> </ul>                                                                                                                   |

## Register 21.7. P0: Port 0 Pin Latch

| Bit   | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|---|---|---|---|---|---|---|

| Name  |    |   |   | P | 0 |   |   |   |

| Туре  | RW |   |   |   |   |   |   |   |

| Reset | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

## Table 21.10. P0 Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                                                                     |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0   | Port 0 Data.                                                                                                                                                                                                                 |

|     |      | Writing this register sets the port latch logic value for the associated I/O pins configured as digital I/O.<br>Reading this register returns the logic value at the pin, regardless if it is configured as output or input. |

## Register 24.4. SMB0ADR: SMBus0 Slave Address

|   | GC |

|---|----|

|   |    |

|   | RW |

| C | 0  |

| ( | 0  |

## Table 24.10. SMB0ADR Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                                                                                                                   |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV  | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |      | Defines the SMBus0 Slave Address(es) for automatic hardware acknowledgement. Only address bits which have a 1 in the corresponding bit position in SLVM are checked against the incoming address. This allows multiple addresses to be recognized.                         |

| 0   | GC   | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |      | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

# 25. Timers (Timer0, Timer1, Timer2 and Timer3)

Each MCU in the C8051F85x/86x family includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timers for timing peripherals or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 are also identical and offer both 16-bit and split 8-bit timer functionality with auto-reload capabilities. Timer 2 and Timer 3 both offer a capture function, but are different in their system-level connections. Timer 2 is capable of performing a capture function on an external signal input routed through the crossbar, while the Timer 3 capture is dedicated to the low-frequency oscillator output. Table 25.1 summarizes the modes available to each timer.

| Timer 0 and Timer 1 Modes                  | Timer 2 Modes                     | Timer 3 Modes                     |

|--------------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                       | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                       | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |

| 8-bit counter/timer with auto-reload       | Input pin capture                 | Low-frequency oscillator capture  |

| Two 8-bit counter/timers<br>(Timer 0 only) |                                   |                                   |

### Table 25.1. Timer Modes

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked.

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it must be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

All four timers are capable of clocking other peripherals and triggering events in the system. The individual peripherals select which timer to use for their respective functions. Table 25.2 summarizes the peripheral connections for each timer. Note that the Timer 2 and Timer 3 high overflows apply to the full timer when operating in 16-bit mode or the high-byte timer when operating in 8-bit split mode.

| Table 25.2. Timer Peripheral | Clocking / Event Triggering |

|------------------------------|-----------------------------|

|------------------------------|-----------------------------|

| Function               | T0<br>Overflow | T1<br>Overflow | T2 High<br>Overflow | T2 Low<br>Overflow | T3 High<br>Overflow | T3 Low<br>Overflow |

|------------------------|----------------|----------------|---------------------|--------------------|---------------------|--------------------|

| UART0 Baud Rate        |                | Х              |                     |                    |                     |                    |

| SMBus0 Clock Rate      | Х              | Х              | Х                   | Х                  |                     |                    |

| SMBus0 SCL Low Timeout |                |                |                     |                    | Х                   |                    |

| PCA0 Clock             | Х              |                |                     |                    |                     |                    |

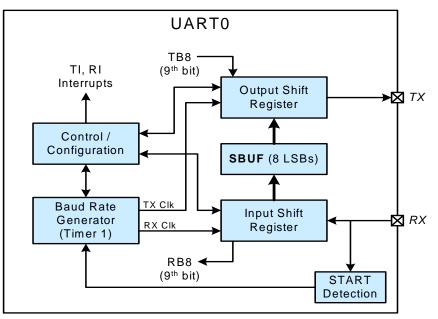

# 26. Universal Asynchronous Receiver/Transmitter (UART0)

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "26.1. Enhanced Baud Rate Generation" on page 289). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the transmit register. Reads of SBUF0 always access the buffered receive register; it is not possible to read data from the transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI is set in SCON0), or a data byte has been received (RI is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 26.1. UART0 Block Diagram

### 26.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 26.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

| Bit | Name | Function                                                                                                                                                                                                                                                                            |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | RI   | Receive Interrupt Flag.                                                                                                                                                                                                                                                             |

|     |      | Set to 1 by hardware when a byte of data has been received by UART0 (set at the STOP bit sampling time). When the UART0 interrupt is enabled, setting this bit to 1 causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software. |

## Table 26.2. SCON0 Register Bit Descriptions

## 27.5. Watchdog Timer Control Registers

## Register 27.1. WDTCN: Watchdog Timer Control

| Bit     | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-------------------|---|---|---|---|---|---|---|

| Name    | WDTCN             |   |   |   |   |   |   |   |

| Туре    | RW                |   |   |   |   |   |   |   |

| Reset   | 0                 | 0 | 0 | 1 | 0 | 1 | 1 | 1 |

| SFR Add | SFR Address: 0x97 |   |   |   |   |   |   |   |

### Table 27.1. WDTCN Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                       |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | WDTCN | WDT Control.                                                                                                                                   |

|     |       | The WDT control field has different behavior for reads and writes.                                                                             |

|     |       | Read:                                                                                                                                          |

|     |       | When reading the WDTCN register, the lower three bits (WDTCN[2:0]) indicate the cur-                                                           |

|     |       | rent timeout interval. Bit WDTCN.4 indicates whether the WDT is active (logic 1) or inac-                                                      |

|     |       | tive (logic 0).                                                                                                                                |

|     |       | Write:                                                                                                                                         |

|     |       | Writing the WDTCN register can set the timeout interval, enable the WDT, disable the WDT, reset the WDT, or lock the WDT to prevent disabling. |

|     |       | Writing to WDTCN with the MSB (WDTCN.7) cleared to 0 will set the timeout interval to                                                          |

|     |       | the value in bits WDTCN[2:0].                                                                                                                  |

|     |       | Writing 0xA5 both enables and reloads the WDT.                                                                                                 |

|     |       | Writing 0xDE followed within 4 system clocks by 0xAD disables the WDT.                                                                         |

|     |       | Writing 0xFF locks out the disable feature until the next device reset.                                                                        |