# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                |                                                                   |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            |                                                                   |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f853-c-iur |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

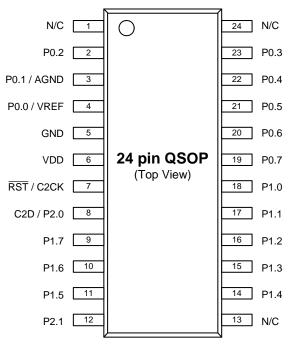

### 3. Pin Definitions

### 3.1. C8051F850/1/2/3/4/5 QSOP24 Pin Definitions

Figure 3.1. C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU Pinout

| Table 3.1. Pin [ | Definitions for | C8051F850/1/2/3/4/5-GU | and C8051F850/1/2/3/4/5-IU |

|------------------|-----------------|------------------------|----------------------------|

|                  |                 |                        |                            |

| Pin Name      | Туре                                 | Pin Numbers | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|--------------------------------------|-------------|---------------------|------------------------------|------------------|

| GND           | Ground                               | 5           |                     |                              |                  |

| VDD           | Power                                | 6           |                     |                              |                  |

| RST /<br>C2CK | Active-low Reset /<br>C2 Debug Clock | 7           |                     |                              |                  |

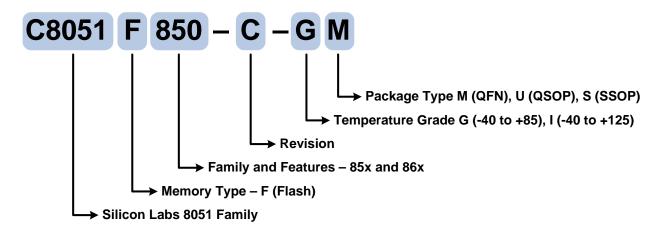

### 4. Ordering Information

#### Figure 4.1. C8051F85x/86x Part Numbering

All C8051F85x/86x family members have the following features:

- CIP-51 Core running up to 25 MHz

- Two Internal Oscillators (24.5 MHz and 80 kHz)

- I2C/SMBus

- SPI

- UART

- 3-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- 4 16-bit Timers

- 2 Analog Comparators

- 16-bit CRC Unit

In addition to these features, each part number in the C8051F85x/86x family has a set of features that vary across the product line. The product selection guide in Table 4.1 shows the features available on each family member.

All devices in Table 4.1 are also available in an industrial version. For the industrial version, the -G in the ordering part number is replaced with -I. For example, the industrial version of the C8051F850-C-GM is the C8051F850-C-IM.

## C8051F85x/86x

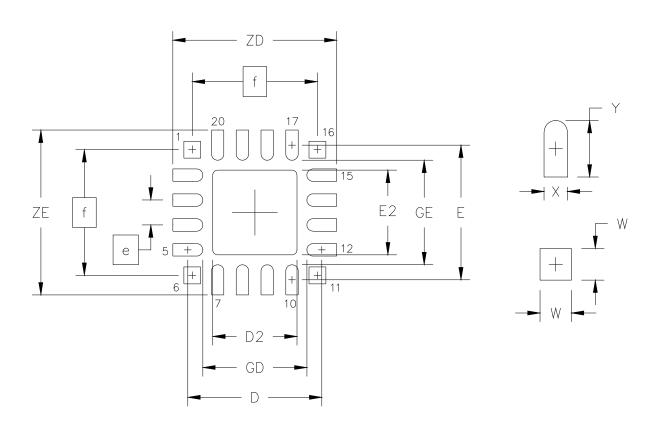

Figure 6.2. QFN-20 Landing Diagram

| Symbol | Millimeters |      | Symbol | Millim | neters |

|--------|-------------|------|--------|--------|--------|

|        | Min         | Max  |        | Min    | Max    |

| D      | 2.71        | REF  | GE     | 2.10   | _      |

| D2     | 1.60        | 1.80 | W      | _      | 0.34   |

| е      | 0.50 BSC    |      | Х      | —      | 0.28   |

| E      | 2.71 REF    |      | Y      | 0.61   | REF    |

| E2     | 1.60        | 1.80 | ZE     | —      | 3.31   |

| f      | 2.53        | BSC  | ZD     | —      | 3.31   |

| GD     | 2.10        | —    |        |        |        |

#### Table 6.2. QFN-20 Landing Diagram Dimensions

#### Notes: General

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Notes: Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Notes: Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- **4.** A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides approximately 70% solder paste coverage on the pad, which is optimum to assure correct component stand-off.

#### Notes: Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| Register | Address | Register Description          | Page |  |  |

|----------|---------|-------------------------------|------|--|--|

| PCA0CPM0 | 0xDA    | PCA Capture/Compare Mode 0    | 171  |  |  |

| PCA0CPM1 | 0xDB    | PCA Capture/Compare Mode 1    |      |  |  |

| PCA0CPM2 | 0xDC    | PCA Capture/Compare Mode 1    | 179  |  |  |

| PCA0H    | 0xFA    | PCA Counter/Timer Low Byte    | 173  |  |  |

| PCA0L    | 0xF9    | PCA Counter/Timer High Byte   | 172  |  |  |

| PCA0MD   | 0xD9    | PCA Mode                      | 168  |  |  |

| PCA0POL  | 0x96    | PCA Output Polarity           | 176  |  |  |

| PCA0PWM  | 0xF7    | PCA PWM Configuration         | 169  |  |  |

| PCON     | 0x87    | Power Control                 | 83   |  |  |

| PRTDRV   | 0xF6    | Port Drive Strength           | 196  |  |  |

| PSCTL    | 0x8F    | Program Store Control         | 66   |  |  |

| PSW      | 0xD0    | Program Status Word           | 124  |  |  |

| REF0CN   | 0xD1    | Voltage Reference Control     | 112  |  |  |

| REG0CN   | 0xC9    | Voltage Regulator Control     | 84   |  |  |

| REVID    | 0xB6    | Revision Identification       | 71   |  |  |

| RSTSRC   | 0xEF    | Reset Source                  | 215  |  |  |

| SBUF0    | 0x99    | UART0 Serial Port Data Buffer | 297  |  |  |

| SCON0    | 0x98    | UART0 Serial Port Control     | 295  |  |  |

| SMB0ADM  | 0xD6    | SMBus0 Slave Address Mask     | 257  |  |  |

| SMB0ADR  | 0xD7    | SMBus0 Slave Address          | 256  |  |  |

| SMB0CF   | 0xC1    | SMBus0 Configuration          | 251  |  |  |

| SMB0CN   | 0xC0    | SMBus0 Control                | 254  |  |  |

| SMB0DAT  | 0xC2    | SMBus0 Data                   | 258  |  |  |

| SMB0TC   | 0xAC    | SMBus0 Timing and Pin Control | 253  |  |  |

| SP       | 0x81    | Stack Pointer                 | 121  |  |  |

| SPI0CFG  | 0xA1    | SPI0 Configuration            | 227  |  |  |

| SPI0CKR  | 0xA2    | SPI0 Clock Control            | 231  |  |  |

| SPIOCN   | 0xF8    | SPI0 Control                  | 229  |  |  |

### Table 9.2. Special Function Registers (Continued)

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted               | Permitted         | N/A               |

|--------------------------------------------------------------------------|-------------------------|-------------------|-------------------|

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted           | Flash Error Reset | Permitted         |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted               | Permitted         | N/A               |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | C2 Device Erase<br>Only | Flash Error Reset | Flash Error Reset |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted           | Flash Error Reset | Flash Error Reset |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted           | Flash Error Reset | Flash Error Reset |

| Read, Write or Erase Reserved Area                                       | Not Permitted           | Flash Error Reset | Flash Error Reset |

#### Table 10.1. Flash Security Summary (Continued)

C2 Device Erase—Erases all flash pages including the page containing the Lock Byte.

Flash Error Reset — Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

### 10.5. Flash Control Registers

### Register 10.1. PSCTL: Program Store Control

| Bit     | 7                 | 6 | 5    | 4    | 3 | 2 | 1  | 0  |  |

|---------|-------------------|---|------|------|---|---|----|----|--|

| Name    |                   |   | PSEE | PSWE |   |   |    |    |  |

| Туре    | R                 |   |      |      |   |   | RW | RW |  |

| Reset   | 0                 | 0 | 0    | 0    | 0 | 0 | 0  | 0  |  |

| SFR Add | SFR Address: 0x8F |   |      |      |   |   |    |    |  |

### Table 10.2. PSCTL Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1   | PSEE     | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of flash program memory to be erased. If this bit is logic 1 and flash writes are enabled (PSWE is logic 1), a write to flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE     | <ul> <li>Program Store Write Enable.</li> <li>Setting this bit allows writing a byte of data to the flash program memory using the MOVX write instruction. The flash location should be erased before writing data.</li> <li>0: Writes to flash program memory disabled.</li> <li>1: Writes to flash program memory enabled; the MOVX write instruction targets flash memory.</li> </ul>                                                                                                                |

### Register 10.2. FLKEY: Flash Lock and Key

|               |       | · · · |   |   | • |                   |   |       |

|---------------|-------|-------|---|---|---|-------------------|---|-------|

|               | FLKEY |       |   |   |   |                   |   | Name  |

| RW            |       |       |   |   |   | Туре              |   |       |

| 0             | 0     | 0     | 0 | 0 | 0 | 0                 | 0 | Reset |

| 0 0 0 0 0 0 0 |       |       |   |   |   | Reset<br>SFR Addr |   |       |

### Table 10.3. FLKEY Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |       | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |       | This register provides a lock and key function for flash erasures and writes. Flash writes<br>and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY register. Flash<br>writes and erases are automatically disabled after the next write or erase is complete. If<br>any writes to FLKEY are performed incorrectly, or if a flash write or erase operation is<br>attempted while these operations are disabled, the flash will be permanently locked from<br>writes or erasures until the next device reset. If an application never writes to flash, it can<br>intentionally lock the flash by writing a non-0xA5 value to FLKEY from software.<br>Read:<br>When read, bits 1-0 indicate the current flash lock state.<br>00: Flash is write/erase locked.<br>01: The first key code has been written (0xA5).<br>10: Flash is unlocked (writes/erases allowed).<br>11: Flash writes/erases are disabled until the next reset. |

### Register 11.3. REVID: Revision Identifcation

| Bit   | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-------|---|---|---|----|-----|---|---|---|

| Name  |   |   |   | RE | /ID |   |   |   |

| Туре  | R |   |   |    |     |   |   |   |

| Reset | Х | Х | Х | Х  | Х   | Х | Х | Х |

### Table 11.4. REVID Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                       |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | REVID | Revision ID.                                                                                                                                                   |

|     |       | This read-only register returns the 8-bit revision ID.<br>00000000: Revision A<br>00000001: Revision B<br>00000010: Revision C<br>00000011-11111111: Reserved. |

| Bit | Name  | Function                                                                                                                                           |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | PSMB0 | SMBus (SMB0) Interrupt Priority Control.                                                                                                           |

|     |       | This bit sets the priority of the SMB0 interrupt.<br>0: SMB0 interrupt set to low priority level.<br>1: SMB0 interrupt set to high priority level. |

### Table 12.5. EIP1 Register Bit Descriptions

#### Table 15.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic         | Description                                | Bytes | Clock<br>Cycles |

|------------------|--------------------------------------------|-------|-----------------|

| DJNZ direct, rel | Decrement direct byte and jump if not zero | 3     | 3/4             |

| NOP              | No operation                               | 1     | 1               |

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

bit—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

### 15.4. CPU Core Registers

| Bit               | 7 6 5 4 3 2 1 |   |   |   |   | 0 |   |   |

|-------------------|---------------|---|---|---|---|---|---|---|

| Name              | DPL           |   |   |   |   |   |   |   |

| Туре              | RW            |   |   |   |   |   |   |   |

| Reset             | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0x82 |               |   |   |   |   |   |   |   |

### Table 15.2. DPL Register Bit Descriptions

| Bit | Name | Function                                                                                                               |

|-----|------|------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DPL  | Data Pointer Low.                                                                                                      |

|     |      | The DPL register is the low byte of the 16-bit DPTR. DPTR is used to access indirectly addressed flash memory or XRAM. |

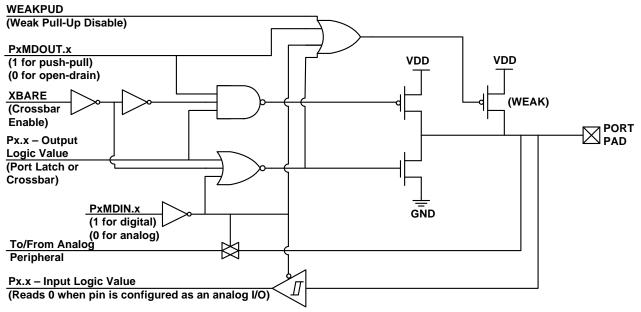

#### 21.4.3. Port Drive Strength

Port drive strength can be controlled on a port-by-port basis using the PRTDRV register. Each port has a bit in PRTDRV to select the high or low drive strength setting for all pins on that port. By default, all ports are configured for high drive strength.

Figure 21.4. Port I/O Cell Block Diagram

### 21.5. Port Match

Port match functionality allows system events to be triggered by a logic value change on one or more port I/O pins. A software controlled value stored in the PnMATCH registers specifies the expected or normal logic values of the associated port pins (for example, P0MATCH.0 would correspond to P0.0). A port mismatch event occurs if the logic levels of the port's input pins no longer match the software controlled value. This allows software to be notified if a certain change or pattern occurs on the input pins regardless of the XBRn settings.

The PnMASK registers can be used to individually select which pins should be compared against the PnMATCH registers. A port mismatch event is generated if (Pn & PnMASK) does not equal (PnMATCH & PnMASK) for all ports with a PnMAT and PnMASK register.

A port mismatch event may be used to generate an interrupt or wake the device from idle mode. See the interrupts and power options chapters for more details on interrupt and wake-up sources.

#### 21.6. Direct Read/Write Access to Port I/O Pins

All port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the crossbar, the port register can always read its corresponding port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

| Hardware Slave Address<br>SLV | Slave Address Mask<br>SLVM | GC bit | Slave Addresses Recognized by Hardware |

|-------------------------------|----------------------------|--------|----------------------------------------|

| 0x34                          | 0x7E                       | 1      | 0x34, 0x35, 0x00 (General Call)        |

| 0x70                          | 0x73                       | 0      | 0x70, 0x74, 0x78, 0x7C                 |

Table 24.4. Hardware Address Recognition Examples (EHACK = 1)

#### 24.4.6. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

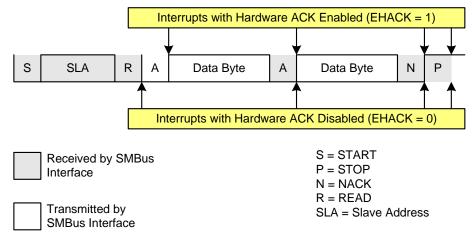

#### 24.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters slave transmitter mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (an error condition may be generated if SMB0DAT is written following a received NACK while in slave transmitter mode). The interface exits slave transmitter mode after receiving a STOP. The interface will switch to slave receiver mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 24.8 shows a typical slave read sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that all of the "data byte transferred" interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

Figure 24.8. Typical Slave Read Sequence

#### 24.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. The appropriate actions to take in response to an SMBus event depend on whether hardware slave address recognition and ACK generation is enabled or disabled. Table 24.5 describes the typical actions when hardware slave address recognition and ACK generation is disabled. Table 24.6 describes the typical actions when hardware slave address recognition and ACK generation is enabled. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

|                   | Val              | ue | es F  | Rea     | d                                          |                                                                                       |                                                                                | Values to<br>Write |   |      | Next Status<br>Vector Expected |   |                        |                          |   |   |                                                                                |      |

|-------------------|------------------|----|-------|---------|--------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------|---|------|--------------------------------|---|------------------------|--------------------------|---|---|--------------------------------------------------------------------------------|------|

| Mode              | Status<br>Vector |    | ACKRQ | ARBLOST | ACK                                        | Current SMbus State                                                                   | Current SMbus State Typical Response Options                                   |                    |   |      |                                |   |                        |                          |   |   |                                                                                |      |

|                   |                  |    |       |         |                                            |                                                                                       | Set ACK for next data byte;<br>Read SMB0DAT.                                   | 0                  | 0 | 1    | 1000                           |   |                        |                          |   |   |                                                                                |      |

|                   |                  |    | 0 0 1 | 1       | A master data byte was received; ACK sent. | Set NACK to indicate next data<br>byte as the last data byte;<br>Read SMB0DAT.        | 0                                                                              | 0                  | 0 | 1000 |                                |   |                        |                          |   |   |                                                                                |      |

| ř                 |                  |    |       |         |                                            | Sent.                                                                                 | Initiate repeated START.                                                       | 1                  | 0 | 0    | 1110                           |   |                        |                          |   |   |                                                                                |      |

| Master Receiver   | 1000             | )  |       |         |                                            |                                                                                       | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI). | 0                  | 0 | Х    | 1100                           |   |                        |                          |   |   |                                                                                |      |

| aste              |                  |    |       |         |                                            |                                                                                       | Read SMB0DAT; send STOP.                                                       | 0                  | 1 | 0    | —                              |   |                        |                          |   |   |                                                                                |      |

| Ξ                 |                  |    |       |         | A master data byte was received;           | Read SMB0DAT; Send STOP followed by START.                                            | 1                                                                              | 1                  | 0 | 1110 |                                |   |                        |                          |   |   |                                                                                |      |

|                   |                  |    | 0     | 0       | 0                                          | 0                                                                                     | 0                                                                              | 0                  | 0 | 0    | 0                              | 0 | NACK sent (last byte). | Initiate repeated START. | 1 | 0 | 0                                                                              | 1110 |

|                   |                  |    |       |         |                                            |                                                                                       |                                                                                |                    |   |      |                                |   |                        |                          |   |   | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI). | 0    |

| er.               |                  |    | 0     | 0       | 0                                          | A slave byte was transmitted; NACK received.                                          | No action required (expecting STOP condition).                                 | 0                  | 0 | Х    | 0001                           |   |                        |                          |   |   |                                                                                |      |

| smitte            | 0100             | )  | 0     | 0       | 1                                          | A slave byte was transmitted; ACK received.                                           | Load SMB0DAT with next data byte to transmit.                                  | 0                  | 0 | Х    | 0100                           |   |                        |                          |   |   |                                                                                |      |

| Slave Transmitter |                  |    | 0     | 1       | Х                                          | A Slave byte was transmitted; error detected.                                         | No action required (expecting Master to end transfer).                         | 0                  | 0 | Х    | 0001                           |   |                        |                          |   |   |                                                                                |      |

| Slav              | 0101             | 1  | 0     | x       | х                                          | An illegal STOP or bus error was detected while a Slave Transmission was in progress. | Clear STO.                                                                     | 0                  | 0 | Х    | —                              |   |                        |                          |   |   |                                                                                |      |

### Table 24.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1) (Continued)

| Bit | Name  | Function                                                                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SMBCS | SMBus0 Clock Source Selection.                                                                                                                                                                                                                                                 |

|     |       | These two bits select the SMBus0 clock source, which is used to generate the SMBus0<br>bit rate. See the SMBus clock timing section for additional details.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow |

### Table 24.7. SMB0CF Register Bit Descriptions

### Register 24.2. SMB0TC: SMBus0 Timing and Pin Control

| Bit               | 7    | 6 | 5    | 4        | 3 | 2 | 1  | 0  |

|-------------------|------|---|------|----------|---|---|----|----|

| Name              | SWAP |   |      | Reserved |   |   | SI | DD |

| Туре              | RW   |   | R RW |          |   |   |    |    |

| Reset             | 0    | 0 | 0    | 0        | 0 | 0 | 0  | 0  |

| SFR Address: 0xAC |      |   |      |          |   |   |    |    |

### Table 24.8. SMB0TC Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SWAP     | SMBus0 Swap Pins.                                                                                                                                                                                                                                                                                                                                         |

|     |          | <ul> <li>This bit swaps the order of the SMBus0 pins on the crossbar.</li> <li>0: SDA is mapped to the lower-numbered port pin, and SCL is mapped to the higher-numbered port pin.</li> <li>1: SCL is mapped to the lower-numbered port pin, and SDA is mapped to the higher-numbered port pin.</li> </ul>                                                |

| 6:2 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                   |

| 1:0 | SDD      | SMBus0 Start Detection Window.                                                                                                                                                                                                                                                                                                                            |

|     |          | <ul> <li>These bits increase the hold time requirement between SDA falling and SCL falling for START detection.</li> <li>00: No additional hold time window (0-1 SYSCLK).</li> <li>01: Increase hold time window to 2-3 SYSCLKs.</li> <li>10: Increase hold time window to 4-5 SYSCLKs.</li> <li>11: Increase hold time window to 8-9 SYSCLKs.</li> </ul> |

### Register 25.3. TMOD: Timer 0/1 Mode

| Bit   | 7     | 6   | 5   | 4  | 3     | 2   | 1   | 0 |

|-------|-------|-----|-----|----|-------|-----|-----|---|

| Name  | GATE1 | CT1 | T1  | IM | GATE0 | CT0 | ТОМ |   |

| Туре  | RW    | RW  | R   | W  | RW    | RW  | R   | W |

| Reset | 0     | 0   | 0 0 |    | 0     | 0   | 0   | 0 |

### Table 25.5. TMOD Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE1 | Timer 1 Gate Control.0: Timer 1 enabled when TR1 = 1 irrespective of INT1 logic level.1: Timer 1 enabled only when TR1 = 1 and INT1 is active as defined by bit IN1PL in register IT01CF.                                                  |

| 6   | CT1   | Counter/Timer 1 Select.0: Timer Mode. Timer 1 increments on the clock defined by T1M in the CKCON register.1: Counter Mode. Timer 1 increments on high-to-low transitions of an external pin (T1).                                         |

| 5:4 | T1M   | Timer 1 Mode Select.These bits select the Timer 1 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Timer 1 Inactive                              |

| 3   | GATE0 | Timer 0 Gate Control.0: Timer 0 enabled when TR0 = 1 irrespective of INT0 logic level.1: Timer 0 enabled only when TR0 = 1 and INT0 is active as defined by bit IN0PL in register IT01CF.                                                  |

| 2   | СТО   | <ul> <li>Counter/Timer 0 Select.</li> <li>0: Timer Mode. Timer 0 increments on the clock defined by T0M in the CKCON register.</li> <li>1: Counter Mode. Timer 0 increments on high-to-low transitions of an external pin (T0).</li> </ul> |

| 1:0 | ТОМ   | Timer 0 Mode Select.These bits select the Timer 0 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Two 8-bit Counter/Timers                      |

### Register 29.5. C2FPDAT: C2 Flash Programming Data

| •       | <u> </u> |  |  |

|---------|----------|--|--|

| C2FPDAT |          |  |  |

| RW      |          |  |  |

| 0       | 0        |  |  |

|         | 0        |  |  |

### Table 29.5. C2FPDAT Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                             |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | C2FPDAT | C2 Flash Programming Data Register.                                                                                                                                                                                                  |

|     |         | This register is used to pass flash commands, addresses, and data during C2 flash<br>accesses. Valid commands are listed below.<br>0x03: Device Erase<br>0x06: Flash Block Read<br>0x07: Flash Block Write<br>0x08: Flash Page Erase |