# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                            |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                   |

| Supplier Device Package    | -                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f854-c-gu |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 1.7. ADC

| Parameter                       | Symbol              | Test Condition                                                           | Min | Тур  | Мах                                     | Unit |

|---------------------------------|---------------------|--------------------------------------------------------------------------|-----|------|-----------------------------------------|------|

| Resolution                      | N <sub>bits</sub>   | 12 Bit Mode                                                              |     | 12   |                                         | Bits |

|                                 |                     | 10 Bit Mode                                                              |     | 10   |                                         | Bits |

| Throughput Rate                 | f <sub>S</sub>      | 12 Bit Mode                                                              | _   | _    | 200                                     | ksps |

| (High Speed Mode)               |                     | 10 Bit Mode                                                              | _   | _    | 800                                     | ksps |

| Throughput Rate                 | f <sub>S</sub>      | 12 Bit Mode                                                              |     | _    | 62.5                                    | ksps |

| (Low Power Mode)                | -                   | 10 Bit Mode                                                              | _   | _    | 250                                     | ksps |

| Tracking Time                   | t <sub>TRK</sub>    | High Speed Mode                                                          | 230 | _    |                                         | ns   |

|                                 | -                   | Low Power Mode                                                           | 450 | _    |                                         | ns   |

| Power-On Time                   | t <sub>PWR</sub>    |                                                                          | 1.2 | _    | _                                       | μs   |

| SAR Clock Frequency             | f <sub>SAR</sub>    | High Speed Mode,<br>Reference is 2.4 V internal                          | _   | _    | 6.25                                    | MHz  |

|                                 |                     | High Speed Mode,<br>Reference is not 2.4 V internal                      | —   | —    | 12.5                                    | MHz  |

|                                 |                     | Low Power Mode                                                           | _   | _    | 4                                       | MHz  |

| Conversion Time                 | t <sub>CNV</sub>    | 10-Bit Conversion,<br>SAR Clock = 12.25 MHz,<br>System Clock = 24.5 MHz. |     | 1.1  |                                         | μs   |

| Sample/Hold Capacitor           | C <sub>SAR</sub>    | Gain = 1                                                                 | _   | 5    |                                         | pF   |

|                                 |                     | Gain = 0.5                                                               | _   | 2.5  |                                         | pF   |

| Input Pin Capacitance           | C <sub>IN</sub>     |                                                                          | _   | 20   |                                         | pF   |

| Input Mux Impedance             | R <sub>MUX</sub>    |                                                                          | _   | 550  |                                         | Ω    |

| Voltage Reference Range         | V <sub>REF</sub>    |                                                                          | 1   | _    | V <sub>DD</sub>                         | V    |

| Input Voltage Range*            | V <sub>IN</sub>     | Gain = 1                                                                 | 0   | _    | V <sub>REF</sub>                        | V    |

|                                 |                     | Gain = 0.5                                                               | 0   |      | $2xV_{REF}$                             | V    |

| Power Supply Rejection<br>Ratio | PSRR <sub>ADC</sub> |                                                                          | —   | 70   | —                                       | dB   |

| DC Performance                  |                     |                                                                          |     |      |                                         |      |

| Integral Nonlinearity           | INL                 | 12 Bit Mode                                                              | _   | ±1   | ±2.3                                    | LSB  |

|                                 |                     | 10 Bit Mode                                                              |     | ±0.2 | ±0.6                                    | LSB  |

| Differential Nonlinearity       | DNL                 | 12 Bit Mode                                                              | -1  | ±0.7 | 1.9                                     | LSB  |

| (Guaranteed Monotonic)          |                     | 10 Bit Mode                                                              | _   | ±0.2 | ±0.6                                    | LSB  |

| *Note: Absolute input pin volta | age is limited by   | the V <sub>DD</sub> supply.                                              |     |      | ı — — — — — — — — — — — — — — — — — — — |      |

### **1.4. Absolute Maximum Ratings**

Stresses above those listed under Table 1.13 may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

| Parameter                                        | Symbol            | Test Condition                              | Min              | Max                  | Unit |

|--------------------------------------------------|-------------------|---------------------------------------------|------------------|----------------------|------|

| Ambient Temperature Under<br>Bias                | T <sub>BIAS</sub> |                                             | -55              | 125                  | °C   |

| Storage Temperature                              | T <sub>STG</sub>  |                                             | -65              | 150                  | °C   |

| Voltage on V <sub>DD</sub>                       | V <sub>DD</sub>   |                                             | GND-0.3          | 4.2                  | V    |

| Voltage on I/O pins or RST                       | V <sub>IN</sub>   | $V_{DD} \ge 3.3 V$                          | GND-0.3          | 5.8                  | V    |

|                                                  |                   | V <sub>DD</sub> < 3.3 V                     | GND-0.3          | V <sub>DD</sub> +2.5 | V    |

| Total Current Sunk into Supply<br>Pin            | I <sub>VDD</sub>  |                                             | _                | 400                  | mA   |

| Total Current Sourced out of<br>Ground Pin       | I <sub>GND</sub>  |                                             | 400              |                      | mA   |

| Current Sourced or Sunk by Any<br>I/O Pin or RST | I <sub>PIO</sub>  |                                             | -100             | 100                  | mA   |

| Operating Junction Temperature                   | Τ <sub>J</sub>    | Commercial Grade Devices<br>(-GM, -GS, -GU) | -40              | 105                  | °C   |

|                                                  |                   | Industrial Grade Devices<br>(-IM, -IS, -IU) | -40              | 125                  | °C   |

| Note: Exposure to maximum ratir                  | ng condition      | ns for extended periods may affe            | ect device relia | bility.              | 1    |

Table 1.13. Absolute Maximum Ratings

| Table 4.1. Product Selection Guide                                                      |                   |             |                           |                         |                                |                          |                    |                   |         |

|-----------------------------------------------------------------------------------------|-------------------|-------------|---------------------------|-------------------------|--------------------------------|--------------------------|--------------------|-------------------|---------|

| Ordering Part Number                                                                    | Flash Memory (kB) | RAM (Bytes) | Digital Port I/Os (Total) | Number of ADC0 Channels | I/O with Comparator 0/1 Inputs | Pb-free (RoHS Compliant) | AEC-Q100 Qualified | Temperature Range | Package |

| -IM, -IU and -IS extended temperature range devices (-40 to 125 °C) are also available. |                   |             |                           |                         |                                |                          |                    |                   |         |

# Table 4.1. Product Selection Guide

| Symbol | Millimeters |      | Symbol | Millim | neters |

|--------|-------------|------|--------|--------|--------|

|        | Min         | Max  |        | Min    | Max    |

| D      | 2.71 REF    |      | GE     | 2.10   | _      |

| D2     | 1.60        | 1.80 | W      | _      | 0.34   |

| е      | 0.50        | BSC  | Х      | —      | 0.28   |

| E      | 2.71        | REF  | Y      | 0.61   | REF    |

| E2     | 1.60        | 1.80 | ZE     | —      | 3.31   |

| f      | 2.53 BSC    |      | ZD     | —      | 3.31   |

| GD     | 2.10        | —    |        |        |        |

#### Table 6.2. QFN-20 Landing Diagram Dimensions

#### Notes: General

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Notes: Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Notes: Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- **4.** A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides approximately 70% solder paste coverage on the pad, which is optimum to assure correct component stand-off.

#### Notes: Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# C8051F85x/86x

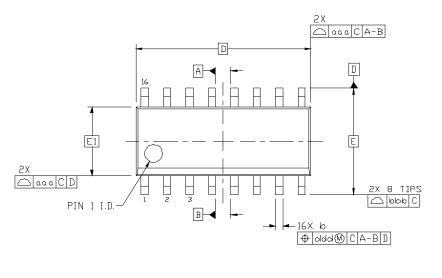

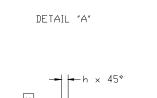

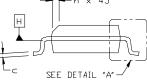

# 7. SOIC-16 Package Specifications

GAUGE PLANE

[[2]

Figure 7.1. SOIC-16 Package Drawing

|           |          |          |      |   | -         |      |          |      |

|-----------|----------|----------|------|---|-----------|------|----------|------|

| Dimension | Min      | Nom      | Max  | ] | Dimension | Min  | Nom      | Max  |

| А         | —        |          | 1.75 |   | L         | 0.40 |          | 1.27 |

| A1        | 0.10     |          | 0.25 |   | L2        |      | 0.25 BSC |      |

| A2        | 1.25     |          |      |   | h         | 0.25 |          | 0.50 |

| b         | 0.31     |          | 0.51 |   | θ         | 0°   |          | 8º   |

| С         | 0.17     |          | 0.25 |   | aaa       |      | 0.10     |      |

| D         |          | 9.90 BSC |      |   | bbb       |      | 0.20     |      |

| Е         | 6.00 BSC |          |      |   | CCC       |      | 0.10     |      |

| E1        | 3.90 BSC |          |      |   | ddd       |      | 0.25     |      |

| е         |          | 1.27 BSC |      |   |           |      |          |      |

### Table 7.1. SOIC-16 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MS-012, Variation AC.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 10.5. Flash Control Registers

### Register 10.1. PSCTL: Program Store Control

| Bit     | 7          | 6 | 5    | 4    | 3  | 2 | 1 | 0 |

|---------|------------|---|------|------|----|---|---|---|

| Name    |            |   | PSEE | PSWE |    |   |   |   |

| Туре    |            |   |      | RW   | RW |   |   |   |

| Reset   | 0 0 0 0 0  |   |      |      |    |   |   | 0 |

| SFR Add | ress: 0x8F |   |      |      |    |   |   |   |

### Table 10.2. PSCTL Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1   | PSEE     | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of flash program memory to be erased. If this bit is logic 1 and flash writes are enabled (PSWE is logic 1), a write to flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE     | <ul> <li>Program Store Write Enable.</li> <li>Setting this bit allows writing a byte of data to the flash program memory using the MOVX write instruction. The flash location should be erased before writing data.</li> <li>0: Writes to flash program memory disabled.</li> <li>1: Writes to flash program memory enabled; the MOVX write instruction targets flash memory.</li> </ul>                                                                                                                |

### 13.4. LDO Control Registers

### Register 13.2. REG0CN: Voltage Regulator Control

| Bit     | 7             | 6    | 5     | 4 | 3      | 2        | 1 | 0 |

|---------|---------------|------|-------|---|--------|----------|---|---|

| Name    |               | Rese | erved |   | STOPCF | Reserved |   |   |

| Туре    |               | F    | २     |   | RW     | R        |   |   |

| Reset   | 0             | 0    | 0     | 0 | 0      | 0        | 0 | 0 |

| SFR Add | Address: 0xC9 |      |       |   |        |          |   |   |

### Table 13.2. REGOCN Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                         |

| 3   |          | <ul> <li>Stop Mode Configuration.</li> <li>This bit configures the regulator's behavior when the device enters stop mode.</li> <li>0: Regulator is still active in stop mode. Any enabled reset source will reset the device.</li> <li>1: Regulator is shut down in stop mode. Only the RST pin or power cycle can reset the device.</li> </ul> |

| 2:0 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                         |

### 14.8. Voltage and Ground Reference Options

The voltage reference multiplexer is configurable to use an externally connected voltage reference, the internal voltage reference, or one of two power supply voltages. The ground reference mux allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (AGND).

The voltage and ground reference options are configured using the REF0CN register.

**Important Note About the VREF and AGND Inputs:** Port pins are used as the external VREF and AGND inputs. When using an external voltage reference, VREF should be configured as an analog input and skipped by the digital crossbar. When using AGND as the ground reference to ADC0, AGND should be configured as an analog input and skipped by the Digital Crossbar.

#### 14.8.1. External Voltage Reference

To use an external voltage reference, REFSL should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference. If the manufacturer does not provide recommendations, a 4.7uF in parallel with a 0.1uF capacitor is recommended.

#### 14.8.2. Internal Voltage Reference

For applications requiring the maximum number of port I/O pins, or very short VREF turn-on time, the highspeed reference will be the best internal reference option to choose. The internal reference is selected by setting REFSL to 11. When selected, the internal reference will be automatically enabled/disabled on an as-needed basis by the ADC. The reference can be set to one of two voltage values: 1.65 V or 2.4 V, depending on the value of the IREFLVL bit.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide the ADC with added dynamic range at the cost of reduced power supply noise rejection. To use the external supply pin (VDD) or the 1.8 V regulated digital supply voltage as the reference source, REFSL should be set to 01 or 10, respectively.

Internal reference sources are not routed to the VREF pin, and do not require external capacitors. The electrical specifications tables detail SAR clock and throughput limitations for each reference source.

#### 14.8.3. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for the ADC during both the tracking/sampling and the conversion periods is taken from the AGND pin. Any external sensors sampled by the ADC should be referenced to the AGND pin. If an external voltage reference is used, the AGND pin should be connected to the ground of the external reference and its associated decoupling capacitor. The separate analog ground reference option is enabled by setting GNDSL to 1. Note that when sampling the internal temperature sensor, the internal chip ground is always used for the sampling operation, regardless of the setting of the GNDSL bit. Similarly, whenever the internal 1.65 V high-speed reference is selected, the internal chip ground is always used during the conversion period, regardless of the setting of the GNDSL bit.

# Register 14.5. ADC0PWR: ADC0 Power Control

| Bit               | 7      | 6 | 5      | 4     | 3     | 2 | 1 | 0 |

|-------------------|--------|---|--------|-------|-------|---|---|---|

| Name              | ADBIAS |   | ADMXLP | ADLPM | ADPWR |   |   |   |

| Туре              | RW     |   | RW     | RW    | RW    |   |   |   |

| Reset             | 0 0    |   | 0      | 0     | 1     | 1 | 1 | 1 |

| SFR Address: 0xDF |        |   |        |       |       |   |   |   |

### Table 14.8. ADC0PWR Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | ADBIAS | Bias Power Select.                                                                                                                                                                         |

|     |        | This field can be used to adjust the ADC's power consumption based on the conversion speed. Higher bias currents allow for faster conversion times.                                        |

|     |        | 00: Select bias current mode 0. Recommended to use modes 1, 2, or 3.                                                                                                                       |

|     |        | 01: Select bias current mode 1 (SARCLK <= 16 MHz).<br>10: Select bias current mode 2.                                                                                                      |

|     |        | 11: Select bias current mode 3 (SARCLK <= 4 MHz).                                                                                                                                          |

| 5   | ADMXLP | Mux and Reference Low Power Mode Enable.                                                                                                                                                   |

|     |        | Enables low power mode operation for the multiplexer and voltage reference buffers.                                                                                                        |

|     |        | 0: Low power mode disabled.                                                                                                                                                                |

|     |        | 1: Low power mode enabled (SAR clock < 4 MHz).                                                                                                                                             |

| 4   | ADLPM  | Low Power Mode Enable.                                                                                                                                                                     |

|     |        | This bit can be used to reduce power to the ADC's internal common mode buffer. It can be set to 1 to reduce power when tracking times in the application are longer (slower sample rates). |

|     |        | 0: Disable low power mode.                                                                                                                                                                 |

|     |        | 1: Enable low power mode (requires extended tracking time).                                                                                                                                |

| 3:0 | ADPWR  | Burst Mode Power Up Time.                                                                                                                                                                  |

|     |        | This field sets the time delay allowed for the ADC to power up from a low power state.<br>When ADTM is set, an additional 4 SARCLKs are added to this time.                                |

|     |        |                                                                                                                                                                                            |

|     |        | $T_{PWRTIME} = \frac{8 \times ADPWR}{F_{HFOSC}}$                                                                                                                                           |

|     |        |                                                                                                                                                                                            |

# 15. CIP-51 Microcontroller Core

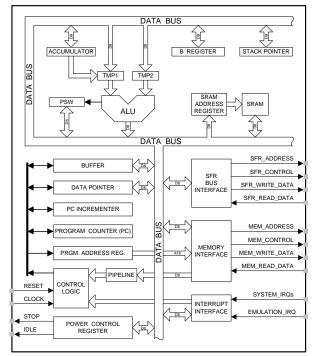

The C8051F85x/86x uses the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 15.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 15.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. The CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 15.1. CIP-51 Block Diagram

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute | 1 | 2 | 2/3 | 3 | 3/4 | 4 | 4/5 | 5 | 8 |

|-------------------|---|---|-----|---|-----|---|-----|---|---|

|-------------------|---|---|-----|---|-----|---|-----|---|---|

# Register 15.5. B: B Register

| Bit                                 | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------------------------------|-----------------|---|---|---|---|---|---|---|--|

| Name                                | B               |   |   |   |   |   |   |   |  |

| Туре                                | RW              |   |   |   |   |   |   |   |  |

| Reset                               | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |  |

| SFR Address: 0xF0 (bit-addressable) |                 |   |   |   |   |   |   |   |  |

# Table 15.6. B Register Bit Descriptions

| Bit | Name | Function                                                                        |

|-----|------|---------------------------------------------------------------------------------|

| 7:0 | В    | B Register.                                                                     |

|     |      | This register serves as a second accumulator for certain arithmetic operations. |

# Register 17.4. CPT1CN: Comparator 1 Control

| Bit     | 7                 | 6     | 5     | 4     | 3     | 2 | 1     | 0 |  |  |

|---------|-------------------|-------|-------|-------|-------|---|-------|---|--|--|

| Name    | CPEN              | CPOUT | CPRIF | CPFIF | СРНҮР |   | CPHYN |   |  |  |

| Туре    | RW                | R     | RW    | RW    | RW    |   | RW    |   |  |  |

| Reset   | 0                 | 0     | 0     | 0     | 0 0   |   | 0 0   |   |  |  |

| SFR Add | SFR Address: 0xBF |       |       |       |       |   |       |   |  |  |

# Table 17.8. CPT1CN Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CPEN  | Comparator 1 Enable Bit.         0: Comparator Disabled.         1: Comparator Enabled.                                                                                                                               |

| 6   | CPOUT | Comparator 1 Output State Flag.0: Voltage on CP1P < CP1N.                                                                                                                                                             |

| 5   | CPRIF | <ul> <li>Comparator 1 Rising-Edge Flag. Must be cleared by software.</li> <li>0: No Comparator Rising Edge has occurred since this flag was last cleared.</li> <li>1: Comparator Rising Edge has occurred.</li> </ul> |

| 4   | CPFIF | Comparator 1 Falling-Edge Flag. Must be cleared by software.0: No Comparator Falling Edge has occurred since this flag was last cleared.1: Comparator Falling Edge has occurred.                                      |

| 3:2 | СРНҮР | Comparator 1 Positive Hysteresis Control Bits.00: Positive Hysteresis Disabled.01: Positive Hysteresis = 5 mV.10: Positive Hysteresis = 10 mV.11: Positive Hysteresis = 20 mV.                                        |

| 1:0 | CPHYN | Comparator 1 Negative Hysteresis Control Bits.00: Negative Hysteresis Disabled.01: Negative Hysteresis = 5 mV.10: Negative Hysteresis = 10 mV.11: Negative Hysteresis = 20 mV.                                        |

# Register 18.3. CRC0DAT: CRC0 Data Output

| '               | 6 | 5   | 4     | 3 | 2 | 1 | 0 |

|-----------------|---|-----|-------|---|---|---|---|

| CRC0DAT         |   |     |       |   |   |   |   |

| RW              |   |     |       |   |   |   |   |

| 0 0 0 0 0 0 0 0 |   |     |       |   |   |   |   |

|                 | 0 | 0 0 | 0 0 0 |   |   |   |   |

### Table 18.4. CRC0DAT Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                              |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0DAT | CRC Data Output.                                                                                                                                                                      |

|     |         | Each read or write performed on CRC0DAT targets the CRC result bits pointed to by the CRC0 Result Pointer (CRC0PNT bits in CRC0CN).                                                   |

|     |         | be valid for one cycle after setting the CRC0INIT bit in the CRC0CN register to 1. Any time in to 1 by firmware, at least one instruction should be performed before reading CRC0DAT. |

# Register 18.5. CRC0CNT: CRC0 Automatic Flash Sector Count

| Bit     | 7                 | 6    | 5     | 4         | 3 | 2 | 1 | 0 |  |  |

|---------|-------------------|------|-------|-----------|---|---|---|---|--|--|

| Name    | CRCDN             | Rese | erved | CRCCNT    |   |   |   |   |  |  |

| Туре    | R                 | F    | २     | RW        |   |   |   |   |  |  |

| Reset   | 1                 | 0    | 0     | 0 0 0 0 0 |   |   |   |   |  |  |

| SFR Add | SFR Address: 0xD3 |      |       |           |   |   |   |   |  |  |

### Table 18.6. CRC0CNT Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                            |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CRCDN    | Automatic CRC Calculation Complete.                                                                                                                                                                                                                 |

|     |          | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                            |

| 6:5 | Reserved | Must write reset value.                                                                                                                                                                                                                             |

| 4:0 | CRCCNT   | Automatic CRC Calculation Block Count.                                                                                                                                                                                                              |

|     |          | These bits specify the number of flash blocks to include in an automatic CRC calculation.<br>The last address of the last flash block included in the automatic CRC calculation is<br>(CRCST+CRCCNT) x Block Size - 1. The block size is 256 bytes. |

### 20.6. PCA Control Registers

| Bit   | 7  | 6  | 5 | 4        | 3 | 2    | 1    | 0    |

|-------|----|----|---|----------|---|------|------|------|

| Name  | CF | CR |   | Reserved |   | CCF2 | CCF1 | CCF0 |

| Туре  | RW | RW |   | R        |   |      | RW   | RW   |

| Reset | 0  | 0  | 0 | 0        | 0 | 0    | 0    | 0    |

|       |    |    |   | •        |   |      |      |      |

### Register 20.1. PCA0CN: PCA Control

#### SFR Address: 0xD8 (bit-addressable)

# Table 20.3. PCA0CN Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CF       | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                          |

|     |          | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000. When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software. |

| 6   | CR       | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                            |

|     |          | This bit enables/disables the PCA Counter/Timer.                                                                                                                                                                                                                                                          |

|     |          | 0: PCA Counter/Timer disabled.                                                                                                                                                                                                                                                                            |

|     |          | 1: PCA Counter/Timer enabled.                                                                                                                                                                                                                                                                             |

| 5:3 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                   |

| 2   | CCF2     | PCA Module 2 Capture/Compare Flag.                                                                                                                                                                                                                                                                        |

|     |          | This bit is set by hardware when a match or capture occurs. When the CCF2 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                        |

| 1   | CCF1     | PCA Module 1 Capture/Compare Flag.                                                                                                                                                                                                                                                                        |

|     |          | This bit is set by hardware when a match or capture occurs. When the CCF1 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                        |

| 0   | CCF0     | PCA Module 0 Capture/Compare Flag.                                                                                                                                                                                                                                                                        |

|     |          | This bit is set by hardware when a match or capture occurs. When the CCF0 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                        |

# Register 20.16. PCA0CPL2: PCA Capture Module Low Byte

| Bit     | 7                 | 6  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------------|----|---|---|---|---|---|---|--|--|

| Dit     | •                 | 0  | 5 | - | 5 | L | I | 0 |  |  |

| Name    | PCA0CPL2          |    |   |   |   |   |   |   |  |  |

| Туре    |                   | RW |   |   |   |   |   |   |  |  |

| Reset   | 0 0 0 0 0 0 0 0 0 |    |   |   |   |   |   |   |  |  |

| SFR Add | SFR Address: 0xEB |    |   |   |   |   |   |   |  |  |

### Table 20.18. PCA0CPL2 Register Bit Descriptions

| Bit     | Name                                                                          | Function                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0     | PCA0CPL2                                                                      | PCA Capture Module Low Byte.                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|         |                                                                               | The PCA0CPL2 register holds the low byte (LSB) of the 16-bit capture module. This reg-<br>ister address also allows access to the low byte of the corresponding PCA channels<br>auto-reload value for 9 to 11-bit PWM mode. The ARSEL bit in register PCA0PWM con-<br>trols which register is accessed. |  |  |  |  |  |

| Note: A | <b>Note:</b> A write to this register will clear the modules ECOM bit to a 0. |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

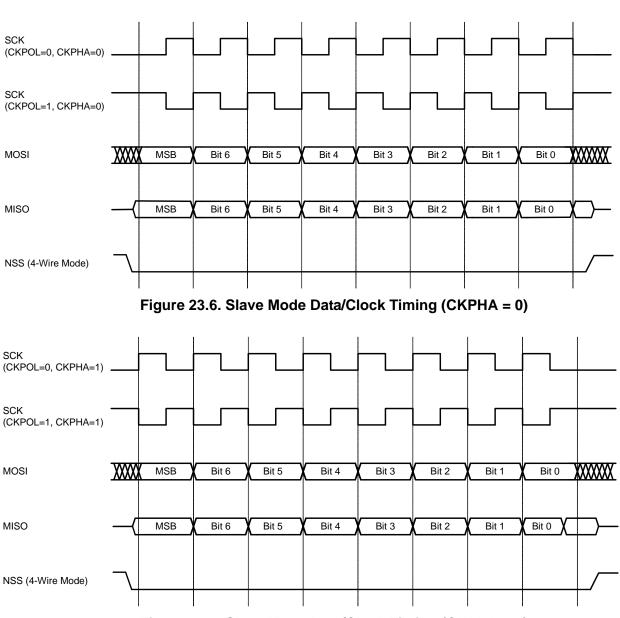

### 23.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

# Register 23.4. SPI0DAT: SPI0 Data

| Bit               | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|---------|---|---|---|---|---|---|---|

| Name              | SPIODAT |   |   |   |   |   |   |   |

| Туре              | RW      |   |   |   |   |   |   |   |

| Reset             | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address: 0xA3 |         |   |   |   |   |   |   |   |

### Table 23.5. SPI0DAT Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                                             |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT | SPI0 Transmit and Receive Data.                                                                                                                                                                                                                      |

|     |         | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0-<br>DAT places the data into the transmit buffer and initiates a transfer when in master mode.<br>A read of SPI0DAT returns the contents of the receive buffer. |

# Register 24.3. SMB0CN: SMBus0 Control

| Bit                                 | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0  |

|-------------------------------------|--------|--------|-----|-----|-------|---------|-----|----|

| Name                                | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI |

| Туре                                | R      | R      | RW  | RW  | R     | R       | RW  | RW |

| Reset                               | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0  |

| SFR Address: 0xC0 (bit-addressable) |        |        |     |     |       |         |     |    |

### Table 24.9. SMB0CN Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | <ul> <li>SMBus0 Master/Slave Indicator.</li> <li>This read-only bit indicates when the SMBus0 is operating as a master.</li> <li>0: SMBus0 operating in slave mode.</li> <li>1: SMBus0 operating in master mode.</li> </ul>                                                                                                                                                                            |

| 6   | TXMODE  | <ul> <li>SMBus0 Transmit Mode Indicator.</li> <li>This read-only bit indicates when the SMBus0 is operating as a transmitter.</li> <li>0: SMBus0 in Receiver Mode.</li> <li>1: SMBus0 in Transmitter Mode.</li> </ul>                                                                                                                                                                                  |

| 5   | STA     | <b>SMBus0 Start Flag.</b><br>When reading STA, a 1 indicates that a start or repeated start condition was detected on the bus.<br>Writing a 1 to the STA bit initiates a start or repeated start on the bus.                                                                                                                                                                                           |

| 4   | STO     | <ul> <li>SMBus0 Stop Flag.</li> <li>When reading STO, a 1 indicates that a stop condition was detected on the bus (in slave mode) or is pending (in master mode).</li> <li>When acting as a master, writing a 1 to the STO bit initiates a stop condition on the bus. This bit is cleared by hardware.</li> </ul>                                                                                      |

| 3   | ACKRQ   | SMBus0 Acknowledge Request.         0: No ACK requested.         1: ACK requested.                                                                                                                                                                                                                                                                                                                     |

| 2   | ARBLOST | SMBus0 Arbitration Lost Indicator.0: No arbitration error.1: Arbitration error occurred.                                                                                                                                                                                                                                                                                                               |

| 1   | ACK     | <ul> <li>SMBus0 Acknowledge.</li> <li>When read as a master, the ACK bit indicates whether an ACK (1) or NACK (0) is received during the most recent byte transfer.</li> <li>As a slave, this bit should be written to send an ACK (1) or NACK (0) to a master request. Note that the logic level of the ACK bit on the SMBus interface is inverted from the logic of the register ACK bit.</li> </ul> |

### 27.5. Watchdog Timer Control Registers

### Register 27.1. WDTCN: Watchdog Timer Control

| Bit               | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|-----------------|---|---|---|---|---|---|---|

| Name              | WDTCN           |   |   |   |   |   |   |   |

| Туре              | RW              |   |   |   |   |   |   |   |

| Reset             | 0 0 0 1 0 1 1 1 |   |   |   |   |   |   |   |

| SFR Address: 0x97 |                 |   |   |   |   |   |   |   |

### Table 27.1. WDTCN Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                       |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | WDTCN | WDT Control.                                                                                                                                   |

|     |       | The WDT control field has different behavior for reads and writes.                                                                             |

|     |       | Read:                                                                                                                                          |

|     |       | When reading the WDTCN register, the lower three bits (WDTCN[2:0]) indicate the cur-                                                           |

|     |       | rent timeout interval. Bit WDTCN.4 indicates whether the WDT is active (logic 1) or inac-                                                      |

|     |       | tive (logic 0).                                                                                                                                |

|     |       | Write:                                                                                                                                         |

|     |       | Writing the WDTCN register can set the timeout interval, enable the WDT, disable the WDT, reset the WDT, or lock the WDT to prevent disabling. |

|     |       | Writing to WDTCN with the MSB (WDTCN.7) cleared to 0 will set the timeout interval to                                                          |

|     |       | the value in bits WDTCN[2:0].                                                                                                                  |

|     |       | Writing 0xA5 both enables and reloads the WDT.                                                                                                 |

|     |       | Writing 0xDE followed within 4 system clocks by 0xAD disables the WDT.                                                                         |

|     |       | Writing 0xFF locks out the disable feature until the next device reset.                                                                        |