# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f854-c-iur |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Туре          | Pin Numbers   | Crossbar Capability | Additional Digital Functions | Analog Functions |

|----------|---------------|---------------|---------------------|------------------------------|------------------|

| N/C      | No Connection | 1<br>13<br>24 |                     |                              |                  |

#### Table 3.1. Pin Definitions for C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU

| Pin Name         | Туре                                        | Pin Numbers | Crossbar Capability | Additional Digital Functions          | Analog Functions           |

|------------------|---------------------------------------------|-------------|---------------------|---------------------------------------|----------------------------|

| P0.1             | Standard I/O                                | 2           | Yes                 | POMAT.1<br>INT0.1<br>INT1.1           | ADC0.1<br>CP0P.1<br>CP0N.1 |

| P0.2             | Standard I/O                                | 1           | Yes                 | POMAT.2<br>INT0.2<br>INT1.2           | ADC0.2<br>CP0P.2<br>CP0N.2 |

| P0.3 /<br>EXTCLK | Standard I/O /<br>External CMOS Clock Input | 16          | Yes                 | POMAT.3<br>EXTCLK<br>INT0.3<br>INT1.3 | ADC0.3<br>CP0P.3<br>CP0N.3 |

| P0.4             | Standard I/O                                | 15          | Yes                 | POMAT.4<br>INT0.4<br>INT1.4           | ADC0.4<br>CP0P.4<br>CP0N.4 |

| P0.5             | Standard I/O                                | 14          | Yes                 | P0MAT.5<br>INT0.5<br>INT1.5           | ADC0.5<br>CP0P.5<br>CP0N.5 |

| P0.6             | Standard I/O                                | 13          | Yes                 | POMAT.6<br>CNVSTR<br>INT0.6<br>INT1.6 | ADC0.6<br>CP1P.0<br>CP1N.0 |

| P0.7             | Standard I/O                                | 12          | Yes                 | POMAT.7<br>INT0.7<br>INT1.7           | ADC0.7<br>CP1P.1<br>CP1N.1 |

| P1.0             | Standard I/O                                | 11          | Yes                 | P1MAT.0                               | ADC0.8<br>CP1P.2<br>CP1N.2 |

#### Table 3.3. Pin Definitions for C8051F860/1/2/3/4/5-GS and C8051F860/1/2/3/4/5-IS

## C8051F85x/86x

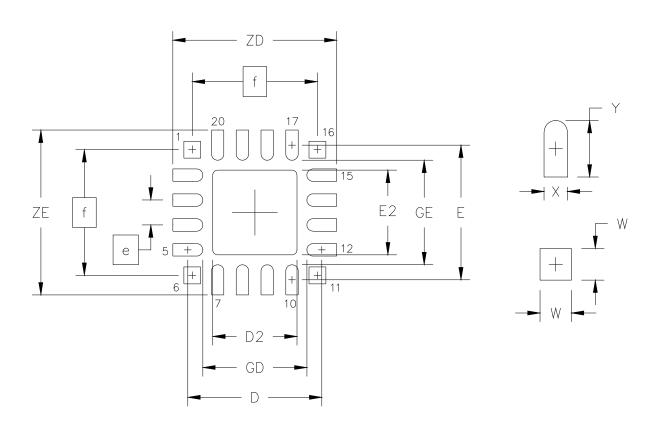

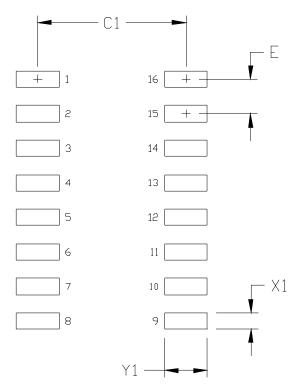

Figure 6.2. QFN-20 Landing Diagram

| Dimension         | Feature            | (mm) |

|-------------------|--------------------|------|

| C1                | Pad Column Spacing | 5.40 |

| Е                 | Pad Row Pitch      | 1.27 |

| X1                | Pad Width          | 0.60 |

| Y1                | Pad Length         | 1.55 |

| Notes:<br>General |                    |      |

$\label{eq:linear} \textbf{1.} \hspace{0.1 cm} \text{All dimensions shown are in millimeters (mm) unless otherwise noted.}$

2. This Land Pattern Design is based on IPC-7351 pattern SOIC127P600X165-16N for Density Level B (Median Land Protrusion).

**3.** All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.

## Register 14.9. ADC0GTH: ADC0 Greater-Than High Byte

| ADC0GTH         |   |  |  |  |  |  |  |  |

|-----------------|---|--|--|--|--|--|--|--|

| RW              |   |  |  |  |  |  |  |  |

| 1 1 1 1 1 1 1 1 |   |  |  |  |  |  |  |  |

|                 | 1 |  |  |  |  |  |  |  |

#### Table 14.12. ADC0GTH Register Bit Descriptions

| Bit | Name    | Function                                                                  |

|-----|---------|---------------------------------------------------------------------------|

| 7:0 | ADC0GTH | Greater-Than High Byte.                                                   |

|     |         | Most Significant Byte of the 16-bit Greater-Than window compare register. |

#### Register 14.14. REF0CN: Voltage Reference Control

| Bit     | 7                 | 6        | 5     | 4     | 3     | 2                  | 1 | 0     |  |

|---------|-------------------|----------|-------|-------|-------|--------------------|---|-------|--|

| Name    | IREFLVL           | Reserved | GNDSL | REFSL |       | FSL TEMPE Reserved |   | erved |  |

| Туре    | RW                | R        | RW    | R     | RW RW |                    | F | २     |  |

| Reset   | 0                 | 0        | 0     | 1     | 1 1 0 |                    | 0 | 0     |  |

| SFR Add | SFR Address: 0xD1 |          |       |       |       |                    |   |       |  |

## Table 14.17. REF0CN Register Bit Descriptions

| Bit | Name     | Function                                                                     |

|-----|----------|------------------------------------------------------------------------------|

| 7   | IREFLVL  | Internal Voltage Reference Level.                                            |

|     |          | Sets the voltage level for the internal reference source.                    |

|     |          | 0: The internal reference operates at 1.65 V nominal.                        |

|     |          | 1: The internal reference operates at 2.4 V nominal.                         |

| 6   | Reserved | Must write reset value.                                                      |

| 5   | GNDSL    | Analog Ground Reference.                                                     |

|     |          | Selects the ADC0 ground reference.                                           |

|     |          | 0: The ADC0 ground reference is the GND pin.                                 |

|     |          | 1: The ADC0 ground reference is the AGND pin.                                |

| 4:3 | REFSL    | Voltage Reference Select.                                                    |

|     |          | Selects the ADC0 voltage reference.                                          |

|     |          | 00: The ADC0 voltage reference is the VREF pin.                              |

|     |          | 01: The ADC0 voltage reference is the VDD pin.                               |

|     |          | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage. |

|     |          | 11: The ADC0 voltage reference is the internal voltage reference.            |

| 2   | TEMPE    | Temperature Sensor Enable.                                                   |

|     |          | Enables/Disables the internal temperature sensor.                            |

|     |          | 0: Temperature Sensor Disabled.                                              |

|     |          | 1: Temperature Sensor Enabled.                                               |

| 1:0 | Reserved | Must write reset value.                                                      |

#### 16.5. High Frequency Oscillator Control Registers

#### Register 16.1. OSCICL: High Frequency Oscillator Calibration

| Bit     | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------------------|---|---|---|---|---|---|---|--|

| Name    | OSCICL            |   |   |   |   |   |   |   |  |

| Туре    | RW                |   |   |   |   |   |   |   |  |

| Reset   | X X X X X X X X   |   |   |   |   |   |   |   |  |

| SFR Add | SFR Address: 0xC7 |   |   |   |   |   |   |   |  |

#### Table 16.1. OSCICL Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                                                                                                                         |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | OSCICL | Oscillator Calibration Bits.                                                                                                                                                                                                                                                                     |

|     |        | These bits determine the internal oscillator period. When set to 0000000b, the oscillator operates at its fastest setting. When set to 1111111b, the oscillator operates at its slowest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz. |

#### Register 17.2. CPT0MD: Comparator 0 Mode

| Bit     | 7                 | 6        | 5     | 4     | 3        | 2 | 1    | 0 |  |

|---------|-------------------|----------|-------|-------|----------|---|------|---|--|

| Name    | CPLOUT            | Reserved | CPRIE | CPFIE | Reserved |   | CPMD |   |  |

| Туре    | RW                | R        | RW    | RW    | R        |   | RW   |   |  |

| Reset   | 0                 | 0        | 0     | 0     | 0 0      |   | 1    | 0 |  |

| SFR Add | SFR Address: 0x9D |          |       |       |          |   |      |   |  |

## Table 17.6. CPT0MD Register Bit Descriptions

| Bit | Name     | Function                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------|

| 7   | CPLOUT   | Comparator 0 Latched Output Flag.                                                        |

|     |          | This bit represents the comparator output value at the most recent PCA counter overflow. |

|     |          | 0: Comparator output was logic low at last PCA overflow.                                 |

|     |          | 1: Comparator output was logic high at last PCA overflow.                                |

| 6   | Reserved | Must write reset value.                                                                  |

| 5   | CPRIE    | Comparator 0 Rising-Edge Interrupt Enable.                                               |

|     |          | 0: Comparator Rising-Edge interrupt disabled.                                            |

|     |          | 1: Comparator Rising-Edge interrupt enabled.                                             |

| 4   | CPFIE    | Comparator 0 Falling-Edge Interrupt Enable.                                              |

|     |          | 0: Comparator Falling-Edge interrupt disabled.                                           |

|     |          | 1: Comparator Falling-Edge interrupt enabled.                                            |

| 3:2 | Reserved | Must write reset value.                                                                  |

| 1:0 | CPMD     | Comparator 0 Mode Select.                                                                |

|     |          | These bits affect the response time and power consumption of the comparator.             |

|     |          | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)                            |

|     |          | 01: Mode 1                                                                               |

|     |          | 10: Mode 2                                                                               |

|     |          | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)                             |

## Register 20.2. PCA0MD: PCA Mode

| Bit     | 7                 | 6        | 5 | 4 | 3   | 2 | 1 | 0   |

|---------|-------------------|----------|---|---|-----|---|---|-----|

| Name    | CIDL              | Reserved |   |   | CPS |   |   | ECF |

| Туре    | RW                | R        |   |   | RW  |   |   | RW  |

| Reset   | 0                 | 0        | 0 | 0 | 0   | 0 | 0 | 0   |

| SFR Add | SFR Address: 0xD9 |          |   |   |     |   |   |     |

## Table 20.4. PCA0MD Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CIDL     | <ul> <li>PCA Counter/Timer Idle Control.</li> <li>Specifies PCA behavior when CPU is in Idle Mode.</li> <li>0: PCA continues to function normally while the system controller is in Idle Mode.</li> <li>1: PCA operation is suspended while the system controller is in Idle Mode.</li> </ul>                                                                                                                                                                                               |

| 6:4 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3:1 | CPS      | PCA Counter/Timer Pulse Select.         These bits select the timebase source for the PCA counter.         000: System clock divided by 12.         001: System clock divided by 4.         010: Timer 0 overflow.         011: High-to-low transitions on ECI (max rate = system clock divided by 4).         100: System clock.         101: External clock divided by 8 (synchronized with the system clock).         110: Low frequency oscillator divided by 8.         111: Reserved. |

| 0   | ECF      | <ul> <li>PCA Counter/Timer Overflow Interrupt Enable.</li> <li>This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.</li> <li>0: Disable the CF interrupt.</li> <li>1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.</li> </ul>                                                                                                                                                                                                    |

## Register 20.4. PCA0CLR: PCA Comparator Clear Control

| Bit     | 7                 | 6 | 5        | 4 | 3 | 2 | 1     | 0     |

|---------|-------------------|---|----------|---|---|---|-------|-------|

| Name    | CPCPOL            |   | Reserved |   |   |   | CPCE1 | CPCE0 |

| Туре    | RW                |   | R        |   |   |   | RW    | RW    |

| Reset   | 0                 | 0 | 0        | 0 | 0 | 0 | 0     | 0     |

| SFR Add | SFR Address: 0x9C |   |          |   |   |   |       |       |

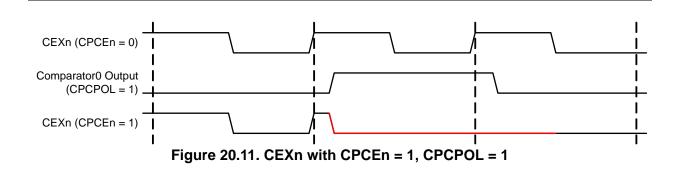

#### Table 20.6. PCA0CLR Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                   |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CPCPOL   | Comparator Clear Polarity.                                                                                                                                                                                                                 |

|     |          | Selects the polarity of the comparator result that will clear the PCA channel(s).<br>0: PCA channel(s) will be cleared when comparator result goes logic low.<br>1: PCA channel(s) will be cleared when comparator result goes logic high. |

| 6:3 | Reserved | Must write reset value.                                                                                                                                                                                                                    |

| 2   | CPCE2    | Comparator Clear Enable for CEX2.                                                                                                                                                                                                          |

|     |          | Enables the comparator clear function on PCA channel 2.                                                                                                                                                                                    |

| 1   | CPCE1    | Comparator Clear Enable for CEX1.                                                                                                                                                                                                          |

|     |          | Enables the comparator clear function on PCA channel 1.                                                                                                                                                                                    |

| 0   | CPCE0    | Comparator Clear Enable for CEX0.                                                                                                                                                                                                          |

|     |          | Enables the comparator clear function on PCA channel 0.                                                                                                                                                                                    |

#### Register 20.9. PCA0CPH0: PCA Capture Module High Byte

| Bit     | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-------------------|---|---|---|---|---|---|---|

| Name    | PCA0CPH0          |   |   |   |   |   |   |   |

| Туре    | RW                |   |   |   |   |   |   |   |

| Reset   | 0                 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Add | SFR Address: 0xFC |   |   |   |   |   |   |   |

#### Table 20.11. PCA0CPH0 Register Bit Descriptions

| Bit     | Name                                                                 | Function                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0     | PCA0CPH0                                                             | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                |  |  |  |  |  |

|         |                                                                      | The PCA0CPH0 register holds the high byte (MSB) of the 16-bit capture module. This register address also allows access to the high byte of the corresponding PCA channels auto-reload value for 9 to 11-bit PWM mode. The ARSEL bit in register PCA0PWM controls which register is accessed. |  |  |  |  |  |

| Note: A | ote: A write to this register will set the module's ECOM bit to a 1. |                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

#### 21.7. Port I/O and Pin Configuration Control Registers

| Bit   | 7      | 6     | 5    | 4     | 3    | 2     | 1     | 0     |

|-------|--------|-------|------|-------|------|-------|-------|-------|

| Name  | SYSCKE | CP1AE | CP1E | CP0AE | CP0E | SMB0E | SPI0E | URT0E |

| Туре  | RW     | RW    | RW   | RW    | RW   | RW    | RW    | RW    |

| Reset | 0      | 0     | 0    | 0     | 0    | 0     | 0     | 0     |

#### Register 21.1. XBR0: Port I/O Crossbar 0

#### Table 21.4. XBR0 Register Bit Descriptions

| Bit | Name   | Function                                                                         |

|-----|--------|----------------------------------------------------------------------------------|

| 7   | SYSCKE | SYSCLK Output Enable.                                                            |

|     |        | 0: SYSCLK unavailable at Port pin.                                               |

|     |        | 1: SYSCLK output routed to Port pin.                                             |

| 6   | CP1AE  | Comparator1 Asynchronous Output Enable.                                          |

|     |        | 0: Asynchronous CP1 unavailable at Port pin.                                     |

|     |        | 1: Asynchronous CP1 routed to Port pin.                                          |

| 5   | CP1E   | Comparator1 Output Enable.                                                       |

|     |        | 0: CP1 unavailable at Port pin.                                                  |

|     |        | 1: CP1 routed to Port pin.                                                       |

| 4   | CP0AE  | Comparator0 Asynchronous Output Enable.                                          |

|     |        | 0: Asynchronous CP0 unavailable at Port pin.                                     |

|     |        | 1: Asynchronous CP0 routed to Port pin.                                          |

| 3   | CP0E   | Comparator0 Output Enable.                                                       |

|     |        | 0: CP0 unavailable at Port pin.                                                  |

|     |        | 1: CP0 routed to Port pin.                                                       |

| 2   | SMB0E  | SMBus0 I/O Enable.                                                               |

|     |        | 0: SMBus0 I/O unavailable at Port pins.                                          |

|     |        | 1: SMBus0 I/O routed to Port pins.                                               |

| 1   | SPI0E  | SPI I/O Enable.                                                                  |

|     |        | 0: SPI I/O unavailable at Port pins.                                             |

|     |        | 1: SPI I/O routed to Port pins. The SPI can be assigned either 3 or 4 GPIO pins. |

| 0   | URT0E  | UART I/O Output Enable.                                                          |

|     |        | 0: UART I/O unavailable at Port pin.                                             |

|     |        | 1: UART TX, RX routed to Port pins P0.4 and P0.5.                                |

| Bit | Name  | Function                                            |

|-----|-------|-----------------------------------------------------|

| 0   | SPIEN | SPI0 Enable.<br>0: SPI disabled.<br>1: SPI enabled. |

#### Table 23.3. SPI0CN Register Bit Descriptions

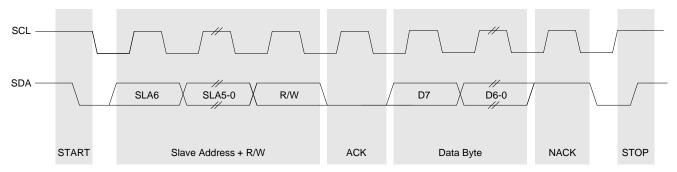

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 24.3 illustrates a typical SMBus transaction.

Figure 24.3. SMBus Transaction

#### 24.3.1. Transmitter vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 24.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "24.3.5. SCL High (SMBus Free) Timeout" on page 236). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 24.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 24.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

## Register 24.3. SMB0CN: SMBus0 Control

| Bit                                 | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0  |

|-------------------------------------|--------|--------|-----|-----|-------|---------|-----|----|

| Name                                | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI |

| Туре                                | R      | R      | RW  | RW  | R     | R       | RW  | RW |

| Reset                               | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0  |

| SFR Address: 0xC0 (bit-addressable) |        |        |     |     |       |         |     |    |

#### Table 24.9. SMB0CN Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | <ul> <li>SMBus0 Master/Slave Indicator.</li> <li>This read-only bit indicates when the SMBus0 is operating as a master.</li> <li>0: SMBus0 operating in slave mode.</li> <li>1: SMBus0 operating in master mode.</li> </ul>                                                                                                                                                                            |

| 6   | TXMODE  | <ul> <li>SMBus0 Transmit Mode Indicator.</li> <li>This read-only bit indicates when the SMBus0 is operating as a transmitter.</li> <li>0: SMBus0 in Receiver Mode.</li> <li>1: SMBus0 in Transmitter Mode.</li> </ul>                                                                                                                                                                                  |

| 5   | STA     | <b>SMBus0 Start Flag.</b><br>When reading STA, a 1 indicates that a start or repeated start condition was detected on the bus.<br>Writing a 1 to the STA bit initiates a start or repeated start on the bus.                                                                                                                                                                                           |

| 4   | STO     | <ul> <li>SMBus0 Stop Flag.</li> <li>When reading STO, a 1 indicates that a stop condition was detected on the bus (in slave mode) or is pending (in master mode).</li> <li>When acting as a master, writing a 1 to the STO bit initiates a stop condition on the bus. This bit is cleared by hardware.</li> </ul>                                                                                      |

| 3   | ACKRQ   | SMBus0 Acknowledge Request.         0: No ACK requested.         1: ACK requested.                                                                                                                                                                                                                                                                                                                     |

| 2   | ARBLOST | SMBus0 Arbitration Lost Indicator.0: No arbitration error.1: Arbitration error occurred.                                                                                                                                                                                                                                                                                                               |

| 1   | ACK     | <ul> <li>SMBus0 Acknowledge.</li> <li>When read as a master, the ACK bit indicates whether an ACK (1) or NACK (0) is received during the most recent byte transfer.</li> <li>As a slave, this bit should be written to send an ACK (1) or NACK (0) to a master request. Note that the logic level of the ACK bit on the SMBus interface is inverted from the logic of the register ACK bit.</li> </ul> |

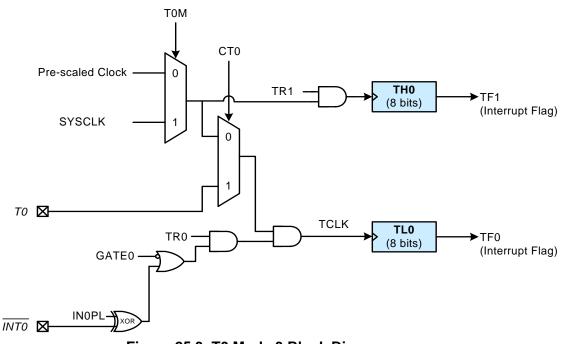

#### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/ timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, CT0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 25.3. T0 Mode 3 Block Diagram

## Register 25.2. TCON: Timer 0/1 Control

| Bit                                 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name                                | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| Туре                                | RW  |

| Reset                               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| SFR Address: 0x88 (bit-addressable) |     |     |     |     |     |     |     |     |

#### Table 25.4. TCON Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                                                                                                        |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag.                                                                                                                                                                                                                                          |

|     |      | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                   |

| 6   | TR1  | Timer 1 Run Control.                                                                                                                                                                                                                                            |

|     |      | Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                                                    |

| 5   | TF0  | Timer 0 Overflow Flag.                                                                                                                                                                                                                                          |

|     |      | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                   |

| 4   | TR0  | Timer 0 Run Control.                                                                                                                                                                                                                                            |

|     |      | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                    |

| 3   | IE1  | External Interrupt 1.                                                                                                                                                                                                                                           |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                         |

| 2   | IT1  | Interrupt 1 Type Select.                                                                                                                                                                                                                                        |

|     |      | <ul> <li>This bit selects whether the configured INT1 interrupt will be edge or level sensitive. INT1 is configured active low or high by the IN1PL bit in register IT01CF.</li> <li>0: INT1 is level triggered.</li> <li>1: INT1 is edge triggered.</li> </ul> |

| 1   | IE0  | External Interrupt 0.                                                                                                                                                                                                                                           |

|     |      | This flag is set by hardware when an edge/level of type defined by IT0 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                         |

| 0   | IT0  | Interrupt 0 Type Select.                                                                                                                                                                                                                                        |

|     |      | <ul><li>This bit selects whether the configured INT0 interrupt will be edge or level sensitive. INT0 is configured active low or high by the IN0PL bit in register IT01CF.</li><li>0: INT0 is level triggered.</li><li>1: INT0 is edge triggered.</li></ul>     |

## Register 25.9. TMR2RLL: Timer 2 Reload Low Byte

| Bit     | 7                 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---------|-------------------|---|---|-----|------|---|---|---|

| Name    |                   |   |   | TMR | 2RLL |   |   |   |

| Туре    | RW                |   |   |     |      |   |   |   |

| Reset   | 0                 | 0 | 0 | 0   | 0    | 0 | 0 | 0 |

| SFR Add | SFR Address: 0xCA |   |   |     |      |   |   |   |

#### Table 25.11. TMR2RLL Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2RLL | <b>Timer 2 Reload Low Byte.</b><br>When operating in one of the auto-reload modes, TMR2RLL holds the reload value for the low byte of Timer 2 (TMR2L). When operating in capture mode, TMR2RLL is the captured value of TMR2L. |

## Register 25.15. TMR3RLH: Timer 3 Reload High Byte

| Bit               | 7  | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|-------------------|----|---|---|-----|------|---|---|---|

| Name              |    |   |   | TMR | 3RLH |   |   |   |

| Туре              | RW |   |   |     |      |   |   |   |

| Reset             | 0  | 0 | 0 | 0   | 0    | 0 | 0 | 0 |

| SFR Address: 0x93 |    |   |   |     |      |   |   |   |

#### Table 25.17. TMR3RLH Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                     |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3RLH | Timer 3 Reload High Byte.                                                                                                                                                                    |

|     |         | When operating in one of the auto-reload modes, TMR3RLH holds the reload value for the high byte of Timer 3 (TMR3H). When oeprating in capture mode, TMR3RLH is the captured value of TMR3H. |