Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                            |

| Number of I/O              | 13                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                      |

| Data Converters            | A/D 12x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                   |

| Supplier Device Package    | -                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f860-c-gs |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Parameter                                                      | Symbol              | Test Condition                                      | Min | Тур | Max | Unit |

|----------------------------------------------------------------|---------------------|-----------------------------------------------------|-----|-----|-----|------|

| ADC0 Burst Mode, 10-bit sin-                                   | I <sub>ADC</sub>    | 200 ksps, V <sub>DD</sub> = 3.0 V                   |     | 490 |     | μA   |

| gle conversions, internal ref-<br>erence, Low power bias       |                     | 100 ksps, V <sub>DD</sub> = 3.0 V                   | _   | 245 |     | μA   |

| settings                                                       |                     | 10 ksps, V <sub>DD</sub> = 3.0 V                    | _   | 23  | _   | μA   |

| ADC0 Burst Mode, 12-bit sin-                                   | I <sub>ADC</sub>    | 100 ksps, V <sub>DD</sub> = 3.0 V                   | —   | 530 | _   | μA   |

| gle conversions, external ref-<br>erence                       |                     | 50 ksps, V <sub>DD</sub> = 3.0 V                    | _   | 265 | _   | μA   |

|                                                                |                     | 10 ksps, V <sub>DD</sub> = 3.0 V                    | _   | 53  | _   | μA   |

| ADC0 Burst Mode, 12-bit sin-<br>gle conversions, internal ref- | I <sub>ADC</sub>    | 100 ksps, V <sub>DD</sub> = 3.0 V,<br>Normal bias   | _   | 950 | _   | μA   |

| erence                                                         |                     | 50 ksps, V <sub>DD</sub> = 3.0 V,<br>Low power bias | _   | 420 | _   | μA   |

|                                                                |                     | 10 ksps, V <sub>DD</sub> = 3.0 V,<br>Low power bias | _   | 85  | _   | μA   |

| Internal ADC0 Reference,                                       | I <sub>IREF</sub>   | Normal Power Mode                                   | _   | 680 | 790 | μA   |

| Always-on <sup>5</sup>                                         |                     | Low Power Mode                                      | _   | 160 | 210 | μA   |

| Temperature Sensor                                             | I <sub>TSENSE</sub> |                                                     | _   | 75  | 120 | μA   |

| Comparator 0 (CMP0),                                           | I <sub>CMP</sub>    | CPnMD = 11                                          | _   | 0.5 |     | μA   |

| Comparator 1 (CMP1)                                            |                     | CPnMD = 10                                          | _   | 3   |     | μA   |

|                                                                |                     | CPnMD = 01                                          | _   | 10  | _   | μA   |

|                                                                |                     | CPnMD = 00                                          | _   | 25  | _   | μA   |

| Voltage Supply Monitor<br>(VMON0)                              | I <sub>VMON</sub>   |                                                     | _   | 15  | 20  | μA   |

Table 1.2. Power Consumption (Continued)

Notes:

1. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

2. Includes supply current from internal regulator, supply monitor, and High Frequency Oscillator.

3. Includes supply current from internal regulator, supply monitor, and Low Frequency Oscillator.

4. ADC0 always-on power excludes internal reference supply current.

5. The internal reference is enabled as-needed when operating the ADC in burst mode to save power.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory organization of the C8051F85x/ 86x.

Revision C C8051F852/5 and C8051F862/5 devices implement the upper four bytes of internal RAM as a 32-bit Unique Identifier. More information can be found in "Device Identification and Unique Identifier" on page 68.

#### 8.2.1.1. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word (PSW) register, RS0 and RS1, select the active register bank. This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 8.2.1.2. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 8.2.1.3. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 8.2.2. External RAM

On devices with 512 bytes total RAM, there are 256 bytes of on-chip RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode. Note: The 16-bit MOVX instruction is also used for writes to the flash memory. See Section "10. Flash Memory" on page 61 for details. The MOVX instruction accesses XRAM by default.

For a 16-bit MOVX operation (@DPTR), the upper 8 bits of the 16-bit external data memory address word are "don't cares". As a result, addresses 0x0000 through 0x00FF are mapped modulo style over the entire 64 k external data memory address range. For example, the XRAM byte at address 0x0000 is shadowed at addresses 0x0100, 0x0200, 0x0300, 0x0400, etc.

Revision C C8051F850/1/3/4 and C8051F860/1/3/4 devices implement the upper four bytes of external RAM as a 32-bit Unique Identifier. More information can be found in "Device Identification and Unique Identifier" on page 68.

## **11.1. Device Identification Registers**

## Register 11.1. DEVICEID: Device Identification

| Bit     | 7                 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-------------------|-----------------|---|---|---|---|---|---|

| Name    | DEVICEID          |                 |   |   |   |   |   |   |

| Туре    | R                 |                 |   |   |   |   |   |   |

| Reset   | 0                 | 0 0 1 1 0 0 0 0 |   |   |   |   |   |   |

| SFR Add | SFR Address: 0xB5 |                 |   |   |   |   |   |   |

## Table 11.2. DEVICEID Register Bit Descriptions

| Bit | Name     | Function                                                                   |

|-----|----------|----------------------------------------------------------------------------|

| 7:0 | DEVICEID | Device ID.                                                                 |

|     |          | This read-only register returns the 8-bit device ID: 0x30 (C8051F85x/86x). |

# Register 11.3. REVID: Revision Identifcation

| Bit   | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-------|---|---|---|----|-----|---|---|---|

| Name  |   |   |   | RE | /ID |   |   |   |

| Туре  | R |   |   |    |     |   |   |   |

| Reset | Х | Х | Х | Х  | Х   | Х | Х | Х |

# Table 11.4. REVID Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                       |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | REVID | Revision ID.                                                                                                                                                   |

|     |       | This read-only register returns the 8-bit revision ID.<br>00000000: Revision A<br>00000001: Revision B<br>00000010: Revision C<br>00000011-11111111: Reserved. |

# 13. Power Management and Internal Regulator

All internal circuitry on the C8051F85x/86x devices draws power from the VDD supply pin. Circuits with external connections (I/O pins, analog muxes) are powered directly from the VDD supply voltage, while most of the internal circuitry is supplied by an on-chip LDO regulator. The regulator output is fully internal to the device, and is available also as an ADC input or reference source for the comparators and ADC.

The devices support the standard 8051 power modes: idle and stop. For further power savings in stop mode, the internal LDO regulator may be disabled, shutting down the majority of the power nets on the device.

Although the C8051F85x/86x has idle and stop modes available, more control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers and serial buses, have their clocks gated off and draw little power when they are not in use.

#### 13.1. Power Modes

Idle mode halts the CPU while leaving the peripherals and clocks active. In stop mode, the CPU is halted, all interrupts and timers are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power because the majority of the device is shut down with no clocks active. The Power Control Register (PCON) is used to control the C8051F85x/86x's Stop and Idle power management modes.

#### 13.1.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the hardware to halt the CPU and enter idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has two or more opcode bytes, for example:

| PCON = PCON;                                       | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system.

| Required<br>Throughput | Reference Source | Mode Configuration                                    | SAR Clock Speed         | Other Register Field<br>Settings             |

|------------------------|------------------|-------------------------------------------------------|-------------------------|----------------------------------------------|

| 180-200 ksps           | Any              | Always-On +<br>Burst Mode<br>(ADEN = 1<br>ADBMEN = 1) | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x40<br>ADC0TK = 0xBF<br>ADRPT = 1 |

| 125-180 ksps           | Any              | Always-On +<br>Burst Mode<br>(ADEN = 1<br>ADBMEN = 1) | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x40<br>ADC0TK = 0x3A<br>ADRPT = 1 |

| 0-125 ksps             | External         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1)                | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x44<br>ADC0TK = 0x3A<br>ADRPT = 1 |

| 50-125 ksps            | Internal         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1)                | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x44<br>ADC0TK = 0x3A<br>ADRPT = 1 |

| 0-50 ksps              | Internal         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1)                | 4.08 MHz<br>(ADSC = 5)  | ADC0PWR = 0xF4<br>ADC0TK = 0x34<br>ADRPT = 1 |

Table 14.3. ADC0 Optimal Power Configuration (12-bit Mode)

**Note:** ADRPT reflects the minimum setting for this bit field. When using the ADC in Burst Mode, up to 64 samples may be auto-accumulated per conversion trigger by adjusting ADRPT.

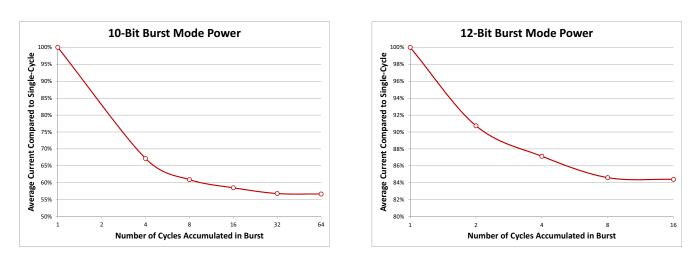

For applications where burst mode is used to automatically accumulate multiple results, additional supply current savings can be realized. The length of time the ADC is active during each burst contains power-up time at the beginning of the burst as well as the conversion time required for each conversion in the burst. The power-on time is only required at the beginning of each burst. When compared with single-sample bursts to collect the same number of conversions, multi-sample bursts will consume significantly less power. For example, performing an eight-cycle burst of 10-bt conversions consumes about 61% of the power required to perform those same eight samples in single-cycle bursts. For 12-bit conversions, an eight-cycle burst results in about 85% of the equivalent single-cycle bursts. Figure 14.5 shows this relationship for the different burst cycle lengths.

See the Electrical Characteristics chapter for details on power consumption and the maximum clock frequencies allowed in each mode.

## 14.6. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the ADSJST field. When the repeat count is set to 1 in 10-bit mode, conversion codes are represented as 10-bit unsigned integers. Inputs are measured from 0 to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to 0.

| Input Voltage    | Right-Justified<br>ADC0H:ADC0L (ADSJST = 000) | Left-Justified<br>ADC0H:ADC0L (ADSJST = 100) |

|------------------|-----------------------------------------------|----------------------------------------------|

|                  | ADCONADCOL (ADSJ31 = 000)                     |                                              |

| VREF x 1023/1024 | 0x03FF                                        | 0xFFC0                                       |

| VREF x 512/1024  | 0x0200                                        | 0x8000                                       |

| VREF x 256/1024  | 0x0100                                        | 0x4000                                       |

| 0                | 0x0000                                        | 0x0000                                       |

When the repeat count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, 16, 32, or 64 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the ADRPT bits in the ADCOAC register. When a repeat count is higher than 1, the ADC output must be right-justified (ADSJST = 0xx); unused bits in the ADCOH and ADCOL registers are set to 0. The example below shows the right-justified result for various input voltages and repeat counts. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 16 | Repeat Count = 64 |

|------------------------------|------------------|-------------------|-------------------|

| V <sub>REF</sub> x 1023/1024 | 0x0FFC           | 0x3FF0            | 0xFFC0            |

| V <sub>REF</sub> x 512/1024  | 0x0800           | 0x2000            | 0x8000            |

| V <sub>REF</sub> x 511/1024  | 0x07FC           | 0x1FF0            | 0x7FC0            |

| 0                            | 0x0000           | 0x0000            | 0x0000            |

## Register 14.11. ADC0LTH: ADC0 Less-Than High Byte

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | ADCOLTH |   |   |   |   |   |   |   |

| Туре  | RW      |   |   |   |   |   |   |   |

| Reset | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## Table 14.14. ADC0LTH Register Bit Descriptions

| Bit | Name    | Function                                                               |

|-----|---------|------------------------------------------------------------------------|

| 7:0 | ADC0LTH | Less-Than High Byte.                                                   |

|     |         | Most Significant Byte of the 16-bit Less-Than window compare register. |

# 15. CIP-51 Microcontroller Core

The C8051F85x/86x uses the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

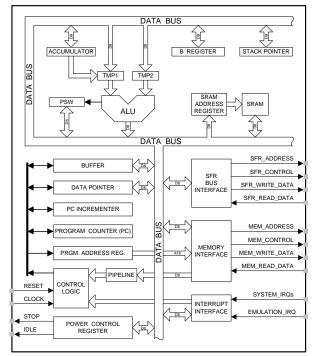

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 15.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 15.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. The CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 15.1. CIP-51 Block Diagram

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute | 1 | 2 | 2/3 | 3 | 3/4 | 4 | 4/5 | 5 | 8 |

|-------------------|---|---|-----|---|-----|---|-----|---|---|

|-------------------|---|---|-----|---|-----|---|-----|---|---|

# Register 15.5. B: B Register

| Bit      | 7                                   | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------|-------------------------------------|---------------|---|---|---|---|---|---|--|--|

| Name     | B                                   |               |   |   |   |   |   |   |  |  |

| Туре     | RW                                  |               |   |   |   |   |   |   |  |  |

| Reset    | 0                                   | 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

| SFR Addr | SFR Address: 0xF0 (bit-addressable) |               |   |   |   |   |   |   |  |  |

# Table 15.6. B Register Bit Descriptions

| Bit | Name | Function                                                                        |

|-----|------|---------------------------------------------------------------------------------|

| 7:0 | В    | B Register.                                                                     |

|     |      | This register serves as a second accumulator for certain arithmetic operations. |

## Register 17.3. CPT0MX: Comparator 0 Multiplexer Selection

| Bit   | 7    | 6 | 5 | 4 | 3    | 2 | 1 | 0 |  |

|-------|------|---|---|---|------|---|---|---|--|

| Name  | CMXN |   |   |   | СМХР |   |   |   |  |

| Туре  |      | R | W |   | RW   |   |   |   |  |

| Reset | 1    | 1 | 1 | 1 | 1    | 1 | 1 | 1 |  |

# Table 17.7. CPT0MX Register Bit Descriptions

| Bit | Name | Function                                   |

|-----|------|--------------------------------------------|

| 7:4 | CMXN | Comparator 0 Negative Input MUX Selection. |

|     |      | 0000: External pin CP0N.0                  |

|     |      | 0001: External pin CP0N.1                  |

|     |      | 0010: External pin CP0N.2                  |

|     |      | 0011: External pin CP0N.3                  |

|     |      | 0100: External pin CP0N.4                  |

|     |      | 0101: External pin CP0N.5                  |

|     |      | 0110: External pin CP0N.6                  |

|     |      | 0111: External pin CP0N.7                  |

|     |      | 1000: GND                                  |

|     |      | 1001-1111: Reserved.                       |

| 3:0 | CMXP | Comparator 0 Positive Input MUX Selection. |

|     |      | 0000: External pin CP0P.0                  |

|     |      | 0001: External pin CP0P.1                  |

|     |      | 0010: External pin CP0P.2                  |

|     |      | 0011: External pin CP0P.3                  |

|     |      | 0100: External pin CP0P.4                  |

|     |      | 0101: External pin CP0P.5                  |

|     |      | 0110: External pin CP0P.6                  |

|     |      | 0111: External pin CP0P.7                  |

|     |      | 1000: Internal LDO output                  |

|     |      | 1001-1111: Reserved.                       |

# Register 18.3. CRC0DAT: CRC0 Data Output

| '               | 6 | 5   | 4     | 3 | 2 | 1 | 0 |  |  |

|-----------------|---|-----|-------|---|---|---|---|--|--|

| CRC0DAT         |   |     |       |   |   |   |   |  |  |

| RW              |   |     |       |   |   |   |   |  |  |

| 0 0 0 0 0 0 0 0 |   |     |       |   |   |   |   |  |  |

|                 | 0 | 0 0 | 0 0 0 |   |   |   |   |  |  |

## Table 18.4. CRC0DAT Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0DAT | CRC Data Output.                                                                                                                                                                        |

|     |         | Each read or write performed on CRC0DAT targets the CRC result bits pointed to by the CRC0 Result Pointer (CRC0PNT bits in CRC0CN).                                                     |

|     |         | t be valid for one cycle after setting the CRC0INIT bit in the CRC0CN register to 1. Any time in to 1 by firmware, at least one instruction should be performed before reading CRC0DAT. |

# Register 20.6. PCA0L: PCA Counter/Timer Low Byte

| Bit   | 7           | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------|-----------------|---|---|---|---|---|---|--|--|--|

| Name  |             | PCA0L           |   |   |   |   |   |   |  |  |  |

| Туре  | RW          |                 |   |   |   |   |   |   |  |  |  |

| Reset | 0           | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

|       | lress: 0xF9 | Ŭ               | Ŭ | Ŭ | Ŭ | Ŭ | Ŭ |   |  |  |  |

## Table 20.8. PCA0L Register Bit Descriptions

| Bit | Name  | Function                                                                     |

|-----|-------|------------------------------------------------------------------------------|

| 7:0 | PCA0L | PCA Counter/Timer Low Byte.                                                  |

|     |       | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |

## Register 20.12. PCA0CPM1: PCA Capture/Compare Mode

| Bit     | 7           | 6    | 5    | 4    | 3   | 2   | 1   | 0    |

|---------|-------------|------|------|------|-----|-----|-----|------|

| Name    | PWM16       | ECOM | CAPP | CAPN | MAT | TOG | PWM | ECCF |

| Туре    | RW          | RW   | RW   | RW   | RW  | RW  | RW  | RW   |

| Reset   | 0           | 0    | 0    | 0    | 0   | 0   | 0   | 0    |

| SFR Add | lress: 0xDB |      |      |      |     |     |     |      |

## Table 20.14. PCA0CPM1 Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWM16 | 16-bit Pulse Width Modulation Enable.                                                                                                                                                                                                                                             |

|     |       | This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.<br>0: 8 to 11-bit PWM selected.                                                                                                                                                                         |

|     |       | 1: 16-bit PWM selected.                                                                                                                                                                                                                                                           |

| 6   | ECOM  | Comparator Function Enable.                                                                                                                                                                                                                                                       |

|     |       | This bit enables the comparator function.                                                                                                                                                                                                                                         |

| 5   | CAPP  | Capture Positive Function Enable.                                                                                                                                                                                                                                                 |

|     |       | This bit enables the positive edge capture capability.                                                                                                                                                                                                                            |

| 4   | CAPN  | Capture Negative Function Enable.                                                                                                                                                                                                                                                 |

|     |       | This bit enables the negative edge capture capability.                                                                                                                                                                                                                            |

| 3   | MAT   | Match Function Enable.                                                                                                                                                                                                                                                            |

|     |       | This bit enables the match function. When enabled, matches of the PCA counter with a module's capture/compare register cause the CCF1 bit in the PCA0MD register to be set to logic 1.                                                                                            |

| 2   | TOG   | Toggle Function Enable.                                                                                                                                                                                                                                                           |

|     |       | This bit enables the toggle function. When enabled, matches of the PCA counter with the capture/compare register cause the logic level on the CEX1 pin to toggle. If the PWM bit is also set to logic 1, the module operates in Frequency Output Mode.                            |

| 1   | PWM   | Pulse Width Modulation Mode Enable.                                                                                                                                                                                                                                               |

|     |       | This bit enables the PWM function. When enabled, a pulse width modulated signal is output on the CEX1 pin. 8 to 11-bit PWM is used if PWM16 is cleared; 16-bit mode is used if PWM16 is set to logic 1. If the TOG bit is also set, the module operates in Frequency Output Mode. |

| 0   | ECCF  | Capture/Compare Flag Interrupt Enable.                                                                                                                                                                                                                                            |

|     |       | This bit sets the masking of the Capture/Compare Flag (CCF1) interrupt.<br>0: Disable CCF1 interrupts.                                                                                                                                                                            |

|     |       | 1: Enable a Capture/Compare Flag interrupt request when CCF1 is set.                                                                                                                                                                                                              |

# Register 21.3. XBR2: Port I/O Crossbar 2

| Bit     | 7                 | 6     | 5 4 3 2 1 0 |   |  |  |  |  |  |  |

|---------|-------------------|-------|-------------|---|--|--|--|--|--|--|

| Name    | WEAKPUD           | XBARE | Reserved    |   |  |  |  |  |  |  |

| Туре    | RW                | RW    |             | R |  |  |  |  |  |  |

| Reset   | 0                 | 0     | 0 0 0 0 0 0 |   |  |  |  |  |  |  |

| SFR Add | SFR Address: 0xE3 |       |             |   |  |  |  |  |  |  |

# Table 21.6. XBR2 Register Bit Descriptions

| Bit | Name     | Function                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------|

| 7   | WEAKPUD  | Port I/O Weak Pullup Disable.                                                                                     |

|     |          | 0: Weak Pullups enabled (except for Ports whose I/O are configured for analog mode).<br>1: Weak Pullups disabled. |

| 6   | XBARE    | Crossbar Enable.                                                                                                  |

|     |          | 0: Crossbar disabled.<br>1: Crossbar enabled.                                                                     |

| 5:0 | Reserved | Must write reset value.                                                                                           |

## 22.11. Supply Monitor Control Registers

| Bit   | 7     | 6       | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---------|----------|---|---|---|---|---|

| Name  | VDMEN | VDDSTAT | Reserved |   |   |   |   |   |

| Туре  | RW    | R       | R        |   |   |   |   |   |

| Reset | Х     | Х       | Х        | Х | Х | Х | Х | Х |

## Register 22.2. VDM0CN: Supply Monitor Control

SFR Address: 0xFF

# Table 22.2. VDM0CN Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN    | Supply Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |          | This bit turns the supply monitor circuit on/off. The supply monitor cannot generate sys-<br>tem resets until it is also selected as a reset source in register RSTSRC. Selecting the<br>supply monitor as a reset source before it has stabilized may generate a system reset. In<br>systems where this reset would be undesirable, a delay should be introduced between<br>enabling the supply monitor and selecting it as a reset source.<br>0: Supply Monitor Disabled.<br>1: Supply Monitor Enabled. |

| 6   | VDDSTAT  | Supply Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          | <ul> <li>This bit indicates the current power supply status (supply monitor output).</li> <li>0: V<sub>DD</sub> is at or below the supply monitor threshold.</li> <li>1: V<sub>DD</sub> is above the supply monitor threshold.</li> </ul>                                                                                                                                                                                                                                                                 |

| 5:0 | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary for SMBus compliance when SYSCLK is above 10 MHz.

| EXTHOLD          | Minimum SDA Setup Time                                                                                                                                                                                                                                                                                                 | Minimum SDA Hold Time |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|--|

| 0                | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup>                                                                                                                                                                                                                                    | 3 system clocks       |  |  |  |  |  |  |

| 1                | 11 system clocks                                                                                                                                                                                                                                                                                                       | 12 system clocks      |  |  |  |  |  |  |

| w delay occurs b | Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgment, the s/<br>w delay occurs between the time SMB0DAT or ACK is written and when SI0 is cleared. Note that if SI is cleared in the<br>same write that defines the outgoing ACK value, s/w delay is zero. |                       |  |  |  |  |  |  |

#### Table 24.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "24.3.4. SCL Low Timeout" on page 235). The SMBus interface will force the associated timer to reload while SCL is high, and allow the timer to count when SCL is low. The timer interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 24.4).

#### 24.4.2. SMBus Pin Swap

The SMBus peripheral is assigned to pins using the priority crossbar decoder. By default, the SMBus signals are assigned to port pins starting with SDA on the lower-numbered pin, and SCL on the next available pin. The SWAP bit in the SMBTC register can be set to 1 to reverse the order in which the SMBus signals are assigned.

#### 24.4.3. SMBus Timing Control

The SDD field in the SMBTC register is used to restrict the detection of a START condition under certain circumstances. In some systems where there is significant mismatch between the impedance or the capacitance on the SDA and SCL lines, it may be possible for SCL to fall after SDA during an address or data transfer. Such an event can cause a false START detection on the bus. These kind of events are not expected in a standard SMBus or I2C-compliant system. In most systems this parameter should not be adjusted, and it is recommended that it be left at its default value.

By default, if the SCL falling edge is detected after the falling edge of SDA (i.e. one SYSCLK cycle or more), the device will detect this as a START condition. The SDD field is used to increase the amount of hold time that is required between SDA and SCL falling before a START is recognized. An additional 2, 4, or 8 SYSCLKs can be added to prevent false START detection in systems where the bus conditions warrant this.

#### 24.4.4. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information. The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

# Register 25.16. TMR3L: Timer 3 Low Byte

| Bit     | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-------------------|---|---|---|---|---|---|---|

| Name    | TMR3L             |   |   |   |   |   |   |   |

| Туре    | RW                |   |   |   |   |   |   |   |

| Reset   | 0 0 0 0 0 0 0 0   |   |   |   |   |   |   |   |

| SFR Add | SFR Address: 0x94 |   |   |   |   |   |   |   |

## Table 25.18. TMR3L Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                      |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L | Timer 3 Low Byte.                                                                                                                             |

|     |       | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-bit mode, TMR3L contains the 8-bit low byte timer value. |

# Register 29.2. C2DEVID: C2 Device ID

| Bit              | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|-----------------|---|---|---|---|---|---|---|

| Name             | C2DEVID         |   |   |   |   |   |   |   |

| Туре             | R               |   |   |   |   |   |   |   |

| Reset            | 0 0 1 1 0 0 0 0 |   |   |   |   |   |   |   |

| C2 Address: 0x00 |                 |   |   |   |   |   |   |   |

# Table 29.2. C2DEVID Register Bit Descriptions

| Bit | Name    | Function                                                                   |

|-----|---------|----------------------------------------------------------------------------|

| 7:0 | C2DEVID | Device ID.                                                                 |

|     |         | This read-only register returns the 8-bit device ID: 0x30 (C8051F85x/86x). |

# Register 29.4. C2FPCTL: C2 Flash Programming Control

| Bit     | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----------------|---|---|---|---|---|---|---|

| Name    | C2FPCTL         |   |   |   |   |   |   |   |

| Туре    | RW              |   |   |   |   |   |   |   |

| Reset   | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

| C2 Addr | 2 Address: 0x02 |   |   |   |   |   |   |   |

## Table 29.4. C2FPCTL Register Bit Descriptions

| Bit | Name    | Function                                                                                                                                                                                                                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | C2FPCTL | Flash Programming Control Register.                                                                                                                                                                                                                                         |

|     |         | This register is used to enable flash programming via the C2 interface. To enable C2 flash programming, the following codes must be written in order: 0x02, 0x01. Note that once C2 flash programming is enabled, a system reset must be issued to resume normal operation. |