Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                            |

| Number of I/O              | 13                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                      |

| Data Converters            | A/D 12x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                   |

| Supplier Device Package    | -                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f861-c-is |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1.7. ADC (Continued)

| Parameter                        | Symbol            | Test Condition                    | Min      | Тур       | Max     | Unit   |

|----------------------------------|-------------------|-----------------------------------|----------|-----------|---------|--------|

| Offset Error                     | E <sub>OFF</sub>  | 12 Bit Mode, VREF = 1.65 V        | -3       | 0         | 3       | LSB    |

|                                  | -                 | 10 Bit Mode, VREF = 1.65 V        | -2       | 0         | 2       | LSB    |

| Offset Temperature Coefficient   | TC <sub>OFF</sub> |                                   | _        | 0.004     | _       | LSB/°C |

| Slope Error                      | E <sub>M</sub>    | 12 Bit Mode                       |          | ±0.02     | ±0.1    | %      |

|                                  | -                 | 10 Bit Mode                       |          | ±0.06     | ±0.24   | %      |

| Dynamic Performance 10 k         | Hz Sine Wa        | ve Input 1dB below full scale, Ma | x throug | ghput, us | sing AG | ND pin |

| Signal-to-Noise                  | SNR               | 12 Bit Mode                       | 61       | 66        |         | dB     |

|                                  | -                 | 10 Bit Mode                       | 53       | 60        |         | dB     |

| Signal-to-Noise Plus Distor-     | SNDR              | 12 Bit Mode                       | 61       | 66        |         | dB     |

| tion                             |                   | 10 Bit Mode                       | 53       | 60        |         | dB     |

| Total Harmonic Distortion        | THD               | 12 Bit Mode                       | —        | 71        | _       | dB     |

| (Up to 5th Harmonic)             | -                 | 10 Bit Mode                       | _        | 70        | _       | dB     |

| Spurious-Free Dynamic            | SFDR              | 12 Bit Mode                       | _        | -79       | _       | dB     |

| Range                            | -                 | 10 Bit Mode                       |          | -74       |         | dB     |

| *Note: Absolute input pin voltag | ge is limited by  | r the V <sub>DD</sub> supply.     | 1        | 1         | 1       | 1      |

### 2.7. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- The core halts program execution.

- Module registers are initialized to their defined reset values unless the bits reset only with a poweron reset.

- External port pins are forced to a known state.

- Interrupts and timers are disabled.

All registers are reset to the predefined values noted in the register descriptions unless the bits only reset with a power-on reset. The contents of RAM are unaffected during a reset; any previously stored data is preserved as long as power is not lost.

The Port I/O latches are reset to 1 in open-drain mode. Weak pullups are enabled during and after the reset. For VDD Supply Monitor and power-on resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal low-power oscillator. The Watchdog Timer is enabled with the Low Frequency Oscillator (LFO0) as its clock source. Program execution begins at location 0x0000.

## 2.8. On-Chip Debugging

The C8051F85x/86x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

| Pin Name      | Туре                            | Pin Numbers | Crossbar Capability | Additional Digital Functions | Analog Functions            |

|---------------|---------------------------------|-------------|---------------------|------------------------------|-----------------------------|

| P1.0          | Standard I/O                    | 18          | Yes                 | P1MAT.0                      | ADC0.8<br>CP1P.0<br>CP1N.0  |

| P1.1          | Standard I/O                    | 17          | Yes                 | P1MAT.1                      | ADC0.9<br>CP1P.1<br>CP1N.1  |

| P1.2          | Standard I/O                    | 16          | Yes                 | P1MAT.2                      | ADC0.10<br>CP1P.2<br>CP1N.2 |

| P1.3          | Standard I/O                    | 15          | Yes                 | P1MAT.3                      | ADC0.11<br>CP1P.3<br>CP1N.3 |

| P1.4          | Standard I/O                    | 14          | Yes                 | P1MAT.4                      | ADC0.12<br>CP1P.4<br>CP1N.4 |

| P1.5          | Standard I/O                    | 11          | Yes                 | P1MAT.5                      | ADC0.13<br>CP1P.5<br>CP1N.5 |

| P1.6          | Standard I/O                    | 10          | Yes                 | P1MAT.6                      | ADC0.14<br>CP1P.6<br>CP1N.6 |

| P1.7          | Standard I/O                    | 9           | Yes                 | P1MAT.7                      | ADC0.15<br>CP1P.7<br>CP1N.7 |

| P2.0 /<br>C2D | Standard I/O /<br>C2 Debug Data | 8           |                     |                              |                             |

| P2.1          | Standard I/O                    | 12          |                     |                              |                             |

#### Table 3.1. Pin Definitions for C8051F850/1/2/3/4/5-GU and C8051F850/1/2/3/4/5-IU

| Register | Address | Register Description                  | Page |

|----------|---------|---------------------------------------|------|

| IE       | 0xA8    | Interrupt Enable                      | 75   |

| IP       | 0xB8    | Interrupt Priority                    | 77   |

| IT01CF   | 0xE4    | INT0 / INT1 Configuration             | 150  |

| OSCICL   | 0xC7    | High Frequency Oscillator Calibration | 127  |

| OSCLCN   | 0xB1    | Low Frequency Oscillator Control      | 128  |

| P0       | 0x80    | Port 0 Pin Latch                      | 199  |

| POMASK   | 0xFE    | Port 0 Mask                           | 197  |

| POMAT    | 0xFD    | Port 0 Match                          | 198  |

| POMDIN   | 0xF1    | Port 0 Input Mode                     | 200  |

| POMDOUT  | 0xA4    | Port 0 Output Mode                    | 201  |

| P0SKIP   | 0xD4    | Port 0 Skip                           | 202  |

| P1       | 0x90    | Port 1 Pin Latch                      | 205  |

| P1MASK   | 0xEE    | Port 1 Mask                           | 203  |

| P1MAT    | 0xED    | Port 1 Match                          | 204  |

| P1MDIN   | 0xF2    | Port 1 Input Mode                     | 206  |

| P1MDOUT  | 0xA5    | Port 1 Output Mode                    | 207  |

| P1SKIP   | 0xD5    | Port 1 Skip                           | 208  |

| P2       | 0xA0    | Port 2 Pin Latch                      | 209  |

| P2MDOUT  | 0xA6    | Port 2 Output Mode                    | 210  |

| PCA0CENT | 0x9E    | PCA Center Alignment Enable           | 177  |

| PCA0CLR  | 0x9C    | PCA Comparator Clear Control          | 170  |

| PCA0CN   | 0xD8    | PCA Control                           | 167  |

| PCA0CPH0 | 0xFC    | PCA Capture Module High Byte 0        | 175  |

| PCA0CPH1 | 0xEA    | PCA Capture Module High Byte 1        | 181  |

| PCA0CPH2 | 0xEC    | PCA Capture Module High Byte 2        | 183  |

| PCA0CPL0 | 0xFB    | PCA Capture Module Low Byte 0         | 174  |

| PCA0CPL1 | 0xE9    | PCA Capture Module Low Byte 1         | 180  |

| PCA0CPL2 | 0xEB    | PCA Capture Module Low Byte 2         | 182  |

## Table 9.2. Special Function Registers (Continued)

## **11.1. Device Identification Registers**

## Register 11.1. DEVICEID: Device Identification

| Bit     | 7                 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------------|-----------------|---|---|---|---|---|---|--|--|

| Name    |                   | DEVICEID        |   |   |   |   |   |   |  |  |

| Туре    | R                 |                 |   |   |   |   |   |   |  |  |

| Reset   | 0                 | 0 0 1 1 0 0 0 0 |   |   |   |   |   |   |  |  |

| SFR Add | SFR Address: 0xB5 |                 |   |   |   |   |   |   |  |  |

## Table 11.2. DEVICEID Register Bit Descriptions

| Bit | Name     | Function                                                                   |

|-----|----------|----------------------------------------------------------------------------|

| 7:0 | DEVICEID | Device ID.                                                                 |

|     |          | This read-only register returns the 8-bit device ID: 0x30 (C8051F85x/86x). |

## 14.6. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the ADSJST field. When the repeat count is set to 1 in 10-bit mode, conversion codes are represented as 10-bit unsigned integers. Inputs are measured from 0 to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to 0.

| Input Voltage    | Right-Justified<br>ADC0H:ADC0L (ADSJST = 000) | Left-Justified<br>ADC0H:ADC0L (ADSJST = 100) |

|------------------|-----------------------------------------------|----------------------------------------------|

|                  | ADCONADCOL (ADSJ31 = 000)                     |                                              |

| VREF x 1023/1024 | 0x03FF                                        | 0xFFC0                                       |

| VREF x 512/1024  | 0x0200                                        | 0x8000                                       |

| VREF x 256/1024  | 0x0100                                        | 0x4000                                       |

| 0                | 0x0000                                        | 0x0000                                       |

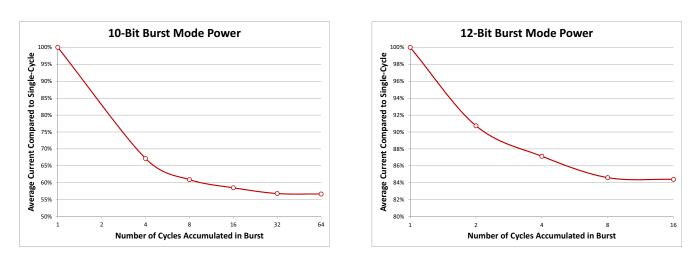

When the repeat count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, 16, 32, or 64 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the ADRPT bits in the ADCOAC register. When a repeat count is higher than 1, the ADC output must be right-justified (ADSJST = 0xx); unused bits in the ADCOH and ADCOL registers are set to 0. The example below shows the right-justified result for various input voltages and repeat counts. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 16 | Repeat Count = 64 |

|------------------------------|------------------|-------------------|-------------------|

| V <sub>REF</sub> x 1023/1024 | 0x0FFC           | 0x3FF0            | 0xFFC0            |

| V <sub>REF</sub> x 512/1024  | 0x0800           | 0x2000            | 0x8000            |

| V <sub>REF</sub> x 511/1024  | 0x07FC           | 0x1FF0            | 0x7FC0            |

| 0                            | 0x0000           | 0x0000            | 0x0000            |

## Register 14.6. ADC0TK: ADC0 Burst Mode Track Time

| Bit               | 7      | 6        | 5           | 4 | 3 | 2 | 1 | 0 |

|-------------------|--------|----------|-------------|---|---|---|---|---|

| Name              | AD12SM | Reserved | ADTK        |   |   |   |   |   |

| Туре              | RW     | RW       | RW          |   |   |   |   |   |

| Reset             | 0      | 0        | 0 1 1 1 1 0 |   |   |   |   |   |

| SFR Address: 0xB9 |        |          |             |   |   |   |   |   |

# Table 14.9. ADC0TK Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD12SM   | 12-Bit Sampling Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |          | <ul> <li>This bit controls the way that the ADC samples the input when in 12-bit mode. When the ADC is configured for multiple 12-bit conversions in burst mode, the AD12SM bit should be cleared to 0.</li> <li>0: The ADC will re-track and sample the input four times during a 12-bit conversion.</li> <li>1: The ADC will sample the input once at the beginning of each 12-bit conversion. The ADTK field can be set to 63 to maximize throughput.</li> </ul> |

| 6   | Reserved | Must write reset value.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5:0 | ADTK     | Burst Mode Tracking Time.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          | This field sets the time delay between consecutive conversions performed in Burst Mode. When ADTM is set, an additional 4 SARCLKs are added to this time.                                                                                                                                                                                                                                                                                                           |

|     |          | $T_{BMTK} = \frac{64 - ADTK}{F_{HFOSC}}$                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          | The Burst Mode track delay is not inserted prior to the first conversion. The required tracking time for the first conversion should be defined with the ADPWR field.                                                                                                                                                                                                                                                                                               |

| Number of Instructions | 26 | 50 | 5 | 14 | 7 | 3 | 1 | 2 | 1 |

|------------------------|----|----|---|----|---|---|---|---|---|

|------------------------|----|----|---|----|---|---|---|---|---|

#### **15.2.** Programming and Debugging Support

In-system programming of the flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

#### 15.3. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 15.3.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 15.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

Rev. 1.0

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| XCH A, Rn            | Exchange Register with A                            | 1     | 1               |

| XCH A, direct        | Exchange direct byte with A                         | 2     | 2               |

| XCH A, @Ri           | Exchange indirect RAM with A                        | 1     | 2               |

| XCHD A, @Ri          | Exchange low nibble of indirect RAM with A          | 1     | 2               |

|                      | Boolean Manipulation                                |       |                 |

| CLR C                | Clear Carry                                         | 1     | 1               |

| CLR bit              | Clear direct bit                                    | 2     | 2               |

| SETB C               | Set Carry                                           | 1     | 1               |

| SETB bit             | Set direct bit                                      | 2     | 2               |

| CPL C                | Complement Carry                                    | 1     | 1               |

| CPL bit              | Complement direct bit                               | 2     | 2               |

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/4             |

|                      | Program Branching                                   |       |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16         | Long subroutine call                                | 3     | 4               |

| RET                  | Return from subroutine                              | 1     | 5               |

| RETI                 | Return from interrupt                               | 1     | 5               |

| AJMP addr11          | Absolute jump                                       | 2     | 3               |

| LJMP addr16          | Long jump                                           | 3     | 4               |

| SJMP rel             | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3             |

## Table 15.1. CIP-51 Instruction Set Summary (Continued)

## Register 15.3. SP: Stack Pointer

| Bit     | 7           | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-------------|-----------------|---|---|---|---|---|---|--|--|--|

| Name    | SP          |                 |   |   |   |   |   |   |  |  |  |

| Туре    | RW          |                 |   |   |   |   |   |   |  |  |  |

| Reset   | 0           | 0 0 0 0 0 1 1 1 |   |   |   |   |   |   |  |  |  |

| SFR Add | lress: 0x81 |                 |   |   |   |   |   |   |  |  |  |

## Table 15.4. SP Register Bit Descriptions

| Bit | Name | Function                                                                                                                                                                       |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP   | Stack Pointer.                                                                                                                                                                 |

|     |      | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

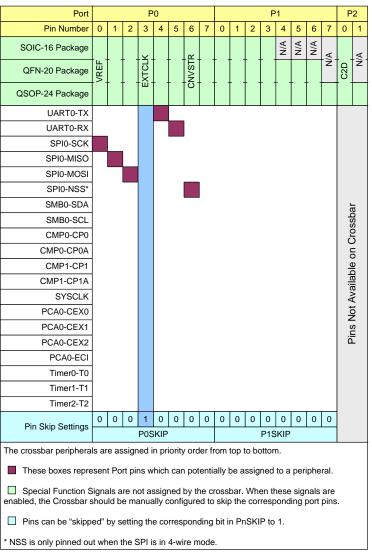

Registers XBR0, XBR1 and XBR2 are used to assign the digital I/O resources to the physical I/O port pins. Note that when the SMBus is selected, the crossbar assigns both pins associated with the SMBus (SDA and SCL); when UART0 is selected, the crossbar assigns both pins associated with UART0 (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART0 TX is always assigned to P0.4; UART0 RX is always assigned to P0.5. Standard port I/Os appear contiguously after the prioritized functions have been assigned.

Figure 21.3 shows an example of the resulting pin assignments of the device with UART0 and SPI0 enabled and the EXTCLK (P0.3) pin skipped (P0SKIP = 0x08). UART0 is the highest priority and it will be assigned first. The UART0 pins can only appear on P0.4 and P0.5, so that is where it is assigned. The next-highest enabled peripheral is SPI0. P0.0, P0.1 and P0.2 are free, so SPI0 takes these three pins. The fourth pin, NSS, is routed to P0.6 because P0.3 is skipped and P0.4 and P0.5 are already occupied by the UART. The other pins on the device are available for use as general-purpose digital I/O or analog functions.

Figure 21.3. Crossbar Priority Decoder Example

# Register 21.2. XBR1: Port I/O Crossbar 1

| Bit   | 7    | 6     | 5   | 4   | 3   | 2    | 1      | 0 |

|-------|------|-------|-----|-----|-----|------|--------|---|

| Name  | Rese | erved | T2E | T1E | T0E | ECIE | PCA0ME |   |

| Туре  | R    | RW    | RW  | RW  | RW  | RW   | RW     |   |

| Reset | 0    | 0     | 0   | 0   | 0   | 0    | 0 0    |   |

## Table 21.5. XBR1 Register Bit Descriptions

| Bit | Name     | Function                                                                         |

|-----|----------|----------------------------------------------------------------------------------|

| 7:6 | Reserved | Must write reset value.                                                          |

| 5   | T2E      | T2 Enable.         0: T2 unavailable at Port pin.                                |

|     |          | 1: T2 routed to Port pin.                                                        |

| 4   | T1E      | T1 Enable.                                                                       |

|     |          | 0: T1 unavailable at Port pin.                                                   |

|     |          | 1: T1 routed to Port pin.                                                        |

| 3   | T0E      | T0 Enable.                                                                       |

|     |          | 0: T0 unavailable at Port pin.                                                   |

|     |          | 1: T0 routed to Port pin.                                                        |

| 2   | ECIE     | PCA0 External Counter Input Enable.                                              |

|     |          | 0: ECI unavailable at Port pin.                                                  |

|     |          | 1: ECI routed to Port pin.                                                       |

| 1:0 | PCA0ME   | PCA Module I/O Enable Bits.                                                      |

|     |          | 00: All PCA I/O unavailable at Port pins.                                        |

|     |          | 01: CEX0 routed to Port pin.                                                     |

|     |          | 10: CEX0, CEX1 routed to Port pins.<br>11: CEX0, CEX1, CEX2 routed to Port pins. |

|     |          |                                                                                  |

## Register 21.6. P0MAT: Port 0 Match

| Bit     | 7          | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------------|-----------------|---|---|---|---|---|---|--|--|--|

| Name    | POMAT      |                 |   |   |   |   |   |   |  |  |  |

| Туре    | RW         |                 |   |   |   |   |   |   |  |  |  |

| Reset   | 1          | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |  |

| SFR Add | ress: 0xFD |                 | 1 |   | 1 |   |   |   |  |  |  |

## Table 21.9. POMAT Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                     |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | POMAT | Port 0 Match Value.                                                                                                                                                                          |

|     |       | Match comparison value used on P0 pins for bits in P0MASK which are set to 1.<br>0: P0.x pin logic value is compared with logic LOW.<br>1: P0.x pin logic value is compared with logic HIGH. |

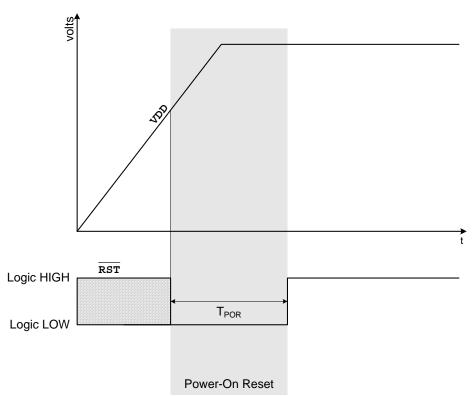

### 22.1. Power-On Reset

During power-up, the POR circuit will fire. When POR fires, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. Two delays are present during the supply ramp time. First, a delay will occur before the POR circuitry fires and pulls the  $\overline{RST}$  pin low. A second delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 22.2. plots the power-on reset timing. For ramp times less than 1 ms, the power-on reset time (T<sub>POR</sub>) is typically less than 0.3 ms. Additionally, the power supply must reach V<sub>RST</sub> before the POR circuit will release the device from reset.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled following a power-on reset.

Figure 22.2. Power-on Reset Timing

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 24.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

#### 24.4.4.1. Software ACK Generation

When the EHACK bit in register SMB0ADM is cleared to 0, the firmware on the device must detect incoming slave addresses and ACK or NACK the slave address and incoming data bytes. As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

#### 24.4.4.2. Hardware ACK Generation

When the EHACK bit in register SMB0ADM is set to 1, automatic slave address recognition and ACK generation is enabled. More detail about automatic slave address recognition can be found in Section 24.4.5. As a receiver, the value currently specified by the ACK bit will be automatically sent on the bus during the ACK cycle of an incoming data byte. As a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. The ACKRQ bit is not used when hardware ACK generation is enabled. If a received slave address is NACKed by hardware, further slave events will be ignored until the next START is detected, and no interrupt will be generated.

Table 24.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 24.5 for SMBus status decoding using the SMB0CN register.

| Bit    | Set by Hardware When:                                                    | Cleared by Hardware When:                                                          |

|--------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| MASTER | <ul> <li>A START is generated.</li> </ul>                                | <ul> <li>A STOP is generated.</li> </ul>                                           |

| WASTER |                                                                          | <ul> <li>Arbitration is lost.</li> </ul>                                           |

|        | <ul> <li>START is generated.</li> </ul>                                  | <ul> <li>A START is detected.</li> </ul>                                           |

| TXMODE | <ul> <li>SMB0DAT is written before the start of an</li> </ul>            | <ul> <li>Arbitration is lost.</li> </ul>                                           |

| TAMODE | SMBus frame.                                                             | <ul> <li>SMB0DAT is not written before the<br/>start of an SMBus frame.</li> </ul> |

| STA    | <ul> <li>A START followed by an address byte is<br/>received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                                   |

| STO    | <ul> <li>A STOP is detected while addressed as a<br/>slave.</li> </ul>   | <ul> <li>A pending STOP is generated.</li> </ul>                                   |

|        | <ul> <li>Arbitration is lost due to a detected STOP.</li> </ul>          |                                                                                    |

#### Table 24.3. Sources for Hardware Changes to SMB0CN

#### 24.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

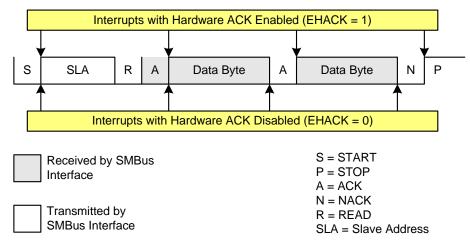

Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 24.6 shows a typical master read sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 24.6. Typical Master Read Sequence

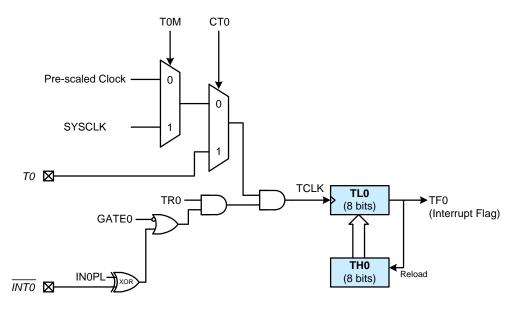

#### 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 in the TCON register is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit enables the timer when either GATE0 in the TMOD register is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF.

Figure 25.2. T0 Mode 2 Block Diagram

## Register 25.3. TMOD: Timer 0/1 Mode

| Bit   | 7     | 6   | 5   | 4 | 3     | 2   | 1   | 0 |

|-------|-------|-----|-----|---|-------|-----|-----|---|

| Name  | GATE1 | CT1 | T1M |   | GATE0 | CT0 | TOM |   |

| Туре  | RW    | RW  | RW  |   | RW    | RW  | R   | W |

| Reset | 0     | 0   | 0   | 0 | 0     | 0   | 0   | 0 |

## Table 25.5. TMOD Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE1 | Timer 1 Gate Control.0: Timer 1 enabled when TR1 = 1 irrespective of INT1 logic level.1: Timer 1 enabled only when TR1 = 1 and INT1 is active as defined by bit IN1PL in register IT01CF.                                                  |

| 6   | CT1   | Counter/Timer 1 Select.0: Timer Mode. Timer 1 increments on the clock defined by T1M in the CKCON register.1: Counter Mode. Timer 1 increments on high-to-low transitions of an external pin (T1).                                         |

| 5:4 | T1M   | Timer 1 Mode Select.These bits select the Timer 1 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Timer 1 Inactive                              |

| 3   | GATE0 | Timer 0 Gate Control.0: Timer 0 enabled when TR0 = 1 irrespective of INT0 logic level.1: Timer 0 enabled only when TR0 = 1 and INT0 is active as defined by bit IN0PL in register IT01CF.                                                  |

| 2   | СТО   | <ul> <li>Counter/Timer 0 Select.</li> <li>0: Timer Mode. Timer 0 increments on the clock defined by T0M in the CKCON register.</li> <li>1: Counter Mode. Timer 0 increments on high-to-low transitions of an external pin (T0).</li> </ul> |

| 1:0 | ТОМ   | Timer 0 Mode Select.These bits select the Timer 0 operation mode.00: Mode 0, 13-bit Counter/Timer01: Mode 1, 16-bit Counter/Timer10: Mode 2, 8-bit Counter/Timer with Auto-Reload11: Mode 3, Two 8-bit Counter/Timers                      |

## Register 25.16. TMR3L: Timer 3 Low Byte

| Bit     | 7          | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------------|---------------|---|---|---|---|---|---|--|--|--|

| Name    | TMR3L      |               |   |   |   |   |   |   |  |  |  |

| Туре    | RW         |               |   |   |   |   |   |   |  |  |  |

| Reset   | 0          | 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

| SFR Add | ress: 0x94 |               |   |   |   |   |   |   |  |  |  |

## Table 25.18. TMR3L Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                      |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L | Timer 3 Low Byte.                                                                                                                             |

|     |       | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-bit mode, TMR3L contains the 8-bit low byte timer value. |

## Register 29.2. C2DEVID: C2 Device ID

| Bit       | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|-----------------|---|---|---|---|---|---|---|--|--|--|

| Name      | C2DEVID         |   |   |   |   |   |   |   |  |  |  |

| Туре      | R               |   |   |   |   |   |   |   |  |  |  |

| Reset     | 0 0 1 1 0 0 0 0 |   |   |   |   |   |   |   |  |  |  |

| C2 Addres | ss: 0x00        |   |   |   |   |   |   |   |  |  |  |

# Table 29.2. C2DEVID Register Bit Descriptions

| Bit | Name    | Function                                                                   |

|-----|---------|----------------------------------------------------------------------------|

| 7:0 | C2DEVID | Device ID.                                                                 |

|     |         | This read-only register returns the 8-bit device ID: 0x30 (C8051F85x/86x). |