Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 13                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | -                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f864-c-isr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 1.10. Comparators

| Parameter                    | Symbol             | Test Condition         | Min   | Тур  | Max                   | Unit  |

|------------------------------|--------------------|------------------------|-------|------|-----------------------|-------|

| Positive Hysteresis          | HYS <sub>CP+</sub> | CPnHYP = 00            |       | 1.5  | _                     | mV    |

| Mode 3 (CPnMD = 11)          |                    | CPnHYP = 01            |       | 4    | _                     | mV    |

|                              |                    | CPnHYP = 10            |       | 8    | _                     | mV    |

|                              |                    | CPnHYP = 11            |       | 16   | _                     | mV    |

| Negative Hysteresis          | HYS <sub>CP-</sub> | CPnHYN = 00            | _     | -1.5 | —                     | mV    |

| Mode 3 (CPnMD = 11)          |                    | CPnHYN = 01            |       | -4   | _                     | mV    |

|                              |                    | CPnHYN = 10            |       | -8   | _                     | mV    |

|                              |                    | CPnHYN = 11            |       | -16  | _                     | mV    |

| Input Range (CP+ or CP-)     | V <sub>IN</sub>    |                        | -0.25 | _    | V <sub>DD</sub> +0.25 | V     |

| Input Pin Capacitance        | C <sub>CP</sub>    |                        | _     | 7.5  | —                     | pF    |

| Common-Mode Rejection Ratio  | CMRR <sub>CP</sub> |                        | _     | 70   | —                     | dB    |

| Power Supply Rejection Ratio | PSRR <sub>CP</sub> |                        |       | 72   | _                     | dB    |

| Input Offset Voltage         | V <sub>OFF</sub>   | T <sub>A</sub> = 25 °C | -10   | 0    | 10                    | mV    |

| Input Offset Tempco          | TC <sub>OFF</sub>  |                        |       | 3.5  | _                     | µV/⁰C |

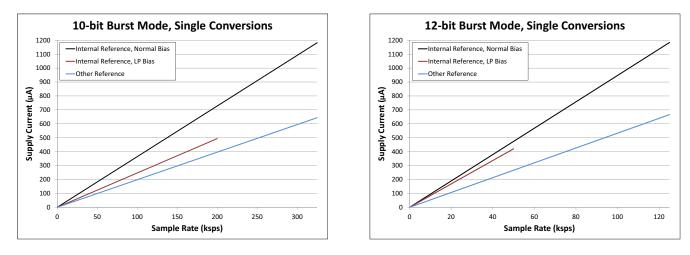

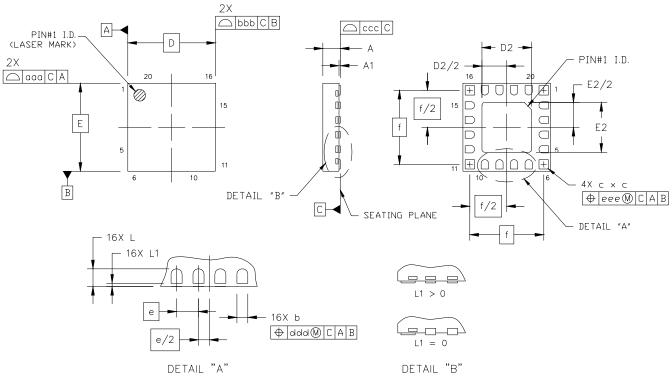

### 1.2.2. ADC Supply Current

Figure 1.3. Typical ADC and Internal Reference Power Consumption in Burst Mode

Figure 1.4. Typical ADC Power Consumption in Normal (Always-On) Mode

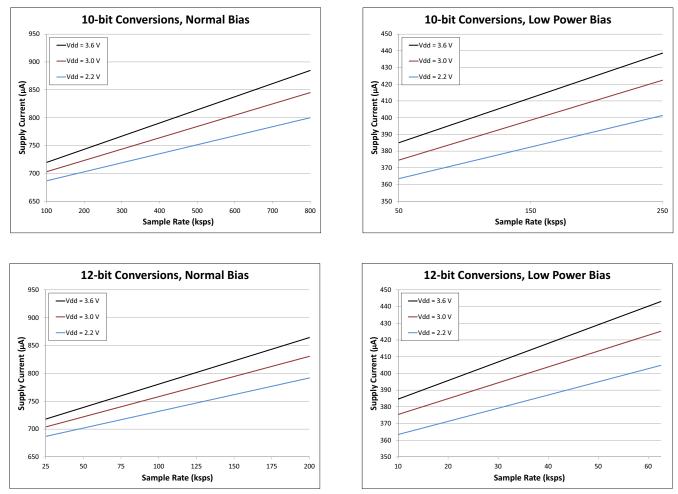

# 6. QFN-20 Package Specifications

Figure 6.1. QFN-20 Package Drawing

| Symbol | Millimeters |      |      |  |  |

|--------|-------------|------|------|--|--|

| ĺ      | Min         | Nom  | Max  |  |  |

| А      | 0.70        | 0.75 | 0.80 |  |  |

| A1     | 0.00        | 0.02 | 0.05 |  |  |

| b      | 0.20        | 0.25 | 0.30 |  |  |

| С      | 0.25        | 0.30 | 0.35 |  |  |

| D      | 3.00 BSC    |      |      |  |  |

| D2     | 1.6         | 1.8  |      |  |  |

| е      | 0.50 BSC    |      |      |  |  |

| Е      | 3.00 BSC    |      |      |  |  |

| E2     | 1.6         | 1.70 | 1.8  |  |  |

#### Table 6.1. QFN-20 Package Dimensions

| Max<br>0.5 |

|------------|

|            |

| 0.5        |

|            |

| 0.10       |

| 0.05       |

| 0.05       |

| 0.08       |

| 0.10       |

| 0.10       |

| -          |

Notes:

1. All dimensions are shown in millimeters unless otherwise noted.

**2.** Dimensioning and tolerancing per ANSI Y14.5M-1994.

needed, it is recommended that AD12SM be set to 1 and ADTK to 0x3F, and that the ADC be placed in always-on mode (ADEN = 1). For sample rates under 180 ksps, or when accumulating multiple samples, AD12SM should normally be cleared to 0, and ADTK should be configured to provide the appropriate settling time for the subsequent conversions.

### 14.5. Power Considerations

The ADC has several power-saving features which can help the user optimize power consumption according to the needs of the application. The most efficient way to use the ADC for slower sample rates is by using burst mode. Burst mode dynamically controls power to the ADC and (if used) the internal voltage reference. By completely powering off these circuits when the ADC is not tracking or converting, the average supply current required for lower sampling rates is reduced significantly.

The ADC also provides low power options that allow reduction in operating current when operating at low SAR clock frequencies or with longer tracking times. The internal common-mode buffer can be configured for low power mode by setting the ADLPM bit in ADCOPWR to 1. Two other fields in the ADCOPWR register (ADBIAS and ADMXLP) may be used together to adjust the power consumed by the ADC and its multiplexer and reference buffers, respectively. In general, these options are used together, when operating with a SAR conversion clock frequency of 4 MHz.

| Required<br>Throughput | Reference Source | Mode Configuration                     | SAR Clock Speed         | Other Register Field<br>Settings             |

|------------------------|------------------|----------------------------------------|-------------------------|----------------------------------------------|

| 325-800 ksps           | Any              | Always-On<br>(ADEN = 1<br>ADBMEN = 0)  | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x40<br>ADC0TK = N/A<br>ADRPT = 0  |

| 0-325 ksps             | External         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1) | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x44<br>ADC0TK = 0x3A<br>ADRPT = 0 |

| 250-325 ksps           | Internal         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1) | 12.25 MHz<br>(ADSC = 1) | ADC0PWR = 0x44<br>ADC0TK = 0x3A<br>ADRPT = 0 |

| 200-250 ksps           | Internal         | Always-On<br>(ADEN = 1<br>ADBMEN = 0)  | 4.08 MHz<br>(ADSC = 5)  | ADC0PWR = 0xF0<br>ADC0TK = N/A<br>ADRPT = 0  |

| 0-200 ksps             | Internal         | Burst Mode<br>(ADEN = 0<br>ADBMEN = 1) | 4.08 MHz<br>(ADSC = 5)  | ADC0PWR = 0xF4<br>ADC0TK = 0x34<br>ADRPT = 0 |

Table 14.2. ADC0 Optimal Power Configuration (8- and 10-bit Mode)

Notes:

1. For always-on configuration, ADSC settings assume SYSCLK is the internal 24.5 MHz high-frequency oscillator. Adjust ADSC as needed if using a different source for SYSCLK.

2. ADRPT reflects the minimum setting for this bit field. When using the ADC in Burst Mode, up to 64 samples may be auto-accumulated per conversion start by adjusting ADRPT.

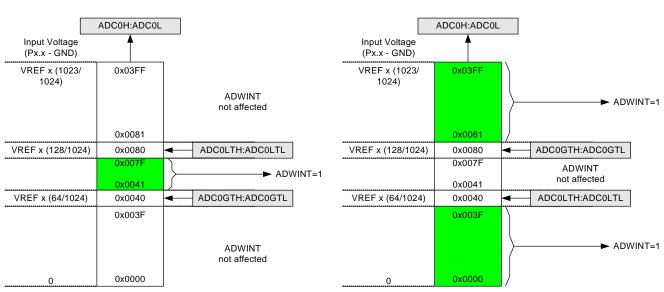

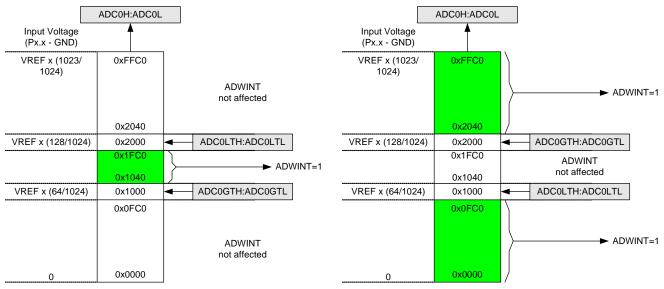

Figure 14.6. ADC Window Compare Example: Right-Justified Single-Ended Data

Figure 14.7. ADC Window Compare Example: Left-Justified Single-Ended Data

### **17.2.** Functional Description

The comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the port pins: a synchronous "latched" output (CPn), or an asynchronous "raw" output (CPnA). The asynchronous CPnA signal is available even when the system clock is not active. This allows the comparator to operate and generate an output with the device in STOP mode.

When disabled, the comparator output (if assigned to a port I/O pin via the crossbar) defaults to the logic low state, and the power supply to the comparator is turned off.

The comparator response time may be configured in software via the CPTnMD register. Selecting a longer response time reduces the comparator supply current.

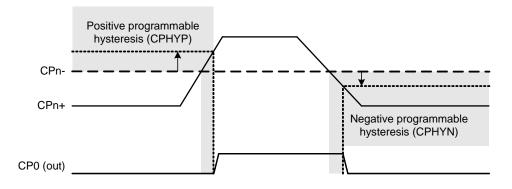

#### Figure 17.2. Comparator Hysteresis Plot

The comparator hysteresis is software-programmable via its Comparator Control register CPTnCN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The comparator hysteresis is programmable using the CPHYN and CPHYP fields in the Comparator Control Register CPTnCN. The amount of negative hysteresis voltage is determined by the settings of the CPHYN bits. As shown in Figure 17.2, settings of 20, 10, or 5 mV (nominal) of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. The CPFIF flag is set to logic 1 upon a comparator falling-edge occurrence, and the CPRIF flag is set to logic 1 upon the comparator rising-edge occurrence. Once set, these bits remain set until cleared by software. The comparator rising-edge interrupt mask is enabled by setting CPRIE to a logic 1. The comparator falling-edge interrupt mask is enabled by setting CPFIE to a logic 1.

The output state of the comparator can be obtained at any time by reading the CPOUT bit. The comparator is enabled by setting the CPEN bit to logic 1, and is disabled by clearing this bit to logic 0.

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed, before enabling comparator interrupts.

## Register 18.2. CRC0IN: CRC0 Data Input

| Bit     | 7                 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------------|-----------------|---|---|---|---|---|---|--|--|

| Name    | CRC0IN            |                 |   |   |   |   |   |   |  |  |

| Туре    | RW                |                 |   |   |   |   |   |   |  |  |

| Reset   | 0                 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

| SFR Add | SFR Address: 0xDD |                 |   |   |   |   |   |   |  |  |

## Table 18.3. CRC0IN Register Bit Descriptions

| Bit | Name   | Function                                                                                                                    |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0IN | CRC Data Input.                                                                                                             |

|     |        | Each write to CRCIN results in the written data being computed into the existing CRC result according to the CRC algorithm. |

## Register 18.3. CRC0DAT: CRC0 Data Output

| '               | 6 | 5   | 4     | 3 | 2 | 1 | 0 |

|-----------------|---|-----|-------|---|---|---|---|

| CRC0DAT         |   |     |       |   |   |   |   |

| RW              |   |     |       |   |   |   |   |

| 0 0 0 0 0 0 0 0 |   |     |       |   |   |   |   |

|                 | 0 | 0 0 | 0 0 0 |   |   |   |   |

## Table 18.4. CRC0DAT Register Bit Descriptions

| Bit | Name                                                                                                                                                                                                                                 | Function                                                                                                                            |  |  |  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:0 | CRC0DAT                                                                                                                                                                                                                              | CRC Data Output.                                                                                                                    |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                                                      | Each read or write performed on CRC0DAT targets the CRC result bits pointed to by the CRC0 Result Pointer (CRC0PNT bits in CRC0CN). |  |  |  |  |  |  |  |

|     | Note:         CRC0DAT may not be valid for one cycle after setting the CRC0INIT bit in the CRC0CN register to 1. Any time CRC0INIT is written to 1 by firmware, at least one instruction should be performed before reading CRC0DAT. |                                                                                                                                     |  |  |  |  |  |  |  |

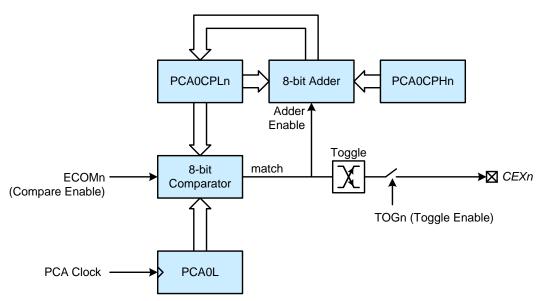

#### 20.3.5. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 20.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 20.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, n is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

Figure 20.5. PCA Frequency Output Mode

## Register 20.10. PCA0POL: PCA Output Polarity

| Bit     | 7                 | 6 | 5        | 4       | 3       | 2       | 1  | 0  |  |  |

|---------|-------------------|---|----------|---------|---------|---------|----|----|--|--|

| Name    |                   |   | Reserved | CEX2POL | CEX1POL | CEX0POL |    |    |  |  |

| Туре    | R                 |   |          |         |         | RW      | RW | RW |  |  |

| Reset   | 0                 | 0 | 0        | 0       | 0       | 0       | 0  | 0  |  |  |

| SFR Add | SFR Address: 0x96 |   |          |         |         |         |    |    |  |  |

# Table 20.12. PCA0POL Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                                                                                                                      |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved | Must write reset value.                                                                                                                                                                                                                       |

| 2   | CEX2POL  | <ul> <li>CEX2 Output Polarity.</li> <li>Selects the polarity of the CEX2 output channel. When this bit is modified, the change takes effect at the pin immediately.</li> <li>0: Use default polarity.</li> <li>1: Invert polarity.</li> </ul> |

| 1   | CEX1POL  | <ul> <li>CEX1 Output Polarity.</li> <li>Selects the polarity of the CEX1 output channel. When this bit is modified, the change takes effect at the pin immediately.</li> <li>0: Use default polarity.</li> <li>1: Invert polarity.</li> </ul> |

| 0   | CEX0POL  | <ul> <li>CEX0 Output Polarity.</li> <li>Selects the polarity of the CEX0 output channel. When this bit is modified, the change takes effect at the pin immediately.</li> <li>0: Use default polarity.</li> <li>1: Invert polarity.</li> </ul> |

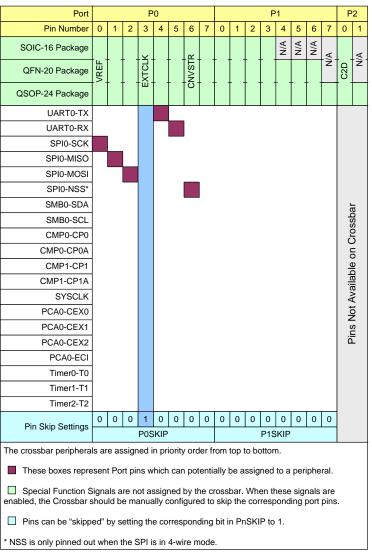

Registers XBR0, XBR1 and XBR2 are used to assign the digital I/O resources to the physical I/O port pins. Note that when the SMBus is selected, the crossbar assigns both pins associated with the SMBus (SDA and SCL); when UART0 is selected, the crossbar assigns both pins associated with UART0 (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART0 TX is always assigned to P0.4; UART0 RX is always assigned to P0.5. Standard port I/Os appear contiguously after the prioritized functions have been assigned.

Figure 21.3 shows an example of the resulting pin assignments of the device with UART0 and SPI0 enabled and the EXTCLK (P0.3) pin skipped (P0SKIP = 0x08). UART0 is the highest priority and it will be assigned first. The UART0 pins can only appear on P0.4 and P0.5, so that is where it is assigned. The next-highest enabled peripheral is SPI0. P0.0, P0.1 and P0.2 are free, so SPI0 takes these three pins. The fourth pin, NSS, is routed to P0.6 because P0.3 is skipped and P0.4 and P0.5 are already occupied by the UART. The other pins on the device are available for use as general-purpose digital I/O or analog functions.

Figure 21.3. Crossbar Priority Decoder Example

## Register 21.4. PRTDRV: Port Drive Strength

| Bit     | 7                 | 6 | 5        | 4     | 3     | 2     | 1  | 0  |  |  |

|---------|-------------------|---|----------|-------|-------|-------|----|----|--|--|

| Name    |                   |   | Reserved | P2DRV | P1DRV | P0DRV |    |    |  |  |

| Туре    |                   | R |          |       |       |       | RW | RW |  |  |

| Reset   | 0                 | 0 | 0        | 0     | 0     | 1     | 1  | 1  |  |  |

| SFR Add | SFR Address: 0xF6 |   |          |       |       |       |    |    |  |  |

# Table 21.7. PRTDRV Register Bit Descriptions

| Bit | Name     | Function                                                                                                                                      |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved | Must write reset value.                                                                                                                       |

| 2   | P2DRV    | <ul><li>Port 2 Drive Strength.</li><li>0: All pins on P2 use low drive strength.</li><li>1: All pins on P2 use high drive strength.</li></ul> |

| 1   | P1DRV    | Port 1 Drive Strength.0: All pins on P1 use low drive strength.1: All pins on P1 use high drive strength.                                     |

| 0   | PODRV    | Port 0 Drive Strength.0: All pins on P0 use low drive strength.1: All pins on P0 use high drive strength.                                     |

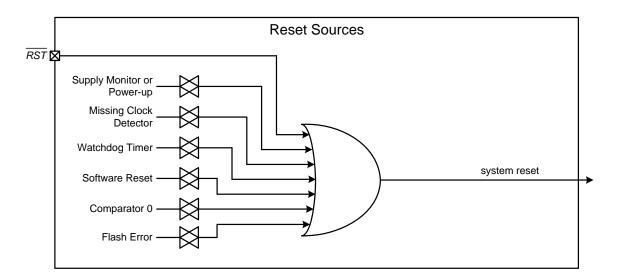

# 22. Reset Sources and Supply Monitor

Reset circuitry allows the controller to be easily placed in a predefined default condition. Upon entering this reset state, the following events occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External port pins are placed in a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain, low-drive mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the RST pin is driven low until the device exits the reset state. Note that during a power-on event, there may be a short delay before the POR circuitry fires and the RST pin is driven low. During that time, the RST pin will be weakly pulled to the  $V_{DD}$  supply pin.

On exit from the reset state, the program counter (PC) is reset, the Watchdog Timer is enabled and the system clock defaults to the internal oscillator. Program execution begins at location 0x0000.

Figure 22.1. Reset Sources

| Hardware Slave Address<br>SLV | Slave Address Mask<br>SLVM | GC bit | Slave Addresses Recognized by Hardware |

|-------------------------------|----------------------------|--------|----------------------------------------|

| 0x34                          | 0x7E                       | 1      | 0x34, 0x35, 0x00 (General Call)        |

| 0x70                          | 0x73                       | 0      | 0x70, 0x74, 0x78, 0x7C                 |

Table 24.4. Hardware Address Recognition Examples (EHACK = 1)

### 24.4.6. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

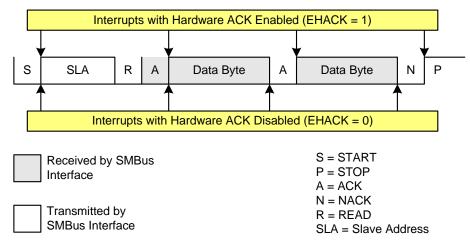

#### 24.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 24.6 shows a typical master read sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 24.6. Typical Master Read Sequence

## Register 24.5. SMB0ADM: SMBus0 Slave Address Mask

| Bit      | 7                 | 6 | 5 | 4    | 3 | 2 | 1  | 0     |

|----------|-------------------|---|---|------|---|---|----|-------|

| Name     |                   |   |   | SLVM |   |   |    | EHACK |

| Туре     | RW                |   |   |      |   |   | RW |       |

| Reset    | 1                 | 1 | 1 | 1    | 1 | 1 | 1  | 0     |

| SFR Addr | SFR Address: 0xD6 |   |   |      |   |   |    |       |

## Table 24.11. SMB0ADM Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                                                                 |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM  | SMBus0 Slave Address Mask.                                                                                                                                                                                                                                               |

|     |       | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM enables comparisons with the corresponding bit in SLV. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK | Hardware Acknowledge Enable.                                                                                                                                                                                                                                             |

|     |       | Enables hardware acknowledgement of slave address and received data bytes.<br>0: Firmware must manually acknowledge all incoming address and data bytes.<br>1: Automatic slave address recognition and hardware acknowledge is enabled.                                  |

## Table 25.10. TMR2CN Register Bit Descriptions

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | T2XCLK | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |        | <ul> <li>This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.</li> <li>0: Timer 2 clock is the system clock divided by 12.</li> <li>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK).</li> </ul> |

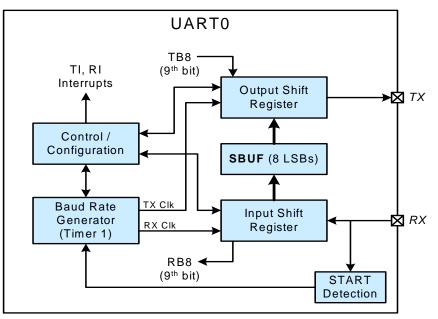

# 26. Universal Asynchronous Receiver/Transmitter (UART0)

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "26.1. Enhanced Baud Rate Generation" on page 289). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the transmit register. Reads of SBUF0 always access the buffered receive register; it is not possible to read data from the transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI is set in SCON0), or a data byte has been received (RI is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 26.1. UART0 Block Diagram

### 26.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 26.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

### 29.2. C2 Interface Registers

The following describes the C2 registers necessary to perform flash programming through the C2 interface. All C2 registers are accessed through the C2 interface, and are not available in the SFR map for firmware access.

#### Register 29.1. C2ADD: C2 Address

| Bit       | 7                                         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|-------------------------------------------|---|---|---|---|---|---|---|

| Name      | C2ADD                                     |   |   |   |   |   |   |   |

| Туре      | RW                                        |   |   |   |   |   |   |   |

| Reset     | 0                                         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| This regi | This register is part of the C2 protocol. |   |   |   |   |   |   |   |

### Table 29.1. C2ADD Register Bit Descriptions

| Bit | Name  | Function                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | C2ADD | C2 Address.                                                                                                                                                                                                                    |

|     |       | The C2ADD register is accessed via the C2 interface. The value written to C2ADD selects the target data register for C2 Data Read and Data Write commands.<br>0x00: C2DEVID<br>0x01: C2REVID<br>0x02: C2FPCTL<br>0xB4: C2FPDAT |

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com