# E·XFL

## Intel - 5SGXEA9N3F45C4N Datasheet

Welcome to <u>E-XFL.COM</u>

## Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Product Status                 | Obsolete                                                   |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 317000                                                     |

| Number of Logic Elements/Cells | 840000                                                     |

| Total RAM Bits                 | 53248000                                                   |

| Number of I/O                  | 840                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.82V ~ 0.88V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1932-BBGA, FCBGA                                           |

| Supplier Device Package        | 1932-FBGA, FC (45x45)                                      |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5sgxea9n3f45c4n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Page 2 |

|--------|

|--------|

| Transceiver Speed        |    |         |      | Core Sp | eed Grade | е        |       |      |

|--------------------------|----|---------|------|---------|-----------|----------|-------|------|

| Grade                    | C1 | C2, C2L | . C3 | C4      | 12, 12    | L 13, 13 | L 13Y | Y 14 |

| 3<br>GX channel—8.5 Gbps |    | Yes     | Yes  | Yes     | _         | Yes      | Yés   | Yes  |

#### Table 1. Stratix V GX and GS Commercial and Industrial Speed Grade Offer (And G) (Part 2 of 2)

Notes toTable 1

(1) C = Commercial temperature gradelindustrial temperature grade.

(2) Lower number refers to faster speed grade.

(3) C2L, I2L, and I3L speed grades are for low-power devices.

(4) I3YY speed grades carhieove up to 10.3125 Gbps.

Table 2 lists the industrial and commercial speed grades for the Stratix V GT devices. Table 2. Stratix V GT Commercial and Industrial Speed Grade Offering

| Transceiver Speed Grade                            | Core Speed Grade |     |     |     |  |  |  |  |  |

|----------------------------------------------------|------------------|-----|-----|-----|--|--|--|--|--|

| Transceiver Speed Grade                            | C1               | C2  | 12  | 13  |  |  |  |  |  |

| 2<br>GX channel—12.5 Gbps<br>GT channel—28.05 Gbps | Yes              | Yes | _   | _   |  |  |  |  |  |

| 3<br>GX channel—12.5 Gbps<br>GT channel—25.78 Gbps | Yes              | Yes | Yes | Yes |  |  |  |  |  |

Notes toTable 2

(1) C = Commercial temperature gradelndustrial temperature grade.

(2) Lower number refers to faster speed grade.

## Absolute Maximum Ratings

Absolute maximum ratings define the maxi mum operating conditions for Stratix V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

c Conditions other than those listed in Table 3 may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

| Symbol              | Description                                                      | Minimum  | Maximu | m Un | it |

|---------------------|------------------------------------------------------------------|----------|--------|------|----|

| V <sub>CC</sub>     | Power supply for core voltage and periphery circuitry            | -0.      | 51.    | 85   | V  |

| V <sub>CCPT</sub>   | Power supply for programmable power technology                   | -0.      | 51.    | 8    | V  |

| V <sub>CCPGM</sub>  | Power supply for configuration pins                              | -0.5     | 3.9    | ١    | 1  |

| V <sub>CC_AUX</sub> | Auxiliary supply for the programmable power technology           | -0       | 5 3    | .4   | V  |

| V <sub>CCBAT</sub>  | Battery back-up power supply for design security volatile key re | gister – | 0.5    | 3.9  | 1  |

| V <sub>CCPD</sub>   | I/O pre-driver power supply                                      | -0.5     | 3.9    | V    |    |

| V <sub>CCIO</sub>   | I/O power supply                                                 | -0.5     | 3.9    | V    | 1  |

Table 3. Absolute Maximum Ratings for Stratix V Devices (Part 1 of 2)

| Symbol            | Description            | Condition   | Mith     | Тур | Max <sup>(4)</sup> | Unit |

|-------------------|------------------------|-------------|----------|-----|--------------------|------|

| t <sub>RAMP</sub> | Power supply ramp time | Standard PO | R 200 µs | _   | 100 ms             | s –  |

|                   |                        | Fast POR    | 200 µs   |     | 4 ms               |      |

#### Table 6. Recommended Operating Conditions for Stratix V Devices (Part 2 of 2)

Notes toTable 6

(1) V<sub>CCPD</sub>must be 2.5 V when<sub>C</sub>y<sub>IO</sub>is 2.5, 1.8, 1.5, 1.35, 1.25 or 1.2 V<sub>C</sub>y<sub>D</sub>must be 3.0 V when<sub>C</sub>y<sub>IO</sub>is 3.0 V.

(2) If you do not use the design secufieig/ture in Stratix V devices, connecte/V to a 1.2- to 3.0-V power supply. Stratix V power-on-reset (POR) circuitry monitors V<sub>CBAT</sub> Stratix V devices will not exit POR<sub>Cife/A</sub> stays at logic low.

(3) C2L and I2L can also be run at 0.90 V for legacy bthatdsere designed forettC2 and I2 speed grades.

(4) The power supply value describes the but day the DC (static) power supply takes and does not include the dynamic ablae requirements. Refer to the PDN food the additional budget for et day namic tolerance requirements.

Table 7 lists the transceiver power supply recommended operating conditions for Stratix V GX, GS, and GT devices.

Table 7. Recommended Transceiver Power Supply Operating Conditions for Stratix V GX, GS, and GT Devices (Part 1 of 2)

| Symbol                | Description                                                                                      | Devices                       | Minimú <del>f</del> h | Typical | Maximun <sup>(4)</sup> | Unit |  |

|-----------------------|--------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|---------|------------------------|------|--|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (I                                                          | eft                           | 2.85                  | 3.0     | 3.15                   | V    |  |

| (1), (3)              | side)                                                                                            |                               | 2.375                 | 2.5     | 2.625                  | v    |  |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (r                                                          | ght <sub>ex cs</sub>          | 2.85                  | 3.0     | 3.15                   | V    |  |

| (1), (3)              | side)                                                                                            | GA, GS                        | 2.375                 | 2.5     | 2.625                  | v    |  |

| V <sub>CCA_GTBR</sub> | Transceiver channel PLL power supply (r side)                                                    | GI                            | 2.85                  | 3.0     | 3.15                   | V    |  |

|                       | Transceiver hard IP power supply (left sid<br>C1, C2, I2, and I3YY speed grades)                 | <sup>le:</sup> GX, GS, GT     | 0.87                  | 0.9     | 0.93                   | Ŋ    |  |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left sid<br>C2L, C3, C4, I2L, I3, I3L, and I4 speed<br>grades) | GX, GS, G1                    |                       | 0.85    | 0.88                   |      |  |

|                       | Transceiver hard IP power supply (right s<br>C1, C2, I2, and I3YY speed grades)                  | <sup>ide:</sup><br>GX, GS, GT | 0.87                  | 0.9     | 0.93                   | Y    |  |

| V <sub>CCHIP_R</sub>  | Transceiver hard IP power supply (right s C2L, C3, C4, I2L, I3, I3L, and I4 speed grades)        | de;<br>GX, GS, G1             | 0.82                  | 0.85    | 0.88                   |      |  |

|                       | Transceiver PCS powearpply (left side;<br>C1, C2, I2, and I3YY speed grades)                     | GX, GS, GT                    | 0.87                  | 0.9     | 0.93                   | Y    |  |

| V <sub>CCHSSI_L</sub> | Transceiver PCS powserpply (left side;<br>C2L, C3, C4, I2L, I3, I3L, and I4 speed<br>grades)     | GX, GS, GT                    | 0.82                  | 0.85    | 0.88                   |      |  |

|                       | Transceiver PCS powseurpply (right side;<br>C1, C2, I2, and I3YY speed grades)                   | GX, GS, GT                    | 0.87                  | 0.9     | 0.93                   | Ŋ    |  |

| V <sub>CCHSSI_R</sub> | Transceiver PCS powserpply (right side;<br>C2L, C3, C4, I2L, I3, I3L, and I4 speed<br>grades)    | GX, GS, GT                    | 0.82                  | 0.85    | 0.88                   |      |  |

|                       |                                                                                                  |                               | 0.82                  | 0.85    | 0.88                   |      |  |

| V <sub>CCR GXBL</sub> | Possiver analog newer supply (left side)                                                         | GX, GS                        | 0.87                  | 0.90    | 0.93                   | v    |  |

| (2)                   | Receiver analog power supply (left side)                                                         | GA, G3                        | 0.97                  | 1.0     | 1.03                   | v    |  |

| V <sub>CCHIP_L</sub>  |                                                                                                  |                               | 1.03                  | 1.05    | 1.07                   |      |  |

| Symbol                       | Description                                                  | Devices                   | Minimú <del>f</del> h | Typical | Maximun <sup>(4)</sup> | Unit |

|------------------------------|--------------------------------------------------------------|---------------------------|-----------------------|---------|------------------------|------|

|                              |                                                              |                           | 0.82                  | 0.85    | 0.88                   |      |

| V <sub>CCR_GXBR</sub>        | Passiver analog newer supply (right side                     | ) GX, GS                  | 0.87                  | 0.90    | 0.93                   | V    |

| (2)                          | Receiver analog power supply (right side                     | ) GA, GC                  | 0.97                  | 1.0     | 1.03                   | v    |

|                              |                                                              |                           | 1.03                  | 1.05    | 1.07                   |      |

| V <sub>CCR_GTBR</sub>        | Receiver analog power supply for GT channels (right side)    | GT                        | 1.02                  | 1.05    | 1.08                   | V    |

|                              |                                                              |                           | 0.82                  | 0.85    | 0.88                   |      |

| V <sub>CCT_GXBL</sub><br>(2) | Transmitter analog power supply (left side                   |                           | 0.87                  | 0.90    | 0.93                   | v    |

|                              | Transmitter analog power supply (left sid                    | e) GX, GS                 | 0.97                  | 1.0     | 1.03                   | v    |

|                              |                                                              |                           | 1.03                  | 1.05    | 1.07                   |      |

|                              |                                                              |                           | 0.82                  | 0.85    | 0.88                   |      |

| V <sub>CCT_GXBR</sub>        | Tanana ittaa aa da a aa aa aa aa aa aa aa a                  | de) GX, G                 | 0.87                  | 0.90    | 0.93                   | V    |

| (2)                          | Transmitter analog power supply (right si                    | ue) GA, GC                | 0.97                  | 1.0     | 1.03                   | v    |

|                              |                                                              |                           | 1.03                  | 1.05    | 1.07                   |      |

| V <sub>CCT_GTBR</sub>        | Transmitter analog power supply for GT channels (right side) | GT                        | 1.02                  | 1.05    | 1.08                   | V    |

| $V_{CCL\_GTBR}$              | Transmitter clock network persupply                          | GT                        | 1.02                  | 1.05    | 1.08                   | V    |

| V <sub>CCH_GXBL</sub>        | Transmitter output buffer power supply (le side)             | <sup>eft</sup> GX, GS, GT | 1.425                 | 1.5     | 1.575                  |      |

| V <sub>CCH_GXBR</sub>        | Transmitter output buffer power supply (right side)          | GX, GS, GT                | 1.425                 | 1.5     | 1.575                  |      |

| Table 7. Recommended Transceiver Power Supply Operating Conditions for Stratix V GX, GS, and GT | Devices |

|-------------------------------------------------------------------------------------------------|---------|

| (Part 2 of 2)                                                                                   |         |

Notes toTable 7.

(1) This supply must be connected to 3.0tl/eifCMU PLL, receiver CDR, or both, antegoured at a base data rate > 6.5 Gbpstol@p5 Gbps, you can connect this supply either 3.0 V or 2.5 V.

(2) Refer to Table & select the correct powseupply level for your design.

(3) When using ATX PLLs, the supply must be 3.0 V.

(4) This value describes the budget for the static) power supply tolerance and does include the dynaic tolerance requiments. Refer to the PDN tool for the additial budget for the dynamic tolerance requirements.

| I/O                    | ,    | V <sub>ccid</sub> (V) |      | V6IF( | <sub>(DC</sub> (V)        |                                              | V <sub>x(AC)</sub> (V)    | )                               |                           | V <sub>ČM(DC</sub> (V     | <b>)</b>                  | YGIF( | <sub>AC</sub> (V)           |

|------------------------|------|-----------------------|------|-------|---------------------------|----------------------------------------------|---------------------------|---------------------------------|---------------------------|---------------------------|---------------------------|-------|-----------------------------|

| Standard               | Min  | Тур                   | Max  | Min   | Мах                       | Min                                          | Тур                       | Max                             | Min                       | Тур                       | o Ma                      | x M   | in Ma                       |

| HSTL-12<br>Class I, II | 1.14 | 1.2                   | 1.26 | 0.16  | V <sub>CCIO</sub><br>+0.3 | —                                            | 0.5*<br>V <sub>CCIO</sub> | —                               | 0.4*<br>V <sub>CCIO</sub> | 0.5*<br>V <sub>CCIO</sub> | 0.6*<br>V <sub>CCIO</sub> | 0.3   | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14 | 1.2                   | 1.3  | 0.2   | 6 0.2                     | 6 <sup>0.5*V<sub>CCIO</sub><br/>- 0.12</sup> | 0.5*<br>V <sub>CCIO</sub> | 0.5*V <sub>CCIO</sub><br>+ 0.12 | 0.4*<br>V <sub>CCIO</sub> | 0.5*<br>V <sub>CCIO</sub> | 0.6*<br>V <sub>CCIO</sub> | 0.44  | 0.44                        |

## Table 21. Differential HSTL and HSUL I/O Standards for Stratix V Devices (Part 2 of 2)

## Table 22. Differential I/O Standard Specifications for Stratix V Devlčes

| I/O                                   | V <sub>C</sub> | <sub>CIO</sub> (V) | (10)  |     | V <sub>ID</sub> (mV) <sup>(8)</sup> |      |       | V <sub>ICM(DC</sub> (V)                 |       | Y      | <sub>DD</sub> (V) <sup>(</sup> | 6)   | V     | <sub>осм</sub> (V) | (6)    |        |

|---------------------------------------|----------------|--------------------|-------|-----|-------------------------------------|------|-------|-----------------------------------------|-------|--------|--------------------------------|------|-------|--------------------|--------|--------|

| Standard                              | Min            | Тур                | Max   | Min | Condition                           | n Ma | k Mii | n Conditio                              | on Ma | ıx M   | in T                           | yp I | Max N | 1in T              | ур     | Max    |

| PCML                                  | Tra            | nsmitt             |       |     | •                                   |      |       | ap <b>ithseof</b> figh-∺<br>lock l∕Opin | •     |        |                                |      |       |                    | andard | l. For |

| 2.5 V                                 | 2.375          | 2.5                | 2.625 | 100 | V <sub>CM</sub> =                   |      | 0.05  | D <sub>MAX</sub> d<br>700 Mbps          | 1.8   | 0.247  |                                | 0.6  | 1.12  | 5 1.2              | 5 1.3  | 375    |

| LVDS <sup>(1)</sup>                   | 2.575          | 2.5                | 2.020 | 100 | 1.25 V                              | _    | 1.05  | D <sub>MAX</sub> ><br>700 Mbps          | 1.55  | 0.247  |                                | 0.6  | 1.12  | 5 1.2              | 5 1.3  | 375    |

| BLVD\$5)                              | 2.375          | 2.5                | 2.625 | 100 |                                     | _    |       | —                                       | _     | _      |                                |      |       |                    |        | -      |

| RSDS<br>(HIO) <sup>(2)</sup>          | 2.375          | 2.5                | 2.625 | 100 | V <sub>CM</sub> =<br>1.25 V         |      | 0.3   | —                                       | 1.4   | 0.1    | 0.2                            | 0.6  | 0.5   | 1.2                | 1.     | .4     |

| Mini-<br>LVDS<br>(HIO) <sup>(3)</sup> | 2.375          | 2.5                | 2.625 | 200 |                                     | 600  | ) 0.4 | 4 —                                     | 1.32  | 25 0.2 | 25 -                           | _ (  | 0.6   | 1 1                | .2     | 1.4    |

| LVPEC <sup>4</sup>                    |                |                    |       | 300 | _                                   | _    | 0.6   | D <sub>MAX</sub> d<br>700 Mbps          | 1.8   | _      |                                | _    | _     | _                  | _      |        |

| ), (9)                                |                | —                  | _     | 300 |                                     |      | 1     | D <sub>MAX</sub> ><br>700 Mbps          | 1.6   |        | _                              | _    |       | _                  | _      |        |

Notes toTable 22

(1) For optimized LVDS receiver **fore** mance, the receiver voltage utrange must be between 1/.00 1.6 V for data rates also 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

(2) For optimized RSDS receiver perforce a the receiver voltage input rangest be between 0.25 V to 1.45 V.

(3) For optimized Mini-LVDS receiver optimized, the receiver voltage input congust be between 0.3 V to 1.425 V.

(4) For optimized LVPECL receiver formance, the receiver voltaiggeut range must be between 0\850 1.75 V for data rate/ave 700 Mbps and 0.45 V to 1.95 V for data rate below 700 Mbps.

(5) There are no fixed<sub>CM</sub>, V<sub>OD</sub> and V<sub>CM</sub>specifications for BLVDS. The system topology.

(6) RL range: 90dRL d110 : .

(7) The 1.4-V and 1.5-V PCML transceivest and a specifications are described in Transceiver Performance applications" on page 18

(8) The minimum VID value is applicativer the entire common mode range, VCM.

(9) LVPECL is only supported on dedicated clock input pins.

(10) Differential inputs are powered by VCCPD which requires 2.5 V.

# **Power Consumption**

Altera offers two ways to estimate power consumption for a design—the Excel-based Early Power Estimator and the Quartus<sup>®</sup> II PowerPlay Power Analyzer feature.

# Switching Characteristics

This section provides performance characteristics of the Stratix V core and periphery blocks.

These characteristics can be desigated as Preliminary or Final.

Preliminary characteristics are created using simulation results, process data, and other known parameters. The title of these tables show the designation as "Preliminary."

Final numbers are based on actual silicon characterization and testing. The numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions. There are no designations on finalized tables.

# Transceiver Performance Specifications

This section describes transceiver performance specifications.

Table 23 lists the Stratix V GX and GStransceiver specifications.

| Symbol/                                                        | Conditions                                                        | Tra   | nsceive<br>Grade                                                                  | er Speed<br>e 1 | Trai | nsceive<br>Grad | er Speed<br>e 2 | Trar | nsceive<br>Grade | er Speed<br>e 3 | Unit |  |

|----------------------------------------------------------------|-------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------|-----------------|------|-----------------|-----------------|------|------------------|-----------------|------|--|

| Description                                                    |                                                                   | Min   | Тур                                                                               | Max             | Min  | Тур             | Max             | Mir  | n Ty             | p Max           |      |  |

| Reference Clock                                                |                                                                   |       |                                                                                   |                 |      |                 |                 |      |                  |                 |      |  |

| Supported I/O<br>Standards                                     | Dedicated<br>reference<br>clock pin                               | 1.2-\ | 1.2-V PCML, 1.4-V PCML, 1.5-V PCML,/2P3GML, Differential LVPECL, LVDS, an<br>HCSL |                 |      |                 |                 |      |                  |                 |      |  |

| Stanuarus                                                      | RX reference<br>clock pin                                         | •     | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS                              |                 |      |                 |                 |      |                  |                 |      |  |

| Input Reference<br>Clock Frequency<br>(CMU PLL <sup>(β)</sup>  | _                                                                 | 40    |                                                                                   | 710             | 40   | _               | 710             | 40   |                  | 710             | MHz  |  |

| Input Reference<br>Clock Frequency<br>(ATX PLL) <sup>(3)</sup> |                                                                   | 100   | _                                                                                 | 710             | 100  |                 | 710             | 100  | _                | 710             | MHz  |  |

| Rise time                                                      | Measure at<br>±60 mV of<br>differential<br>signal <sup>(26)</sup> | _     | _                                                                                 | 400             |      |                 | 400             |      | _                | 400             | 05   |  |

| Fall time                                                      | Measure at<br>±60 mV of<br>differential<br>signal <sup>(26)</sup> | _     | _                                                                                 | 400             |      |                 | 400             | _    | _                | 400             | ps   |  |

| Duty cycle                                                     | —                                                                 | 45    | —                                                                                 | 55              | 45   |                 | 55              | 45   | _                | - 55            | %    |  |

| Spread-spectrum<br>modulating clock<br>frequency               | PCI Express<br>(PCI&)                                             | 30    |                                                                                   | 33              | 30   | _               | 33              | 30   | _                | 33              | kHz  |  |

| Symbol/                                                  | Conditions                                                          | Tra | nsceive<br>Grade | er Speed<br>e 1 | Trai | nsceive<br>Grade | er Speed<br>e 2 | Trar | nsceiv<br>Grad  | er Speed<br>e 3 | Unit |

|----------------------------------------------------------|---------------------------------------------------------------------|-----|------------------|-----------------|------|------------------|-----------------|------|-----------------|-----------------|------|

| Description                                              |                                                                     | Min | Тур              | Max             | Min  | Тур              | Max             | Mir  | і Ту            | p Max           |      |

|                                                          | 85 : setting                                                        | _   | 85 ±<br>30%      | _               | _    | 85 ±<br>30%      | —               | _    | 85 ±<br>30%     | _               | :    |

| Differential on-                                         | 100:<br>setting                                                     | _   | 100<br>±<br>30%  | _               | _    | 100<br>±<br>30%  | —               | _    | 100<br>±<br>30% | _               | :    |

| chip termination resistors <sup>(21)</sup>               | 120 :<br>setting                                                    | _   | 120<br>±<br>30%  | _               | _    | 120<br>±<br>30%  | —               | _    | 120<br>±<br>30% | _               | :    |

|                                                          | 150-:<br>setting                                                    | -   | 150<br>±<br>30%  | _               | _    | 150<br>±<br>30%  | _               | _    | 150<br>±<br>30% | _               | :    |

|                                                          | V <sub>CCR_GX</sub><br>0.85 V or 0.9<br>V<br>full<br>bandwidth      |     | 600              |                 |      | 600              | _               |      | 600             | _               | mV   |

| V <sub>ICM</sub><br>(AC and DC<br>coupled)               | V <sub>CCR_GX₿</sub> =<br>0.85 V or 0.9<br>V<br>half<br>bandwidth   | _   | 600              | _               | _    | 600              |                 | _    | 600             | _               | mV   |

|                                                          | V <sub>CCR_GX</sub> €<br>1.0 V/1.05 V<br>full<br>bandwidth          | _   | 700              | _               | _    | 700              | —               | _    | 700             | _               | mV   |

|                                                          | V <sub>CCR_GX</sub> r<br>1.0 V<br>half<br>bandwidth                 | _   | 750              | _               | _    | 750              | _               | _    | 750             | _               | mV   |

| t <sub>LTR</sub> <sup>(11)</sup>                         | —                                                                   | Ι   | _                | 10              |      |                  | 10              |      | _               | 10              | μs   |

| t <sub>LTD</sub> <sup>(12)</sup>                         | —                                                                   | 4   | _                | _               | 4    | —                | —               | 4    |                 |                 | μs   |

| t <sub>LTD_manual</sub> <sup>(13)</sup>                  |                                                                     | 4   |                  | _               | 4    | _                | —               | 4    |                 |                 | μs   |

| (14) (14) (14)                                           | —                                                                   | 15  | _                | _               | 15   | —                | —               | 15   |                 | —               | μs   |

| Run Length                                               | —                                                                   | —   | _                | 200             | —    | _                | 200             |      |                 | 200             | UI   |

| Programmable<br>equalization<br>(AC Gain <sup>()0)</sup> | Full<br>bandwidth<br>(6.25 GHz)<br>Half<br>bandwidth<br>(3.125 GHz) |     |                  | 16              | _    | _                | 16              | _    |                 | 16              | dB   |

Table 23. Transceiver Specifications for Stratix V GX and GS DeviceBart 4 of 7)

|                     | Transceiver                             | PMA Width                               | 20                   | 20      | 16     | 16       | 10    | 10    | ) 8          |      | 8    |

|---------------------|-----------------------------------------|-----------------------------------------|----------------------|---------|--------|----------|-------|-------|--------------|------|------|

| Mode <sup>(2)</sup> | Speed Grade                             | PCS/Core Width                          | 40                   | 20      | 32     | 16       | 20    | ) 1   | 0 1          | 6    | 8    |

|                     | 1                                       | C1, C2, C2L, I2, I2<br>core speed grade |                      | 11.4    | 9.76   | 9.12     | 6.5   | 5.8   | 3 5.         | 24   | .72  |

| 2<br>FIFO           | C1, C2, C2L, I2, I2<br>core speed grade | L 12.2                                  | 11.4                 | 9.76    | 9.12   | 6.5      | 5.8   | 3 5.3 | 24           | .72  |      |

|                     | C3, I3, I3L<br>core speed grade         | 9.8                                     | 9.0                  | 7.84    | 7.2    | 5.3      | 4.7   | 4.2   | 4 3.         | 76   |      |

|                     | C1, C2, C2L, I2, I2<br>core speed grade | L 8.5                                   | 8.5                  | 8.5     | 8.5    | 6.5      | 5.8   | 5.2   | 4.           | 72   |      |

|                     | 3                                       | I3YY<br>core speed grade                | 10.3125              | 10.3125 | 7.84   | 7.2      | 5.3   | 8 4.  | 74.          | 24 : | 3.76 |

|                     | 5                                       | C3, I3, I3L<br>core speed grade         | 8.5                  | 8.5     | 7.84   | 7.2      | 5.3   | 4.7   | 4.2          | 4 3. | 76   |

|                     |                                         | C4, I4<br>core speed grade              | 8.5                  | 8.2     | 7.04   | 6.56     | 4.8   | 4.2   | 3.8          | 43   | .44  |

|                     | 1                                       | C1, C2, C2L, I2, I2<br>core speed grade | L 12.2               | 11.4    | 9.76   | 9.12     | 6.1   | 5.7   | <b>7</b> 4.8 | 84   | .56  |

|                     | 2                                       | C1, C2, C2L, I2, I2<br>core speed grade | L 12.2               | 11.4    | 9.76   | 9.12     | 6.1   | 5.7   | <b>7</b> 4.8 | 84   | .56  |

|                     | 2                                       | C3, I3, I3L<br>core speed grade         |                      | 9.0     | 7.92   | 7.2      | 4.9   | 4.5   | 3.9          | 63   | .6   |

| Register            |                                         | C1, C2, C2L, I2, I2<br>core speed grade | L <sub>10.3125</sub> | 10.3125 | 10.312 | 5 10.312 | 25 6. | 1 5   | .7 4         | .88  | 4.56 |

| 3                   | 2                                       | I3YY<br>core speed grade                | 10.3125              | 10.3125 | 7.92   | 7.2      | 4.9   | ) 4.  | 5 3.         | 96   | 3.6  |

|                     | 3                                       | C3, I3, I3L<br>core speed grade         | 8.5                  | 8.5     | 7.92   | 7.2      | 4.9   | 4.5   | 3.9          | 63   | .6   |

|                     |                                         | C4, I4<br>core speed grade              | 8.5                  | 8.2     | 7.04   | 6.56     | 4.4   | 4.1   | 3.5          | 23   | .28  |

Table 25 shows the approximate maximum data rate using the standard PCS.

Table 25. Stratix V Standard PCS Approximate Maximum Date Rate

Notes toTable 25

(1) The maximum data rate is in Gbps.

(2) The Phase Compensation FIFO can be guzzerdi in FIFO mode or register moden er FIFO mode, the pointers are not fixed the latency can vary. In the register mode provincers are fixed to low latency.

(3) The maximum data rateals o constrained by the transiver speed grade. Referitizable for the transcerer speed grade.

Table 26 shows the approximate maximum data rate using the 10G PCS.

| Table 26  | Strativ V/ 100 | C BCS Approvimate | Maximum Data (Pata  |

|-----------|----------------|-------------------|---------------------|

| Table 26. | Stratix V TU   | 5 PUS Approximate | e Maximum Data Rate |

| $M_{\rm ender}$ (2) | Transceiver | PMA Width                               | 64            | 40    | 40    | 40   | 32      | 32    |  |  |  |

|---------------------|-------------|-----------------------------------------|---------------|-------|-------|------|---------|-------|--|--|--|

| Mode <sup>(2)</sup> | Speed Grade | PCS Width                               | 64            | 66/67 | 50    | 40   | 64/66/6 | 7 32  |  |  |  |

|                     | 1           | C1, C2, C2L, I2, I2<br>core speed grade |               | 14.1  | 10.69 | 14.1 | 13.6    | 13.6  |  |  |  |

|                     | 2           | C1, C2, C2L, I2, I2<br>core speed grade | 125           | 12.5  | 10.69 | 12.5 | 12.5    | 12.5  |  |  |  |

|                     | 2           | C3, I3, I3L<br>core speed grade         | 12.5          | 12.5  | 10.69 | 12.5 | 10.88   | 10.88 |  |  |  |

| FIFO or<br>Register |             | C1, C2, C2L, I2, I2<br>core speed grade |               |       |       |      |         |       |  |  |  |

|                     | 3           | C3, I3, I3L<br>core speed grade         | -<br>8.5 Gbps |       |       |      |         |       |  |  |  |

| 3                   |             | C4, I4<br>core speed grade              | e             |       |       |      |         |       |  |  |  |

|                     |             | I3YY<br>core speed grade                | 10.3125 Gbps  |       |       |      |         |       |  |  |  |

Notes toTable 26

(1) The maximum data rate is in Gbps.

(2) The Phase Compensation FIFO can be counting uf IFO mode or register mode. In Fith FO mode, the ptoins are not fixed number of the latency can vary. In the register mode through the latency.

Table 27 shows the  $V_{\text{OD}}$  settings for the GX channel.

| Symbol                                    | \g <sub>D</sub> Setting | V <sub>OD</sub> Value<br>(mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value<br>(mV) |

|-------------------------------------------|-------------------------|-------------------------------|-------------------------|-------------------------------|

|                                           | 0 <sup>(1)</sup>        | 0                             | 32                      | 640                           |

|                                           | 1 <sup>(1)</sup>        | 20                            | 33                      | 660                           |

|                                           | 2 <sup>(1)</sup>        | 40                            | 34                      | 680                           |

|                                           | 3 <sup>(1)</sup>        | 60                            | 35                      | 700                           |

|                                           | 4 <sup>(1)</sup>        | 80                            | 36                      | 720                           |

|                                           | 5 <sup>(1)</sup>        | 100                           | 37                      | 740                           |

|                                           | 6                       | 120                           | 38                      | 760                           |

|                                           | 7                       | 140                           | 39                      | 780                           |

|                                           | 8                       | 160                           | 40                      | 800                           |

|                                           | 9                       | 180                           | 41                      | 820                           |

|                                           | 10                      | 200                           | 42                      | 840                           |

|                                           | 11                      | 220                           | 43                      | 860                           |

|                                           | 12                      | 240                           | 44                      | 880                           |

|                                           | 13                      | 260                           | 45                      | 900                           |

|                                           | 14                      | 280                           | 46                      | 920                           |

| V <sub>OD</sub> differential peak to peak | 15                      | 300                           | 47                      | 940                           |

| typical <sup>(3)</sup>                    | 16                      | 320                           | 48                      | 960                           |

|                                           | 17                      | 340                           | 49                      | 980                           |

|                                           | 18                      | 360                           | 50                      | 1000                          |

|                                           | 19                      | 380                           | 51                      | 1020                          |

|                                           | 20                      | 400                           | 52                      | 1040                          |

|                                           | 21                      | 420                           | 53                      | 1060                          |

|                                           | 22                      | 440                           | 54                      | 1080                          |

|                                           | 23                      | 460                           | 55                      | 1100                          |

|                                           | 24                      | 480                           | 56                      | 1120                          |

|                                           | 25                      | 500                           | 57                      | 1140                          |

|                                           | 26                      | 520                           | 58                      | 1160                          |

|                                           | 27                      | 540                           | 59                      | 1180                          |

|                                           | 28                      | 560                           | 60                      | 1200                          |

|                                           | 29                      | 580                           | 61                      | 1220                          |

|                                           | 30                      | 600                           | 62                      | 1240                          |

|                                           | 31                      | 620                           | 63                      | 1260                          |

Note toTable 27

(1) If TX termination resistance = 100 his VOD setting is illegal.

(2) The tolerance is  $\pm$ -20% for all**D/Settings** except for settings 2 and below.

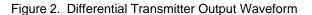

(3) Refer to Figure 2

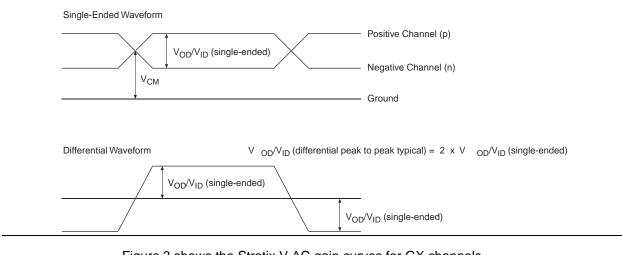

Figure 2 shows the differential transmitter output waveform.

Figure 3 shows the Stratix V AC gain curves for GX channels.

Figure 3. AC Gain Curves for GX Channels (full bandwidth)

1 Stratix V GT devices contain both GX and GT channels. All transceiver specifications for the GX channels not listed in Table 28 are the same as those listed inTable 23.

Table 28 lists the Stratix V GT transceiver specifications.

| Symbol/<br>Description                                         | Conditions                                             |           | Transceive<br>Speed Grad |             |                        | Fransceive<br>peed Grad |              | Unit     |  |

|----------------------------------------------------------------|--------------------------------------------------------|-----------|--------------------------|-------------|------------------------|-------------------------|--------------|----------|--|

| Description                                                    |                                                        | Min       | Тур                      | Max         | Min                    | Тур                     | Max          |          |  |

| Reference Clock                                                |                                                        |           | <u> </u>                 |             |                        |                         | ·            |          |  |

| Supported I/O<br>Standards                                     | Dedicated<br>reference<br>clock pin                    | 1.2-V PCI | ML, 1.4-V F              |             | V PCM5L;V2<br>and HCSL |                         | ferential LV | PECL, L\ |  |

| olandardo                                                      | RX reference<br>clock pin                              |           | 1.4-V PCM                | L, 1.5-V P( | CML, 2%.5PC            | ML, LVPE                | CL, and L\   | /DS      |  |

| Input Reference Clock<br>Frequency (CMU<br>PLL) <sup>(6)</sup> | _                                                      | 40        | _                        | 710         | 40                     | _                       | 710          | MHz      |  |

| Input Reference Clock<br>Frequency (ATX PL(한)                  |                                                        | 100       | —                        | 710         | 100                    | —                       | 710          | MHz      |  |

| Rise time                                                      | 20% to 80%                                             | , —       | —                        | 400         |                        | —                       | 400          | ~~       |  |

| Fall time                                                      | 80% to 20%                                             |           |                          | 400         |                        |                         | 400          | ps       |  |

| Duty cycle                                                     |                                                        | 45        | —                        | 55          | 45                     |                         | 55           | %        |  |

| Spread-spectrum<br>modulating clock<br>frequency               | PCI Express<br>(PCIe)                                  | 30        | _                        | 33          | 30                     | _                       | 33           | kHz      |  |

| Spread-spectrum<br>downspread                                  | PCle                                                   | _         | 0 to0.5                  | _           |                        | 0 to –0                 | 5 —          | %        |  |

| On-chip termination resistors <sup>(19)</sup>                  | —                                                      | —         | 100                      |             |                        | 100                     | _            | :        |  |

| Absolute ₩ <sub>AX</sub> <sup>(3)</sup>                        | Dedicated<br>reference<br>clock pin                    |           | _                        | 1.6         |                        | _                       | 1.6          | V        |  |

|                                                                | RX reference<br>clock pin                              | _         | _                        | 1.2         | —                      | _                       | 1.2          |          |  |

| Absolute M <sub>IN</sub>                                       | _                                                      | -0.4      |                          |             | -0.4                   |                         |              | V        |  |

| Peak-to-peak<br>differential input<br>voltage                  | _                                                      | 200       | _                        | 1600        | 200                    | —                       | 1600         | mV       |  |

| V <sub>ICM</sub> (AC coupled)                                  | Dedicated<br>reference<br>clock pin                    |           | 1050/1000 <sup>2</sup>   | :)          | 1                      | 050/1000 <sup>2</sup>   | 2)           | mV       |  |

|                                                                | RX reference<br>clock pin                              | 1         | .0/0.9/0.852             | 22)         | 1.0                    | 22)                     | V            |          |  |

| V <sub>ICM</sub> (DC coupled)                                  | HCSL I/O<br>standard for<br>PCIe<br>reference<br>clock | 250       | _                        | 550         | 250                    |                         | 550          | mV       |  |

## Table 28. Transceiver Specifications for Stratix V GT Devices (Part 1 & 5)

Figure 6 shows the Stratix V DC gain curves for GT channels.

Figure 6. DC Gain Curves for GT Channels

## Transceiver Characterization

This section summarizes the Stratix V transceiver characterization results for compliance with the following protocols:

Interlaken 40G (XLAUI)/100G (CAUI) 10GBase-KR QSGMII XAUI SFI Gigabit Ethernet (Gbe / GIGE) SPAUI Serial Rapid IO (SRIO) CPRI OBSAI Hyper Transport (HT) SATA SAS

June 2018 Altera Corporation

| Symbol                                 | Parameter                                                                                         | Min            | Тур   | Max                                          | Unit      |

|----------------------------------------|---------------------------------------------------------------------------------------------------|----------------|-------|----------------------------------------------|-----------|

| t <sub>INCCJ</sub> <sup>(3), (4)</sup> | Input clock cycle-to-cycle jitter $\pm 200 \text{ MHz}$                                           | —              | _     | 0.15                                         | UI (p-p)  |

| INCCJ Y                                | Input clock cycle-to-cycle jittek (< 100 MHz)                                                     | -750           | _     | +750                                         | ps (p-p   |

| + (5)                                  | Period Jitter for dedicated clock outp⊌t <del>,{</del> ⊵<br>100 MHz)                              | _              | _     | 175 <sup>(1)</sup>                           | ps (p-p)  |

| t <sub>OUTPJ_DC<sup>(5)</sup></sub>    | Period Jitter for dedicated clock outp⊌t <del>,{</del> ≮<br>100 MHz)                              | _              | —     | 17.5 <sup>(1)</sup>                          | mUI (p-p) |

| <b>t</b> (5)                           | Period Jitter for dedicated clock output in fractional PLL ( $f_{UT}$ t 100 MHz)                  | al             | —     | 250 <sup>(11)</sup> ,<br>175 <sup>(12)</sup> | ps (p-p)  |

| t <sub>FOUTPJ_D</sub> C <sup>(5)</sup> | Period Jitter for dedicated clock output in fractional PLL ( $f_{UT}$ < 100 MHz)                  | al             | —     | 25 <sup>(11)</sup> ,<br>17.5 <sup>(12)</sup> | mUI (p-p) |

| t                                      | Cycle-to-Cycle Jitter for a dedicated clock output ( $f_{OUT} \ge 100 \text{ MHz}$ )              | _              | —     | 175                                          | ps (p-p)  |

| t <sub>outccj_d</sub> c <sup>5)</sup>  | Cycle-to-Cycle Jitter for a dedicated clock output $(f_{OUT} < 100 \text{ MHz})$                  | _              | —     | 17.5                                         | mUI (p-p) |

| t(5)                                   | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{UT}$ t 100 MHz)        | n              | —     | 250 <sup>(11)</sup> ,<br>175 <sup>(12)</sup> | ps (p-p)  |

| tFOUTCCJ_d <sup>5)</sup>               | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{UT}$ < 100 MHz)+       | n              | —     | 25 <sup>(11)</sup> ,<br>17.5 <sup>(12)</sup> | mUI (p-p) |

| t <sub>outpj_i0</sub> <sup>(5),</sup>  | Period Jitter for a clock output on a regular I/O in integer PLL ( $f_{UT} \ge 100 \text{ MHz}$ ) | —              | —     | 600                                          | ps (p-p)  |

| (8)                                    | Period Jitter for a clock output on a regular I/O (f <sub>OUT</sub> < 100 MHz)                    | —              | —     | 60                                           | mUI (p-p) |

| t <sub>FOUTPJ_IO</sub> (5),            | Period Jitter for a clock output on a regular I/O in fractional PLL ( $f_{UT}$ t 100 MHz)         | —              | —     | 600 <sup>(10)</sup>                          | ps (p-p)  |

| (8), (11)                              | Period Jitter for a clock output on a regular I/O in fractional PLL ( $f_{UT}$ < 100 MHz)         | —              | —     | 60 <sup>(10)</sup>                           | mUI (p-p) |

| t <sub>outccj_lo<sup>(5),</sup></sub>  | Cycle-to-cycle Jitter for a clock output on a regular in integer PLL ( $f_{UT}$ t 100 MHz)        | r I/O          | —     | 600                                          | ps (p-p)  |

| (8)                                    | Cycle-to-cycle Jitter for a clock output on a regulation in integer PLL ( $f_{UT}$ < 100 MHz)     | r I/O          | —     | 60 <sup>(10)</sup>                           | mUI (p-p) |

| t <sub>FOUTCCJ_IO</sub> ),             | Cycle-to-cycle Jitter for a clock output on a regulation fractional PLL ( $f_{UT}$ t 100 MHz)     | r I/O          | _     | 600 <sup>(10)</sup>                          | ps (p-p)  |

| (8), (11)                              | Cycle-to-cycle Jitter for a clock output on a regulation fractional PLL $d_{UT}$ < 100 MHz)       | r I/O          | —     | 60                                           | mUI (p-p) |

|                                        | Period Jitter for a dedicated clock output in cascal PLLs ( $f_{UT} \ge 100 \text{ MHz}$ )        | ded            | —     | 175                                          | ps (p-p)  |

| (5), (6)                               | Period Jitter for a dedicated clock output in cascal PLLs ( $f_{\text{DUT}}$ < 100 MHz)           | ded            | _     | 17.5                                         | mUI (p-p) |

| f <sub>DRIFT</sub>                     | Frequency drift after PFDENA is disabled for a du<br>of 100 μs                                    | ratio <u>n</u> | —     | ±10                                          | %         |

| dK <sub>BIT</sub>                      | Bit number of Delta Sigma Modulator (DSM)                                                         | 8              | 24    | 32                                           | Bi        |

| k <sub>value</sub>                     | Numerator of Fraction                                                                             | 128            | 83886 | 08 2147483                                   | 648 —     |

| <b>T</b> 1 1 0 4 |                   |                   | <b>–</b> · |              |

|------------------|-------------------|-------------------|------------|--------------|

| Table 31.        | PLL Specification | ons for Stratix V | Devices (  | Part 2 of 3) |

## Table 31. PLL Specifications for Stratix V Devices (Part 3 of 3)

| Symbol           | Parameter                                                           | Min    | Тур  | Max   | Unit |

|------------------|---------------------------------------------------------------------|--------|------|-------|------|

| f <sub>RES</sub> | Resolution of VCO frequenc <sub>Mr</sub> (# <sub>D</sub> = 100 MHz) | 390625 | 5.96 | 0.023 | Hz   |

Notes toTable 31

(1) This specification is limited in the actual II software by the I/Oaximum frequency. The maximul/O frequency is difference in the actual of the standard.

(2) This specification is limited the lower of the two:  $I/Q_{A}f_{X}$  or  $f_{OUT}$  of the PLL.

- (3) A high input jitter directly affectset FLL output jitter. To have low PLL output k jitter, you must provide a clearackal source < 120 ps.

- (4)  $f_{REF}$  is fIN/N when N = 1.

- (5) Peak-to-peak jitter withprobability level of 1<sup>1</sup>/<sub>2</sub> (14 sigma, 99.9999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PL when an input jitter of 30s is applied. The external memory interface clock output jitterifications use a different measurement nhed and are available Tiable 44 on page 52

- (6) The cascaded PLL specification is applicable with the llowing condition: a. Upstream PLL: 0.59Mht Upstream PLL BW < 1 MHz</p>

- b. Downstream PLL: Downstream PLL BW > 2 MHz

- (7) High bandwidth PLL settings are supported in external feedback mode.

- (8) The external memory interface clodpolujitter specifications use a differenteasurement method, ich is available in able 42 on page 50

- (9) The VCO frequency reported by the Quartus II software PinLtibusage Summary section of the pilation report takes into consideration the VCO post-scale counter K value. Therefore counter K has a value of 2 fitted uncy reported can be lower than the takes into consideration.

- (10) This specification only covers fractional PLL for low bandwidth<sub>C</sub> to the fractional value range 0.05 0.95 must be00 MHz, while to for fractional value range 0.20 0.80 must be00 MHz.

- (11) This specification only coveremetrional PLL for low bandwidth. Theofor fractional value range 0.05-0.95 must the00 MHz.

- (12) This specification only coveremetrional PLL for low bandwidth. Theofor fractional value range 0.20-0.80 must ble200 MHz.

## **DSP Block Specifications**

Table 32 lists the Stratix V DSP block performance specifications.

|                                           |      |         | P         | eforman | ce               |     |       |      |

|-------------------------------------------|------|---------|-----------|---------|------------------|-----|-------|------|

| Mode                                      | C1   | C2, C2l | - 12, 121 | . C3    | 13, 13L,<br>13YY | C4  | 14    | Unit |

|                                           |      | Modes   | using one | DSP     |                  |     |       |      |

| Three 9 x 9                               | 600  | 600     | 600       | 480     | 480              | 420 | 420   | MHz  |

| One 18 x 18                               | 600  | 600     | 600       | 480     | 480              | 420 | 400   | MHz  |

| Two partial 18 x 18 (or 16 x 16)          | 600  | 600     | 600       | 480     | 480              | 420 | 400   | MHz  |

| One 27 x 27                               | 500  | 500     | 500       | 400     | 400              | 350 | 350   | MHz  |

| One 36 x 18                               | 500  | 500     | 500       | 400     | 400              | 350 | 350   | MHz  |

| One sum of two 18 x 18(One sum 2 16 x 16) | 9f00 | 500     | 500       | 400     | 400              | 350 | 350   | MHz  |

| One sum of square                         | 500  | 500     | 500       | 400     | 400              | 350 | 350   | MHz  |

| One 18 x 18 plus 36 (a x b) + c           | 500  | 500     | 500       | 400     | 400              | 35  | ) 350 | MHz  |

|                                           |      | Modes ι | using two | DSPs    |                  |     | ·     |      |

| Three 18 x 18                             | 500  | 500     | 500       | 400     | 400              | 350 | 350   | MHz  |

| One sum of four 18 x 18                   | 475  | 475     | 475       | 380     | 380              | 300 | 300   | MHz  |

| One sum of two 27 x 27                    | 465  | 465     | 450       | 380     | 380              | 300 | 290   | MHz  |

| One sum of two 36 x 18                    | 475  | 475     | 475       | 380     | 380              | 300 | 300   | MHz  |

| One complex 18 x 18                       | 500  | 500     | 500       | 400     | 400              | 350 | 350   | MHz  |

| One 36 x 36                               | 475  | 475     | 475       | 380     | 380              | 300 | 300   | MHz  |

| Table 32. Block Performance Specifications for Stratix V DSP Devices (Part 1 of 2) |

|------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------|

|               |                                                                                                 | Resou           | rces Used | I    | Performance |     |     |         |                       |     |      |    |

|---------------|-------------------------------------------------------------------------------------------------|-----------------|-----------|------|-------------|-----|-----|---------|-----------------------|-----|------|----|

| Memory        | Mode                                                                                            | ALUTs           | Memor     | y C1 | C2,<br>C2L  | C3  | C4  | 12, 12L | 13,<br>. 13L,<br>13YY | 14  | Unit |    |

|               | Single-port, all<br>supported widths                                                            | 0               | 1         | 700  | 700         | 650 | 550 | 700     | 500                   | 450 | ) M  | Hz |

|               | Simple dual-port, all supported widths                                                          | 0               | 1         | 700  | 700         | 650 | 550 | 700     | 500                   | 450 | ) M  | Hz |

| M20K<br>Block | Simple dual-port with<br>the read-during-write<br>option set toOld Data<br>all supported widths | 0               | 1         | 525  | 525         | 455 | 400 | 525     | 455                   | 400 | ) M  | Hz |

|               | Simple dual-port with ECC enabled, 512 × 3                                                      | <sub>32</sub> 0 | 1         | 450  | 450         | 400 | 350 | 450     | 400                   | 350 | ) M  | Hz |

|               | Simple dual-port with<br>ECC and optional<br>pipeline registers<br>enabled, 512 × 32            | 0               | 1         | 600  | 600         | 500 | 450 | 600     | 500                   | 450 | ) M  | Hz |

|               | True dual port, all supported widths                                                            | 0               | 1         | 700  | 700         | 650 | 550 | 700     | 500                   | 450 | ) M  | Hz |

|               | ROM, all supported widths                                                                       | 0               | 1         | 700  | 700         | 650 | 550 | 700     | 500                   | 450 | ) M  | Hz |

Table 33. Memory Block Performance Specifications for Stratix V Deviders) (Part 2 of 2)

Notes toTable 33

(1) To achieve the maximum memory blockopperaince, use a memory block clock that comes through global clock routing free mignRtrL set to 50% output duty cycle. Use the Quartus II software to reipriving for this and other memory block clocking schemes.

(2) When you use the error detection in the contract of the co

(3) The F<sub>MAX</sub> specification is only activable with Fitter option SLAB Implementation 16-Bit Deep Modenabled.

# **Temperature Sensing Diode Specifications**

Table 34 lists the internal TSD specification.

Table 34. Internal Temperature Sensing Diode Specification

|      | nperature<br>Range | Accuracy | Offset<br>Calibrated<br>Option | Sampling Rate | Conversion<br>Time | Resolution | Minimum<br>Resolution<br>with no<br>Missing Codes |

|------|--------------------|----------|--------------------------------|---------------|--------------------|------------|---------------------------------------------------|

| -40° | °C to 100°C        | €±8°C    | No                             | 1 MHz, 500 k  | (Hz < 100 n        | ns 8 bits  | s 8 bits                                          |

Table 35 lists the specifications for the Stratix V external temperature sensing diode.

| Description                              | Min   | Тур   | Max   | Unit |

|------------------------------------------|-------|-------|-------|------|

| I <sub>bias</sub> diode source current   | 8     | —     | 200   | FA   |

| V <sub>bias</sub> , voltage across diode | 0.3   | _     | 0.9   | V    |

| Series resistance                        | —     | _     | < 1   | :    |

| Diode ideality factor                    | 1.006 | 1.008 | 1.010 | ) —  |

## Table 36. High-Speed I/O Specifications for Stratix V Devide (Part 2 of 4)

| Symbol                                                                                                                                                      | Conditions                                                                          |                  | C1  |      | C2, | C2L, | 12, 121 | - C  | C3, I3, I3L, I3YY C4,I4 |       |     |       | Unit |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|-----|------|-----|------|---------|------|-------------------------|-------|-----|-------|------|------|

| Symbol                                                                                                                                                      |                                                                                     | Min              | Тур | Max  | Min | Тур  | o Max   | < Mi | n Ty                    | ′p Ma | x N | lin T | ур М | ax   |

| Transmitter                                                                                                                                                 | Transmitter                                                                         |                  |     |      |     |      |         |      |                         |       |     |       |      |      |

|                                                                                                                                                             | SERDES factor<br>= 3 to 10 <sup>(9), (11),</sup><br>(12), (13), (14), (15),<br>(16) | J<br>(6)         |     | 1600 | (6) |      | 1434    | (6)  | _                       | 1250  | (6) | _     | 1050 | Mbps |

|                                                                                                                                                             | SERDES factor<br>t 4                                                                | J                |     |      |     |      |         |      |                         |       |     |       |      |      |

| True<br>Differential<br>I/O Standards                                                                                                                       | LVDS TX with<br>DPA <sup>(12)</sup> , <sup>(14),</sup> <sup>(15),</sup><br>(16)     | (6)              | —   | 1600 | (6) | _    | 1600    | (6)  |                         | 1600  | (6) | _     | 1250 | Mbps |

| - f <sub>HSDR</sub> (data<br>rate)                                                                                                                          | SERDES factor<br>= 2,<br>uses DDR<br>Registers                                      | J<br>(6)         | _   | (7)  | (6) | _    | (7)     | (6)  | _                       | (7)   | (6) | _     | (7)  | Mbps |

|                                                                                                                                                             | SERDES factor<br>= 1,<br>uses SDR<br>Register                                       | J<br>(6)         | _   | (7)  | (6) | _    | (7)     | (6)  | _                       | (7)   | (6) | _     | (7)  | Mbps |

| Emulated<br>Differential<br>I/O Standards<br>with Three<br>External<br>Output<br>Resistor<br>Networks -<br>f <sub>HSDR</sub> (data<br>rate) <sup>(10)</sup> | SERDES factor $= 4 \text{ to } 10^{(17)}$                                           | J <sub>(6)</sub> |     | 1100 | (6) |      | 1100    | (6)  |                         | 840   | (6) |       | 840  | Mbps |

| t <sub>x Jitter</sub> - True<br>Differential                                                                                                                | Total Jitter for<br>Data Rate<br>600 Mbps -<br>1.25 Gbps                            |                  |     | 160  |     |      | 160     | _    | _                       | 160   |     | _     | 160  | ps   |

| I/O Standards                                                                                                                                               | Total Jitter for<br>Data Rate<br>< 600 Mbps                                         |                  | _   | 0.1  | _   | _    | 0.1     |      | _                       | 0.1   |     | _     | 0.1  | UI   |

| t <sub>x Jitter</sub> -<br>Emulated<br>Differential<br>I/O Standards                                                                                        | Total Jitter for<br>Data Rate<br>600 Mbps - 1.25<br>Gbps                            |                  |     | 300  |     |      | 300     |      | _                       | 300   |     |       | 325  | ps   |

| with Three<br>External<br>Output<br>Resistor<br>Network                                                                                                     | Total Jitter for<br>Data Rate<br>< 600 Mbps                                         |                  |     | 0.2  |     |      | 0.2     |      |                         | 0.2   |     |       | 0.25 | UI   |

Figure 7 shows the dynamic phase alignment (DPA) lock time specifications with the DPA PLL calibration option enabled.

Figure 7. DPA Lock Time Specification with DPA PLL Calibration Enabled

| rx_reset      |  |  |

|---------------|--|--|

| rx_dpa_locked |  |  |

| -             |  |  |

Table 37 lists the DPA lock time specifications for Stratix V devices.

| Standard           | Training Pattern    | Number of Data<br>Transitions in One<br>Repetition of the<br>Training Pattern | Number of<br>Repetitions per 256<br>Data Transitions <sup>(4)</sup> | Maximum              |

|--------------------|---------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------|

| SPI-4              | 0000000000111111111 | 1 2                                                                           | 128                                                                 | 640 data transitions |

| Parallal Papid I/O | 00001111            | 2                                                                             | 128                                                                 | 640 data transitions |

| Parallel Rapid I/O | 10010000            | 4                                                                             | 64                                                                  | 640 data transitions |

| Miscellaneous      | 10101010            | 8                                                                             | 32                                                                  | 640 data transitions |

| Miscellaneous      | 01010101            | 8                                                                             | 32                                                                  | 640 data transitions |

Notes toTable 37

(1) The DPA lock time is for one channel.

(2) One data transition is defined as a 0-to-1 or 1-to-0 transition.

(3) The DPA lock time stated in this tapleties to both commendiand industrial grade.

(4) This is the number of repetitisofor the stated training patternachieve the 25 that transitions.

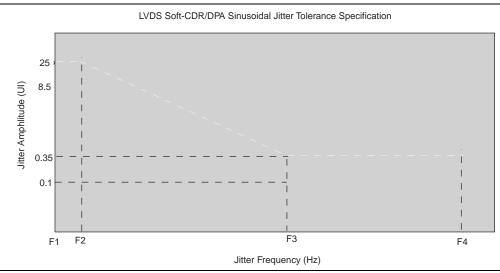

Figure 8 shows the LVDS soft-clock data recovery (CDR)/DPA sinusoidal jitter tolerance specification for a data rate t 1.25 Gbps.Table 38lists the LVDS soft-CDR/DPA sinusoidal jitter tolerance specification for a data rate t 1.25 Gbps.