### Intel - 5SGXMA3E3H29I3N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                   |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 128300                                                     |

| Number of Logic Elements/Cells | 340000                                                     |

| Total RAM Bits                 | 19456000                                                   |

| Number of I/O                  | 600                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.82V ~ 0.88V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 780-BBGA, FCBGA                                            |

| Supplier Device Package        | 780-HBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5sgxma3e3h29i3n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol                | Description                    | Minimum | Maximum | Unit |

|-----------------------|--------------------------------|---------|---------|------|

| V <sub>CCD_FPLL</sub> | PLL digital power supply       | -0.5    | 1.8     | V    |

| V <sub>CCA_FPLL</sub> | PLL analog power supply        | -0.5    | 3.4     | V    |

| VI                    | DC input voltage               | -0.5    | 3.8     | V    |

| TJ                    | Operating junction temperature | -55     | 125     | °C   |

| T <sub>STG</sub>      | Storage temperature (No bias)  | -65     | 150     | °C   |

| I <sub>OUT</sub>      | DC output current per pin      | -25     | 40      | mA   |

Table 3. Absolute Maximum Ratings for Stratix V Devices (Part 2 of 2)

Table 4 lists the absolute conditions for the transceiver power supply for Stratix V GX, GS, and GT devices.

Table 4. Transceiver Power Supply Absolute Conditions for Stratix V GX, GS, and GT Devices

| Symbol                | Description                                                  | Devices    | Minimum | Maximum | Unit |

|-----------------------|--------------------------------------------------------------|------------|---------|---------|------|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left side)             | GX, GS, GT | -0.5    | 3.75    | V    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right side)            | GX, GS     | -0.5    | 3.75    | V    |

| V <sub>CCA_GTBR</sub> | Transceiver channel PLL power supply (right side)            | GT         | -0.5    | 3.75    | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side)                 | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCHIP_R</sub>  | Transceiver hard IP power supply (right side)                | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS power supply (left side)                     | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS power supply (right side)                    | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBL</sub> | Receiver analog power supply (left side)                     | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBR</sub> | Receiver analog power supply (right side)                    | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCR_GTBR</sub> | Receiver analog power supply for GT channels (right side)    | GT         | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)                  | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBR</sub> | Transmitter analog power supply (right side)                 | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCT_GTBR</sub> | Transmitter analog power supply for GT channels (right side) | GT         | -0.5    | 1.35    | V    |

| V <sub>CCL_GTBR</sub> | Transmitter clock network power supply (right side)          | GT         | -0.5    | 1.35    | V    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (left side)           | GX, GS, GT | -0.5    | 1.8     | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side)          | GX, GS, GT | -0.5    | 1.8     | V    |

### **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage shown in Table 5 and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

Table 8 shows the transceiver power supply voltage requirements for various conditions.

**Table 8. Transceiver Power Supply Voltage Requirements**

| Conditions                                                          | Core Speed Grade                  | VCCR_GXB &<br>VCCT_GXB <sup>(2)</sup> | VCCA_GXB | VCCH_GXB | Unit |

|---------------------------------------------------------------------|-----------------------------------|---------------------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                       | All                               | 1.05                                  |          |          |      |

| <ul> <li>Data rate &gt; 10.3 Gbps.</li> <li>DFE is used.</li> </ul> | All                               | 1.05                                  |          |          |      |

| If ANY of the following conditions are true <sup>(1)</sup> :        |                                   |                                       | 3.0      |          |      |

| ATX PLL is used.                                                    |                                   |                                       |          |          |      |

| ■ Data rate > 6.5Gbps.                                              | All                               | 1.0                                   |          |          |      |

| ■ DFE (data rate ≤<br>10.3 Gbps), AEQ, or<br>EyeQ feature is used.  |                                   |                                       |          | 1.5      | V    |

| If ALL of the following                                             | C1, C2, I2, and I3YY              | 0.90                                  | 2.5      |          |      |

| <ul><li>conditions are true:</li><li>ATX PLL is not used.</li></ul> |                                   |                                       |          |          |      |

| ■ Data rate ≤ 6.5Gbps.                                              | C2L, C3, C4, I2L, I3, I3L, and I4 | 0.85                                  | 2.5      |          |      |

| <ul> <li>DFE, AEQ, and EyeQ are<br/>not used.</li> </ul>            |                                   |                                       |          |          |      |

### Notes to Table 8:

(1) Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

(2) If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to either 0.90 V or 0.85 V, they can be shared with the VCC core supply.

### **DC Characteristics**

This section lists the supply current, I/O pin leakage current, input pin capacitance, on-chip termination tolerance, and hot socketing specifications.

### **Supply Current**

Supply current is the current drawn from the respective power rails used for power budgeting. Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

For more information about power estimation tools, refer to the *PowerPlay Early Power Estimator User Guide* and the *PowerPlay Power Analysis* chapter in the *Quartus II Handbook*.

|                      |                                                                        |                            | <b>Resistance Tolerance</b> |       |                 |        |      |  |

|----------------------|------------------------------------------------------------------------|----------------------------|-----------------------------|-------|-----------------|--------|------|--|

| Symbol               | Description                                                            | Conditions                 | C1                          | C2,I2 | C3, I3,<br>I3YY | C4, I4 | Unit |  |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO} = 1.8$ and 1.5 V | ±30                         | ±30   | ±40             | ±40    | %    |  |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCI0</sub> = 1.2 V  | ±35                         | ±35   | ±50             | ±50    | %    |  |

| 100-Ω R <sub>D</sub> | Internal differential termination (100- $\Omega$ setting)              | V <sub>CCPD</sub> = 2.5 V  | ±25                         | ±25   | ±25             | ±25    | %    |  |

Table 12. OCT Without Calibration Resistance Tolerance Specifications for Stratix V Devices (Part 2 of 2)

Calibration accuracy for the calibrated series and parallel OCTs are applicable at the moment of calibration. When voltage and temperature conditions change after calibration, the tolerance may change.

OCT calibration is automatically performed at power-up for OCT-enabled I/Os. Table 13 lists the OCT variation with temperature and voltage after power-up calibration. Use Table 13 to determine the OCT variation after power-up calibration and Equation 1 to determine the OCT variation without recalibration.

### Equation 1. OCT Variation Without Recalibration for Stratix V Devices (1), (2), (3), (4), (5), (6)

$$R_{OCT} \,=\, R_{SCAL} \Big( 1 + \langle \frac{dR}{dT} \times \Delta T \rangle \pm \langle \frac{dR}{dV} \times \Delta V \rangle \Big)$$

### Notes to Equation 1:

- (1) The  $R_{OCT}$  value shows the range of OCT resistance with the variation of temperature and  $V_{CCIO}$ .

- (2) R<sub>SCAL</sub> is the OCT resistance value at power-up.

- (3)  $\Delta T$  is the variation of temperature with respect to the temperature at power-up.

- (4)  $\Delta V$  is the variation of voltage with respect to the V<sub>CCIO</sub> at power-up.

- (5) dR/dT is the percentage change of  $R_{\text{SCAL}}$  with temperature.

- (6) dR/dV is the percentage change of  $\mathsf{R}_{\mathsf{SCAL}}$  with voltage.

Table 13 lists the on-chip termination variation after power-up calibration.

| Table 13. | OCT Variation after Power-U | Calibration for Stratix V Devices | (Part 1 of 2) <sup>(1)</sup> |

|-----------|-----------------------------|-----------------------------------|------------------------------|

|-----------|-----------------------------|-----------------------------------|------------------------------|

| Symbol | Description                                      | V <sub>CCIO</sub> (V) | Typical | Unit |

|--------|--------------------------------------------------|-----------------------|---------|------|

|        |                                                  | 3.0                   | 0.0297  |      |

|        |                                                  | 2.5                   | 0.0344  |      |

| dR/dV  | OCT variation with voltage without recalibration | 1.8                   | 0.0499  | %/mV |

|        |                                                  | 1.5                   | 0.0744  |      |

|        |                                                  | 1.2                   | 0.1241  |      |

## **Switching Characteristics**

This section provides performance characteristics of the Stratix V core and periphery blocks.

These characteristics can be designated as Preliminary or Final.

- Preliminary characteristics are created using simulation results, process data, and other known parameters. The title of these tables show the designation as "Preliminary."

- Final numbers are based on actual silicon characterization and testing. The numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions. There are no designations on finalized tables.

## **Transceiver Performance Specifications**

This section describes transceiver performance specifications.

Table 23 lists the Stratix V GX and GS transceiver specifications.

| Table 23. | <b>Transceiver S</b> | necifications ( | for Stratix | V GX and GS | Devices (1) | (Part 1 of 7)   |

|-----------|----------------------|-----------------|-------------|-------------|-------------|-----------------|

|           | 114113001101 0       | poolitioutions  | IOI OUIUUA  |             |             | (1 41 ( 1 01 1) |

| Symbol/<br>Description                                         | Conditions                                                        | Transceiver Speed<br>Grade 1 |                                                      | Transceiver Speed<br>Grade 2 |          |     | Transceiver Speed<br>Grade 3 |           |         | Unit       |          |

|----------------------------------------------------------------|-------------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------|----------|-----|------------------------------|-----------|---------|------------|----------|

| Description                                                    |                                                                   | Min                          | Тур                                                  | Max                          | Min      | Тур | Max                          | Min       | Тур     | Max        | 1        |

| <b>Reference Clock</b>                                         |                                                                   |                              |                                                      |                              |          |     |                              |           |         |            |          |

| Supported I/O<br>Standards                                     | Dedicated<br>reference<br>clock pin                               | 1.2-V                        | PCML,                                                | 1.4-V PCM                    | L, 1.5-V |     | , 2.5-V PCN<br>HCSL          | 1L, Diffe | rential | LVPECL, L\ | /DS, and |

| Standards                                                      | RX reference<br>clock pin                                         |                              | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |                              |          |     |                              |           |         |            |          |

| Input Reference<br>Clock Frequency<br>(CMU PLL) <sup>(8)</sup> | _                                                                 | 40                           | _                                                    | 710                          | 40       | _   | 710                          | 40        | _       | 710        | MHz      |

| Input Reference<br>Clock Frequency<br>(ATX PLL) <sup>(8)</sup> | _                                                                 | 100                          |                                                      | 710                          | 100      |     | 710                          | 100       | _       | 710        | MHz      |

| Rise time                                                      | Measure at<br>±60 mV of<br>differential<br>signal <sup>(26)</sup> | _                            | _                                                    | 400                          | _        | _   | 400                          | _         | _       | 400        | ne       |

| Fall time                                                      | Measure at<br>±60 mV of<br>differential<br>signal <sup>(26)</sup> | _                            | _                                                    | 400                          | _        |     | 400                          | _         |         | 400        | - ps     |

| Duty cycle                                                     | —                                                                 | 45                           |                                                      | 55                           | 45       |     | 55                           | 45        | —       | 55         | %        |

| Spread-spectrum<br>modulating clock<br>frequency               | PCI Express®<br>(PCIe <sup>®</sup> )                              | 30                           |                                                      | 33                           | 30       |     | 33                           | 30        |         | 33         | kHz      |

| Symbol/<br>Description                                    | Conditions                                                          | Tra | nsceive<br>Grade | r Speed<br>1 | Transceiver Speed<br>Grade 2 |                 |     | Transceiver Speed<br>Grade 3 |                 |     | Unit |

|-----------------------------------------------------------|---------------------------------------------------------------------|-----|------------------|--------------|------------------------------|-----------------|-----|------------------------------|-----------------|-----|------|

| Description                                               |                                                                     | Min | Тур              | Max          | Min                          | Тур             | Max | Min                          | Тур             | Max |      |

|                                                           | 85– $\Omega$ setting                                                |     | 85 ±<br>30%      |              | —                            | 85 ±<br>30%     |     |                              | 85 ±<br>30%     |     | Ω    |

| Differential on-                                          | 100–Ω<br>setting                                                    | _   | 100<br>±<br>30%  |              | _                            | 100<br>±<br>30% |     | _                            | 100<br>±<br>30% |     | Ω    |

| chip termination<br>resistors <sup>(21)</sup>             | 120–Ω<br>setting                                                    | _   | 120<br>±<br>30%  |              | _                            | 120<br>±<br>30% |     | _                            | 120<br>±<br>30% |     | Ω    |

|                                                           | 150-Ω<br>setting                                                    | _   | 150<br>±<br>30%  | _            | _                            | 150<br>±<br>30% |     | _                            | 150<br>±<br>30% |     | Ω    |

| V <sub>ICM</sub><br>(AC and DC                            | V <sub>CCR_GXB</sub> =<br>0.85 V or 0.9<br>V<br>full<br>bandwidth   |     | 600              |              | _                            | 600             | _   |                              | 600             |     | mV   |

|                                                           | V <sub>CCR_GXB</sub> =<br>0.85 V or 0.9<br>V<br>half<br>bandwidth   | _   | 600              | _            | _                            | 600             | _   | _                            | 600             | _   | mV   |

| coupled)                                                  | V <sub>CCR_GXB</sub> =<br>1.0 V/1.05 V<br>full<br>bandwidth         | _   | 700              |              | _                            | 700             |     |                              | 700             |     | mV   |

|                                                           | V <sub>CCR_GXB</sub> =<br>1.0 V<br>half<br>bandwidth                | _   | 750              | _            | _                            | 750             | _   | _                            | 750             | _   | mV   |

| t <sub>LTR</sub> <sup>(11)</sup>                          | _                                                                   | —   | —                | 10           | _                            | —               | 10  | —                            | —               | 10  | μs   |

| t <sub>LTD</sub> (12)                                     | _                                                                   | 4   |                  |              | 4                            |                 |     | 4                            |                 |     | μs   |

| t <sub>LTD_manual</sub> <sup>(13)</sup>                   |                                                                     | 4   |                  |              | 4                            |                 |     | 4                            | _               |     | μs   |

| t <sub>LTR_LTD_manual</sub> <sup>(14)</sup>               |                                                                     | 15  |                  |              | 15                           | —               |     | 15                           | —               |     | μs   |

| Run Length                                                | _                                                                   | _   |                  | 200          |                              | —               | 200 |                              | —               | 200 | UI   |

| Programmable<br>equalization<br>(AC Gain) <sup>(10)</sup> | Full<br>bandwidth<br>(6.25 GHz)<br>Half<br>bandwidth<br>(3.125 GHz) |     |                  | 16           | _                            |                 | 16  | _                            |                 | 16  | dB   |

Table 23. Transceiver Specifications for Stratix V GX and GS Devices <sup>(1)</sup> (Part 4 of 7)

### Table 23. Transceiver Specifications for Stratix V GX and GS Devices <sup>(1)</sup> (Part 6 of 7)

| Symbol/                                                               | Conditions                                   | Trai | isceive<br>Grade | r Speed<br>1                  | Transceiver Speed<br>Grade 2 |     |                               | Transceiver Speed<br>Grade 3 |     |                               | Unit |

|-----------------------------------------------------------------------|----------------------------------------------|------|------------------|-------------------------------|------------------------------|-----|-------------------------------|------------------------------|-----|-------------------------------|------|

| Description                                                           |                                              | Min  | Тур              | Max                           | Min                          | Тур | Max                           | Min                          | Тур | Max                           |      |

| Inter-transceiver<br>block transmitter<br>channel-to-<br>channel skew | xN PMA<br>bonded mode                        |      |                  | 500                           | _                            |     | 500                           | _                            |     | 500                           | ps   |

| CMU PLL                                                               |                                              |      |                  |                               |                              |     |                               |                              |     |                               |      |

| Supported Data<br>Range                                               | _                                            | 600  |                  | 12500                         | 600                          | _   | 12500                         | 600                          | _   | 8500/<br>10312.5<br>(24)      | Mbps |

| t <sub>pll_powerdown</sub> <sup>(15)</sup>                            | _                                            | 1    |                  | —                             | 1                            | —   | —                             | 1                            | —   | —                             | μs   |

| t <sub>pll_lock</sub> (16)                                            | _                                            |      | _                | 10                            | —                            | _   | 10                            | —                            | —   | 10                            | μs   |

| ATX PLL                                                               | 1                                            |      |                  |                               |                              |     |                               |                              |     |                               |      |

|                                                                       | VCO<br>post-divider<br>L=2                   | 8000 |                  | 14100                         | 8000                         | _   | 12500                         | 8000                         | _   | 8500/<br>10312.5<br>(24)      | Mbps |

| Current and Date                                                      | L=4                                          | 4000 | _                | 7050                          | 4000                         | _   | 6600                          | 4000                         | —   | 6600                          | Mbps |

| Supported Data<br>Rate Range                                          | L=8                                          | 2000 | _                | 3525                          | 2000                         | _   | 3300                          | 2000                         | _   | 3300                          | Mbps |

|                                                                       | L=8,<br>Local/Central<br>Clock Divider<br>=2 | 1000 | _                | 1762.5                        | 1000                         |     | 1762.5                        | 1000                         |     | 1762.5                        | Mbps |

| t <sub>pll_powerdown</sub> (15)                                       | _                                            | 1    |                  | _                             | 1                            |     |                               | 1                            | —   | _                             | μs   |

| t <sub>pll_lock</sub> <sup>(16)</sup>                                 | —                                            |      |                  | 10                            | —                            | —   | 10                            | —                            | —   | 10                            | μs   |

| fPLL                                                                  | •                                            |      |                  | •                             |                              |     |                               |                              | •   |                               |      |

| Supported Data<br>Range                                               | _                                            | 600  | _                | 3250/<br>3125 <sup>(25)</sup> | 600                          | _   | 3250/<br>3125 <sup>(25)</sup> | 600                          | _   | 3250/<br>3125 <sup>(25)</sup> | Mbps |

| t <sub>pll_powerdown</sub> <sup>(15)</sup>                            | _                                            | 1    |                  | _                             | 1                            | _   | —                             | 1                            | —   | —                             | μs   |

Figure 3 shows the Stratix V AC gain curves for GX channels.

Figure 3. AC Gain Curves for GX Channels (full bandwidth)

Stratix V GT devices contain both GX and GT channels. All transceiver specifications for the GX channels not listed in Table 28 are the same as those listed in Table 23.

Table 28 lists the Stratix V GT transceiver specifications.

| Symbol/                                                        | Conditions                                             | :                                                    | Transceive<br>Speed Grade                                                             |      |      | Transceive<br>peed Grade |      | Unit |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|--------------------------|------|------|--|--|--|--|

| Description                                                    |                                                        | Min                                                  | Тур                                                                                   | Max  | Min  | Тур                      | Max  |      |  |  |  |  |

| Reference Clock                                                |                                                        |                                                      |                                                                                       |      |      |                          |      |      |  |  |  |  |

| Supported I/O<br>Standards                                     | Dedicated<br>reference<br>clock pin                    | 1.2-V PCN                                            | 1.2-V PCML, 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, Differential LVPECL, LVDS<br>and HCSL |      |      |                          |      |      |  |  |  |  |

|                                                                | RX reference<br>clock pin                              | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |                                                                                       |      |      |                          |      |      |  |  |  |  |

| Input Reference Clock<br>Frequency (CMU<br>PLL) <sup>(6)</sup> | _                                                      | 40                                                   | _                                                                                     | 710  | 40   | _                        | 710  | MHz  |  |  |  |  |

| Input Reference Clock<br>Frequency (ATX PLL) <sup>(6)</sup>    | _                                                      | 100                                                  | -                                                                                     | 710  | 100  | _                        | 710  | MHz  |  |  |  |  |

| Rise time                                                      | 20% to 80%                                             |                                                      | _                                                                                     | 400  |      | —                        | 400  |      |  |  |  |  |

| Fall time                                                      | 80% to 20%                                             |                                                      |                                                                                       | 400  | —    |                          | 400  | ps   |  |  |  |  |

| Duty cycle                                                     | —                                                      | 45                                                   |                                                                                       | 55   | 45   |                          | 55   | %    |  |  |  |  |

| Spread-spectrum<br>modulating clock<br>frequency               | PCI Express<br>(PCIe)                                  | 30                                                   | _                                                                                     | 33   | 30   | _                        | 33   | kHz  |  |  |  |  |

| Spread-spectrum<br>downspread                                  | PCle                                                   | _                                                    | 0 to -0.5                                                                             |      | _    | 0 to -0.5                | _    | %    |  |  |  |  |

| On-chip termination resistors <sup>(19)</sup>                  | _                                                      | _                                                    | 100                                                                                   | _    | _    | 100                      | _    | Ω    |  |  |  |  |

| Absolute V <sub>MAX</sub> <sup>(3)</sup>                       | Dedicated<br>reference<br>clock pin                    |                                                      | _                                                                                     | 1.6  | _    | _                        | 1.6  | V    |  |  |  |  |

|                                                                | RX reference<br>clock pin                              | _                                                    | _                                                                                     | 1.2  | _    | _                        | 1.2  |      |  |  |  |  |

| Absolute V <sub>MIN</sub>                                      | —                                                      | -0.4                                                 | —                                                                                     | —    | -0.4 | —                        | —    | V    |  |  |  |  |

| Peak-to-peak<br>differential input<br>voltage                  | _                                                      | 200                                                  | _                                                                                     | 1600 | 200  | _                        | 1600 | mV   |  |  |  |  |

| V <sub>ICM</sub> (AC coupled)                                  | Dedicated<br>reference<br>clock pin                    |                                                      | 1050/1000 (                                                                           | 2)   |      | 1050/1000 (              | 2)   | mV   |  |  |  |  |

|                                                                | RX reference<br>clock pin                              | 1                                                    | .0/0.9/0.85 (                                                                         | 22)  | 1.   | V                        |      |      |  |  |  |  |

| V <sub>ICM</sub> (DC coupled)                                  | HCSL I/O<br>standard for<br>PCIe<br>reference<br>clock | 250                                                  | _                                                                                     | 550  | 250  | _                        | 550  | mV   |  |  |  |  |

### Table 28. Transceiver Specifications for Stratix V GT Devices (Part 1 of 5) <sup>(1)</sup>

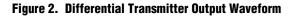

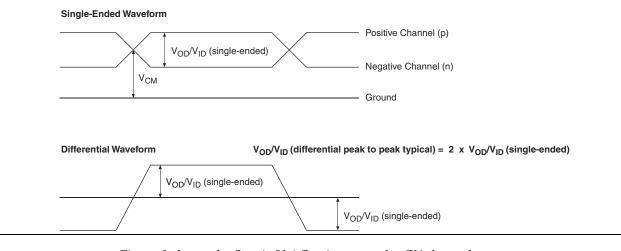

Table 29 shows the  $V_{\text{OD}}$  settings for the GT channel.

| Table 29. | Typical Von Setting | g for GT Channel, T | <b>EX Termination = 100</b> $\Omega$ |

|-----------|---------------------|---------------------|--------------------------------------|

|-----------|---------------------|---------------------|--------------------------------------|

| Symbol                                                  | V <sub>OD</sub> Setting | V <sub>op</sub> Value (mV) |

|---------------------------------------------------------|-------------------------|----------------------------|

|                                                         | 0                       | 0                          |

|                                                         | 1                       | 200                        |

| $\mathbf{V}_{0D}$ differential peak to peak typical (1) | 2                       | 400                        |

| VOD unicicilitat peak to peak typical (*)               | 3                       | 600                        |

|                                                         | 4                       | 800                        |

|                                                         | 5                       | 1000                       |

### Note:

(1) Refer to Figure 4.

Figure 4 shows the differential transmitter output waveform.

Figure 5 shows the Stratix V AC gain curves for GT channels.

Figure 5. AC Gain Curves for GT Channels

- XFI

- ASI

- HiGig/HiGig+

- HiGig2/HiGig2+

- Serial Data Converter (SDC)

- GPON

- SDI

- SONET

- Fibre Channel (FC)

- PCIe

- QPI

- SFF-8431

Download the Stratix V Characterization Report Tool to view the characterization report summary for these protocols.

## **Core Performance Specifications**

This section describes the clock tree, phase-locked loop (PLL), digital signal processing (DSP), memory blocks, configuration, and JTAG specifications.

### **Clock Tree Specifications**

Table 30 lists the clock tree specifications for Stratix V devices.

Table 30. Clock Tree Performance for Stratix V Devices (1)

|                              |                             | Performance              |        |      |  |

|------------------------------|-----------------------------|--------------------------|--------|------|--|

| Symbol                       | C1, C2, C2L, I2, and<br>I2L | C3, I3, I3L, and<br>I3YY | C4, I4 | Unit |  |

| Global and<br>Regional Clock | 717                         | 650                      | 580    | MHz  |  |

| Periphery Clock              | 550                         | 500                      | 500    | MHz  |  |

### Note to Table 30:

(1) The Stratix V ES devices are limited to 600 MHz core clock tree performance.

| Mode                  | C1  | C2, C2L  | 12, 12L   | C3   | 13, 13L,<br>13YY | C4  | 14  | Unit |

|-----------------------|-----|----------|-----------|------|------------------|-----|-----|------|

|                       |     | Modes us | ing Three | DSPs |                  |     |     |      |

| One complex 18 x 25   | 425 | 425      | 415       | 340  | 340              | 275 | 265 | MHz  |

| Modes using Four DSPs |     |          |           |      |                  |     |     |      |

| One complex 27 x 27   | 465 | 465      | 465       | 380  | 380              | 300 | 290 | MHz  |

### Table 32. Block Performance Specifications for Stratix V DSP Devices (Part 2 of 2)

## **Memory Block Specifications**

Table 33 lists the Stratix V memory block specifications.

### Table 33. Memory Block Performance Specifications for Stratix V Devices <sup>(1), (2)</sup> (Part 1 of 2)

|        |                                            | <b>Resources Used</b> |        | Performance |            |     |     |         |                     |     |      |

|--------|--------------------------------------------|-----------------------|--------|-------------|------------|-----|-----|---------|---------------------|-----|------|

| Memory | Mode                                       | ALUTS                 | Memory | C1          | C2,<br>C2L | C3  | C4  | 12, 12L | 13,<br>13L,<br>13YY | 14  | Unit |

|        | Single port, all supported widths          | 0                     | 1      | 450         | 450        | 400 | 315 | 450     | 400                 | 315 | MHz  |

|        | Simple dual-port,<br>x32/x64 depth         | 0                     | 1      | 450         | 450        | 400 | 315 | 450     | 400                 | 315 | MHz  |

| MLAB   | Simple dual-port, x16 depth <sup>(3)</sup> | 0                     | 1      | 675         | 675        | 533 | 400 | 675     | 533                 | 400 | MHz  |

|        | ROM, all supported widths                  | 0                     | 1      | 600         | 600        | 500 | 450 | 600     | 500                 | 450 | MHz  |

| Speed Grade | Min | Max | Unit |

|-------------|-----|-----|------|

| C4,I4       | 8   | 16  | ps   |

### Table 40. DQS Phase Offset Delay Per Setting for Stratix V Devices <sup>(1), (2)</sup> (Part 2 of 2)

#### Notes to Table 40:

(1) The typical value equals the average of the minimum and maximum values.

(2) The delay settings are linear with a cumulative delay variation of 40 ps for all speed grades. For example, when using a -2 speed grade and applying a 10-phase offset setting to a 90° phase shift at 400 MHz, the expected average cumulative delay is [625 ps + (10 × 10 ps) ± 20 ps] = 725 ps ± 20 ps.

Table 41 lists the DQS phase shift error for Stratix V devices.

Table 41. DQS Phase Shift Error Specification for DLL-Delayed Clock (t<sub>DQS\_PSERR</sub>) for Stratix V Devices <sup>(1)</sup>

| Number of DQS Delay<br>Buffers | C1  | C2, C2L, I2, I2L | C3, I3, I3L, I3YY | C4,14 | Unit |

|--------------------------------|-----|------------------|-------------------|-------|------|

| 1                              | 28  | 28               | 30                | 32    | ps   |

| 2                              | 56  | 56               | 60                | 64    | ps   |

| 3                              | 84  | 84               | 90                | 96    | ps   |

| 4                              | 112 | 112              | 120               | 128   | ps   |

Notes to Table 41:

(1) This error specification is the absolute maximum and minimum error. For example, skew on three DQS delay buffers in a -2 speed grade is  $\pm 78$  ps or  $\pm 39$  ps.

Table 42 lists the memory output clock jitter specifications for Stratix V devices.

| Clock<br>Network | Parameter                       | Symbol                | C1   |     | C2, C2L, I2, I2L |     | C3, I3, I3L,<br>I3YY |      | C4,14 |                                                                                                                                                                                        | Unit |

|------------------|---------------------------------|-----------------------|------|-----|------------------|-----|----------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| NELWUIK          |                                 | -                     | Min  | Max | Min              | Max | Min                  | Max  | Min   | Min         Max         Unit           -55         55         ps           -110         110         ps           -82.5         82.5         ps           -82.5         82.5         ps |      |

|                  | Clock period jitter             | t <sub>JIT(per)</sub> | -50  | 50  | -50              | 50  | -55                  | 55   | -55   | 55                                                                                                                                                                                     | ps   |

| Regional         | Cycle-to-cycle period<br>jitter | $t_{\rm JIT(cc)}$     | -100 | 100 | -100             | 100 | -110                 | 110  | -110  | 110                                                                                                                                                                                    | ps   |

|                  | Duty cycle jitter               | $t_{JIT(duty)}$       | -50  | 50  | -50              | 50  | -82.5                | 82.5 | -82.5 | 82.5                                                                                                                                                                                   | ps   |

|                  | Clock period jitter             | t <sub>JIT(per)</sub> | -75  | 75  | -75              | 75  | -82.5                | 82.5 | -82.5 | 82.5                                                                                                                                                                                   | ps   |

| Global           | Cycle-to-cycle period<br>jitter | $t_{\text{JIT(cc)}}$  | -150 | 150 | -150             | 150 | -165                 | 165  | -165  | 165                                                                                                                                                                                    | ps   |

|                  | Duty cycle jitter               | $t_{JIT(duty)}$       | -75  | 75  | -75              | 75  | -90                  | 90   | -90   | 90                                                                                                                                                                                     | ps   |

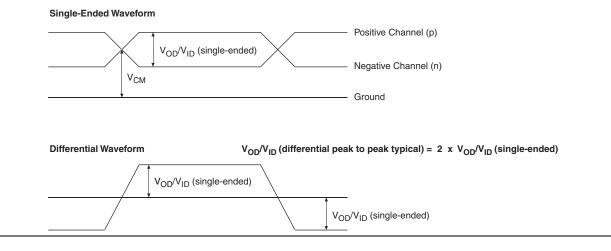

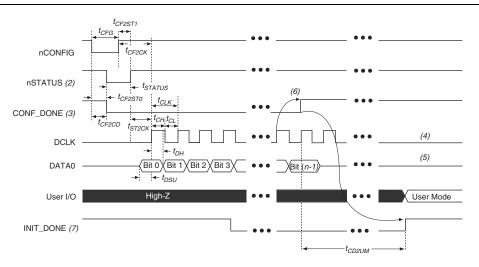

#### Figure 13. FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is >1 (1), (2)

#### Notes to Figure 13:

- (1) Use this timing waveform and parameters when the DCLK-to-DATA [] ratio is >1. To find out the DCLK-to-DATA [] ratio for your system, refer to Table 49 on page 55.

- (2) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (3) After power-up, the Stratix V device holds nSTATUS low for the time as specified by the POR delay.

- (4) After power-up, before and during configuration, CONF\_DONE is low.

- (5) Do not leave DCLK floating after configuration. You can drive it high or low, whichever is more convenient.

- (6) "r" denotes the DCLK-to-DATA [] ratio. For the DCLK-to-DATA [] ratio based on the decompression and the design security feature enable settings, refer to Table 49 on page 55.

- (7) If needed, pause DCLK by holding it low. When DCLK restarts, the external host must provide data on the DATA [31..0] pins prior to sending the first DCLK rising edge.

- (8) To ensure a successful configuration, send the entire configuration data to the Stratix V device. CONF\_DONE is released high after the Stratix V device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- (9) After the option bit to enable the INIT DONE pin is configured into the device, the INIT DONE goes low.

Page 60

Table 51 lists the timing parameters for Stratix V devices for FPP configuration when the DCLK-to-DATA[] ratio is more than 1.

| Symbol                            | Parameter                                         | Minimum                                             | Maximum              | Units |

|-----------------------------------|---------------------------------------------------|-----------------------------------------------------|----------------------|-------|

| t <sub>CF2CD</sub>                | nCONFIG low to CONF_DONE low                      | —                                                   | 600                  | ns    |

| t <sub>CF2ST0</sub>               | nCONFIG low to nSTATUS low                        | —                                                   | 600                  | ns    |

| t <sub>CFG</sub>                  | nCONFIG low pulse width                           | 2                                                   | _                    | μS    |

| t <sub>STATUS</sub>               | nSTATUS low pulse width                           | 268                                                 | 1,506 <sup>(2)</sup> | μS    |

| t <sub>CF2ST1</sub>               | nCONFIG high to nSTATUS high                      | —                                                   | 1,506 <sup>(2)</sup> | μS    |

| t <sub>CF2CK</sub> <sup>(5)</sup> | nCONFIG high to first rising edge on DCLK         | 1,506                                               | _                    | μS    |

| t <sub>ST2CK</sub> <sup>(5)</sup> | nSTATUS high to first rising edge of DCLK         | 2                                                   | —                    | μS    |

| t <sub>DSU</sub>                  | DATA [] setup time before rising edge on DCLK     | 5.5                                                 |                      | ns    |

| t <sub>DH</sub>                   | DATA [] hold time after rising edge on DCLK       | N-1/f <sub>DCLK</sub> <sup>(5)</sup>                |                      | S     |

| t <sub>CH</sub>                   | DCLK high time                                    | $0.45 	imes 1/f_{MAX}$                              |                      | S     |

| t <sub>CL</sub>                   | DCLK low time                                     | $0.45\times1/f_{MAX}$                               |                      | S     |

| t <sub>CLK</sub>                  | DCLK period                                       | 1/f <sub>MAX</sub>                                  |                      | S     |

| f                                 | DCLK frequency (FPP ×8/×16)                       | —                                                   | 125                  | MHz   |

| f <sub>MAX</sub>                  | DCLK frequency (FPP ×32)                          | —                                                   | 100                  | MHz   |

| t <sub>R</sub>                    | Input rise time                                   | —                                                   | 40                   | ns    |

| t <sub>F</sub>                    | Input fall time                                   | —                                                   | 40                   | ns    |

| t <sub>CD2UM</sub>                | CONF_DONE high to user mode <sup>(3)</sup>        | 175                                                 | 437                  | μS    |

| t <sub>CD2CU</sub>                | CONF_DONE high to CLKUSR enabled                  | 4 × maximum<br>DCLK period                          | _                    | _     |

| t <sub>CD2UMC</sub>               | CONF_DONE high to user mode with CLKUSR option on | $t_{CD2CU}$ + (8576 × CLKUSR period) <sup>(4)</sup> | _                    | _     |

#### Notes to Table 51:

- (1) Use these timing parameters when you use the decompression and design security features.

- (2) You can obtain this value if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

- (3) The minimum and maximum numbers apply only if you use the internal oscillator as the clock source for initializing the device.

- (4) To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the Initialization section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices" chapter.

- (5) N is the  ${\tt DCLK}\mbox{-to-DATA}$  ratio and  $f_{{\tt DCLK}}$  is the  ${\tt DCLK}$  frequency the system is operating.

- (6) If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

| Symbol              | Parameter                                         | Minimum                                        | Maximum | Units |

|---------------------|---------------------------------------------------|------------------------------------------------|---------|-------|

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode $(3)$                 | 175                                            | 437     | μS    |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                        | _       | —     |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | t <sub>cd2cu</sub> + (8576 ×<br>clkusr period) | _       | —     |

Table 53. AS Timing Parameters for AS  $\times$ 1 and AS  $\times$ 4 Configurations in Stratix V Devices <sup>(1), (2)</sup> (Part 2 of 2)

#### Notes to Table 53:

(1) The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

(2) t<sub>CF2CD</sub>, t<sub>CF2ST0</sub>, t<sub>CF2ST0</sub>, t<sub>CF6</sub>, t<sub>STATUS</sub>, and t<sub>CF2ST1</sub> timing parameters are identical to the timing parameters for PS mode listed in Table 54 on page 63.

(3) To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on this pin, refer to the Initialization section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices" chapter.

## **Passive Serial Configuration Timing**

Figure 15 shows the timing waveform for a passive serial (PS) configuration when using a MAX II device, MAX V device, or microprocessor as an external host.

Figure 15. PS Configuration Timing Waveform <sup>(1)</sup>

#### Notes to Figure 15:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (2) After power-up, the Stratix V device holds <code>nSTATUS</code> low for the time of the POR delay.

- (3) After power-up, before and during configuration, CONF DONE is low.

- (4) Do not leave DCLK floating after configuration. You can drive it high or low, whichever is more convenient.

- (5) DATAO is available as a user I/O pin after configuration. The state of this pin depends on the dual-purpose pin settings in the **Device and Pins Option**.

- (6) To ensure a successful configuration, send the entire configuration data to the Stratix V device. CONF\_DONE is released high after the Stratix V device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- (7) After the option bit to enable the INIT DONE pin is configured into the device, the INIT DONE goes low.

## **Remote System Upgrades**

Table 56 lists the timing parameter specifications for the remote system upgrade circuitry.

| Table 56. Remote System Upgrade Circuitry Timing Specifications |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| Parameter                               | Parameter Minimum |   | Unit |  |

|-----------------------------------------|-------------------|---|------|--|

| t <sub>RU_nCONFIG</sub> <sup>(1)</sup>  | 250               | — | ns   |  |

| t <sub>RU_nRSTIMER</sub> <sup>(2)</sup> | 250               | _ | ns   |  |

#### Notes to Table 56:

- (1) This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE megafunction high for the minimum timing specification. For more information, refer to the Remote System Upgrade State Machine section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices" chapter.

- (2) This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE megafunction high for the minimum timing specification. For more information, refer to the User Watchdog Timer section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices" chapter.

## **User Watchdog Internal Circuitry Timing Specification**

Table 57 lists the operating range of the 12.5-MHz internal oscillator.

### Table 57. 12.5-MHz Internal Oscillator Specifications

| Minimum Typical |     | Maximum | Units |  |

|-----------------|-----|---------|-------|--|

| 5.3             | 7.9 | 12.5    | MHz   |  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the Quartus II Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis. The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

You can download the Excel-based I/O Timing spreadsheet from the Stratix V Devices Documentation web page.

## **Programmable IOE Delay**

Table 58 lists the Stratix V IOE programmable delay settings.

Table 58. IOE Programmable Delay for Stratix V Devices (Part 1 of 2)

| Deremeter        | Available             | Min           | Fast       | Model      |       |       |       | Slow N | lodel |             |       |      |

|------------------|-----------------------|---------------|------------|------------|-------|-------|-------|--------|-------|-------------|-------|------|

| Parameter<br>(1) | Available<br>Settings | Offset<br>(2) | Industrial | Commercial | C1    | C2    | C3    | C4     | 12    | 13,<br>13YY | 14    | Unit |

| D1               | 64                    | 0             | 0.464      | 0.493      | 0.838 | 0.838 | 0.924 | 1.011  | 0.844 | 0.921       | 1.006 | ns   |

| D2               | 32                    | 0             | 0.230      | 0.244      | 0.415 | 0.415 | 0.459 | 0.503  | 0.417 | 0.456       | 0.500 | ns   |

### Table 60. Glossary (Part 2 of 4)

| Letter                | Subject                            | Definitions                                                                                                                                                                                                                   |

|-----------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G                     |                                    |                                                                                                                                                                                                                               |

| Н                     | _                                  | _                                                                                                                                                                                                                             |

| Ι                     |                                    |                                                                                                                                                                                                                               |

| J                     | J<br>JTAG Timing<br>Specifications | High-speed I/O block—Deserialization factor (width of parallel data bus).<br>JTAG Timing Specifications:<br>TMS<br>TDI<br>$t_{JCP}$<br>$t_{JCP}$<br>$t_{JPCO}$<br>$t_{JPCO}$<br>$t_{JPXZ}$<br>TDO<br>$t_{JPXZ}$<br>$t_{JPXZ}$ |

| K<br>L<br>M<br>N<br>O | _                                  | _                                                                                                                                                                                                                             |

| Ρ                     | PLL<br>Specifications              | Diagram of PLL Specifications (1)                                                                                                                                                                                             |

| Q                     |                                    | _                                                                                                                                                                                                                             |

|                       | 1                                  |                                                                                                                                                                                                                               |

### Table 61. Document Revision History (Part 2 of 3)

| Date          | Version | Changes                                                                                                                                                                                                                                         |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         | Added the I3YY speed grade and changed the data rates for the GX channel in Table 1.                                                                                                                                                            |

|               |         | <ul> <li>Added the I3YY speed grade to the V<sub>CC</sub> description in Table 6.</li> </ul>                                                                                                                                                    |

|               |         | <ul> <li>Added the I3YY speed grade to V<sub>CCHIP_L</sub>, V<sub>CCHIP_R</sub>, V<sub>CCHSSI_L</sub>, and V<sub>CCHSSI_R</sub> descriptions in<br/>Table 7.</li> </ul>                                                                         |

|               |         | ■ Added 240-Ω to Table 11.                                                                                                                                                                                                                      |

|               |         | Changed CDR PPM tolerance in Table 23.                                                                                                                                                                                                          |

|               |         | <ul> <li>Added additional max data rate for fPLL in Table 23.</li> </ul>                                                                                                                                                                        |

|               |         | <ul> <li>Added the I3YY speed grade and changed the data rates for transceiver speed grade 3 in<br/>Table 25.</li> </ul>                                                                                                                        |

|               |         | <ul> <li>Added the I3YY speed grade and changed the data rates for transceiver speed grade 3 in<br/>Table 26.</li> </ul>                                                                                                                        |

|               |         | Changed CDR PPM tolerance in Table 28.                                                                                                                                                                                                          |

|               |         | <ul> <li>Added additional max data rate for fPLL in Table 28.</li> </ul>                                                                                                                                                                        |

|               |         | Changed the mode descriptions for MLAB and M20K in Table 33.                                                                                                                                                                                    |

|               |         | ■ Changed the Max value of f <sub>HSCLK_OUT</sub> for the C2, C2L, I2, I2L speed grades in Table 36.                                                                                                                                            |

| November 2014 | 3.3     | <ul> <li>Changed the frequency ranges for C1 and C2 in Table 39.</li> </ul>                                                                                                                                                                     |

|               |         | Changed the .rbf file sizes for 5SGSD6 and 5SGSD8 in Table 47.                                                                                                                                                                                  |

|               |         | <ul> <li>Added note about nSTATUS to Table 50, Table 51, Table 54.</li> </ul>                                                                                                                                                                   |

|               |         | <ul> <li>Changed the available settings in Table 58.</li> </ul>                                                                                                                                                                                 |

|               |         | <ul> <li>Changed the note in "Periphery Performance".</li> </ul>                                                                                                                                                                                |

|               |         | <ul> <li>Updated the "I/O Standard Specifications" section.</li> </ul>                                                                                                                                                                          |

|               |         | <ul> <li>Updated the "Raw Binary File Size" section.</li> </ul>                                                                                                                                                                                 |

|               |         | <ul> <li>Updated the receiver voltage input range in Table 22.</li> </ul>                                                                                                                                                                       |

|               |         | <ul> <li>Updated the max frequency for the LVDS clock network in Table 36.</li> </ul>                                                                                                                                                           |

|               |         | ■ Updated the DCLK note to Figure 11.                                                                                                                                                                                                           |

|               |         | <ul> <li>Updated Table 23 VO<sub>CM</sub> (DC Coupled) condition.</li> </ul>                                                                                                                                                                    |

|               |         | <ul> <li>Updated Table 6 and Table 7.</li> </ul>                                                                                                                                                                                                |

|               |         | ■ Added the DCLK specification to Table 55.                                                                                                                                                                                                     |

|               |         | <ul> <li>Updated the notes for Table 47.</li> </ul>                                                                                                                                                                                             |

|               |         | <ul> <li>Updated the list of parameters for Table 56.</li> </ul>                                                                                                                                                                                |

| November 2013 | 3.2     | Updated Table 28                                                                                                                                                                                                                                |

| November 2013 | 3.1     | Updated Table 33                                                                                                                                                                                                                                |

| November 2013 | 3.0     | Updated Table 23 and Table 28                                                                                                                                                                                                                   |

| October 2013  | 2.9     | <ul> <li>Updated the "Transceiver Characterization" section</li> </ul>                                                                                                                                                                          |

|               |         | <ul> <li>Updated Table 3, Table 12, Table 14, Table 19, Table 20, Table 23, Table 24, Table 28, Table 30, Table 31, Table 32, Table 33, Table 36, Table 39, Table 40, Table 41, Table 42, Table 47, Table 53, Table 58, and Table 59</li> </ul> |

| October 2013  | 2.8     | <ul> <li>Added Figure 1 and Figure 3</li> </ul>                                                                                                                                                                                                 |

|               |         | <ul> <li>Added the "Transceiver Characterization" section</li> </ul>                                                                                                                                                                            |

|               |         | <ul> <li>Removed all "Preliminary" designations.</li> </ul>                                                                                                                                                                                     |