### Intel - 5SGXMA7H3F35I3 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                  |

|--------------------------------|-----------------------------------------------------------|

| Number of LABs/CLBs            | 234720                                                    |

| Number of Logic Elements/Cells | 622000                                                    |

| Total RAM Bits                 | 51200000                                                  |

| Number of I/O                  | 552                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 0.82V ~ 0.88V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 1152-BBGA, FCBGA                                          |

| Supplier Device Package        | 1152-FBGA (35x35)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5sgxma7h3f35i3 |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol                | Description                    | Minimu | m Maxin         | num l | Init |

|-----------------------|--------------------------------|--------|-----------------|-------|------|

| V <sub>CCD_FPLL</sub> | PLL digital power supply       | 0.5    | 5 1.            | 8     | V    |

| V <sub>CCA_FPLL</sub> | PLL analog power supply        | 0.5    | 5 3.            | 4     | V    |

| VI                    | DC input voltage               | 0.5    | 3.8             | 3     | v    |

| TJ                    | Operating junction temperature |        | 55              | 125   | °C   |

| T <sub>STG</sub>      | Storage temperature (No bias)  | (      | 55 <sup>-</sup> | 150   | °C   |

| I <sub>OUT</sub>      | DC output current per pin      | 2      | 5 4             | 40    | mA   |

Table 3. Absolute Maximum Ratings for Stratix V Devices (Part 2 of 2)

Table 4 lists the absolute conditions fort*itane*sceiver power supply for Stratix V GX, GS, and GT devices.

Table 4. Transceiver Power Supply Absolute Conditions for Stratix V GX, GS, and GT Devices

| [                     |                                                   |              |            |        |      |      |

|-----------------------|---------------------------------------------------|--------------|------------|--------|------|------|

| Symbol                | Description                                       | Devices      | s Minim    | um Max | imum | Unit |

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left side)  | G            | X, GS, GT  | 0.5    | 3.75 | 5 V  |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right side) |              | GX, GS     | 0.5    | 3.75 | V    |

| $V_{CCA\_GTBR}$       | Transceiver channel PLL power supply (right side) |              | GT         | 0.5    | 3.75 | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side)      | GX           | , GS, GT   | 0.5    | 1.35 | V    |

| V <sub>CCHIP_R</sub>  | Transceiver hard IP power supply (right side)     | GX           | (, GS, GT  | 0.5    | 1.35 | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS powerpply (left side)             | GX, GS,      | GT O.      | 51.    | 35   | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS powerpply (right side)            | GX, GS,      | GT O.      | 51.    | 35   | V    |

| $V_{CCR_GXBL}$        | Receiver analog power supply (left side)          | GX           | GS, GT     | 0.5    | 1.35 | V    |

| $V_{CCR_GXBR}$        | Receiver analog power supply (right side)         | GX           | GS, GT     | 0.5    | 1.35 | V    |

| $V_{CCR_GTBR}$        | Receiver analog power supply for GT channels (rig | ht side)     | GT         | 0.5    | 1.3  | 5 V  |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)       | G>           | (, GS, GT  | 0.5    | 1.35 | V    |

| $V_{CCT\_GXBR}$       | Transmitter analog power supply (right side)      | G>           | (, GS, GT  | 0.5    | 1.35 | V    |

| $V_{CCT\_GTBR}$       | Transmitter analog power supply for GT channels   | (right side) | GT         | 0.5    | 1.3  | 35 V |

| $V_{CCL\_GTBR}$       | Transmitter clock network power supply (right sid | de)          | GT         | 0.5    | 1.3! | 5 V  |

| $V_{CCH_GXBL}$        | Transmitter output buffer power supply (left side | )            | GX, GS, GT | 0.5    | 1.8  | 8 V  |

| $V_{CCH_GXBR}$        | Transmitter output buffer power supply (right sid | e)           | GX, GS, GT | 0.5    | 1.8  | 8 V  |

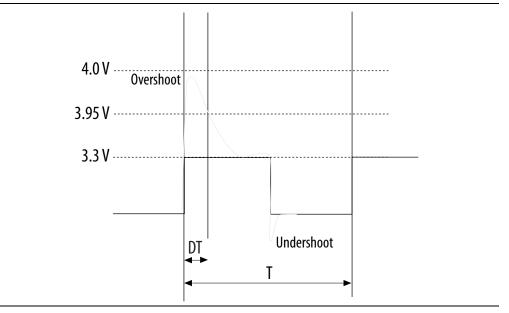

Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals  $m_{ab}$  vershoot to the voltage show  $m_{ab} = 5$  and undershoot to 2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

Table 5 lists the maximum allowed input ove**osh** voltage and the duration of the overshoot voltage as a percentageevorce lifetime. The maximum allowed overshoot duration is specified as a pergentoal high time over the lifetime of the device. A DC signal is equivalent to 100% of the duty cycle. For example, a signal that overshoots to 3.95 V can be at 3.95 V for 201% yover the lifetime of the device; for a device lifetime of 10 years, therefore duration amounts to ~2 years.

Overshoot Duration as %Unit Symbol Description Condition @  $T_J = 100^{\circ}C$ 100 3.8 % 3.85 64 % 3.9 36 % 3.95 21 % Vi (AC) AC input voltage 4 12 % 4.05 7 % 4.1 4 % 2 4.15 % 4.2 1 %

Table 5. Maximum Allowed Overshoot During Transitions

Figure 1. Stratix V Device Overshoot Duration

Table 8 shows the transceiver power suppolytage requirements for various conditions.

Table 8. Transceiver Power Supply Voltage Requirements

| Conditions                                                                                                                                                  | Core Speed Grade                     | VCCR_GXB &<br>VCCT_GXB <sup>(2)</sup> | VCCA_GXB | VCCH_GX | B Uni |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------|----------|---------|-------|

| If BOTH of the followin<br>conditions are true:<br>Data rate > 10.3 Gbp<br>DFE is used.                                                                     | ΔΙΙ                                  | 1.05                                  |          |         |       |

| If ANY of the following<br>conditions are tftle<br>ATX PLL is used.<br>Data rate > 6.5Gbps<br>DFE (data rate<br>10.3 Gbps), AEQ, or<br>EyeQ feature is used | All                                  | 1.0                                   | 3.0      | 1.5     | V     |

| If ALL of the following                                                                                                                                     | C1, C2, I2, and I3YY                 | 0.90                                  | 2.5      | •       |       |

| conditions are true:<br>ATX PLL is not used.<br>Data rat <b>d</b> 6.5Gbps.<br>DFE, AEQ, and EyeQ a<br>not used.                                             | C2L, C3, C4, I2L, I3, I3L, an<br>are | d 14 0.85                             |          | 2.5     |       |

Notes toable 8

(1) Choose this power supply voltation option if you plan to upgradesignoutater with a finitive listed condition

(2) If the VCCR\_GXB and VCCT\_GXB supplies tare 1.0 V or 1.05 V, they casimate blewith the VOCe supply. If the RCGXB and VCCT\_GXB are set to either 0.90 V other 985 and, be shared twite hVCC core supply.

## **DC** Characteristics

This section lists the supply current,  $\beta$  leakage current, input pin capacitance, on-chip termination tolerance, and hot socketing specifications.

#### Supply Current

Supply current is the current drawn from the respective power rails used for power budgeting. Use the Excel-based Early Povestimator (EPE) to get supply current estimates for your design because the second vary greatly with the resources you use.

f For more information about power estimation tools, refer Rowthe Play Early Power Estimator User Guialed the Power Play Power Analysinapter in the Quartus II Handbook

- 1 You typically use the interactive Excel-bda&arly Power Estimator before designing the FPGA to get a magnitude estimateholderice power. The Quartus II PowerPlay Power Analyzer provides better quality estters based on the specifics of the design after you complete place-and-route. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-dedivand estimated signal activities that, when combined with detailed circuit modelields very accurate power estimates.

- f For more information about power estimation tools, referRowthePlay Early Power Estimator User Guialed thePowerPlay Power Analysinapter in thQuartus II Handbook

## Table 24 shows the maximum transmittertadaate for the clock network.

|                                  |                                  | ATX PLL                  |                                                      |                                  | CMU P(2                  | )                             |                                  | fPLL                     |                               |

|----------------------------------|----------------------------------|--------------------------|------------------------------------------------------|----------------------------------|--------------------------|-------------------------------|----------------------------------|--------------------------|-------------------------------|

| Clock Network                    | Non-<br>bonded<br>Mode<br>(Gbps) | Bonded<br>Mode<br>(Gbps) | Channel<br>Span                                      | Non-<br>bonded<br>Mode<br>(Gbps) | Bonded<br>Mode<br>(Gbps) | Channel<br>Span               | Non-<br>bonded<br>Mode<br>(Gbps) | Bonded<br>Mode<br>(Gbps) | Channel<br>Span               |

| x1 <sup>(3)</sup>                | 14.1                             |                          | 6                                                    | 12.5                             |                          | 6                             | 3.125                            |                          | 3                             |

| x6 <sup>(3)</sup>                |                                  | 14.1                     | 6                                                    |                                  | 12.5                     | 6                             |                                  | 3.125                    | 6                             |

| x6 PLL<br>Feedbac <sup>(∉)</sup> |                                  | 14.1                     | Side-<br>wide                                        |                                  | 12.5                     | Side-<br>wide                 |                                  |                          |                               |

| xN (PCIe)                        |                                  | 8.0                      | 8                                                    |                                  | 5.0                      | 8                             |                                  |                          |                               |

| xN (Native PHY I                 | 8.0<br>D)                        | 8.0                      | Up to 13<br>channels<br>above<br>and<br>below<br>PLL |                                  | 7.99                     | Up to 13<br>channels<br>above |                                  | 3.125                    | Up to 13<br>channels<br>above |

|                                  | <del>r)</del>                    | 8.01 to<br>9.8304        |                                                      |                                  | 1.99                     | and<br>below<br>PLL           | 3.123                            | 3.123                    | and<br>below<br>PLL           |

Notes toable 24

(1) Valid data rates belowabiencom specified this table depend on the reference for equency and the PLL counters. Set the MegaWizard message dutring PHY IP instantiation.

(2) ATX PLL is recommended at 8 Gbpsvændætborates for improved jitter performance.

(3) Channel span is invitantransceiver bank.

(4) Side-wide channel bonding is allowed up to the maximum supported by the PHY IP.

Table 26shows the approximate maximum data rate using the 10G PCS.

| Table 26          | Strativ V | / 106 | PCS | Approximate | Maximum       | Nata Rate | 2 |

|-------------------|-----------|-------|-----|-------------|---------------|-----------|---|

| $1 a D E \ge 0$ . | Suaux     | V 100 | гсэ | Approximate | IVIAAIIIIUIII |           |   |

|                     |                                       |                                        |                      |       |        |         |       | 1      | -  |  |  |

|---------------------|---------------------------------------|----------------------------------------|----------------------|-------|--------|---------|-------|--------|----|--|--|

| Mode <sup>(2)</sup> | Transceiver                           | PMA Width                              | 64                   | 40    | 40     | 4       | 0 3   | 2      | 32 |  |  |

| IVIOUe(-)           | Speed Grade                           | FC3 WIUTH                              | 64                   | 66/6  | 57 5   | 0 4     | 40 64 | /66/67 | 32 |  |  |

|                     | 1                                     | C1, C2, C2L, I2, I<br>core speed grad  | 2L<br>e 14.1         | 14.1  | 10.69  | 14.1    | 13.6  | 5 13   | 6  |  |  |

| 2                   | C1, C2, C2L, I2, I<br>core speed grad |                                        | 12.5                 | 10.69 | 9 12.5 | 5 12.   | 5 12  | 2.5    |    |  |  |

|                     | C3, I3, I3L<br>core speed grad        | e 12.5                                 | 12.5                 | 10.69 | 9 12.5 | 5 10.8  | 38 10 | .88    |    |  |  |

| FIFO or<br>Register |                                       | C1, C2, C2L, I2, I2<br>core speed grad |                      |       |        |         |       |        |    |  |  |

|                     | 3                                     | C3, I3, I3L<br>core speed grad         | speed grade 8.5 Gbps |       |        |         |       |        |    |  |  |

|                     | 5                                     | C4, I4<br>core speed grad              |                      |       |        |         |       |        |    |  |  |

|                     |                                       | I3YY<br>core speed grad                | e                    |       | 10.31  | 25 Gbps |       |        |    |  |  |

Notes toable 26

(1) The maximum data rate is in Gbps.

(2) The Phase Compensation FIFO can beed configed mode or register mode FIFiCthmode, the period are not fixed, the latency can vary. In the register mode inthers are fixed low latency.

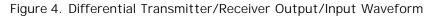

### Figure 4 shows the differential transmitter output waveform.

Figure 5 shows the Stratix V AC gain curves for GT channels.

Figure 5. AC Gain Curves for GT Channels

# Periphery Performance

This section describes periphery performanincluding high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such Lak DShehigh-speed I/O interface, external memory interface, and PCDL PCI-X bus interface. General-purpose I/O standards suchs 3.3-, 2,51-8-, and 1.5VTTL/LVCMOS are capable of a typical 167 MHz and LIVICMOS at 100 MHz interfacing frequency with a 10 pF load.

1 The actual achievable frequency dependents design- and system-specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design andstearn setup to determine the maximum achievable frequency in your system.

High-Speed I/O Specification

Table 36lists high-speed I/O timig for Stratix V devices.

| Symbol                                                                                      | Conditions                     |     | C1  |     | C2, | C2L  | , 12, 12 | !L ( | C3, I3 | 3, I3L, I  | ЗҮҮ |     | C4,I4      | Unit |

|---------------------------------------------------------------------------------------------|--------------------------------|-----|-----|-----|-----|------|----------|------|--------|------------|-----|-----|------------|------|

| Symbol                                                                                      | Conditions                     | Min | Тур | Max | Mi  | n Tỵ | yp M     | ax N | ∕lin   | Typ N      | Иах | Min | Тур        | Max  |

| f <sub>HSCLK_in</sub> (input<br>clock<br>frequency)<br>True<br>Differential<br>I/O Standard | Clock boost fac<br>W = 1 to 4€ | tor |     | 800 | 5   |      | 800      | 5    |        | 625        | 5   |     | 525        | MHz  |

| f <sub>HSCLK_in</sub> (input<br>clock<br>frequency)<br>Single Ended<br>I/O<br>Standard§)    | Clock boost fac                | tor |     | 800 | 5   |      | 800      | 5    |        | 625        | 5   |     | 525        | MHz  |

| f <sub>HSCLK_in</sub> (input<br>clock<br>frequency)<br>Single Ended<br>I/O Standard         | Clock boost fac<br>W = 1 to 4€ | tor |     | 520 | 5   |      | 520      | 5    |        | 420        | 5   |     | 420        | MHz  |

| f <sub>HSCLK_OUT</sub><br>(output cloc<br>frequency)                                        | k                              | 5   |     | 800 | 5   | 2    | 800      | 5    |        | 625<br>(5) | 5   |     | 525<br>(5) | MHz  |

Table 36. High-Speed I/O Specifications for Stratix V<sup>1</sup>DeVi¢Bart 1 of 4)

## Table 36. High-Speed I/O Specifications for Stratix V<sup>1</sup>Devicesrt 2 of 4)

| Currente e l                                                                                                                                               | O an ditti ana                                                                            | C1       |     |      | C2, C2L, I2, I2L C3, I3, I3L, I3YY C4,I4 |      |      |      |      |       | C4,I4 | l lus i t |      |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------|-----|------|------------------------------------------|------|------|------|------|-------|-------|-----------|------|-------------|

| Symbol                                                                                                                                                     | Conditions                                                                                | Min      | Тур | Max  | Mir                                      | n Ty | /p M | ax N | /lin | Тур М | Иах   | Min       | Тур  | Unit<br>Max |

| Transmitter                                                                                                                                                |                                                                                           |          |     |      |                                          |      |      |      |      |       |       |           |      |             |

|                                                                                                                                                            | SERDES factor<br>= 3 to 1 <sup>(0)</sup> ( <sup>11</sup> )<br>(12) (13) (14) (15)<br>(16) | (6)      |     | 1600 | (6)                                      |      | 1434 | (6)  |      | 1250  | (6)   |           | 1050 | Mbps        |

|                                                                                                                                                            | SERDES factor<br>t 4                                                                      | J        |     |      |                                          |      |      |      |      |       |       |           |      |             |

| True<br>Differential<br>I/O Standard                                                                                                                       | LVDS TX with<br>DPA <sup>(12)</sup> (14) (15)<br>Is <sup>(16)</sup>                       | (6)      |     | 1600 | (6)                                      |      | 1600 | (6)  |      | 1600  | (6)   |           | 1250 | Mbps        |

| - f <sub>HSDR</sub> (data<br>rate)                                                                                                                         | SERDES factor<br>= 2,<br>uses DDR<br>Registers                                            | (6)      |     | (7)  | (6)                                      |      | (7)  | (6)  |      | (7)   | (6)   |           | (7)  | Mbps        |

|                                                                                                                                                            | SERDES factor<br>= 1,<br>uses SDR<br>Register                                             | )<br>(6) |     | (7)  | (6)                                      |      | (7)  | (6)  |      | (7)   | (6)   |           | (7)  | Mbps        |

| Emulated<br>Differential<br>I/O Standard<br>with Three<br>External<br>Output<br>Resistor<br>Networks -<br>f <sub>HSDR</sub> (data<br>rate) <sup>(10)</sup> | s<br>SERDES factor<br>= 4 to 10 <sup>7)</sup>                                             | J (6)    |     | 1100 | (6)                                      |      | 1100 | (6)  |      | 840   | (6)   |           | 840  | Mbps        |

| t <sub>x Jitter</sub> True<br>Differential                                                                                                                 | Total Jitter fo<br>Data Rate<br>600 Mbps -<br>1.25 Gbps                                   |          | 1   | 60   |                                          | 16   | D    |      | 160  |       | 1     | 60        | ps   |             |

| I/O Standard                                                                                                                                               | <sup>IS</sup> Total Jitter fo<br>Data Rate<br>< 600 Mbps                                  | r        | C   | D.1  |                                          | 0.1  |      |      | 0.1  |       | 0.    | 1         | UI   |             |

| t <sub>x Jitter</sub><br>Emulated<br>Differential<br>I/O Standard                                                                                          | Total Jitter fo<br>Data Rate<br>600 Mbps - 1.2<br>Is Gbps                                 |          | ()  | 300  |                                          | 30   | 0    |      | 300  | D     |       | 325       | ps   |             |

| with Three<br>External<br>Output<br>Resistor<br>Network                                                                                                    | Total Jitter fo<br>Data Rate<br>< 600 Mbps                                                | r        | C   | ).2  |                                          | 0.2  | 2    |      | 0.2  |       | 0.    | 25        | UI   |             |

| Symbol            | Description                              | Min | Max                       | Unit |

|-------------------|------------------------------------------|-----|---------------------------|------|

| t <sub>JPH</sub>  | JTAG port hold time                      | 5   | —                         | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                | —   | 11 <sup>(1)</sup>         | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output | —   | 14 <sup>(1)</sup>         | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance | —   | <b>1</b> 4 <sup>(1)</sup> | ns   |

Table 46. JTAG Timing Parameters and Values for Stratix V Devices

Notes to Table 46:

(1) A 1 ns adder is required for each V<sub>CCI0</sub> voltage step down from 3.0 V. For example,  $t_{JPC0} = 12$  ns if V<sub>CCI0</sub> of the TDO I/O bank = 2.5 V, or 13 ns if it equals 1.8 V.

(2) The minimum TCK clock period is 167 ns if VCCBAT is within the range 1.2V-1.5V when you perform the volatile key programming.

## **Raw Binary File Size**

For the POR delay specification, refer to the "POR Delay Specification" section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices".

Table 47 lists the uncompressed raw binary file (.rbf) sizes for Stratix V devices.

| Family       | Device | Package                      | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) <sup>(4), (5)</sup> |

|--------------|--------|------------------------------|--------------------------------|--------------------------------------------|

|              | ECCVA2 | H35, F40, F35 <sup>(2)</sup> | 213,798,880                    | 562,392                                    |

|              | 5SGXA3 | H29, F35 <sup>(3)</sup>      | 137,598,880                    | 564,504                                    |

|              | 5SGXA4 | _                            | 213,798,880                    | 563,672                                    |

|              | 5SGXA5 | _                            | 269,979,008                    | 562,392                                    |

|              | 5SGXA7 | _                            | 269,979,008                    | 562,392                                    |

| Stratix V GX | 5SGXA9 | _                            | 342,742,976                    | 700,888                                    |

|              | 5SGXAB | _                            | 342,742,976                    | 700,888                                    |

|              | 5SGXB5 | _                            | 270,528,640                    | 584,344                                    |

|              | 5SGXB6 | _                            | 270,528,640                    | 584,344                                    |

|              | 5SGXB9 | _                            | 342,742,976                    | 700,888                                    |

|              | 5SGXBB | _                            | 342,742,976                    | 700,888                                    |

| Stratix V GT | 5SGTC5 | _                            | 269,979,008                    | 562,392                                    |

|              | 5SGTC7 | —                            | 269,979,008                    | 562,392                                    |

|              | 5SGSD3 | _                            | 137,598,880                    | 564,504                                    |

|              | 5SGSD4 | F1517                        | 213,798,880                    | 563,672                                    |

| Ctratic V CC | 556504 | _                            | 137,598,880                    | 564,504                                    |

| Stratix V GS | 5SGSD5 | _                            | 213,798,880                    | 563,672                                    |

|              | 5SGSD6 | _                            | 293,441,888                    | 565,528                                    |

|              | 5SGSD8 | _                            | 293,441,888                    | 565,528                                    |

Table 47. Uncompressed .rbf Sizes for Stratix V Devices