# E·XFL

### Intel - 5SGXMA7K2F35I3LN Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 234720                                                      |

| Number of Logic Elements/Cells | 622000                                                      |

| Total RAM Bits                 | 51200000                                                    |

| Number of I/O                  | 432                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 0.82V ~ 0.88V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 1152-BBGA, FCBGA                                            |

| Supplier Device Package        | 1152-FBGA (35x35)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5sgxma7k2f35i3ln |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol            | Description            | Condition   | Mith     | Тур | Max <sup>(4)</sup> | Unit |

|-------------------|------------------------|-------------|----------|-----|--------------------|------|

| +                 | Power supply ramp time | Standard PO | R 200 µs | _   | 100 ms             | \$ - |

| τ <sub>RAMP</sub> |                        | Fast POR    | 200 µs   |     | 4 ms               |      |

#### Table 6. Recommended Operating Conditions for Stratix V Devices (Part 2 of 2)

Notes toTable 6

(1) V<sub>CCPD</sub>must be 2.5 V when<sub>C</sub>y<sub>IO</sub>is 2.5, 1.8, 1.5, 1.35, 1.25 or 1.2 V<sub>C</sub>y<sub>D</sub>must be 3.0 V when<sub>C</sub>y<sub>IO</sub>is 3.0 V.

(2) If you do not use the design secufieig/ture in Stratix V devices, connecte/V to a 1.2- to 3.0-V power supply. Stratix V power-on-reset (POR) circuitry monitors V<sub>CBAT</sub> Stratix V devices will not exit POR<sub>Cife/A</sub> stays at logic low.

(3) C2L and I2L can also be run at 0.90 V for legacy bthatdsere designed forettC2 and I2 speed grades.

(4) The power supply value describes the but day the DC (static) power supply takes and does not include the dynamic ablae requirements. Refer to the PDN food the additional budget for et day namic tolerance requirements.

Table 7 lists the transceiver power supply recommended operating conditions for Stratix V GX, GS, and GT devices.

Table 7. Recommended Transceiver Power Supply Operating Conditions for Stratix V GX, GS, and GT Devices (Part 1 of 2)

| Symbol                | Description                                                                                      | Devices                       | Minimú <del>f</del> h | Typical | Maximun <sup>(4)</sup> | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|---------|------------------------|------|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left                                                       |                               | 2.85                  | 3.0     | 3.15                   | V    |

| (1), (3)              | side)                                                                                            |                               | 2.375                 | 2.5     | 2.625                  | v    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (rg<br>side)                                                | ght <sub>ex cs</sub>          | 2.85                  | 3.0     | 3.15                   | V    |

| (1), (3)              |                                                                                                  | GA, GS                        | 2.375                 | 2.5     | 2.625                  | v    |

| V <sub>CCA_GTBR</sub> | Transceiver channel PLL power supply (r side)                                                    | GI                            | 2.85                  | 3.0     | 3.15                   | V    |

|                       | Transceiver hard IP power supply (left sid<br>C1, C2, I2, and I3YY speed grades)                 | <sup>le:</sup> GX, GS, GT     | 0.87                  | 0.9     | 0.93                   | Ŋ    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left sid<br>C2L, C3, C4, I2L, I3, I3L, and I4 speed<br>grades) | GX, GS, G1                    |                       | 0.85    | 0.88                   |      |

|                       | Transceiver hard IP power supply (right s<br>C1, C2, I2, and I3YY speed grades)                  | <sup>ide:</sup><br>GX, GS, GT | 0.87                  | 0.9     | 0.93                   | Y    |

| V <sub>CCHIP_R</sub>  | Transceiver hard IP power supply (right s C2L, C3, C4, I2L, I3, I3L, and I4 speed grades)        | de;<br>GX, GS, G1             | 0.82                  | 0.85    | 0.88                   |      |

|                       | Transceiver PCS powearpply (left side;<br>C1, C2, I2, and I3YY speed grades)                     | GX, GS, GT                    | 0.87                  | 0.9     | 0.93                   | Y    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS powserpply (left side;<br>C2L, C3, C4, I2L, I3, I3L, and I4 speed<br>grades)     | GX, GS, GT                    | 0.82                  | 0.85    | 0.88                   |      |

|                       | Transceiver PCS powseurpply (right side;<br>C1, C2, I2, and I3YY speed grades)                   | GX, GS, GT                    | 0.87                  | 0.9     | 0.93                   | Ŋ    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS powserpply (right side;<br>C2L, C3, C4, I2L, I3, I3L, and I4 speed<br>grades)    | GX, GS, GT                    | 0.82                  | 0.85    | 0.88                   |      |

|                       |                                                                                                  | GX, GS                        | 0.82                  | 0.85    | 0.88                   |      |

| V <sub>CCR_GXBL</sub> |                                                                                                  |                               | ст <sup>0.87</sup>    | 0.90    | 0.93                   | v    |

| (2)                   | Receiver analog power supply (left side)                                                         |                               | 0.97                  | 1.0     | 1.03                   | v    |

|                       |                                                                                                  |                               | 1.03                  | 1.05    | 1.07                   |      |

| Symbol                | Description                                                     | Devices                   | Minimú <del>f</del> h      | Typical | Maximun <sup>(4)</sup> | Unit |   |

|-----------------------|-----------------------------------------------------------------|---------------------------|----------------------------|---------|------------------------|------|---|

|                       | Receiver analog power supply (right side                        | ) GX, GS                  | 0.82                       | 0.85    | 0.88                   |      |   |

| V <sub>CCR_GXBR</sub> |                                                                 |                           | 0.87                       | 0.90    | 0.93                   | V    |   |

| (2)                   |                                                                 |                           | 0.97                       | 1.0     | 1.03                   | v    |   |

|                       |                                                                 |                           | 1.03                       | 1.05    | 1.07                   |      |   |

| V <sub>CCR_GTBR</sub> | Receiver analog power supply for GT channels (right side)       | GT                        | 1.02                       | 1.05    | 1.08                   | V    |   |

|                       |                                                                 |                           | 0.82                       | 0.85    | 0.88                   | V    |   |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left sid                       | e)       GX, GS           | 0.87                       | 0.90    | 0.93                   |      |   |

| (2)                   |                                                                 |                           | 0.97                       | 1.0     | 1.03                   | v    |   |

|                       |                                                                 |                           | 1.03                       | 1.05    | 1.07                   |      |   |

|                       | Transmitter analog power supply (right si                       | de) GX, GS                | 0.82                       | 0.85    | 0.88                   |      |   |

| V <sub>CCT_GXBR</sub> |                                                                 |                           | de) GX, GS <del>, GT</del> | 0.87    | 0.90                   | 0.93 | V |

| (2)                   |                                                                 |                           | 0.97                       | 1.0     | 1.03                   | v    |   |

|                       |                                                                 |                           | 1.03                       | 1.05    | 1.07                   |      |   |

| V <sub>CCT_GTBR</sub> | Transmitter analog power supply for GT GT channels (right side) |                           | 1.02                       | 1.05    | 1.08                   | V    |   |

| $V_{CCL\_GTBR}$       | Transmitter clock network persupply                             | GT                        | 1.02                       | 1.05    | 1.08                   | V    |   |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (le side)                | <sup>eft</sup> GX, GS, GT | 1.425                      | 1.5     | 1.575                  |      |   |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side)             | GX, GS, GT                | 1.425                      | 1.5     | 1.575                  |      |   |

| Table 7. Recommended Transceiver Power Supply Operating Conditions for Stratix V GX, GS, and GT | Devices |

|-------------------------------------------------------------------------------------------------|---------|

| (Part 2 of 2)                                                                                   |         |

Notes toTable 7.

(1) This supply must be connected to 3.0tl/eifCMU PLL, receiver CDR, or both, antegoured at a base data rate > 6.5 Gbpstol@p5 Gbps, you can connect this supply either 3.0 V or 2.5 V.

(2) Refer to Table & select the correct powseupply level for your design.

(3) When using ATX PLLs, the supply must be 3.0 V.

(4) This value describes the budget for the static) power supply tolerance and does include the dynaic tolerance requiments. Refer to the PDN tool for the additial budget for the dynamic tolerance requirements.

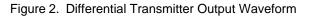

Figure 2 shows the differential transmitter output waveform.

Figure 3 shows the Stratix V AC gain curves for GX channels.

Figure 3. AC Gain Curves for GX Channels (full bandwidth)

Stratix V GT devices contain both GX and GT channels. All transceiver specifications for the GX channels not listed in Table 28 are the same as those listed inTable 23

Table 28 lists the Stratix V GT transceiver specifications.

Table 50 lists the timing parameters for Strati x V devices for FPP configuration when the DCLK-to-DATA[] ratio is 1.

Table 50. FPP Timing Parameters for Stratix V Devides

| Symbol                            | Parameter                                           | Minimum                                                         | Maximum             | Units |

|-----------------------------------|-----------------------------------------------------|-----------------------------------------------------------------|---------------------|-------|

| t <sub>CF2CD</sub>                | nCONFIGIow toCONF_DONEow                            | —                                                               | 600                 | ns    |

| t <sub>CF2ST0</sub>               | nCONFIGIow tonSTATUSIow                             | —                                                               | 600                 | ns    |

| t <sub>CFG</sub>                  | nCONFIGIow pulse width                              | 2                                                               |                     | μs    |

| t <sub>STATUS</sub>               | nSTATUSIow pulse width                              | 268                                                             | 1,50%               | μs    |

| t <sub>CF2ST1</sub>               | nCONFIGhigh tonSTATUShigh                           | —                                                               | 1,506 <sup>3)</sup> | μs    |

| t <sub>CF2CK</sub> <sup>(6)</sup> | nCONFIGhigh to first rising edge @CLK               | 1,506                                                           | _                   | μs    |

| t <sub>ST2CK</sub> <sup>(6)</sup> | nSTATUShigh to first rising edge D/CLK              | 2                                                               | _                   | μs    |

| t <sub>DSU</sub>                  | DATA[] setup time before rising edge DOLK           | 5.5                                                             | _                   | ns    |

| t <sub>DH</sub>                   | DATA[] hold time after rising edge DCLK             | 0                                                               | _                   | ns    |

| t <sub>CH</sub>                   | DCLKhigh time                                       | 0.45 1/f <sub>MAX</sub>                                         | _                   | S     |

| t <sub>CL</sub>                   | DCLKlow time                                        | 0.45 1/f <sub>MAX</sub>                                         | _                   | S     |

| t <sub>CLK</sub>                  | DCLK period                                         | 1/f <sub>MAX</sub>                                              | _                   | S     |

| 4                                 | DCLKfrequency (FP₽8/×16)                            | —                                                               | 125                 | MHz   |

| f <sub>MAX</sub>                  | DCLKfrequency (FPR32)                               | —                                                               | 100                 | MHz   |

| t <sub>CD2UM</sub>                | CONF_DON <b>E</b> igh to user mode <sup>4)</sup>    | 175                                                             | 437                 | μs    |

| t <sub>CD2CU</sub>                | CONF_DON <b>E</b> igh toCLKUSRenabled<br>DCLKperiod |                                                                 |                     |       |

| t <sub>CD2UMC</sub>               | CONF_DONE igh to user mode wit CLKUSR option on     | t <sub>CD2CU</sub> +<br>(8576× CLKUSR<br>period) <sup>(5)</sup> |                     |       |

Notes toTable 50

(1) Use these timing parameters wither decompressional design security features are disabled.

(2) This value is applicable if younded delay configuration by extending rt6@NFIG or nSTATUS low pulse width.

(3) This value is applicable if you do ndayle on figuration by externally holding the ATUS low.

(4) The minimum and maximum numbers apply ionyou chose the internaticillator as the clock source for initializing the dieve.

(5) To enable the LKUSRpin as the initialization or k source and to obtain the maximum frequespecification on these pins, refer to the Initialization section of the Onfiguration, sign Security, and Remote System grades in Stratix V Devices appendix of the Onfiguration of the Onfiguratic of the Onfiguratic

(6) If nSTATUS is monitored, follow the  $t_{2CK}$  specification. In STATUS is not monitored, follow the  $t_{2CK}$  specification.

# FPP Configuration Timing when DCLK-to-DATA [] > 1

Figure 13 shows the timing waveform for FPP configuration when using a MAX II device, MAX V device, or microprocessor as an external host. This waveform shows timing when the DCLKto-DATA[] ratio is more than 1.

Page 58

| Letter | Subject              | Definitions                                                                                                                                                      |

|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | V <sub>CM(DC)</sub>  | DC common mode input voltage.                                                                                                                                    |

|        | V <sub>ICM</sub>     | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                            |

|        | V <sub>ID</sub>      | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.     |

|        | V <sub>DIF(AC)</sub> | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                      |

|        | V <sub>DIF(DC)</sub> | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                     |

|        | V <sub>IH</sub>      | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                            |

|        | V <sub>IH(AC)</sub>  | High-level AC input voltage                                                                                                                                      |

|        | V <sub>IH(DC)</sub>  | High-level DC input voltage                                                                                                                                      |

| V      | V <sub>IL</sub>      | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                              |

|        | V <sub>IL(AC)</sub>  | Low-level AC input voltage                                                                                                                                       |

|        | V <sub>IL(DC)</sub>  | Low-level DC input voltage                                                                                                                                       |

|        | V <sub>OCM</sub>     | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                        |

|        | V <sub>OD</sub>      | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. |

|        | V <sub>SWING</sub>   | Differential input voltage                                                                                                                                       |

|        | V <sub>X</sub>       | Input differential cross point voltage                                                                                                                           |

|        | V <sub>OX</sub>      | Output differential cross point voltage                                                                                                                          |

| W      | W                    | High-speed I/O block—clock boost factor                                                                                                                          |

| Х      |                      |                                                                                                                                                                  |

| Y      | —                    | _                                                                                                                                                                |

| Ζ      |                      |                                                                                                                                                                  |

## Table 60. Glossary (Part 4 of 4)

# **Document Revision History**

Table 61 lists the revision history for this chapter.

Table 61. Document Revision History (Part 1 of 3)

| Date          | Version | Changes                                                                                                                                                                          |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2018     | 3.9     | Added the "Stratix V Device Overshoot Duration" figure.                                                                                                                          |

|               |         | Added a footnote to the "High-Speed I/O Specifications for Stratix V Devices" table.<br>Changed the minimum value for the "PS Timing Parameters for Stratix V<br>Devices" table. |

|               |         | Changed the condition for $1\Omega O R_D$ in the "OCT Without Calibration Resistance Tolerance Specifications for Stratix V Devices" table.                                      |

| April 2017    | 3.8     | Changed the minimum value $\log_{2UM}$ in the "AS Timing Parameters for AS ´1 and AS ´4 Configurations in Stratix V Devices" table                                               |

|               |         | Changed the minimum value $t_{M_2}$ to the "FPP Timing Parameters for Stratix V Devices When the DCLK-to-DATA[] Ratio is >1" table.                                              |

|               |         | Changed the minimum value $t_{M_2}$ to the "FPP Timing Parameters for Stratix V Devices When the DCLK-to-DATA[] Ratio is >1" table.                                              |

|               |         | Changed the minimum number of clock cycles value in the "Initialization Clock Spurce Option and the Maximum Frequency" table.                                                    |

| lupa 2016     | 2.7     | Added the M minimum specification for LVPECL in the "Differential I/O Standard Specifications for Stratix V Devices" table                                                       |

| June 2016     | 3.7     | Added thed <sub>UT</sub> specification to the "Absolute Maximum Ratings for Stratix V Devices" table.                                                                            |

| December 2015 | 3.6     | Added a footnote to the "High-Speed I/O Specifications for Stratix V Devices" table.                                                                                             |

| December 2015 | 3.5     | Changed the transmitter, receiver, and ATX PLL data rate specifications in the<br>"Transceiver Specifications for Stratix V GX and GS Devices" table.                            |

| December 2015 | 3.5     | Changed the configuration .rbf sizes in the "Uncompressed .rbf Sizes for Stratix V Devices" table.                                                                               |

|               |         | Changed the data rate specification for transceiver speed grade 3 in the following tables                                                                                        |

|               |         | "Transceiver Specifications for Stratix V GX and GS Devices"                                                                                                                     |

|               |         | "Stratix V Standard PCS Approximate Maximum Date Rate"                                                                                                                           |

|               |         | "Stratix V 10G PCS Approximate Maximum Data Rate"                                                                                                                                |

| July 2015     | 3.4     | Changed the conditions for reference clock rise and fall time, and added a note to the<br>"Transceiver Specifications for Stratix V GX and GS Devices" table.                    |

|               |         | Added a note to the "Minimum differential eye opening at receiver serial input pins" specification in the "Transceiver Specifications for Stratix V GX and GS Devices" table.    |

|               |         | Changed theூt maximum value in the "AS Timing Parameters for AS ´1 and AS ´4<br>Configurations in Stratix V Devices" table.                                                      |

|               |         | Removed the CDR ppm tolerance specification from the "Transceiver Specifications for Stratix V GX and GS Devices" table.                                                         |