Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 234720                                                      |

| Number of Logic Elements/Cells | 622000                                                      |

| Total RAM Bits                 | 51200000                                                    |

| Number of I/O                  | 840                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 0.82V ~ 0.88V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 1932-BBGA, FCBGA                                            |

| Supplier Device Package        | 1932-FBGA, FC (45x45)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5sgxma7n2f45i2ln |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Page 10 Electrical Characteristics

Table 11. OCT Calibration Accuracy Specifications for Stratix V Devices (1) (Part 2 of 2)

|                                                                                                                                            |                                                                                                                                        |                                                  |            | Calibratio | n Accuracy     |            |      |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|------------|----------------|------------|------|

| Symbol                                                                                                                                     | Description                                                                                                                            | Conditions                                       | C1         | C2,I2      | C3,I3,<br>I3YY | C4,I4      | Unit |

| 50-Ω R <sub>S</sub>                                                                                                                        | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5,<br>1.8, 1.5, 1.2 V | ±15        | ±15        | ±15            | ±15        | %    |

| $34\text{-}\Omega$ and $40\text{-}\Omega$ $R_S$                                                                                            | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   | V <sub>CCIO</sub> = 1.5, 1.35,<br>1.25, 1.2 V    | ±15        | ±15        | ±15            | ±15        | %    |

| $48$ - $\Omega$ , $60$ - $\Omega$ , $80$ - $\Omega$ , and $240$ - $\Omega$ R <sub>S</sub>                                                  | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)                  | V <sub>CCIO</sub> = 1.2 V                        | ±15        | ±15        | ±15            | ±15        | %    |

| 50-Ω R <sub>T</sub>                                                                                                                        | Internal parallel termination with calibration (50-Ω setting)                                                                          | V <sub>CCIO</sub> = 2.5, 1.8,<br>1.5, 1.2 V      | -10 to +40 | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| $\begin{array}{c} 20\text{-}\Omega,30\text{-}\Omega,\\ 40\text{-}\Omega,60\text{-}\Omega,\\ \text{and}\\ 120\text{-}\OmegaR_T \end{array}$ | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35,<br>1.25 V         | -10 to +40 | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| 60- $\Omega$ and 120- $\Omega$ R <sub>T</sub>                                                                                              | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | V <sub>CCIO</sub> = 1.2                          | -10 to +40 | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| $\begin{array}{c} \textbf{25-}\Omega \\ \textbf{R}_{S\_left\_shift} \end{array}$                                                           | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                               | V <sub>CCIO</sub> = 3.0, 2.5,<br>1.8, 1.5, 1.2 V | ±15        | ±15        | ±15            | ±15        | %    |

### Note to Table 11:

Table 12 lists the Stratix V OCT without calibration resistance tolerance to PVT changes.

Table 12. OCT Without Calibration Resistance Tolerance Specifications for Stratix V Devices (Part 1 of 2)

|                             |                                                                        |                                   | Resistance Tolerance |       |                 |        |      |  |

|-----------------------------|------------------------------------------------------------------------|-----------------------------------|----------------------|-------|-----------------|--------|------|--|

| Symbol                      | Description                                                            | Conditions                        | C1                   | C2,I2 | C3, I3,<br>I3YY | C4, I4 | Unit |  |

| 25-Ω R, 50-Ω R <sub>S</sub> | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0 and 2.5 V | ±30                  | ±30   | ±40             | ±40    | %    |  |

| 25-Ω R <sub>S</sub>         | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 and 1.5 V | ±30                  | ±30   | ±40             | ±40    | %    |  |

| 25-Ω R <sub>S</sub>         | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2 V         | ±35                  | ±35   | ±50             | ±50    | %    |  |

<sup>(1)</sup> OCT calibration accuracy is valid at the time of calibration only.

Page 18 Switching Characteristics

## **Switching Characteristics**

This section provides performance characteristics of the Stratix V core and periphery blocks.

These characteristics can be designated as Preliminary or Final.

- Preliminary characteristics are created using simulation results, process data, and other known parameters. The title of these tables show the designation as "Preliminary."

- Final numbers are based on actual silicon characterization and testing. The numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions. There are no designations on finalized tables.

## **Transceiver Performance Specifications**

This section describes transceiver performance specifications.

Table 23 lists the Stratix V GX and GS transceiver specifications.

Table 23. Transceiver Specifications for Stratix V GX and GS Devices (1) (Part 1 of 7)

| Symbol/                                                        | Conditions                                                        | Trai  | nsceive<br>Grade                                     | r Speed<br>1 | Trar     | sceive<br>Grade | r Speed<br>2      | Transceiver Speed<br>Grade 3 |         |            | Unit    |

|----------------------------------------------------------------|-------------------------------------------------------------------|-------|------------------------------------------------------|--------------|----------|-----------------|-------------------|------------------------------|---------|------------|---------|

| Description                                                    |                                                                   | Min   | Тур                                                  | Max          | Min      | Тур             | Max               | Min                          | Тур     | Max        |         |

| Reference Clock                                                |                                                                   |       |                                                      |              |          |                 |                   |                              |         |            |         |

| Supported I/O<br>Standards                                     | Dedicated<br>reference<br>clock pin                               | 1.2-V | PCML,                                                | 1.4-V PCM    | L, 1.5-V |                 | 2.5-V PCM<br>HCSL | IL, Diffe                    | rential | LVPECL, L\ | DS, and |

| Sidiludius                                                     | RX reference clock pin                                            |       | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |              |          |                 |                   |                              |         |            |         |

| Input Reference<br>Clock Frequency<br>(CMU PLL) (8)            | _                                                                 | 40    | —                                                    | 710          | 40       |                 | 710               | 40                           | _       | 710        | MHz     |

| Input Reference<br>Clock Frequency<br>(ATX PLL) <sup>(8)</sup> | _                                                                 | 100   |                                                      | 710          | 100      |                 | 710               | 100                          | _       | 710        | MHz     |

| Rise time                                                      | Measure at<br>±60 mV of<br>differential<br>signal <sup>(26)</sup> | _     | _                                                    | 400          | _        |                 | 400               | _                            | _       | 400        | ne      |

| Fall time                                                      | Measure at<br>±60 mV of<br>differential<br>signal <sup>(26)</sup> | —     | —                                                    | 400          | _        | _               | 400               | _                            | _       | 400        | ps      |

| Duty cycle                                                     | _                                                                 | 45    | _                                                    | 55           | 45       | _               | 55                | 45                           | _       | 55         | %       |

| Spread-spectrum<br>modulating clock<br>frequency               | PCI Express®<br>(PCIe®)                                           | 30    | _                                                    | 33           | 30       |                 | 33                | 30                           | _       | 33         | kHz     |

Page 20 Switching Characteristics

Table 23. Transceiver Specifications for Stratix V GX and GS Devices  $^{(1)}$  (Part 3 of 7)

| Symbol/                                                                                                                      | Conditions                                                                  | Trai | nsceive<br>Grade | r Speed<br>1 | Trai     | nsceive<br>Grade | r Speed<br>2 | Transceiver Speed<br>Grade 3 |         |                          | Unit |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------------------|--------------|----------|------------------|--------------|------------------------------|---------|--------------------------|------|

| Description                                                                                                                  |                                                                             | Min  | Тур              | Max          | Min      | Тур              | Max          | Min                          | Тур     | Max                      |      |

| Reconfiguration clock (mgmt_clk_clk) frequency                                                                               | _                                                                           | 100  | _                | 125          | 100      | _                | 125          | 100                          | _       | 125                      | MHz  |

| Receiver                                                                                                                     |                                                                             |      |                  |              |          |                  |              |                              |         |                          |      |

| Supported I/O<br>Standards                                                                                                   | _                                                                           |      |                  | 1.4-V PCMI   | L, 1.5-V | PCML,            | 2.5-V PCM    | L, LVPE                      | CL, and | d LVDS                   |      |

| Data rate<br>(Standard PCS)                                                                                                  | _                                                                           | 600  | _                | 12200        | 600      | _                | 12200        | 600                          | _       | 8500/<br>10312.5<br>(24) | Mbps |

| Data rate<br>(10G PCS) (9), (23)                                                                                             | _                                                                           | 600  | _                | 14100        | 600      | _                | 12500        | 600                          | _       | 8500/<br>10312.5<br>(24) | Mbps |

| Absolute V <sub>MAX</sub> for a receiver pin <sup>(5)</sup>                                                                  | _                                                                           | _    | _                | 1.2          | _        | _                | 1.2          | _                            | _       | 1.2                      | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                                 | _                                                                           | -0.4 | _                | _            | -0.4     | _                | _            | -0.4                         | _       | _                        | V    |

| Maximum peak-<br>to-peak<br>differential input<br>voltage V <sub>ID</sub> (diff p-<br>p) before device<br>configuration (22) | _                                                                           | _    | _                | 1.6          | _        | _                | 1.6          | _                            | _       | 1.6                      | V    |

| Maximum peak-                                                                                                                | $V_{CCR\_GXB} = 1.0 \text{ V}/1.05 \text{ V} $ $(V_{ICM} = 0.70 \text{ V})$ | _    | _                | 2.0          | _        | _                | 2.0          | _                            | _       | 2.0                      | V    |

| differential input<br>voltage V <sub>ID</sub> (diff p-<br>p) after device                                                    | $V_{CCR\_GXB} = 0.90 \text{ V}$ $(V_{ICM} = 0.6 \text{ V})$                 |      | _                | 2.4          | _        | _                | 2.4          | _                            | _       | 2.4                      | V    |

| configuration <sup>(18)</sup> , (22)                                                                                         | $V_{CCR\_GXB} = 0.85 \text{ V}$ $(V_{ICM} = 0.6 \text{ V})$                 | _    | _                | 2.4          | _        | _                | 2.4          | _                            | _       | 2.4                      | V    |

| Minimum differential eye opening at receiver serial input pins (6), (22), (27)                                               | _                                                                           | 85   | _                | _            | 85       | _                | _            | 85                           | _       | _                        | mV   |

Page 22 Switching Characteristics

Table 23. Transceiver Specifications for Stratix V GX and GS Devices (1) (Part 5 of 7)

| Symbol/                                                               | Conditions                                        | Tra | nsceive<br>Grade | r Speed<br>1 | Trai | nsceive<br>Grade | r Speed<br>2 | Trai | sceive<br>Grade | r Speed<br>e 3           | Unit |

|-----------------------------------------------------------------------|---------------------------------------------------|-----|------------------|--------------|------|------------------|--------------|------|-----------------|--------------------------|------|

| Description                                                           |                                                   | Min | Тур              | Max          | Min  | Тур              | Max          | Min  | Тур             | Max                      |      |

|                                                                       | DC Gain<br>Setting = 0                            |     | 0                | _            | _    | 0                |              | _    | 0               | _                        | dB   |

|                                                                       | DC Gain<br>Setting = 1                            |     | 2                | _            | _    | 2                |              | _    | 2               | _                        | dB   |

| Programmable<br>DC gain                                               | DC Gain<br>Setting = 2                            |     | 4                | _            |      | 4                | _            | _    | 4               | _                        | dB   |

|                                                                       | DC Gain<br>Setting = 3                            | _   | 6                | _            | _    | 6                | _            | _    | 6               | _                        | dB   |

|                                                                       | DC Gain<br>Setting = 4                            | _   | 8                | _            | _    | 8                | _            | _    | 8               | _                        | dB   |

| Transmitter                                                           |                                                   |     |                  |              |      |                  |              |      |                 |                          |      |

| Supported I/O<br>Standards                                            | _                                                 |     |                  |              | -    | 1.4-V an         | ıd 1.5-V PC  | ML   |                 |                          |      |

| Data rate<br>(Standard PCS)                                           | _                                                 | 600 | _                | 12200        | 600  | _                | 12200        | 600  | _               | 8500/<br>10312.5<br>(24) | Mbps |

| Data rate<br>(10G PCS)                                                | _                                                 | 600 | _                | 14100        | 600  | _                | 12500        | 600  | _               | 8500/<br>10312.5<br>(24) | Mbps |

|                                                                       | 85- $\Omega$ setting                              |     | 85 ±<br>20%      | _            | _    | 85 ± 20%         | _            | _    | 85 ± 20%        | _                        | Ω    |

| Differential on-                                                      | 100-Ω<br>setting                                  |     | 100<br>±<br>20%  | _            | _    | 100<br>±<br>20%  | _            | _    | 100<br>±<br>20% | _                        | Ω    |

| chip termination resistors                                            | 120-Ω<br>setting                                  | _   | 120<br>±<br>20%  | _            | _    | 120<br>±<br>20%  | _            | _    | 120<br>±<br>20% | _                        | Ω    |

|                                                                       | 150-Ω<br>setting                                  |     | 150<br>±<br>20%  | _            | _    | 150<br>±<br>20%  | _            | _    | 150<br>±<br>20% | _                        | Ω    |

| V <sub>OCM</sub> (AC coupled)                                         | 0.65-V<br>setting                                 | _   | 650              | _            | _    | 650              | _            | _    | 650             | _                        | mV   |

| V <sub>OCM</sub> (DC<br>coupled)                                      | _                                                 |     | 650              | _            | _    | 650              | _            | _    | 650             | _                        | mV   |

| Rise time (7)                                                         | 20% to 80%                                        | 30  | _                | 160          | 30   | _                | 160          | 30   | _               | 160                      | ps   |

| Fall time <sup>(7)</sup>                                              | 80% to 20%                                        | 30  | _                | 160          | 30   | _                | 160          | 30   |                 | 160                      | ps   |

| Intra-differential<br>pair skew                                       | Tx V <sub>CM</sub> = 0.5 V and slew rate of 15 ps | _   | _                | 15           | _    | _                | 15           | _    | _               | 15                       | ps   |

| Intra-transceiver<br>block transmitter<br>channel-to-<br>channel skew | x6 PMA<br>bonded mode                             | _   | _                | 120          | _    | _                | 120          | _    | _               | 120                      | ps   |

Table 23. Transceiver Specifications for Stratix V GX and GS Devices (1) (Part 6 of 7)

| Symbol/                                                               | Conditions                                   | Trai | nsceive<br>Grade | r Speed<br>e 1                | Trar | sceive<br>Grade | r Speed<br>2                  | Tran | sceive<br>Grade | er Speed<br>e 3               | Unit |

|-----------------------------------------------------------------------|----------------------------------------------|------|------------------|-------------------------------|------|-----------------|-------------------------------|------|-----------------|-------------------------------|------|

| Description                                                           |                                              | Min  | Тур              | Max                           | Min  | Тур             | Max                           | Min  | Тур             | Max                           |      |

| Inter-transceiver<br>block transmitter<br>channel-to-<br>channel skew | xN PMA<br>bonded mode                        | ı    | ı                | 500                           | _    | ı               | 500                           | _    | _               | 500                           | ps   |

| CMU PLL                                                               |                                              |      |                  |                               |      |                 |                               |      |                 |                               |      |

| Supported Data<br>Range                                               | _                                            | 600  | _                | 12500                         | 600  | _               | 12500                         | 600  | _               | 8500/<br>10312.5<br>(24)      | Mbps |

| t <sub>pll_powerdown</sub> (15)                                       | _                                            | 1    | _                | _                             | 1    | _               | _                             | 1    | _               | _                             | μs   |

| t <sub>pll_lock</sub> (16)                                            | _                                            | _    | _                | 10                            | _    | _               | 10                            | _    | _               | 10                            | μs   |

| ATX PLL                                                               |                                              |      |                  |                               |      |                 |                               |      |                 |                               |      |

|                                                                       | VCO<br>post-divider<br>L=2                   | 8000 | _                | 14100                         | 8000 | _               | 12500                         | 8000 | _               | 8500/<br>10312.5<br>(24)      | Mbps |

| Currented Date                                                        | L=4                                          | 4000 | _                | 7050                          | 4000 | _               | 6600                          | 4000 |                 | 6600                          | Mbps |

| Supported Data<br>Rate Range                                          | L=8                                          | 2000 | _                | 3525                          | 2000 | _               | 3300                          | 2000 | _               | 3300                          | Mbps |

| Ç                                                                     | L=8,<br>Local/Central<br>Clock Divider<br>=2 | 1000 | _                | 1762.5                        | 1000 | _               | 1762.5                        | 1000 | _               | 1762.5                        | Mbps |

| t <sub>pll_powerdown</sub> (15)                                       | _                                            | 1    | _                | _                             | 1    | _               | _                             | 1    | _               | _                             | μs   |

| t <sub>pll_lock</sub> (16)                                            | _                                            |      |                  | 10                            | _    |                 | 10                            | _    |                 | 10                            | μs   |

| fPLL                                                                  |                                              |      |                  |                               |      |                 |                               |      |                 |                               |      |

| Supported Data<br>Range                                               | _                                            | 600  | _                | 3250/<br>3125 <sup>(25)</sup> | 600  | _               | 3250/<br>3125 <sup>(25)</sup> | 600  | _               | 3250/<br>3125 <sup>(25)</sup> | Mbps |

| t <sub>pll_powerdown</sub> (15)                                       | _                                            | 1    | _                | _                             | 1    | _               | _                             | 1    | _               |                               | μs   |

Page 24 Switching Characteristics

Table 23. Transceiver Specifications for Stratix V GX and GS Devices (1) (Part 7 of 7)

| Symbol/<br>Description     | Conditions | Transceiver Speed<br>Grade 1 |     | Transceiver Speed<br>Grade 2 |     |     | Transceiver Speed<br>Grade 3 |     |     | Unit |    |

|----------------------------|------------|------------------------------|-----|------------------------------|-----|-----|------------------------------|-----|-----|------|----|

| Description                |            | Min                          | Тур | Max                          | Min | Тур | Max                          | Min | Тур | Max  |    |

| t <sub>pll_lock</sub> (16) | _          | _                            | _   | 10                           | _   | _   | 10                           | _   | _   | 10   | μs |

### Notes to Table 23:

- (1) Speed grades shown in Table 23 refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Stratix V Device Overview*.

- (2) The reference clock common mode voltage is equal to the  $V_{CCR\_GXB}$  power supply level.

- (3) This supply must be connected to 1.0 V if the transceiver is configured at a data rate > 6.5 Gbps, and to 1.05 V if configured at a data rate > 10.3 Gbps when DFE is used. For data rates up to 6.5 Gbps, you can connect this supply to 0.85 V.

- (4) This supply follows VCCR\_GXB.

- (5) The device cannot tolerate prolonged operation at this absolute maximum.

- (6) The differential eye opening specification at the receiver input pins assumes that **Receiver Equalization** is disabled. If you enable **Receiver Equalization**, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

- (7) The Quartus II software automatically selects the appropriate slew rate depending on the configured data rate or functional mode.

- (8) The input reference clock frequency options depend on the data rate and the device speed grade.

- (9) The line data rate may be limited by PCS-FPGA interface speed grade.

- (10) Refer to Figure 1 for the GX channel AC gain curves. The total effective AC gain is the AC gain minus the DC gain.

- (11) t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

- (12) t<sub>I TD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

- (13) t<sub>LTD\_manual</sub> is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

- (14) t<sub>LTR\_LTD\_manual</sub> is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

- (15)  $t_{pll\ powerdown}$  is the PLL powerdown minimum pulse width.

- (16) t<sub>nll lock</sub> is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

- (17) To calculate the REFCLK rms phase jitter requirement for PCle at reference clock frequencies other than 100 MHz, use the following formula: REFCLK rms phase jitter at f(MHz) = REFCLK rms phase jitter at 100 MHz × 100/f.

- (18) The maximum peak to peak differential input voltage V<sub>ID</sub> after device configuration is equal to 4 × (absolute V<sub>MAX</sub> for receiver pin V<sub>ICM</sub>).

- (19) For ES devices,  $R_{REF}$  is 2000  $\Omega$  ±1%.

- (20) To calculate the REFCLK phase noise requirement at frequencies other than 622 MHz, use the following formula: REFCLK phase noise at f(MHz) = REFCLK phase noise at 622 MHz + 20\*log(f/622).

- (21) SFP/+ optical modules require the host interface to have RD+/- differentially terminated with 100 Ω. The internal OCT feature is available after the Stratix V FPGA configuration is completed. Altera recommends that FPGA configuration is completed before inserting the optical module. Otherwise, minimize unnecessary removal and insertion with unconfigured devices.

- (22) Refer to Figure 2.

- (23) For oversampling designs to support data rates less than the minimum specification, the CDR needs to be in LTR mode only.

- (24) I3YY devices can achieve data rates up to 10.3125 Gbps.

- (25) When you use fPLL as a TXPLL of the transceiver.

- (26) REFCLK performance requires to meet transmitter REFCLK phase noise specification.

- (27) Minimum eye opening of 85 mV is only for the unstressed input eye condition.

Page 26 Switching Characteristics

Table 25 shows the approximate maximum data rate using the standard PCS.

Table 25. Stratix V Standard PCS Approximate Maximum Date Rate (1), (3)

| Made (2)            | Transceiver                           | PMA Width                                | 20      | 20      | 16      | 16      | 10  | 10  | 8    | 8    |

|---------------------|---------------------------------------|------------------------------------------|---------|---------|---------|---------|-----|-----|------|------|

| Mode <sup>(2)</sup> | Speed Grade                           | PCS/Core Width                           | 40      | 20      | 32      | 16      | 20  | 10  | 16   | 8    |

|                     | 1                                     | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.5 | 5.8 | 5.2  | 4.72 |

|                     | 2                                     | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.5 | 5.8 | 5.2  | 4.72 |

|                     |                                       | C3, I3, I3L<br>core speed grade          | 9.8     | 9.0     | 7.84    | 7.2     | 5.3 | 4.7 | 4.24 | 3.76 |

| FIFO                | C1, C2, C2L, I2, I2L core speed grade | 8.5                                      | 8.5     | 8.5     | 8.5     | 6.5     | 5.8 | 5.2 | 4.72 |      |

|                     | 3                                     | I3YY<br>core speed grade                 | 10.3125 | 10.3125 | 7.84    | 7.2     | 5.3 | 4.7 | 4.24 | 3.76 |

|                     |                                       | C3, I3, I3L<br>core speed grade          | 8.5     | 8.5     | 7.84    | 7.2     | 5.3 | 4.7 | 4.24 | 3.76 |

|                     |                                       | C4, I4<br>core speed grade               | 8.5     | 8.2     | 7.04    | 6.56    | 4.8 | 4.2 | 3.84 | 3.44 |

|                     | 1                                     | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.1 | 5.7 | 4.88 | 4.56 |

|                     | 2                                     | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.1 | 5.7 | 4.88 | 4.56 |

|                     | 2                                     | C3, I3, I3L<br>core speed grade          | 9.8     | 9.0     | 7.92    | 7.2     | 4.9 | 4.5 | 3.96 | 3.6  |

| Register            |                                       | C1, C2, C2L, I2, I2L<br>core speed grade | 10.3125 | 10.3125 | 10.3125 | 10.3125 | 6.1 | 5.7 | 4.88 | 4.56 |

|                     | 3                                     | I3YY<br>core speed grade                 | 10.3125 | 10.3125 | 7.92    | 7.2     | 4.9 | 4.5 | 3.96 | 3.6  |

|                     |                                       | C3, I3, I3L<br>core speed grade          | 8.5     | 8.5     | 7.92    | 7.2     | 4.9 | 4.5 | 3.96 | 3.6  |

|                     |                                       | C4, I4<br>core speed grade               | 8.5     | 8.2     | 7.04    | 6.56    | 4.4 | 4.1 | 3.52 | 3.28 |

### Notes to Table 25:

<sup>(1)</sup> The maximum data rate is in Gbps.

<sup>(2)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

<sup>(3)</sup> The maximum data rate is also constrained by the transceiver speed grade. Refer to Table 1 for the transceiver speed grade.

Table 26 shows the approximate maximum data rate using the 10G PCS.

Table 26. Stratix V 10G PCS Approximate Maximum Data Rate (1)

| Mode (2)                           | Transceiver | PMA Width                                | 64       | 40    | 40    | 40   | 32       | 32    |

|------------------------------------|-------------|------------------------------------------|----------|-------|-------|------|----------|-------|

| Widue (2)                          | Speed Grade | PCS Width                                | 64       | 66/67 | 50    | 40   | 64/66/67 | 32    |

|                                    | 1           | C1, C2, C2L, I2, I2L<br>core speed grade | 14.1     | 14.1  | 10.69 | 14.1 | 13.6     | 13.6  |

|                                    | 2           | C1, C2, C2L, I2, I2L<br>core speed grade | 12.5     | 12.5  | 10.69 | 12.5 | 12.5     | 12.5  |

|                                    | 2           | C3, I3, I3L<br>core speed grade          | 12.5     | 12.5  | 10.69 | 12.5 | 10.88    | 10.88 |

| FIFO or<br>Register                |             | C1, C2, C2L, I2, I2L<br>core speed grade | 8.5 Gbps |       |       |      |          |       |

|                                    | 3           | C3, I3, I3L<br>core speed grade          |          |       |       |      |          |       |

|                                    | 3           | C4, I4<br>core speed grade               |          |       |       |      |          |       |

| 13YY core speed grade 10.3125 Gbps |             |                                          |          |       |       |      |          |       |

### Notes to Table 26:

<sup>(1)</sup> The maximum data rate is in Gbps.

<sup>(2)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

Page 28 Switching Characteristics

Table 27 shows the  $\ensuremath{V_{OD}}$  settings for the GX channel.

Table 27. Typical V $_{\text{OD}}$  Setting for GX Channel, TX Termination = 100  $\Omega$   $^{(2)}$

| Symbol                                | V <sub>OD</sub> Setting | V <sub>op</sub> Value<br>(mV) | V <sub>op</sub> Setting | V <sub>op</sub> Value<br>(mV) |

|---------------------------------------|-------------------------|-------------------------------|-------------------------|-------------------------------|

|                                       | 0 (1)                   | 0                             | 32                      | 640                           |

|                                       | 1 (1)                   | 20                            | 33                      | 660                           |

|                                       | 2 (1)                   | 40                            | 34                      | 680                           |

|                                       | 3 (1)                   | 60                            | 35                      | 700                           |

|                                       | 4 (1)                   | 80                            | 36                      | 720                           |

|                                       | 5 <sup>(1)</sup>        | 100                           | 37                      | 740                           |

|                                       | 6                       | 120                           | 38                      | 760                           |

|                                       | 7                       | 140                           | 39                      | 780                           |

|                                       | 8                       | 160                           | 40                      | 800                           |

|                                       | 9                       | 180                           | 41                      | 820                           |

|                                       | 10                      | 200                           | 42                      | 840                           |

|                                       | 11                      | 220                           | 43                      | 860                           |

|                                       | 12                      | 240                           | 44                      | 880                           |

|                                       | 13                      | 260                           | 45                      | 900                           |

|                                       | 14                      | 280                           | 46                      | 920                           |

| <b>V</b> op differential peak to peak | 15                      | 300                           | 47                      | 940                           |

| typical <sup>(3)</sup>                | 16                      | 320                           | 48                      | 960                           |

|                                       | 17                      | 340                           | 49                      | 980                           |

|                                       | 18                      | 360                           | 50                      | 1000                          |

|                                       | 19                      | 380                           | 51                      | 1020                          |

|                                       | 20                      | 400                           | 52                      | 1040                          |

|                                       | 21                      | 420                           | 53                      | 1060                          |

|                                       | 22                      | 440                           | 54                      | 1080                          |

|                                       | 23                      | 460                           | 55                      | 1100                          |

|                                       | 24                      | 480                           | 56                      | 1120                          |

|                                       | 25                      | 500                           | 57                      | 1140                          |

|                                       | 26                      | 520                           | 58                      | 1160                          |

|                                       | 27                      | 540                           | 59                      | 1180                          |

|                                       | 28                      | 560                           | 60                      | 1200                          |

|                                       | 29                      | 580                           | 61                      | 1220                          |

|                                       | 30                      | 600                           | 62                      | 1240                          |

|                                       | 31                      | 620                           | 63                      | 1260                          |

### Note to Table 27:

- (1) If TX termination resistance =  $100\Omega$ , this VOD setting is illegal.

- (2) The tolerance is +/-20% for all VOD settings except for settings 2 and below.

- (3) Refer to Figure 2.

Page 34 Switching Characteristics

Table 28. Transceiver Specifications for Stratix V GT Devices (Part 5 of 5) (1)

| Symbol/                    | Conditions | Transceiver<br>Speed Grade 2 |     |     | T<br>Sp | Unit |     |    |

|----------------------------|------------|------------------------------|-----|-----|---------|------|-----|----|

| Description                |            | Min                          | Тур | Max | Min     | Тур  | Max |    |

| t <sub>pll_lock</sub> (14) | _          | _                            | _   | 10  | _       | _    | 10  | μs |

### Notes to Table 28:

- (1) Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Stratix V Device Overview*.

- (2) The reference clock common mode voltage is equal to the VCCR\_GXB power supply level.

- (3) The device cannot tolerate prolonged operation at this absolute maximum.

- (4) The differential eye opening specification at the receiver input pins assumes that receiver equalization is disabled. If you enable receiver equalization, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

- (5) Refer to Figure 5 for the GT channel AC gain curves. The total effective AC gain is the AC gain minus the DC gain.

- (6) Refer to Figure 6 for the GT channel DC gain curves.

- (7) CFP2 optical modules require the host interface to have the receiver data pins differentially terminated with 100 Ω. The internal OCT feature is available after the Stratix V FPGA configuration is completed. Altera recommends that FPGA configuration is completed before inserting the optical module. Otherwise, minimize unnecessary removal and insertion with unconfigured devices.

- (8) Specifications for this parameter are the same as for Stratix V GX and GS devices. See Table 23 for specifications.

- (9) t<sub>LTB</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

- (10) tLTD is time required for the receiver CDR to start recovering valid data after the rx is lockedtodata signal goes high.

- (11) t<sub>LTD\_manual</sub> is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

- (12) t<sub>LTR\_LTD\_manual</sub> is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

- (13) tpll powerdown is the PLL powerdown minimum pulse width.

- (14) tpll lock is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

- (15) To calculate the REFCLK rms phase jitter requirement for PCle at reference clock frequencies other than 100 MHz, use the following formula: REFCLK rms phase jitter at f(MHz) = REFCLK rms phase jitter at 100 MHz × 100/f.

- (16) The maximum peak to peak differential input voltage V<sub>ID</sub> after device configuration is equal to 4 × (absolute V<sub>MAX</sub> for receiver pin V<sub>ICM</sub>).

- (17) For ES devices, RREF is 2000  $\Omega$  ±1%.

- (18) To calculate the REFCLK phase noise requirement at frequencies other than 622 MHz, use the following formula: REFCLK phase noise at f(MHz) = REFCLK phase noise at 622 MHz + 20\*log(f/622).

- (19) SFP/+ optical modules require the host interface to have RD+/- differentially terminated with 100 Ω. The internal OCT feature is available after the Stratix V FPGA configuration is completed. Altera recommends that FPGA configuration is completed before inserting the optical module. Otherwise, minimize unnecessary removal and insertion with unconfigured devices.

- (20) Refer to Figure 4.

- (21) For oversampling design to support data rates less than the minimum specification, the CDR needs to be in LTR mode only.

- (22) This supply follows VCCR\_GXB for both GX and GT channels.

- (23) When you use fPLL as a TXPLL of the transceiver.

Table 29 shows the  $\ensuremath{V_{\text{OD}}}$  settings for the GT channel.

Table 29. Typical  $\text{V}_{\text{0D}}$  Setting for GT Channel, TX Termination = 100  $\Omega$

| Symbol                                                                  | V <sub>op</sub> Setting | V <sub>op</sub> Value (mV) |

|-------------------------------------------------------------------------|-------------------------|----------------------------|

|                                                                         | 0                       | 0                          |

|                                                                         | 1                       | 200                        |

| V differential peak to peak tunical (1)                                 | 2                       | 400                        |

| <b>V</b> <sub>OD</sub> differential peak to peak typical <sup>(1)</sup> | 3                       | 600                        |

|                                                                         | 4                       | 800                        |

|                                                                         | 5                       | 1000                       |

### Note:

(1) Refer to Figure 4.

Page 38 Switching Characteristics

- XFI

- ASI

- HiGig/HiGig+

- HiGig2/HiGig2+

- Serial Data Converter (SDC)

- GPON

- SDI

- SONET

- Fibre Channel (FC)

- PCIe

- QPI

- SFF-8431

Download the Stratix V Characterization Report Tool to view the characterization report summary for these protocols.

## **Core Performance Specifications**

This section describes the clock tree, phase-locked loop (PLL), digital signal processing (DSP), memory blocks, configuration, and JTAG specifications.

### **Clock Tree Specifications**

Table 30 lists the clock tree specifications for Stratix V devices.

Table 30. Clock Tree Performance for Stratix V Devices (1)

|                              |                          | Performance              |        |      |  |  |  |  |

|------------------------------|--------------------------|--------------------------|--------|------|--|--|--|--|

| Symbol                       | C1, C2, C2L, I2, and I2L | C3, I3, I3L, and<br>I3YY | C4, I4 | Unit |  |  |  |  |

| Global and<br>Regional Clock | 717                      | 650                      | 580    | MHz  |  |  |  |  |

| Periphery Clock              | 550                      | 500                      | 500    | MHz  |  |  |  |  |

### Note to Table 30:

(1) The Stratix V ES devices are limited to 600 MHz core clock tree performance.

Table 36. High-Speed I/O Specifications for Stratix V Devices (1), (2) (Part 2 of 4)

| Cumbal                                                                                                                | Conditions                                                                 |     | C1  |      | C2, | C2L, I | 2, I2L | C3, | I3, I3I | ., I3YY | C4,14 |     |      | IIi. |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|------|-----|--------|--------|-----|---------|---------|-------|-----|------|------|

| Symbol                                                                                                                | Conditions                                                                 | Min | Тур | Max  | Min | Тур    | Max    | Min | Тур     | Max     | Min   | Тур | Max  | Unit |

| Transmitter                                                                                                           |                                                                            |     |     |      |     |        |        |     |         |         |       |     |      |      |

|                                                                                                                       | SERDES factor J<br>= 3 to 10 (9), (11),<br>(12), (13), (14), (15),<br>(16) | (6) | _   | 1600 | (6) | _      | 1434   | (6) | _       | 1250    | (6)   | _   | 1050 | Mbps |

| True<br>Differential                                                                                                  | SERDES factor J ≥ 4  LVDS TX with DPA (12), (14), (15), (16)               | (6) | _   | 1600 | (6) | _      | 1600   | (6) | _       | 1600    | (6)   |     | 1250 | Mbps |

| I/O Standards<br>- f <sub>HSDR</sub> (data<br>rate)                                                                   | SERDES factor J<br>= 2,<br>uses DDR<br>Registers                           | (6) | _   | (7)  | (6) | _      | (7)    | (6) | _       | (7)     | (6)   | _   | (7)  | Mbps |

|                                                                                                                       | SERDES factor J<br>= 1,<br>uses SDR<br>Register                            | (6) | _   | (7)  | (6) | _      | (7)    | (6) | _       | (7)     | (6)   | _   | (7)  | Mbps |

| Emulated Differential I/O Standards with Three External Output Resistor Networks - f <sub>HSDR</sub> (data rate) (10) | SERDES factor J<br>= 4 to 10 (17)                                          | (6) | _   | 1100 | (6) | _      | 1100   | (6) | _       | 840     | (6)   |     | 840  | Mbps |

| t <sub>x Jitter</sub> - True<br>Differential                                                                          | Total Jitter for<br>Data Rate<br>600 Mbps -<br>1.25 Gbps                   | _   | _   | 160  | _   | _      | 160    | _   | _       | 160     | _     | _   | 160  | ps   |

| I/O Standards                                                                                                         | Total Jitter for<br>Data Rate<br>< 600 Mbps                                | _   | _   | 0.1  | _   | _      | 0.1    | _   | _       | 0.1     | _     | _   | 0.1  | UI   |

| t <sub>x Jitter</sub> -<br>Emulated<br>Differential<br>I/O Standards                                                  | Total Jitter for<br>Data Rate<br>600 Mbps - 1.25<br>Gbps                   | _   | _   | 300  | _   | _      | 300    | _   | _       | 300     | _     | _   | 325  | ps   |

| with Three<br>External<br>Output<br>Resistor<br>Network                                                               | Total Jitter for<br>Data Rate<br>< 600 Mbps                                | _   | _   | 0.2  | _   | _      | 0.2    | _   | _       | 0.2     | _     | _   | 0.25 | UI   |

Page 46 Switching Characteristics

Table 36. High-Speed I/O Specifications for Stratix V Devices (1), (2) (Part 3 of 4)

|                                       |                                                                                           |     | C1  |      | C2, | C2L, I | 2, I2L | C3, | 13, I3L | ., I3YY | C4,I4 |     |      |      |

|---------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|------|-----|--------|--------|-----|---------|---------|-------|-----|------|------|

| Symbol                                | Conditions                                                                                | Min | Тур | Max  | Min | Тур    | Max    | Min | Тур     | Max     | Min   | Тур | Max  | Unit |

| t <sub>DUTY</sub>                     | Transmitter output clock duty cycle for both True and Emulated Differential I/O Standards | 45  | 50  | 55   | 45  | 50     | 55     | 45  | 50      | 55      | 45    | 50  | 55   | %    |

|                                       | True Differential<br>I/O Standards                                                        | _   | _   | 160  | _   | _      | 160    | _   | _       | 200     | _     | _   | 200  | ps   |

| t <sub>RISE</sub> & t <sub>FALL</sub> | Emulated Differential I/O Standards with three external output resistor networks          | _   |     | 250  | _   | _      | 250    | _   |         | 250     | _     |     | 300  | ps   |

|                                       | True Differential<br>I/O Standards                                                        | _   | _   | 150  | _   |        | 150    |     | _       | 150     |       | _   | 150  | ps   |

| TCCS                                  | Emulated<br>Differential I/O<br>Standards                                                 | _   | _   | 300  | _   | _      | 300    | _   |         | 300     | _     |     | 300  | ps   |

| Receiver                              |                                                                                           |     |     |      |     |        |        |     |         |         |       |     |      |      |

|                                       | SERDES factor J<br>= 3 to 10 (11), (12),<br>(13), (14), (15), (16)                        | 150 | _   | 1434 | 150 | _      | 1434   | 150 | _       | 1250    | 150   | _   | 1050 | Mbps |

| True<br>Differential<br>I/O Standards | SERDES factor J ≥ 4  LVDS RX with DPA (12), (14), (15), (16)                              | 150 | _   | 1600 | 150 | _      | 1600   | 150 | _       | 1600    | 150   | _   | 1250 | Mbps |

| - f <sub>HSDRDPA</sub><br>(data rate) | SERDES factor J<br>= 2,<br>uses DDR<br>Registers                                          | (6) | _   | (7)  | (6) | _      | (7)    | (6) |         | (7)     | (6)   |     | (7)  | Mbps |

|                                       | SERDES factor J<br>= 1,<br>uses SDR<br>Register                                           | (6) | _   | (7)  | (6) | _      | (7)    | (6) |         | (7)     | (6)   | _   | (7)  | Mbps |

Table 42. Memory Output Clock Jitter Specification for Stratix V Devices (1), (Part 2 of 2) (2), (3)

| Clock<br>Network | Parameter                    | Symbol                | C1    |      | C2, C2L, I2, I2L |      | C3, I3, I3L,<br>I3YY |     | C4,I4 |     | Unit |

|------------------|------------------------------|-----------------------|-------|------|------------------|------|----------------------|-----|-------|-----|------|

|                  |                              |                       | Min   | Max  | Min              | Max  | Min                  | Max | Min   | Max |      |

|                  | Clock period jitter          | $t_{\text{JIT(per)}}$ | -25   | 25   | -25              | 25   | -30                  | 30  | -35   | 35  | ps   |

| PHY<br>Clock     | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>  | -50   | 50   | -50              | 50   | -60                  | 60  | -70   | 70  | ps   |

|                  | Duty cycle jitter            | $t_{JIT(duty)}$       | -37.5 | 37.5 | -37.5            | 37.5 | -45                  | 45  | -56   | 56  | ps   |

### Notes to Table 42:

- (1) The clock jitter specification applies to the memory output clock pins generated using differential signal-splitter and DDIO circuits clocked by a PLL output routed on a PHY, regional, or global clock network as specified. Altera recommends using PHY clock networks whenever possible.

- (2) The clock jitter specification applies to the memory output clock pins clocked by an integer PLL.

- (3) The memory output clock jitter is applicable when an input jitter of 30 ps peak-to-peak is applied with bit error rate (BER) -12, equivalent to 14 sigma.

### **OCT Calibration Block Specifications**

Table 43 lists the OCT calibration block specifications for Stratix V devices.

Table 43. OCT Calibration Block Specifications for Stratix V Devices

| Symbol                | Description                                                                                                                                                                | Min | Тур  | Max | Unit   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by the OCT calibration blocks                                                                                                                               | _   | _    | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of OCTUSRCLK clock cycles required for OCT $\ensuremath{R}_{\ensuremath{S}}/\ensuremath{R}_{\ensuremath{T}}$ calibration                                            |     | 1000 | _   | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for the OCT code to shift out                                                                                                    |     | 32   | _   | Cycles |

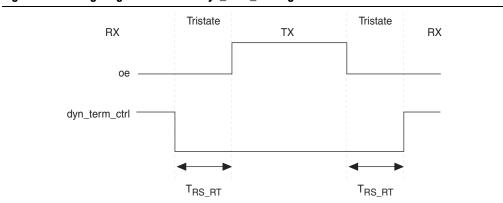

| T <sub>RS_RT</sub>    | Time required between the $\mathtt{dyn\_term\_ctrl}$ and oe signal transitions in a bidirectional I/O buffer to dynamically switch between OCT $R_S$ and $R_T$ (Figure 10) | _   | 2.5  | _   | ns     |

Figure 10 shows the timing diagram for the oe and dyn term ctrl signals.

Figure 10. Timing Diagram for oe and dyn\_term\_ctrl Signals

Configuration Specification Page 55

Table 48. Minimum Configuration Time Estimation for Stratix V Devices

|         | Member<br>Code |       | Active Serial (1) | 1                      | Fast Passive Parallel <sup>(2)</sup> |            |                        |  |

|---------|----------------|-------|-------------------|------------------------|--------------------------------------|------------|------------------------|--|

| Variant |                | Width | DCLK (MHz)        | Min Config<br>Time (s) | Width                                | DCLK (MHz) | Min Config<br>Time (s) |  |

|         | D3             | 4     | 100               | 0.344                  | 32                                   | 100        | 0.043                  |  |

|         | D4             | 4     | 100               | 0.534                  | 32                                   | 100        | 0.067                  |  |

| GS      | D4             | 4     | 100               | 0.344                  | 32                                   | 100        | 0.043                  |  |

| us      | D5             | 4     | 100               | 0.534                  | 32                                   | 100        | 0.067                  |  |

|         | D6             | 4     | 100               | 0.741                  | 32                                   | 100        | 0.093                  |  |

|         | D8             | 4     | 100               | 0.741                  | 32                                   | 100        | 0.093                  |  |

| E       | E9             | 4     | 100               | 0.857                  | 32                                   | 100        | 0.107                  |  |

| _       | EB             | 4     | 100               | 0.857                  | 32                                   | 100        | 0.107                  |  |

### Notes to Table 48:

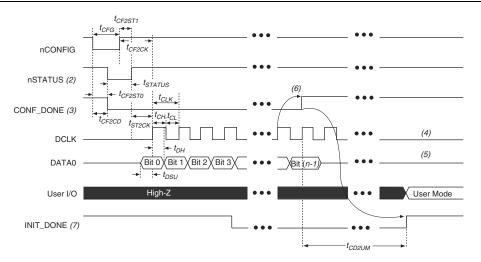

## **Fast Passive Parallel Configuration Timing**

This section describes the fast passive parallel (FPP) configuration timing parameters for Stratix V devices.

## DCLK-to-DATA[] Ratio for FPP Configuration

FPP configuration requires a different DCLK-to-DATA[] ratio when you enable the design security, decompression, or both features. Table 49 lists the DCLK-to-DATA[] ratio for each combination.

Table 49. DCLK-to-DATA[] Ratio (1) (Part 1 of 2)

| Configuration<br>Scheme | Decompression | Design Security | DCLK-to-DATA[]<br>Ratio |

|-------------------------|---------------|-----------------|-------------------------|

|                         | Disabled      | Disabled        | 1                       |

| FPP ×8                  | Disabled      | Enabled         | 1                       |

|                         | Enabled       | Disabled        | 2                       |

|                         | Enabled       | Enabled         | 2                       |

|                         | Disabled      | Disabled        | 1                       |

| FPP ×16                 | Disabled      | Enabled         | 2                       |

| FPP×ID                  | Enabled       | Disabled        | 4                       |

|                         | Enabled       | Enabled         | 4                       |

<sup>(1)</sup> DCLK frequency of 100 MHz using external CLKUSR.

<sup>(2)</sup> Max FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

Page 56 Configuration Specification

Table 49. DCLK-to-DATA[] Ratio (1) (Part 2 of 2)

| Configuration<br>Scheme | Decompression | Design Security | DCLK-to-DATA[]<br>Ratio |

|-------------------------|---------------|-----------------|-------------------------|

|                         | Disabled      | Disabled        | 1                       |

| FPP ×32                 | Disabled      | Enabled         | 4                       |

|                         | Enabled       | Disabled        | 8                       |

|                         | Enabled       | Enabled         | 8                       |

### Note to Table 49:

(1) Depending on the DCLK-to-DATA [] ratio, the host must send a DCLK frequency that is r times the data rate in bytes per second (Bps), or words per second (Wps). For example, in FPP ×16 when the DCLK-to-DATA [] ratio is 2, the DCLK frequency must be 2 times the data rate in Wps. Stratix V devices use the additional clock cycles to decrypt and decompress the configuration data.

If the DCLK-to-DATA[] ratio is greater than 1, at the end of configuration, you can only stop the DCLK (DCLK-to-DATA[] ratio -1) clock cycles after the last data is latched into the Stratix V device.

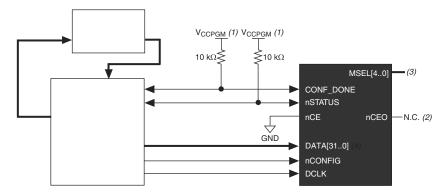

Figure 11 shows the configuration interface connections between the Stratix V device and a MAX II or MAX V device for single device configuration.

Figure 11. Single Device FPP Configuration Using an External Host

### Notes to Figure 11:

- (1) Connect the resistor to a supply that provides an acceptable input signal for the Stratix V device. V<sub>CCPGM</sub> must be high enough to meet the V<sub>IH</sub> specification of the I/O on the device and the external host. Altera recommends powering up all configuration system I/Os with V<sub>CCPGM</sub>.

- (2) You can leave the nceo pin unconnected or use it as a user I/O pin when it does not feed another device's nce pin.

- (3) The MSEL pin settings vary for different data width, configuration voltage standards, and POR delay. To connect MSEL, refer to the MSEL Pin Settings section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices" chapter.

- (4) If you use FPP  $\times 8$ , use DATA [7..0]. If you use FPP  $\times 16$ , use DATA [15..0].

Page 58 Configuration Specification

Table 50 lists the timing parameters for Stratix V devices for FPP configuration when the DCLK-to-DATA[] ratio is 1.

Table 50. FPP Timing Parameters for Stratix V Devices (1)

| Symbol                 | Parameter                                         | Minimum                                                    | Maximum              | Units |

|------------------------|---------------------------------------------------|------------------------------------------------------------|----------------------|-------|

| t <sub>CF2CD</sub>     | nCONFIG low to CONF_DONE low                      | _                                                          | 600                  | ns    |

| t <sub>CF2ST0</sub>    | nconfig low to nstatus low                        | _                                                          | 600                  | ns    |

| t <sub>CFG</sub>       | nCONFIG low pulse width                           | 2                                                          | _                    | μS    |

| t <sub>STATUS</sub>    | nstatus low pulse width                           | 268                                                        | 1,506 <sup>(2)</sup> | μ\$   |

| t <sub>CF2ST1</sub>    | nCONFIG high to nSTATUS high                      | _                                                          | 1,506 <sup>(3)</sup> | μ\$   |

| t <sub>CF2CK</sub> (6) | nCONFIG high to first rising edge on DCLK         | 1,506                                                      | _                    | μ\$   |

| t <sub>ST2CK</sub> (6) | nSTATUS high to first rising edge of DCLK         | 2                                                          | _                    | μ\$   |

| t <sub>DSU</sub>       | DATA[] setup time before rising edge on DCLK      | 5.5                                                        | _                    | ns    |

| t <sub>DH</sub>        | DATA[] hold time after rising edge on DCLK        | 0                                                          | _                    | ns    |

| t <sub>CH</sub>        | DCLK high time                                    | $0.45 \times 1/f_{MAX}$                                    | _                    | S     |

| t <sub>CL</sub>        | DCLK low time                                     | $0.45 \times 1/f_{MAX}$                                    | _                    | S     |

| t <sub>CLK</sub>       | DCLK period                                       | 1/f <sub>MAX</sub>                                         | _                    | S     |

| f                      | DCLK frequency (FPP ×8/×16)                       | _                                                          | 125                  | MHz   |

| f <sub>MAX</sub>       | DCLK frequency (FPP ×32)                          | _                                                          | 100                  | MHz   |

| t <sub>CD2UM</sub>     | CONF_DONE high to user mode (4)                   | 175                                                        | 437                  | μS    |

| +                      | GOVER DOVER high to GUVERN anabled                | 4 × maximum                                                |                      |       |

| t <sub>CD2CU</sub>     | CONF_DONE high to CLKUSR enabled                  | DCLK period                                                | _                    | _     |

| t <sub>CD2UMC</sub>    | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × CLKUSR period) <sup>(5)</sup> | _                    | _     |

### Notes to Table 50:

- (1) Use these timing parameters when the decompression and design security features are disabled.

- (2) This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

- (3) This value is applicable if you do not delay configuration by externally holding the nstatus low.

- (4) The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

- (5) To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the Initialization section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices" chapter.

- (6) If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

## FPP Configuration Timing when DCLK-to-DATA [] > 1

Figure 13 shows the timing waveform for FPP configuration when using a MAX II device, MAX V device, or microprocessor as an external host. This waveform shows timing when the DCLK-to-DATA [] ratio is more than 1.

Configuration Specification Page 61

## **Active Serial Configuration Timing**

Table 52 lists the DCLK frequency specification in the AS configuration scheme.

Table 52. DCLK Frequency Specification in the AS Configuration Scheme (1), (2)

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

| 10.6    | 15.7    | 25.0    | MHz  |

| 21.3    | 31.4    | 50.0    | MHz  |

| 42.6    | 62.9    | 100.0   | MHz  |

### Notes to Table 52:

- This applies to the DCLK frequency specification when using the internal oscillator as the configuration clock source.

- (2) The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

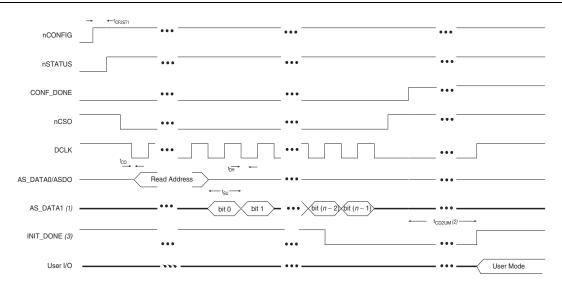

Figure 14 shows the single-device configuration setup for an AS ×1 mode.

Figure 14. AS Configuration Timing

### Notes to Figure 14:

- (1) If you are using AS ×4 mode, this signal represents the AS\_DATA [3..0] and EPCQ sends in 4-bits of data for each DCLK cycle.

- (2) The initialization clock can be from internal oscillator or  ${\tt CLKUSR}$  pin.

- (3) After the option bit to enable the  $INIT\_DONE$  pin is configured into the device, the  $INIT\_DONE$  goes low.

Table 53 lists the timing parameters for AS  $\times 1$  and AS  $\times 4$  configurations in Stratix V devices.

Table 53. AS Timing Parameters for AS  $\times$ 1 and AS  $\times$ 4 Configurations in Stratix V Devices (1), (2) (Part 1 of 2)

| Symbol          | Parameter                                   | Minimum | Maximum | Units |

|-----------------|---------------------------------------------|---------|---------|-------|

| t <sub>CO</sub> | DCLK falling edge to AS_DATAO/ASDO output   | _       | 2       | ns    |

| t <sub>SU</sub> | Data setup time before falling edge on DCLK | 1.5     | _       | ns    |

| t <sub>H</sub>  | Data hold time after falling edge on DCLK   | 0       | _       | ns    |

Page 62 Configuration Specification

Table 53. AS Timing Parameters for AS  $\times$ 1 and AS  $\times$ 4 Configurations in Stratix V Devices (1), (2) (Part 2 of 2)

| Symbol              | Parameter                                         | Minimum                                                                                 | Maximum | Units |

|---------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------|---------|-------|

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode (3)                   | 175                                                                                     | 437     | μS    |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                                                                 | _       | _     |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | $\begin{array}{c} t_{\text{CD2CU}} + (8576 \times \\ \text{CLKUSR period}) \end{array}$ | _       | _     |

### Notes to Table 53:

- (1) The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

- $(2) \quad t_{\text{CF2CD}}, t_{\text{CF2ST0}}, t_{\text{CFG}}, t_{\text{STATUS}}, \text{ and } t_{\text{CF2ST1}} \text{ timing parameters are identical to the timing parameters for PS mode listed in Table 54 on page 63}.$

- (3) To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on this pin, refer to the Initialization section of the "Configuration, Design Security, and Remote System Upgrades in Stratix V Devices" chapter.

## **Passive Serial Configuration Timing**