Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 317000                                                      |

| Number of Logic Elements/Cells | 840000                                                      |

| Total RAM Bits                 | 53248000                                                    |

| Number of I/O                  | 600                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 0.82V ~ 0.88V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1760-BBGA, FCBGA                                            |

| Supplier Device Package        | 1760-HBGA (45x45)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5sgxmb9r2h43c2ln |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Page 2 Electrical Characteristics

Table 1. Stratix V GX and GS Commercial and Industrial Speed Grade Offering (1), (2), (3) (Part 2 of 2)

| Transceiver Speed     |    |         |     | Core Spe | ed Grade |         |                    |     |

|-----------------------|----|---------|-----|----------|----------|---------|--------------------|-----|

| Grade                 | C1 | C2, C2L | C3  | C4       | 12, 12L  | 13, 13L | I3YY               | 14  |

| 3 GX channel—8.5 Gbps | _  | Yes     | Yes | Yes      | _        | Yes     | Yes <sup>(4)</sup> | Yes |

#### Notes to Table 1:

- (1) C = Commercial temperature grade; I = Industrial temperature grade.

- (2) Lower number refers to faster speed grade.

- (3) C2L, I2L, and I3L speed grades are for low-power devices.

- (4) I3YY speed grades can achieve up to 10.3125 Gbps.

Table 2 lists the industrial and commercial speed grades for the Stratix V GT devices.

Table 2. Stratix V GT Commercial and Industrial Speed Grade Offering (1), (2)

| Transacius Snood Crada                             | Core Speed Grade |     |     |     |  |  |  |  |

|----------------------------------------------------|------------------|-----|-----|-----|--|--|--|--|

| Transceiver Speed Grade                            | C1               | C2  | 12  | 13  |  |  |  |  |

| 2<br>GX channel—12.5 Gbps<br>GT channel—28.05 Gbps | Yes              | Yes | _   | _   |  |  |  |  |

| 3<br>GX channel—12.5 Gbps<br>GT channel—25.78 Gbps | Yes              | Yes | Yes | Yes |  |  |  |  |

#### Notes to Table 2:

- (1) C = Commercial temperature grade; I = Industrial temperature grade.

- (2) Lower number refers to faster speed grade.

#### **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Stratix V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

Conditions other than those listed in Table 3 may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

Table 3. Absolute Maximum Ratings for Stratix V Devices (Part 1 of 2)

| Symbol              | Description                                                            | Minimum | Maximum | Unit |

|---------------------|------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>     | Power supply for core voltage and periphery circuitry                  | -0.5    | 1.35    | V    |

| V <sub>CCPT</sub>   | Power supply for programmable power technology                         | -0.5    | 1.8     | V    |

| V <sub>CCPGM</sub>  | Power supply for configuration pins                                    | -0.5    | 3.9     | V    |

| V <sub>CC_AUX</sub> | Auxiliary supply for the programmable power technology                 | -0.5    | 3.4     | V    |

| V <sub>CCBAT</sub>  | Battery back-up power supply for design security volatile key register | -0.5    | 3.9     | V    |

| V <sub>CCPD</sub>   | I/O pre-driver power supply                                            | -0.5    | 3.9     | V    |

| V <sub>CCIO</sub>   | I/O power supply                                                       | -0.5    | 3.9     | V    |

Page 4 Electrical Characteristics

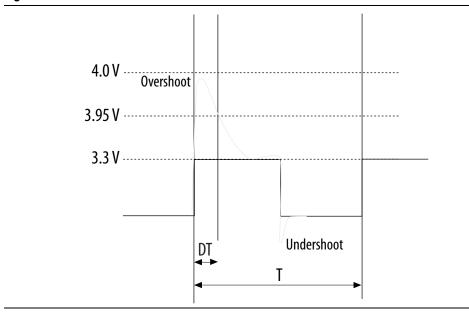

Table 5 lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime. The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% of the duty cycle. For example, a signal that overshoots to 3.95 V can be at 3.95 V for only ~21% over the lifetime of the device; for a device lifetime of 10 years, the overshoot duration amounts to ~2 years.

**Table 5. Maximum Allowed Overshoot During Transitions**

| Symbol  | Description      | Condition (V) | Overshoot Duration as %<br>@ T <sub>J</sub> = 100°C | Unit |

|---------|------------------|---------------|-----------------------------------------------------|------|

|         |                  | 3.8           | 100                                                 | %    |

|         |                  | 3.85          | 64                                                  | %    |

|         |                  | 3.9           | 36                                                  | %    |

|         |                  | 3.95          | 21                                                  | %    |

| Vi (AC) | AC input voltage | 4             | 12                                                  | %    |

|         |                  | 4.05          | 7                                                   | %    |

|         |                  | 4.1           | 4                                                   | %    |

|         |                  | 4.15          | 2                                                   | %    |

|         |                  | 4.2           | 1                                                   | %    |

Figure 1. Stratix V Device Overshoot Duration

Page 10 Electrical Characteristics

Table 11. OCT Calibration Accuracy Specifications for Stratix V Devices (1) (Part 2 of 2)

|                                                                                                                                            |                                                                                                                                        |                                                  | Calibration Accuracy |            |                |            |      |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------|------------|----------------|------------|------|

| Symbol                                                                                                                                     | Description                                                                                                                            | Conditions                                       | C1                   | C2,I2      | C3,I3,<br>I3YY | C4,I4      | Unit |

| 50-Ω R <sub>S</sub>                                                                                                                        | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5,<br>1.8, 1.5, 1.2 V | ±15                  | ±15        | ±15            | ±15        | %    |

| $34\text{-}\Omega$ and $40\text{-}\Omega$ $R_S$                                                                                            | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   | V <sub>CCIO</sub> = 1.5, 1.35,<br>1.25, 1.2 V    | ±15                  | ±15        | ±15            | ±15        | %    |

| $48$ - $\Omega$ , $60$ - $\Omega$ , $80$ - $\Omega$ , and $240$ - $\Omega$ R <sub>S</sub>                                                  | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)                  | V <sub>CCIO</sub> = 1.2 V                        | ±15                  | ±15        | ±15            | ±15        | %    |

| 50-Ω R <sub>T</sub>                                                                                                                        | Internal parallel termination with calibration (50-Ω setting)                                                                          | V <sub>CCIO</sub> = 2.5, 1.8,<br>1.5, 1.2 V      | -10 to +40           | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| $\begin{array}{c} 20\text{-}\Omega,30\text{-}\Omega,\\ 40\text{-}\Omega,60\text{-}\Omega,\\ \text{and}\\ 120\text{-}\OmegaR_T \end{array}$ | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35,<br>1.25 V         | -10 to +40           | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| 60- $\Omega$ and 120- $\Omega$ R <sub>T</sub>                                                                                              | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | V <sub>CCIO</sub> = 1.2                          | -10 to +40           | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| $\begin{array}{c} \textbf{25-}\Omega \\ \textbf{R}_{S\_left\_shift} \end{array}$                                                           | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                               | V <sub>CCIO</sub> = 3.0, 2.5,<br>1.8, 1.5, 1.2 V | ±15                  | ±15        | ±15            | ±15        | %    |

#### Note to Table 11:

Table 12 lists the Stratix V OCT without calibration resistance tolerance to PVT changes.

Table 12. OCT Without Calibration Resistance Tolerance Specifications for Stratix V Devices (Part 1 of 2)

|                             |                                                                        |                                   | Resistance Tolerance |       |                 |        |      |

|-----------------------------|------------------------------------------------------------------------|-----------------------------------|----------------------|-------|-----------------|--------|------|

| Symbol                      | Description                                                            | Conditions                        | C1                   | C2,I2 | C3, I3,<br>I3YY | C4, I4 | Unit |

| 25-Ω R, 50-Ω R <sub>S</sub> | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0 and 2.5 V | ±30                  | ±30   | ±40             | ±40    | %    |

| 25-Ω R <sub>S</sub>         | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 and 1.5 V | ±30                  | ±30   | ±40             | ±40    | %    |

| 25-Ω R <sub>S</sub>         | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2 V         | ±35                  | ±35   | ±50             | ±50    | %    |

<sup>(1)</sup> OCT calibration accuracy is valid at the time of calibration only.

Page 12 Electrical Characteristics

Table 13. OCT Variation after Power-Up Calibration for Stratix V Devices (Part 2 of 2) (1)

| Symbol | Description                                          | V <sub>CCIO</sub> (V) | Typical | Unit |  |

|--------|------------------------------------------------------|-----------------------|---------|------|--|

|        |                                                      | 3.0                   | 0.189   |      |  |

|        |                                                      | 2.5                   | 0.208   |      |  |

| dR/dT  | OCT variation with temperature without recalibration | 1.8                   | 0.266   | %/°C |  |

|        |                                                      | 1.5                   | 0.273   | -    |  |

|        |                                                      | 1.2                   | 0.317   |      |  |

#### Note to Table 13:

(1) Valid for a  $V_{\text{CCIO}}$  range of  $\pm 5\%$  and a temperature range of  $0^\circ$  to  $85^\circ\text{C}.$

#### **Pin Capacitance**

Table 14 lists the Stratix V device family pin capacitance.

**Table 14. Pin Capacitance for Stratix V Devices**

| Symbol             | Description                                                      | Value | Unit |

|--------------------|------------------------------------------------------------------|-------|------|

| C <sub>IOTB</sub>  | Input capacitance on the top and bottom I/O pins                 | 6     | pF   |

| C <sub>IOLR</sub>  | Input capacitance on the left and right I/O pins                 | 6     | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6     | pF   |

#### **Hot Socketing**

Table 15 lists the hot socketing specifications for Stratix V devices.

Table 15. Hot Socketing Specifications for Stratix V Devices

| Symbol                    | Description                                | Maximum             |

|---------------------------|--------------------------------------------|---------------------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                     | 300 μΑ              |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                     | 8 mA <sup>(1)</sup> |

| I <sub>XCVR-TX (DC)</sub> | DC current per transceiver transmitter pin | 100 mA              |

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver pin    | 50 mA               |

#### Note to Table 15:

(1) The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

Page 14 Electrical Characteristics

Table 18. Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Stratix V Devices

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       |                             | V <sub>REF</sub> (V)    |                             | V <sub>TT</sub> (V)         |                            |                             |  |

|-------------------------|-------|-----------------------|-------|-----------------------------|-------------------------|-----------------------------|-----------------------------|----------------------------|-----------------------------|--|

| I/O Standard            | Min   | Тур                   | Max   | Min                         | Тур                     | Max                         | Min                         | Тур                        | Мах                         |  |

| SSTL-2<br>Class I, II   | 2.375 | 2.5                   | 2.625 | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | V <sub>REF</sub> – 0.04     | $V_{REF}$                  | V <sub>REF</sub> + 0.04     |  |

| SSTL-18<br>Class I, II  | 1.71  | 1.8                   | 1.89  | 0.833                       | 0.9                     | 0.969                       | V <sub>REF</sub> – 0.04     | V <sub>REF</sub>           | V <sub>REF</sub> + 0.04     |  |

| SSTL-15<br>Class I, II  | 1.425 | 1.5                   | 1.575 | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>VCCIO             | 0.51 *<br>V <sub>CCIO</sub> |  |

| SSTL-135<br>Class I, II | 1.283 | 1.35                  | 1.418 | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> |  |

| SSTL-125<br>Class I, II | 1.19  | 1.25                  | 1.26  | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>VCCIO             | 0.51 *<br>V <sub>CCIO</sub> |  |

| SSTL-12<br>Class I, II  | 1.14  | 1.20                  | 1.26  | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>VCCIO             | 0.51 *<br>V <sub>CCIO</sub> |  |

| HSTL-18<br>Class I, II  | 1.71  | 1.8                   | 1.89  | 0.85                        | 0.9                     | 0.95                        | _                           | V <sub>CCIO</sub> /2       | _                           |  |

| HSTL-15<br>Class I, II  | 1.425 | 1.5                   | 1.575 | 0.68                        | 0.75                    | 0.9                         | _                           | V <sub>CCIO</sub> /2       | _                           |  |

| HSTL-12<br>Class I, II  | 1.14  | 1.2                   | 1.26  | 0.47 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.53 *<br>V <sub>CCIO</sub> | _                           | V <sub>CCIO</sub> /2       | _                           |  |

| HSUL-12                 | 1.14  | 1.2                   | 1.3   | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | _                           | _                          | _                           |  |

Table 19. Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Stratix V Devices (Part 1 of 2)

| I/O Standard            | V <sub>IL(D(</sub> | ; <sub>)</sub> (V)       | V <sub>IH(D</sub>        | <sub>C)</sub> (V)       | V <sub>IL(AC)</sub> (V)    | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)        | V <sub>OH</sub> (V)        | I (mA)               | l <sub>oh</sub> |

|-------------------------|--------------------|--------------------------|--------------------------|-------------------------|----------------------------|--------------------------|----------------------------|----------------------------|----------------------|-----------------|

| i/U Stanuaru            | Min                | Max                      | Min                      | Max                     | Max                        | Min                      | Max                        | Min                        | I <sub>ol</sub> (mA) | (mA)            |

| SSTL-2<br>Class I       | -0.3               | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> –<br>0.31 | V <sub>REF</sub> + 0.31  | V <sub>TT</sub> – 0.608    | V <sub>TT</sub> + 0.608    | 8.1                  | -8.1            |

| SSTL-2<br>Class II      | -0.3               | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> – 0.31    | V <sub>REF</sub> + 0.31  | V <sub>TT</sub> – 0.81     | V <sub>TT</sub> + 0.81     | 16.2                 | -16.2           |

| SSTL-18<br>Class I      | -0.3               | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> – 0.25    | V <sub>REF</sub> + 0.25  | V <sub>TT</sub> – 0.603    | V <sub>TT</sub> + 0.603    | 6.7                  | -6.7            |

| SSTL-18<br>Class II     | -0.3               | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> –<br>0.25 | V <sub>REF</sub> + 0.25  | 0.28                       | V <sub>CCIO</sub> - 0.28   | 13.4                 | -13.4           |

| SSTL-15<br>Class I      | _                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> – 0.175   | V <sub>REF</sub> + 0.175 | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | 8                    | -8              |

| SSTL-15<br>Class II     | _                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> – 0.175   | V <sub>REF</sub> + 0.175 | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | 16                   | -16             |

| SSTL-135<br>Class I, II | _                  | V <sub>REF</sub> – 0.09  | V <sub>REF</sub> + 0.09  | _                       | V <sub>REF</sub> –<br>0.16 | V <sub>REF</sub> + 0.16  | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | _                    | _               |

| SSTL-125<br>Class I, II | _                  | V <sub>REF</sub> – 0.85  | V <sub>REF</sub> + 0.85  | _                       | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> + 0.15  | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | _                    | _               |

| SSTL-12<br>Class I, II  | _                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> + 0.15  | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | _                    | _               |

Page 16 Electrical Characteristics

Table 21. Differential HSTL and HSUL I/O Standards for Stratix V Devices (Part 2 of 2)

| I/O                    |      | V <sub>CCIO</sub> (V) |      |      | <sub>DC)</sub> (V)      |                                 | V <sub>X(AC)</sub> (V)    |                                 |                           | V <sub>CM(DC)</sub> (V    | )                         | V <sub>DIF(AC)</sub> (V) |                             |

|------------------------|------|-----------------------|------|------|-------------------------|---------------------------------|---------------------------|---------------------------------|---------------------------|---------------------------|---------------------------|--------------------------|-----------------------------|

| Standard               | Min  | Тур                   | Max  | Min  | Max                     | Min                             | Тур                       | Max                             | Min                       | Тур                       | Max                       | Min                      | Max                         |

| HSTL-12<br>Class I, II | 1.14 | 1.2                   | 1.26 | 0.16 | V <sub>CCIO</sub> + 0.3 | _                               | 0.5*<br>V <sub>CCIO</sub> | _                               | 0.4*<br>V <sub>CCIO</sub> | 0.5*<br>V <sub>CCIO</sub> | 0.6*<br>V <sub>CCIO</sub> | 0.3                      | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14 | 1.2                   | 1.3  | 0.26 | 0.26                    | 0.5*V <sub>CCIO</sub><br>- 0.12 | 0.5*<br>V <sub>CCIO</sub> | 0.5*V <sub>CCIO</sub><br>+ 0.12 | 0.4*<br>V <sub>CCIO</sub> | 0.5*<br>V <sub>CCIO</sub> | 0.6*<br>V <sub>CCIO</sub> | 0.44                     | 0.44                        |

Table 22. Differential I/O Standard Specifications for Stratix V Devices (7)

| I/O                          | Vc    | <sub>CIO</sub> (V) | (10)  |     | V <sub>ID</sub> (mV) <sup>(8)</sup> |     |      | $V_{ICM(DC)}$ (V)              |       | V <sub>o</sub> | <sub>D</sub> (V) ( | 6)  | V <sub>OCM</sub> (V) <sup>(6)</sup> |      |       |

|------------------------------|-------|--------------------|-------|-----|-------------------------------------|-----|------|--------------------------------|-------|----------------|--------------------|-----|-------------------------------------|------|-------|

| Standard                     | Min   | Тур                | Max   | Min | Condition                           | Max | Min  | Condition                      | Max   | Min            | Тур                | Max | Min                                 | Тур  | Max   |

| PCML                         | Trar  | nsmitte            |       |     |                                     |     |      | of the high-s<br>I/O pin speci |       |                |                    |     |                                     |      | . For |

| 2.5 V                        | 2.375 | 2.5                | 2.625 | 100 | V <sub>CM</sub> =                   | _   | 0.05 | D <sub>MAX</sub> ≤ 700 Mbps    | 1.8   | 0.247          | _                  | 0.6 | 1.125                               | 1.25 | 1.375 |

| LVDS (1)                     | 2.373 | 2.3                | 2.023 | 100 | 1.25 V                              |     | 1.05 | D <sub>MAX</sub> > 700 Mbps    | 1.55  | 0.247          | _                  | 0.6 | 1.125                               | 1.25 | 1.375 |

| BLVDS (5)                    | 2.375 | 2.5                | 2.625 | 100 | _                                   | _   | _    | _                              | _     | _              | _                  | _   | _                                   | _    | _     |

| RSDS<br>(HIO) <sup>(2)</sup> | 2.375 | 2.5                | 2.625 | 100 | V <sub>CM</sub> = 1.25 V            | _   | 0.3  | _                              | 1.4   | 0.1            | 0.2                | 0.6 | 0.5                                 | 1.2  | 1.4   |

| Mini-<br>LVDS<br>(HIO) (3)   | 2.375 | 2.5                | 2.625 | 200 | _                                   | 600 | 0.4  | _                              | 1.325 | 0.25           | _                  | 0.6 | 1                                   | 1.2  | 1.4   |

| LVPECL (4                    | _     | _                  | _     | 300 | _                                   | _   | 0.6  | D <sub>MAX</sub> ≤ 700 Mbps    | 1.8   | _              | _                  | _   | _                                   | _    |       |

| ), (9)                       | _     | _                  | _     | 300 | _                                   | _   | 1    | D <sub>MAX</sub> > 700 Mbps    | 1.6   | _              | _                  | _   | _                                   | _    | _     |

#### Notes to Table 22:

- (1) For optimized LVDS receiver performance, the receiver voltage input range must be between 1.0 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

- (2) For optimized RSDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.45 V.

- (3) For optimized Mini-LVDS receiver performance, the receiver voltage input range must be between 0.3 V to 1.425 V.

- (4) For optimized LVPECL receiver performance, the receiver voltage input range must be between 0.85 V to 1.75 V for data rate above 700 Mbps and 0.45 V to 1.95 V for data rate below 700 Mbps.

- (5) There are no fixed  $V_{\text{ICM}}$ ,  $V_{\text{OD}}$ , and  $V_{\text{OCM}}$  specifications for BLVDS. They depend on the system topology.

- (6) RL range:  $90 \le RL \le 110 \Omega$ .

- (7) The 1.4-V and 1.5-V PCML transceiver I/O standard specifications are described in "Transceiver Performance Specifications" on page 18.

- (8) The minimum VID value is applicable over the entire common mode range, VCM.

- (9) LVPECL is only supported on dedicated clock input pins.

- (10) Differential inputs are powered by VCCPD which requires 2.5  $\rm V.$

## **Power Consumption**

Altera offers two ways to estimate power consumption for a design—the Excel-based Early Power Estimator and the Quartus<sup>®</sup> II PowerPlay Power Analyzer feature.

Page 20 Switching Characteristics

Table 23. Transceiver Specifications for Stratix V GX and GS Devices  $^{(1)}$  (Part 3 of 7)

| Symbol/                                                                                                                      | Conditions                                                                  | Trai | nsceive<br>Grade | r Speed<br>1 | Trai     | nsceive<br>Grade | r Speed<br>2 | Trar    | sceive<br>Grade | er Speed<br>e 3          | Unit |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------------------|--------------|----------|------------------|--------------|---------|-----------------|--------------------------|------|

| Description                                                                                                                  |                                                                             | Min  | Тур              | Max          | Min      | Тур              | Max          | Min     | Тур             | Max                      |      |

| Reconfiguration clock (mgmt_clk_clk) frequency                                                                               | _                                                                           | 100  | _                | 125          | 100      | _                | 125          | 100     | _               | 125                      | MHz  |

| Receiver                                                                                                                     |                                                                             |      |                  |              |          |                  |              |         |                 |                          |      |

| Supported I/O<br>Standards                                                                                                   | _                                                                           |      |                  | 1.4-V PCMI   | L, 1.5-V | PCML,            | 2.5-V PCM    | L, LVPE | CL, and         | d LVDS                   |      |

| Data rate<br>(Standard PCS)                                                                                                  | _                                                                           | 600  | _                | 12200        | 600      | _                | 12200        | 600     | _               | 8500/<br>10312.5<br>(24) | Mbps |

| Data rate<br>(10G PCS) (9), (23)                                                                                             | _                                                                           | 600  | _                | 14100        | 600      | _                | 12500        | 600     | _               | 8500/<br>10312.5<br>(24) | Mbps |

| Absolute V <sub>MAX</sub> for a receiver pin <sup>(5)</sup>                                                                  | _                                                                           | _    | _                | 1.2          | _        | _                | 1.2          | _       | _               | 1.2                      | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                                 | _                                                                           | -0.4 | _                | _            | -0.4     | _                | _            | -0.4    | _               | _                        | V    |

| Maximum peak-<br>to-peak<br>differential input<br>voltage V <sub>ID</sub> (diff p-<br>p) before device<br>configuration (22) | _                                                                           | _    | _                | 1.6          | _        | _                | 1.6          | _       | _               | 1.6                      | V    |

| Maximum peak-                                                                                                                | $V_{CCR\_GXB} = 1.0 \text{ V}/1.05 \text{ V} $ $(V_{ICM} = 0.70 \text{ V})$ | _    | _                | 2.0          | _        | _                | 2.0          | _       | _               | 2.0                      | V    |

| differential input<br>voltage V <sub>ID</sub> (diff p-<br>p) after device<br>configuration (18),                             | $V_{CCR\_GXB} = 0.90 \text{ V}$ $(V_{ICM} = 0.6 \text{ V})$                 |      | _                | 2.4          | _        | _                | 2.4          | _       | _               | 2.4                      | V    |

| (22)                                                                                                                         | $V_{CCR\_GXB} = 0.85 \text{ V}$ $(V_{ICM} = 0.6 \text{ V})$                 | _    | _                | 2.4          | _        | _                | 2.4          | _       | _               | 2.4                      | V    |

| Minimum differential eye opening at receiver serial input pins (6), (22), (27)                                               | _                                                                           | 85   | _                | _            | 85       | _                | _            | 85      | _               | _                        | mV   |

Switching Characteristics Page 21

Table 23. Transceiver Specifications for Stratix V GX and GS Devices (1) (Part 4 of 7)

| Symbol/                                                   | Conditions                                                                                                             | Tra | nsceive<br>Grade | r Speed<br>1 | Trai | nsceive<br>Grade |     | Trai | nsceive<br>Grade | r Speed<br>3 | Unit |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|------------------|--------------|------|------------------|-----|------|------------------|--------------|------|

| Description                                               |                                                                                                                        | Min | Тур              | Max          | Min  | Тур              | Max | Min  | Тур              | Max          |      |

|                                                           | 85– $\Omega$ setting                                                                                                   | _   | 85 ±<br>30%      | _            | _    | 85 ± 30%         | _   | _    | 85 ±<br>30%      | _            | Ω    |

| Differential on-                                          | 100–Ω<br>setting                                                                                                       | _   | 100<br>±<br>30%  | _            | _    | 100<br>±<br>30%  | _   | _    | 100<br>±<br>30%  | _            | Ω    |

| chip termination resistors (21)                           | 120–Ω<br>setting                                                                                                       | _   | 120<br>±<br>30%  |              | _    | 120<br>±<br>30%  |     | _    | 120<br>±<br>30%  | _            | Ω    |

|                                                           | 150-Ω<br>setting                                                                                                       | _   | 150<br>±<br>30%  | _            | _    | 150<br>±<br>30%  | _   | _    | 150<br>±<br>30%  | _            | Ω    |

|                                                           | V <sub>CCR_GXB</sub> = 0.85 V or 0.9 V full bandwidth                                                                  | _   | 600              | _            | _    | 600              | _   | _    | 600              | _            | mV   |

| V <sub>ICM</sub><br>(AC and DC<br>coupled)                | $\begin{array}{c} V_{CCR\_GXB} = \\ 0.85 \text{ V or } 0.9 \\ \text{V} \\ \text{half} \\ \text{bandwidth} \end{array}$ | _   | 600              | _            | _    | 600              | _   | _    | 600              | _            | mV   |

| coupleu)                                                  | V <sub>CCR_GXB</sub> = 1.0 V/1.05 V full bandwidth                                                                     | _   | 700              | _            | _    | 700              | _   | _    | 700              | _            | mV   |

|                                                           | V <sub>CCR_GXB</sub> = 1.0 V half bandwidth                                                                            | _   | 750              | _            | _    | 750              | _   | _    | 750              | _            | mV   |

| t <sub>LTR</sub> (11)                                     | _                                                                                                                      | _   | _                | 10           | _    | _                | 10  | _    | _                | 10           | μs   |

| t <sub>LTD</sub> (12)                                     | _                                                                                                                      | 4   | _                |              | 4    |                  |     | 4    |                  | _            | μs   |

| t <sub>LTD_manual</sub> (13)                              | _                                                                                                                      | 4   | _                |              | 4    | _                |     | 4    | _                |              | μs   |

| t <sub>LTR_LTD_manual</sub> (14)                          | _                                                                                                                      | 15  | _                | _            | 15   |                  | _   | 15   |                  | _            | μs   |

| Run Length                                                | _                                                                                                                      |     | _                | 200          |      | _                | 200 | _    |                  | 200          | UI   |

| Programmable<br>equalization<br>(AC Gain) <sup>(10)</sup> | Full<br>bandwidth<br>(6.25 GHz)<br>Half<br>bandwidth<br>(3.125 GHz)                                                    | _   | _                | 16           | _    | _                | 16  | _    | _                | 16           | dB   |

Page 26 Switching Characteristics

Table 25 shows the approximate maximum data rate using the standard PCS.

Table 25. Stratix V Standard PCS Approximate Maximum Date Rate (1), (3)

| Made (2)            | Transceiver | PMA Width                                | 20      | 20      | 16      | 16      | 10  | 10  | 8    | 8    |

|---------------------|-------------|------------------------------------------|---------|---------|---------|---------|-----|-----|------|------|

| Mode <sup>(2)</sup> | Speed Grade | PCS/Core Width                           | 40      | 20      | 32      | 16      | 20  | 10  | 16   | 8    |

|                     | 1           | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.5 | 5.8 | 5.2  | 4.72 |

|                     | 2           | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.5 | 5.8 | 5.2  | 4.72 |

|                     | 2           | C3, I3, I3L<br>core speed grade          | 9.8     | 9.0     | 7.84    | 7.2     | 5.3 | 4.7 | 4.24 | 3.76 |

| FIFO                |             | C1, C2, C2L, I2, I2L core speed grade    | 8.5     | 8.5     | 8.5     | 8.5     | 6.5 | 5.8 | 5.2  | 4.72 |

|                     | 3           | I3YY<br>core speed grade                 | 10.3125 | 10.3125 | 7.84    | 7.2     | 5.3 | 4.7 | 4.24 | 3.76 |

|                     | 3           | C3, I3, I3L<br>core speed grade          | 8.5     | 8.5     | 7.84    | 7.2     | 5.3 | 4.7 | 4.24 | 3.76 |

|                     |             | C4, I4<br>core speed grade               | 8.5     | 8.2     | 7.04    | 6.56    | 4.8 | 4.2 | 3.84 | 3.44 |

|                     | 1           | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.1 | 5.7 | 4.88 | 4.56 |

|                     | 2           | C1, C2, C2L, I2, I2L<br>core speed grade | 12.2    | 11.4    | 9.76    | 9.12    | 6.1 | 5.7 | 4.88 | 4.56 |

|                     | 2           | C3, I3, I3L<br>core speed grade          | 9.8     | 9.0     | 7.92    | 7.2     | 4.9 | 4.5 | 3.96 | 3.6  |

| Register            |             | C1, C2, C2L, I2, I2L<br>core speed grade | 10.3125 | 10.3125 | 10.3125 | 10.3125 | 6.1 | 5.7 | 4.88 | 4.56 |

|                     | 3           | I3YY<br>core speed grade                 | 10.3125 | 10.3125 | 7.92    | 7.2     | 4.9 | 4.5 | 3.96 | 3.6  |

|                     | 3           | C3, I3, I3L<br>core speed grade          | 8.5     | 8.5     | 7.92    | 7.2     | 4.9 | 4.5 | 3.96 | 3.6  |

|                     |             | C4, I4<br>core speed grade               | 8.5     | 8.2     | 7.04    | 6.56    | 4.4 | 4.1 | 3.52 | 3.28 |

#### Notes to Table 25:

<sup>(1)</sup> The maximum data rate is in Gbps.

<sup>(2)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

<sup>(3)</sup> The maximum data rate is also constrained by the transceiver speed grade. Refer to Table 1 for the transceiver speed grade.

Page 28 Switching Characteristics

Table 27 shows the  $\ensuremath{V_{OD}}$  settings for the GX channel.

Table 27. Typical V $_{\text{OD}}$  Setting for GX Channel, TX Termination = 100  $\Omega$   $^{(2)}$

| Symbol                                | V <sub>OD</sub> Setting | V <sub>op</sub> Value<br>(mV) | V <sub>op</sub> Setting | V <sub>op</sub> Value<br>(mV) |

|---------------------------------------|-------------------------|-------------------------------|-------------------------|-------------------------------|

|                                       | 0 (1)                   | 0                             | 32                      | 640                           |

|                                       | 1 (1)                   | 20                            | 33                      | 660                           |

|                                       | 2 (1)                   | 40                            | 34                      | 680                           |

|                                       | 3 (1)                   | 60                            | 35                      | 700                           |

|                                       | 4 (1)                   | 80                            | 36                      | 720                           |

|                                       | 5 <sup>(1)</sup>        | 100                           | 37                      | 740                           |

|                                       | 6                       | 120                           | 38                      | 760                           |

|                                       | 7                       | 140                           | 39                      | 780                           |

|                                       | 8                       | 160                           | 40                      | 800                           |

|                                       | 9                       | 180                           | 41                      | 820                           |

|                                       | 10                      | 200                           | 42                      | 840                           |

|                                       | 11                      | 220                           | 43                      | 860                           |

|                                       | 12                      | 240                           | 44                      | 880                           |

|                                       | 13                      | 260                           | 45                      | 900                           |

|                                       | 14                      | 280                           | 46                      | 920                           |

| <b>V</b> op differential peak to peak | 15                      | 300                           | 47                      | 940                           |

| typical <sup>(3)</sup>                | 16                      | 320                           | 48                      | 960                           |

|                                       | 17                      | 340                           | 49                      | 980                           |

|                                       | 18                      | 360                           | 50                      | 1000                          |

|                                       | 19                      | 380                           | 51                      | 1020                          |

|                                       | 20                      | 400                           | 52                      | 1040                          |

|                                       | 21                      | 420                           | 53                      | 1060                          |

|                                       | 22                      | 440                           | 54                      | 1080                          |

|                                       | 23                      | 460                           | 55                      | 1100                          |

|                                       | 24                      | 480                           | 56                      | 1120                          |

|                                       | 25                      | 500                           | 57                      | 1140                          |

|                                       | 26                      | 520                           | 58                      | 1160                          |

|                                       | 27                      | 540                           | 59                      | 1180                          |

|                                       | 28                      | 560                           | 60                      | 1200                          |

|                                       | 29                      | 580                           | 61                      | 1220                          |

|                                       | 30                      | 600                           | 62                      | 1240                          |

|                                       | 31                      | 620                           | 63                      | 1260                          |

#### Note to Table 27:

- (1) If TX termination resistance =  $100\Omega$ , this VOD setting is illegal.

- (2) The tolerance is +/-20% for all VOD settings except for settings 2 and below.

- (3) Refer to Figure 2.

Switching Characteristics Page 31

Table 28. Transceiver Specifications for Stratix V GT Devices (Part 2 of 5)  $^{(1)}$

| Symbol/                                                                                                          | Conditions                                                    | S      | Transceive<br>peed Grade |              |              | Transceive<br>Deed Grade |             | Unit     |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------|--------------------------|--------------|--------------|--------------------------|-------------|----------|

| Description                                                                                                      |                                                               | Min    | Тур                      | Max          | Min          | Тур                      | Max         | 1        |

|                                                                                                                  | 100 Hz                                                        | _      | _                        | -70          | _            | _                        | -70         |          |

| Transmitter REFCLK                                                                                               | 1 kHz                                                         | _      | _                        | -90          |              | _                        | -90         |          |

| Phase Noise (622                                                                                                 | 10 kHz                                                        | _      | _                        | -100         | _            | _                        | -100        | dBc/Hz   |

| MHz) <sup>(18)</sup>                                                                                             | 100 kHz                                                       | _      | _                        | -110         | _            | _                        | -110        |          |

|                                                                                                                  | ≥1 MHz                                                        |        | _                        | -120         | _            |                          | -120        | 1        |

| Transmitter REFCLK<br>Phase Jitter (100<br>MHz) <sup>(15)</sup>                                                  | 10 kHz to<br>1.5 MHz<br>(PCle)                                | _      | _                        | 3            | _            | _                        | 3           | ps (rms) |

| RREF (17)                                                                                                        | _                                                             | _      | 1800<br>± 1%             | _            | _            | 1800<br>± 1%             | _           | Ω        |

| Transceiver Clocks                                                                                               |                                                               |        |                          |              |              |                          |             |          |

| fixedclk clock<br>frequency                                                                                      | PCIe<br>Receiver<br>Detect                                    | _      | 100 or<br>125            | _            | _            | 100 or<br>125            | _           | MHz      |

| Reconfiguration clock<br>(mgmt_clk_clk)<br>frequency                                                             |                                                               | 100    | _                        | 125          | 100          |                          | 125         | MHz      |

| Receiver                                                                                                         |                                                               |        |                          |              |              |                          |             |          |

| Supported I/O<br>Standards                                                                                       | _                                                             |        | 1.4-V PCML               | , 1.5-V PCML | _, 2.5-V PCI | ML, LVPEC                | L, and LVDS | 6        |

| Data rate<br>(Standard PCS) (21)                                                                                 | GX channels                                                   | 600    | _                        | 8500         | 600          | _                        | 8500        | Mbps     |

| Data rate<br>(10G PCS) (21)                                                                                      | GX channels                                                   | 600    | _                        | 12,500       | 600          | _                        | 12,500      | Mbps     |

| Data rate                                                                                                        | GT channels                                                   | 19,600 | _                        | 28,050       | 19,600       | _                        | 25,780      | Mbps     |

| Absolute V <sub>MAX</sub> for a receiver pin <sup>(3)</sup>                                                      | GT channels                                                   | _      | _                        | 1.2          |              | _                        | 1.2         | V        |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                     | GT channels                                                   | -0.4   | _                        | _            | -0.4         | _                        | _           | V        |

| Maximum peak-to-peak                                                                                             | GT channels                                                   |        | _                        | 1.6          | _            |                          | 1.6         | V        |

| differential input<br>voltage V <sub>ID</sub> (diff p-p)<br>before device<br>configuration <sup>(20)</sup>       | GX channels                                                   |        |                          |              | (8)          |                          |             |          |

|                                                                                                                  | GT channels                                                   |        |                          |              |              |                          |             |          |

| Maximum peak-to-peak differential input voltage V <sub>ID</sub> (diff p-p) after device configuration (16), (20) | $V_{CCR\_GTB} = 1.05 \text{ V} $ $(V_{ICM} = 0.65 \text{ V})$ | _      | _                        | 2.2          | _            | _                        | 2.2         | V        |

| Johnguration 7, 17                                                                                               | GX channels                                                   |        |                          |              | (8)          |                          | •           | •        |

| Minimum differential                                                                                             | GT channels                                                   | 200    | _                        | _            | 200          |                          | _           | mV       |

| eye opening at receiver serial input pins <sup>(4)</sup> , <sup>(20)</sup>                                       | GX channels                                                   |        |                          |              | (8)          |                          |             |          |

Page 32 Switching Characteristics

Table 28. Transceiver Specifications for Stratix V GT Devices (Part 3 of 5)  $^{(1)}$

| Symbol/                                                   | Conditions                       |     | Transceiver<br>Speed Grade |        |             | Transceive<br>peed Grade |        | Unit  |

|-----------------------------------------------------------|----------------------------------|-----|----------------------------|--------|-------------|--------------------------|--------|-------|

| Description                                               |                                  | Min | Тур                        | Max    | Min         | Тур                      | Max    |       |

| Differential on-chip termination resistors (7)            | GT channels                      | _   | 100                        | _      | _           | 100                      | _      | Ω     |

|                                                           | 85-Ω setting                     | _   | 85 ± 30%                   | _      | _           | 85<br>± 30%              | _      | Ω     |

| Differential on-chip termination resistors                | 100-Ω<br>setting                 | _   | 100<br>± 30%               | _      | _           | 100<br>± 30%             | _      | Ω     |

| for GX channels (19)                                      | 120-Ω<br>setting                 | _   | 120<br>± 30%               | _      | _           | 120<br>± 30%             | _      | Ω     |

|                                                           | 150-Ω<br>setting                 | _   | 150<br>± 30%               | _      | _           | 150<br>± 30%             | _      | Ω     |

| V <sub>ICM</sub> (AC coupled)                             | GT channels                      | _   | 650                        | _      | _           | 650                      | _      | mV    |

|                                                           | VCCR_GXB =<br>0.85 V or<br>0.9 V | _   | 600                        | _      | _           | 600                      | _      | mV    |

| VICM (AC and DC coupled) for GX Channels                  | VCCR_GXB = 1.0 V full bandwidth  | _   | 700                        | _      | _           | 700                      | _      | mV    |

|                                                           | VCCR_GXB = 1.0 V half bandwidth  | _   | 750                        | _      | _           | 750                      | _      | mV    |

| t <sub>LTR</sub> <sup>(9)</sup>                           | _                                | _   | _                          | 10     | _           | _                        | 10     | μs    |

| t <sub>LTD</sub> <sup>(10)</sup>                          | _                                | 4   | _                          | _      | 4           | _                        | _      | μs    |

| t <sub>LTD_manual</sub> (11)                              |                                  | 4   | _                          | _      | 4           | _                        | _      | μs    |

| t <sub>LTR_LTD_manual</sub> (12)                          |                                  | 15  | _                          | _      | 15          | _                        | _      | μs    |

| Run Length                                                | GT channels                      | _   | _                          | 72     | _           | _                        | 72     | CID   |

| nuii Leiigiii                                             | GX channels                      |     |                            |        | (8)         |                          |        |       |

| CDR PPM                                                   | GT channels                      | _   | _                          | 1000   | _           | _                        | 1000   | ± PPM |

| ODITITIVI                                                 | GX channels                      |     |                            |        | (8)         |                          |        |       |

| Programmable                                              | GT channels                      | _   | _                          | 14     | _           | _                        | 14     | dB    |

| equalization<br>(AC Gain) <sup>(5)</sup>                  | GX channels                      |     |                            |        | (8)         |                          |        |       |

| Programmable                                              | GT channels                      | _   | _                          | 7.5    | _           | _                        | 7.5    | dB    |

| DC gain <sup>(6)</sup>                                    | GX channels                      |     |                            |        | (8)         |                          |        |       |

| Differential on-chip termination resistors <sup>(7)</sup> | GT channels                      |     | 100                        | _      | _           | 100                      | _      | Ω     |

| Transmitter                                               | · '                              |     | •                          |        |             | •                        | •      |       |

| Supported I/O<br>Standards                                | _                                |     |                            | 1.4-V  | and 1.5-V F | PCML                     |        |       |

| Data rate<br>(Standard PCS)                               | GX channels                      | 600 | _                          | 8500   | 600         | _                        | 8500   | Mbps  |

| Data rate<br>(10G PCS)                                    | GX channels                      | 600 | _                          | 12,500 | 600         |                          | 12,500 | Mbps  |

Page 42 Switching Characteristics

Table 32. Block Performance Specifications for Stratix V DSP Devices (Part 2 of 2)

|                       |     | Peformance |           |      |                  |     |     |      |  |  |  |  |  |

|-----------------------|-----|------------|-----------|------|------------------|-----|-----|------|--|--|--|--|--|

| Mode                  | C1  | C2, C2L    | 12, 12L   | C3   | 13, 13L,<br>13YY | C4  | 14  | Unit |  |  |  |  |  |

|                       |     | Modes us   | ing Three | DSPs | •                |     |     |      |  |  |  |  |  |

| One complex 18 x 25   | 425 | 425        | 415       | 340  | 340              | 275 | 265 | MHz  |  |  |  |  |  |

| Modes using Four DSPs |     |            |           |      |                  |     |     |      |  |  |  |  |  |

| One complex 27 x 27   | 465 | 465        | 465       | 380  | 380              | 300 | 290 | MHz  |  |  |  |  |  |

## **Memory Block Specifications**

Table 33 lists the Stratix V memory block specifications.

Table 33. Memory Block Performance Specifications for Stratix V Devices (1), (2) (Part 1 of 2)

|        |                                    | Resour | ces Used | Performance |            |     |     |         |                     |     |      |

|--------|------------------------------------|--------|----------|-------------|------------|-----|-----|---------|---------------------|-----|------|

| Memory | Mode                               | ALUTS  | Memory   | C1          | C2,<br>C2L | C3  | C4  | 12, I2L | 13,<br>13L,<br>13YY | 14  | Unit |

|        | Single port, all supported widths  | 0      | 1        | 450         | 450        | 400 | 315 | 450     | 400                 | 315 | MHz  |

| MLAB   | Simple dual-port,<br>x32/x64 depth | 0      | 1        | 450         | 450        | 400 | 315 | 450     | 400                 | 315 | MHz  |

| IVILAD | Simple dual-port, x16 depth (3)    | 0      | 1        | 675         | 675        | 533 | 400 | 675     | 533                 | 400 | MHz  |

|        | ROM, all supported widths          | 0      | 1        | 600         | 600        | 500 | 450 | 600     | 500                 | 450 | MHz  |

Page 46 Switching Characteristics

Table 36. High-Speed I/O Specifications for Stratix V Devices (1), (2) (Part 3 of 4)

|                                       |                                                                                           |     | C1  |      | C2, | C2L, I | 2, I2L | C3, | 13, I3L | ., I3YY |     | C4,I4 | 4    |      |

|---------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|------|-----|--------|--------|-----|---------|---------|-----|-------|------|------|

| Symbol                                | Conditions                                                                                | Min | Тур | Max  | Min | Тур    | Max    | Min | Тур     | Max     | Min | Тур   | Max  | Unit |

| t <sub>DUTY</sub>                     | Transmitter output clock duty cycle for both True and Emulated Differential I/O Standards | 45  | 50  | 55   | 45  | 50     | 55     | 45  | 50      | 55      | 45  | 50    | 55   | %    |

|                                       | True Differential<br>I/O Standards                                                        | _   | _   | 160  | _   | _      | 160    | _   | _       | 200     | _   | _     | 200  | ps   |

| t <sub>RISE</sub> & t <sub>FALL</sub> | Emulated Differential I/O Standards with three external output resistor networks          | _   |     | 250  | _   | _      | 250    | _   |         | 250     | _   |       | 300  | ps   |

|                                       | True Differential<br>I/O Standards                                                        | _   | _   | 150  | _   |        | 150    |     | _       | 150     |     | _     | 150  | ps   |

| TCCS                                  | Emulated<br>Differential I/O<br>Standards                                                 | _   | _   | 300  | _   | _      | 300    | _   |         | 300     | _   |       | 300  | ps   |

| Receiver                              |                                                                                           |     |     |      |     |        |        |     |         |         |     |       |      |      |

|                                       | SERDES factor J<br>= 3 to 10 (11), (12),<br>(13), (14), (15), (16)                        | 150 | _   | 1434 | 150 | _      | 1434   | 150 | _       | 1250    | 150 | _     | 1050 | Mbps |

| True<br>Differential<br>I/O Standards | SERDES factor J ≥ 4  LVDS RX with DPA (12), (14), (15), (16)                              | 150 | _   | 1600 | 150 | _      | 1600   | 150 | _       | 1600    | 150 | _     | 1250 | Mbps |

| - f <sub>HSDRDPA</sub><br>(data rate) | SERDES factor J<br>= 2,<br>uses DDR<br>Registers                                          | (6) | _   | (7)  | (6) | _      | (7)    | (6) |         | (7)     | (6) |       | (7)  | Mbps |

|                                       | SERDES factor J<br>= 1,<br>uses SDR<br>Register                                           | (6) | _   | (7)  | (6) | _      | (7)    | (6) |         | (7)     | (6) | _     | (7)  | Mbps |

Configuration Specification Page 57

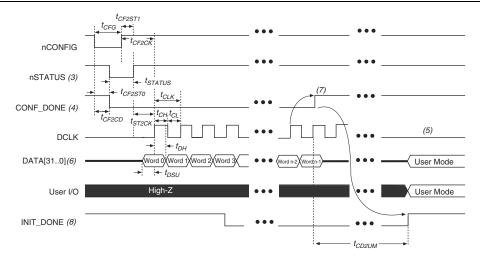

#### FPP Configuration Timing when DCLK-to-DATA [] = 1

Figure 12 shows the timing waveform for FPP configuration when using a MAX II or MAX V device as an external host. This waveform shows timing when the DCLK-to-DATA[] ratio is 1.

Figure 12. FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is 1 (1), (2)

#### Notes to Figure 12:

- (1) Use this timing waveform when the DCLK-to-DATA[] ratio is 1.

- (2) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic-high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (3) After power-up, the Stratix V device holds nSTATUS low for the time of the POR delay.

- (4) After power-up, before and during configuration, CONF DONE is low.

- (5) Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- (6) For FPP ×16, use DATA [15..0]. For FPP ×8, use DATA [7..0]. DATA [31..0] are available as a user I/O pin after configuration. The state of this pin depends on the dual-purpose pin settings.

- (7) To ensure a successful configuration, send the entire configuration data to the Stratix V device. CONF\_DONE is released high when the Stratix V device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- (8) After the option bit to enable the <code>INIT\_DONE</code> pin is configured into the device, the <code>INIT\_DONE</code> goes low.

Configuration Specification Page 63

Table 54 lists the PS configuration timing parameters for Stratix V devices.

Table 54. PS Timing Parameters for Stratix V Devices

| Symbol                 | Parameter                                         | Minimum                                         | Maximum              | Units |

|------------------------|---------------------------------------------------|-------------------------------------------------|----------------------|-------|

| t <sub>CF2CD</sub>     | nCONFIG low to CONF_DONE low                      | _                                               | 600                  | ns    |

| t <sub>CF2ST0</sub>    | nCONFIG low to nSTATUS low                        | _                                               | 600                  | ns    |

| t <sub>CFG</sub>       | nCONFIG low pulse width                           | 2                                               |                      | μS    |

| t <sub>STATUS</sub>    | nstatus low pulse width                           | 268                                             | 1,506 <sup>(1)</sup> | μS    |

| t <sub>CF2ST1</sub>    | nCONFIG high to nSTATUS high                      | _                                               | 1,506 <sup>(2)</sup> | μS    |

| t <sub>CF2CK</sub> (5) | nCONFIG high to first rising edge on DCLK         | 1,506                                           |                      | μS    |

| t <sub>ST2CK</sub> (5) | nstatus high to first rising edge of DCLK         | 2                                               | _                    | μS    |

| t <sub>DSU</sub>       | DATA[] setup time before rising edge on DCLK      | 5.5                                             | _                    | ns    |

| t <sub>DH</sub>        | DATA[] hold time after rising edge on DCLK        | 0                                               |                      | ns    |

| t <sub>CH</sub>        | DCLK high time                                    | $0.45 \times 1/f_{MAX}$                         | _                    | S     |

| t <sub>CL</sub>        | DCLK low time                                     | $0.45 \times 1/f_{MAX}$                         | _                    | S     |

| t <sub>CLK</sub>       | DCLK period                                       | 1/f <sub>MAX</sub>                              |                      | S     |

| f <sub>MAX</sub>       | DCLK frequency                                    | _                                               | 125                  | MHz   |

| t <sub>CD2UM</sub>     | CONF_DONE high to user mode (3)                   | 175                                             | 437                  | μS    |

| t <sub>CD2CU</sub>     | CONF_DONE high to CLKUSR enabled                  | 4 × maximum  DCLK period                        | _                    | _     |

| t <sub>CD2UMC</sub>    | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × CLKUSR period) (4) | _                    | _     |

#### Notes to Table 54:

- (1) This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

- (2) This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

- (3) The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

- (4) To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section.

- (5) If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

#### Initialization

Table 55 lists the initialization clock source option, the applicable configuration schemes, and the maximum frequency.

Table 55. Initialization Clock Source Option and the Maximum Frequency

| Initialization Clock<br>Source | I:ONTINUIPATION SCHEMES |          | Minimum Number of Clock<br>Cycles <sup>(1)</sup> |

|--------------------------------|-------------------------|----------|--------------------------------------------------|

| Internal Oscillator            | AS, PS, FPP             | 12.5 MHz |                                                  |

| CLKUSR                         | AS, PS, FPP (2)         | 125 MHz  | 8576                                             |

| DCLK                           | PS, FPP                 | 125 MHz  |                                                  |

#### Notes to Table 55:

- $(1) \quad \text{The minimum number of clock cycles required for device initialization}.$

- (2) To enable CLKUSR as the initialization clock source, turn on the Enable user-supplied start-up clock (CLKUSR) option in the Quartus II software from the General panel of the Device and Pin Options dialog box.

Glossary Page 65

Table 58. IOE Programmable Delay for Stratix V Devices (Part 2 of 2)

| Parameter | Available Min |        | Fast Model |            | Slow Model |       |       |       |       |             |       |      |

|-----------|---------------|--------|------------|------------|------------|-------|-------|-------|-------|-------------|-------|------|

| (1)       | Settings      | Offset | Industrial | Commercial | C1         | C2    | C3    | C4    | 12    | 13,<br>13YY | 14    | Unit |

| D3        | 8             | 0      | 1.587      | 1.699      | 2.793      | 2.793 | 2.992 | 3.192 | 2.811 | 3.047       | 3.257 | ns   |

| D4        | 64            | 0      | 0.464      | 0.492      | 0.838      | 0.838 | 0.924 | 1.011 | 0.843 | 0.920       | 1.006 | ns   |

| D5        | 64            | 0      | 0.464      | 0.493      | 0.838      | 0.838 | 0.924 | 1.011 | 0.844 | 0.921       | 1.006 | ns   |

| D6        | 32            | 0      | 0.229      | 0.244      | 0.415      | 0.415 | 0.458 | 0.503 | 0.418 | 0.456       | 0.499 | ns   |

#### Notes to Table 58:

- (1) You can set this value in the Quartus II software by selecting D1, D2, D3, D5, and D6 in the Assignment Name column of Assignment Editor.

- (2) Minimum offset does not include the intrinsic delay.

### **Programmable Output Buffer Delay**

Table 59 lists the delay chain settings that control the rising and falling edge delays of the output buffer. The default delay is 0 ps.

Table 59. Programmable Output Buffer Delay for Stratix V Devices (1)

| Symbol              | Parameter                        | Typical     | Unit |

|---------------------|----------------------------------|-------------|------|

|                     |                                  | 0 (default) | ps   |

| D                   | Rising and/or falling edge delay | 25          | ps   |

| D <sub>OUTBUF</sub> |                                  | 50          | ps   |

|                     |                                  | 75          | ps   |

#### Note to Table 59:

## **Glossary**

Table 60 lists the glossary for this chapter.

Table 60. Glossary (Part 1 of 4)

| Letter | Subject                                                                                                            | Definitions                                                                                                  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| Α      |                                                                                                                    |                                                                                                              |  |  |