Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betails                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 40MHz                                                                                    |

| Connectivity               | EBI/EMI, Serial Port                                                                     |

| Peripherals                | POR, WDT                                                                                 |

| Number of I/O              | 36                                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                            |

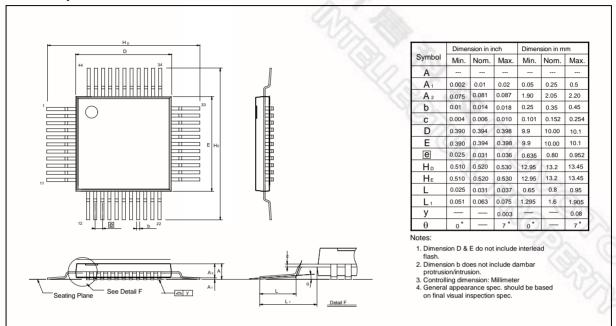

| Package / Case             | 44-BQFP                                                                                  |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w77e516a40fl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **1. GENERAL DESCRIPTION**

The W77E516 is a fast 8051 compatible microcontroller with a redesigned processor core without wasted clock and memory cycles. As a result, it executes every 8051 instruction faster than the original 8051 for the same crystal speed. Typically, the instruction executing time of W77E516 is 1.5 to 3 times faster then that of traditional 8051, depending on the type of instruction. In general, the overall performance is about 2.5 times better than the original for the same crystal speed. Giving the same throughput with lower clock speed, power consumption has been improved. Consequently, the W77E516 is a fully static CMOS design; it can also be operated at a lower crystal clock. The W77E516 contains In-System Programmable (ISP) 64 KB Flash EPROM; 4KB auxiliary Flash EPROM for loader program; operating voltage from 4.5V to 5.5V; on-chip 1 KB MOVX SRAM; three power saving modes.

### 2. FEATURES

- 8-bit CMOS microcontroller

- High speed architecture of 4 clocks/machine cycle runs up to 40 MHz

- Pin compatible with standard 80C52

- Instruction-set compatible with MCS-51

- 64KB on-chip Flash-EPROM

- Four 8-bit I/O Ports; Port 0 has internal pull-up resisters enabled by software

- One extra 4-bit I/O port and Wait State control signal (available on 44-pin PLCC/QFP package)

- Three 16-bit Timers

- 12 interrupt sources with two levels of priority

- On-chip oscillator and clock circuitry

- Two enhanced full duplex serial ports

- 64KB In-system Programmable Flash EPROM (APROM)

- 4KB Auxiliary Flash EPROM for loader program (LDROM)

- 256 bytes scratch-pad RAM

- 1KB on-chip SRAM for MOVX instruction

- Programmable Watchdog Timer

- Dual 16-bit Data Pointers

- Software programmable access cycle to external RAM/peripherals

- Packages:

- Lead Free(RoHs) DIP 40: W77E516A40DL

- Lead Free(RoHs) PLCC 44: W77E516A40PL

- Lead Free(RoHs) QFP 44: W77E516A40FL

- 3 -

# nuvoTon

- TF1: Timer 1 overflow flag: This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit.

- TR1: Timer 1 run control: This bit is set or cleared by software to turn timer/counter on or off.

- TF0: Timer 0 overflow flag: This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.

- TR0: Timer 0 run control: This bit is set or cleared by software to turn timer/counter on or off.

- IE1: Interrupt 1 edge detect: Set by hardware when an edge/level is detected on INT1. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the pin.

- IT1: Interrupt 1 type control: Set/cleared by software to specify falling edge/ low level triggered external inputs.

- IE0: Interrupt 0 edge detect: Set by hardware when an edge/level is detected on INT0. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the pin.

- IT0: Interrupt 0 type control: Set/cleared by software to specify falling edge/ low level triggered external inputs.

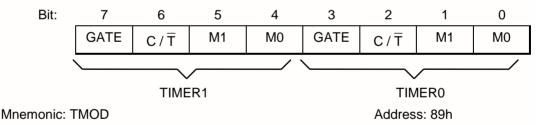

#### **Timer Mode Control**

- GATE: Gating control: When this bit is set, Timer/counter x is enabled only while INTx pin is high and TRx control bit is set. When cleared, Timer x is enabled whenever TRx control bit is set.

- C/T: Timer or Counter Select: When cleared, the timer is incremented by internal clocks. When set, the timer counts high-to-low edges of the Tx pin.

#### M1, M0: Mode Select bits:

| M1 | MO | Mode                                                                                                                                                 |

|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Mode 0: 8-bits with 5-bit prescale.                                                                                                                  |

| 0  | 1  | Mode 1: 16-bits, no prescale.                                                                                                                        |

| 1  | 0  | Mode 2: 8-bits with auto-reload from THx                                                                                                             |

| 1  | 1  | Mode 3: (Timer 0) TL0 is an 8-bit timer/counter controlled I control bits. TH0 is a 8-bit timer only controlled by Timer 1 Timer/counter is stopped. |

by the standard Timer 0 control bits. (Timer 1)

ENP: In System Programming Mode Enable. Set this be to launch the ISP mode. Device will operate ISP procedures, such as Erase, Program and Read operations, according to correlative SFRs settings. During ISP mode, device achieves ISP operations by the way of IDLE state. In the other words, device is not indeed in IDLE mode is set bit PCON.1 while ISP is enabled. Clear this bit to disable ISP mode, device get back to normal operation including IDLE state.

#### Port 2

| Bit:        | 7    | 6    | 5    | 4    | 3    | 2      | 1      | 0    |

|-------------|------|------|------|------|------|--------|--------|------|

|             | P2.7 | P2.6 | P2.5 | P2.4 | P2.3 | P2.2   | P2.1   | P2.0 |

| Mnemonic: F | 2    |      |      |      |      | Addres | s: A0h |      |

P2.7 – 0: Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides the upper address bits for accesses to external memory.

#### **Port 4 Chip-Select Polarity**

| Bit: | 7      | 6      | 5      | 4      | 3 | 2 | 1 | 0    |

|------|--------|--------|--------|--------|---|---|---|------|

|      | P43INV | P42INV | P42INV | P40INV | - | - | - | POUP |

Mnemonic: P4CSIN

Address: A2h

P4xINV: The active polarity of P4.x when set it as chip-select signal. High = Active High. Low = Active Low.

POUP: Enable Port 0 weak pull up.

#### Port 4

| Bit: | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|------|---|---|---|---|------|------|------|------|

|      | - | - | - | - | P4.3 | P4.2 | P4.1 | P4.0 |

Mnemonic: P4

Address: A5h

P4.3 – 0: Port 4 is a bi-directional I/O port with internal pull-ups. Port 4 can not use bit-addressable instruction (SETB or CLR).

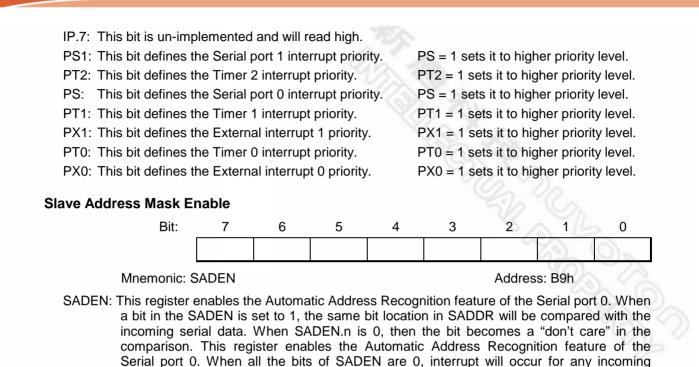

### **Interrupt Enable**

| Bit: | 7  | 6   | 5   | 4  | 3   | 2   | 1   | 0   |

|------|----|-----|-----|----|-----|-----|-----|-----|

|      | EA | ES1 | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

Mnemonic: IE

Address: A8h

EA: Global enable. Enable/disable all interrupts except for PFI.

ES1: Enable Serial Port 1 interrupt.

ET2: Enable Timer 2 interrupt.

ES: Enable Serial Port 0 interrupt.

ET1: Enable Timer 1 interrupt

## nuvoTon

EX1: Enable external interrupt 1 ET0: Enable Timer 0 interrupt EX0: Enable external interrupt 0 **Slave Address** Bit: 7 6 5 4 3 2 1 0 Mnemonic: SADDR Address: A9h SADDR: The SADDR should be programmed to the given or broadcast address for serial port 0 to which the slave processor is designated. **Slave Address 1** Bit: 2 7 6 5 3 4 **Mnemonic: SADDR1** Address: Aah SADDR1: The SADDR1 should be programmed to the given or broadcast address for serial port 1 to which the slave processor is designated. **ISP Address Low Byte** Bit: 7 6 5 4 3 2 1 0 A7 A6 Α5 A4 A3 A2 A1 A0 **Mnemonic: SFRAL** Address: Ach Low byte destination address for In System Programming operations. SFRAH and SFRAL address a specific ROM bytes for erasure, 21 escription or read. **ISP Address High Byte** Bit: 7 0 6 5 4 3 2 1 A15 A14 A13 A12 A11 A10 A9 A8 Address: Adh Mnemonic: SFRAH High byte destination address for In System Programming operations. SFRAH and SFRAL address a specific ROM bytes for erasure, 21 escription or read. **ISP Data Buffer** Bit: 5 0 7 6 4 3 2 1 D7 D6 D5 D2 D4 D3 D1 D0 **Mnemonic: SFRFD** Address: Aeh Publication Release Date: November 19, 2007 - 21 -Revision A9

### Slave Address Mask Enable 1

address.

Address: Bah

SADEN1: This register enables the Automatic Address Recognition feature of the Serial port 1. When a bit in the SADEN1 is set to 1, the same bit location in SADDR1 will be compared with the incoming serial data. When SADEN1.n is 0, then the bit becomes a "don't care" in the comparison. This register enables the Automatic Address Recognition feature of the Serial port 1. When all the bits of SADEN1 are 0, interrupt will occur for any incoming address.

### **Serial Port Control 1**

| Bit: | 7             | 6     | 5     | 4     | 3     | 2     | 1       | 0    |

|------|---------------|-------|-------|-------|-------|-------|---------|------|

|      | SM0_1/FE_1    | SM1_1 | SM2_1 | REN_1 | TB8_1 | RB8_1 | TI_1    | RI_1 |

| N    | Inemonic: SCO | N1    |       |       |       | Addre | ss: C0h |      |

SM0\_1/FE\_1: Serial port 1, Mode 0 bit or Framing Error Flag 1: The SMOD0 bit in PCON SFR determines whether this bit acts as SM0\_1 or as FE\_1, the operation of SM0\_1 is described below. When used as FE\_1, this bit will be set to indicate an invalid stop bit. This bit must be manually cleared in software to clear the FE\_1 condition.

WS: Wait State Signal Enable. Setting this bit enables the WAIT signal on P4.0. The device will sample the wait state control signal WAIT via P4.0 during MOVX instruction. This bit is time access protected.

| ТА       | REG C7H                                                                    |

|----------|----------------------------------------------------------------------------|

| WSCONREG | C2H                                                                        |

| CKCON    | REG 8EH                                                                    |

| MOV      | TA, #AAH                                                                   |

| MOV      | TA, #55H                                                                   |

| ORL      | WSCON, #10000000B; Set WS bit and stretch value = 0 to enable wait signal. |

#### **Power Management Register**

| Bit: | 7   | 6   | 5   | 4 | 3 | 2       | 19 | 0     |

|------|-----|-----|-----|---|---|---------|----|-------|

|      | CD1 | CD0 | SWB | - | - | ALE-OFF | -  | DME0  |

|      |     |     |     |   |   |         |    | Not 1 |

#### Mnemonic: PMR

Address: C4h

CD1, CD0: Clock Divide Control. These bit selects the number of clocks required to generate one machine cycle. There are three modes including divide by 4, 64 or 1024. Switching between modes must first go back divide by 4 mode. For instance, to go from 64 to 1024 clocks/machine cycle the device must first go from 64 to 4 clocks/machine cycle, and then from 4 to 1024 clocks/machine cycle.

| CD1, | CD0 | Clocks/machine Cycle |

|------|-----|----------------------|

| 0    | 0   | Reserved             |

| 0    | 1   | 4                    |

| 1    | 0   | 64                   |

| 1    | 1   | 1024                 |

- SWB: Switchback Enable. Setting this bit allows an enabled external interrupt or serial port activity to force the CD1, CD0 to divide by 4 state (0,1). The device will switch modes at the start of the jump to interrupt service routine while a external interrupt is enabled and actually recognized by micro controller. While a serial port reception, the switchback occurs at the start of the instruction following the falling edge of the start bit.

- ALEOFF: This bit disables the expression of the ALE signal on the device pin during all on-board program and data memory accesses. External memory accesses will automatically enable ALE independent of ALEOFF.

- 0 = ALE expression is enable; 1 = ALE expression is disable

- DME0: This bit determines the on-chip MOVX SRAM to be enabled or disabled. Set this bit to 1 will enable the on-chip 1KB MOVX SRAM.

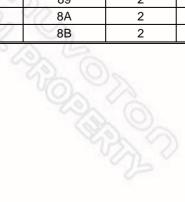

CP / RL2: Capture/Reload Select. This bit determines whether the capture or reload function will be used for timer 2. If either RCLK or TCLK is set, this bit will be ignored and the timer will function in an auto-reload mode following each overflow. If the bit is 0 then auto-reload will occur when timer 2 overflows or a falling edge is detected on T2EX pin if EXEN2 = 1. If this bit is 1, then timer 2 captures will occur when a falling edge is detected on T2EX pin if EXEN2 = 1.

### **Timer 2 Mode Control**

| Bit: | 7   | 6   | 5   | 4   | 3    | 2  | 2    | 0    |

|------|-----|-----|-----|-----|------|----|------|------|

|      | HC5 | HC4 | HC3 | HC2 | T2CR | 50 | T2OE | DCEN |

Mnemonic: T2MOD

Address: C9h

- HC5: Hardware Clear INT5 flag. Setting this bit allows the flag of external interrupt 5 to be automatically cleared by hardware while entering the interrupt service routine.

- HC4: Hardware Clear INT4 flag. Setting this bit allows the flag of external interrupt 4 to be automatically cleared by hardware while entering the interrupt service routine.

- HC3: Hardware Clear INT3 flag. Setting this bit allows the flag of external interrupt 3 to be automatically cleared by hardware while entering the interrupt service routine.

- HC3: Hardware Clear INT2 flag. Setting this bit allows the flag of external interrupt 3 to be automatically cleared by hardware while entering the interrupt service routine.

- T2CR: Timer 2 Capture Reset. In the Timer 2 Capture Mode this bit enables/disables hardware automatically reset Timer 2 while the value in TL2 and TH2 have been transferred into the capture register.

- T2OE: Timer 2 Output Enable. This bit enables/disables the Timer 2 clock out function.

- DCEN: Down Count Enable: This bit, in conjunction with the T2EX pin, controls the direction that timer 2 counts in 16-bit auto-reload mode.

### **Timer 2 Capture LSB**

| Bit: | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------|----------|----------|----------|----------|----------|----------|----------|----------|

|      | RCAP2L.7 | RCAP2L.6 | RCAP2L.5 | RCAP2L.4 | RCAP2L.3 | RCAP2L.2 | RCAP2L.1 | RCAP2L.0 |

Mnemonic: RCAP2L

Address: Cah

RCAP2L: This register is used to capture the TL2 value when a timer 2 is configured in capture mode. RCAP2L is also used as the LSB of a 16-bit reload value when timer 2 is configured in auto-reload mode.

### Timer 2 Capture MSB

| Bit:             | 7        | 6        | 5        | 4        | 3            | 2           | 1        | 0                           |  |

|------------------|----------|----------|----------|----------|--------------|-------------|----------|-----------------------------|--|

|                  | RCAP2H.7 | RCAP2H.6 | RCAP2H.5 | RCAP2H.4 | RCAP2H.3     | RCAP2H.2    | RCAP2H.1 | RCAP2H.0                    |  |

| Mnemonic: RCAP2H |          |          |          |          | Address: CBh |             |          |                             |  |

| - 29 -           |          |          |          |          | Publicatio   | n Release D |          | ber 19, 2007<br>Revision A9 |  |

| INSTRUCTION         | HEX<br>OP-CODE                       | BYTES | W77E516<br>MACHINE<br>CYCLES | W77E516<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | W77E516 VS<br>8032 SPEED<br>RATIO |

|---------------------|--------------------------------------|-------|------------------------------|----------------------------|-------------------------|-----------------------------------|

| ADD A, R6           | 2E                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADD A, R7           | 2F                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADD A, @R0          | 26                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADD A, @R1          | 27                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADD A, direct       | 25                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ADD A, #data        | 24                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ADDC A, R0          | 38                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R1          | 39                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R2          | 3A                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R3          | 3B                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R4          | 3C                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R5          | 3D                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R6          | 3E                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R7          | 3F                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, @R0         | 36                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, @R1         | 37                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, direct      | 35                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ADDC A, #data       | 34                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ACALL addr11        | 71, 91, B1,<br>11, 31, 51,<br>D1, F1 | 2     | 3                            | 12                         | 24                      | 2                                 |

| AJMP ADDR11         | 01, 21, 41,<br>61, 81, A1,<br>C1, E1 | 2     | 3                            | 12                         | 24                      | 2                                 |

| ANL A, R0           | 58                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R1           | 59                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R2           | 5A                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R3           | 5B                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R4           | 5C                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R5           | 5D                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R6           | 5E                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R7           | 5F                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, @R0          | 56                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, @R1          | 57                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, direct       | 55                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ANL A, #data        | 54                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ANL direct, A       | 52                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ANL direct, #data   | 53                                   | 3     | 3                            | 12                         | 24                      | 2                                 |

| ANL C, bit          | 82                                   | 2     | 2                            | 8                          | 24                      | 3                                 |

| ANL C, /bit         | B0                                   | 2     | 2                            | 8                          | 24                      | 3                                 |

| CJNE A, direct, rel | B5                                   | 3     | 4                            | 16                         | 24                      | 1.5                               |

Table 3. Instruction Timing for W77E516, continued

- 34 -

# ηυνοτοη

| Table | 3. Instruction | Timing for | W77E516, | continued |

|-------|----------------|------------|----------|-----------|

| INSTRUCTION      | HEX<br>OP-CODE | BYTES | W77E516<br>MACHINE<br>CYCLES | W77E516<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | W77E516 VS<br>8032 SPEED<br>RATIO |

|------------------|----------------|-------|------------------------------|----------------------------|-------------------------|-----------------------------------|

| DJNZ R4, rel     | DC             | 2     | 3                            | 12                         | 24                      | 2                                 |

| DJNZ R6, rel     | DE             | 2     | 3                            | 12                         | 24                      | 2                                 |

| DJNZ R7, rel     | DF             | 2     | 3                            | 12                         | 24                      | 2                                 |

| DJNZ direct, rel | D5             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| INC A            | 04             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R0           | 08             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R1           | 09             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R2           | 0A             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R3           | 0B             | 1     | 1                            | 4                          | 12 🗸                    | 3                                 |

| INC R4           | 0C             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R5           | 0D             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R6           | 0E             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R7           | 0F             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC @R0          | 06             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC @R1          | 07             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC direct       | 05             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| INC DPTR         | A3             | 1     | 2                            | 8                          | 24                      | 3                                 |

| JMP @A+DPTR      | 73             | 1     | 2                            | 8                          | 24                      | 3                                 |

| JZ rel           | 60             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JNZ rel          | 70             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JC rel           | 40             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JNC rel          | 50             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JB bit, rel      | 20             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| JNB bit, rel     | 30             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| JBC bit, rel     | 10             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| LCALL addr16     | 12             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| LJMP addr16      | 02             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| MUL AB           | A4             | 1     | 5                            | 20                         | 48                      | 2.4                               |

| MOV A, R0        | E8             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R1        | E9             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R2        | EA             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R3        | EB             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R4        | EC             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R5        | ED             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R6        | EE             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R7        | G EF           | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, @R0       | E6             | />1   | 1                            | 4                          | 12                      | 3                                 |

| Table 3. | Instruction | Timina  | for W77 | 7E516. | continued |

|----------|-------------|---------|---------|--------|-----------|

| Tuble 0. | moulon      | rinning | 101 111 | L010,  | oontinuou |

| INSTRUCTION     | HEX<br>OP-CODE | BYTES | W77E516<br>MACHINE<br>CYCLES | W77E516<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | W77E516 VS<br>8032 SPEED<br>RATIO |

|-----------------|----------------|-------|------------------------------|----------------------------|-------------------------|-----------------------------------|

| MOV A, direct   | E5             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV A, #data    | 74             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R0, A       | F8             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R1, A       | F9             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R2, A       | FA             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R3, A       | FB             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R4, A       | FC             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R5, A       | FD             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R6, A       | FE             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R7, A       | FF             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV R0, direct  | A8             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R1, direct  | A9             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R2, direct  | AA             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R3, direct  | AB             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R4, direct  | AC             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R5, direct  | AD             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R6, direct  | AE             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R7, direct  | AF             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R0, #data   | 78             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R1, #data   | 79             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R2, #data   | 7A             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R3, #data   | 7B             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R4, #data   | 7C             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R5, #data   | 7D             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R6, #data   | 7E             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV R7, #data   | 7F             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV @R0, A      | F6             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV @R1, A      | F7             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV @R0, direct | A6             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV @R1, direct | A7             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV @R0, #data  | 76             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV @R1, #data  | 77             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV direct, A   | F5             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV direct, R0  | 88             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV direct, R1  | 89             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV direct, R2  | 8A             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| MOV direct, R3  | 8B             | 2     | 2                            | 8                          | 12                      | 1.5                               |

#### 6.8 Reset State

Most of the SFRs and registers on the device will go to the same condition in the reset state. The Program Counter is forced to 0000h and is held there as long as the reset condition is applied. However, the reset state does not affect the on-chip RAM. The data in the RAM will be preserved during the reset. However, the stack pointer is reset to 07h, and therefore the stack contents will be lost. The RAM contents will be lost if the VDD falls below approximately 2V, as this is the minimum voltage level required for the RAM to operate normally. Therefore after a first time power on reset the RAM contents will be indeterminate. During a power fail condition, if the power falls below 2V, the RAM contents are lost. Hence it should be assumed that after a power on/fail reset, POR = 1, the RAM contents are lost.

After a reset most SFRs are cleared. Interrupts and Timers are disabled. The Watchdog timer is disabled if the reset source was a POR. The port SFRs have FFh written into them which puts the port pins in a high state. Port 0 floats as it does not have on-chip pull-ups.

| SFF    | RNAME | RESET VALUE | SFR NAME | RESET VALUE |

|--------|-------|-------------|----------|-------------|

|        | P0    | 1111111b    | IE       | 0000000b    |

|        | SP    | 00000111b   | SADDR    | 0000000b    |

|        | DPL   | 0000000b    | P3       | 11111111b   |

|        | DPH   | 0000000b    | IP       | x000000b    |

| [      | DPL1  | 0000000b    | SADEN    | 0000000b    |

| [      | DPH1  | 0000000b    | T2CON    | 0000000b    |

|        | DPS   | 0000000b    | T2MOD    | 00000x00b   |

| F      | CON   | 00xx0000b   | RCAP2L   | 0000000b    |

| Т      | CON   | 0000000b    | RCAP2H   | 0000000b    |

| Т      | MOD   | 0000000b    | TL2      | 0000000b    |

|        | TL0   | 0000000b    | TH2      | 0000000b    |

| 0      | TL1   | 0000000b    | ТА       | 11111111b   |

| 1.0    | ТНО   | 0000000b    | PSW      | 0000000b    |

| 685    | TH1   | 0000000b    | WDCON    | 0x0x0xx0b   |

| C      | KCON  | 0000001b    | ACC      | 0000000b    |

| Co The | P1    | 1111111b    | EIE      | xxx00000b   |

| S      | CON   | 0000000b    | В        | 0000000b    |

| NO.S   | BUF   | xxxxxxxb    | EIP      | xxx00000b   |

| -07    | P2    | 1111111b    | PC       | 0000000b    |

| SA     | DDR1  | 0000000b    | SADEN1   | 0000000b    |

| S      | CON1  | 0000000b    | SBUF1    | xxxxxxxb    |

| RC     | MMAP  | 01xxxxxb    | PMR      | 010xx0x0b   |

|        | EXIF  | 0000xxx0b   | STATUS   | 000x0000b   |

|        | P4    | xxxx1111b   |          |             |

### Table 6. SFR Reset Value

Publication Release Date: November 19, 2007 Revision A9

The processor responds to a valid interrupt by executing an LCALL instruction to the appropriate service routine. This may or may not clear the flag which caused the interrupt. In case of Timer interrupts, the TF0 or TF1 flags are cleared by hardware whenever the processor vectors to the appropriate timer service routine. In case of external interrupt, INT0 and INT1, the flags are cleared only if they are edge triggered. In case of Serial interrupts, the flags are not cleared by hardware. In the case of Timer 2 interrupt, the flags are not cleared by hardware. The Power-Fail interrupt PFI flag and Watchdog timer interrupt flag WDIF have to be cleared by software. The hardware LCALL behaves exactly like the software LCALL instruction. This instruction saves the Program Counter contents onto the Stack, but does not save the Program Status Word PSW. The PC is reloaded with the vector address of that interrupt which caused the LCALL. These vector address for the different sources are as follows.

| SOURCE               | VECTOR ADDRESS | SOURCE               | VECTOR ADDRESS |

|----------------------|----------------|----------------------|----------------|

| Timer 0 Overflow     | 000Bh          | External Interrupt 0 | 0003h          |

| Timer 1 Overflow     | 001Bh          | External Interrupt 1 | 0013h          |

| Timer 2 Interrupt    | 002Bh          | Serial Port          | 0023h          |

| External Interrupt 2 | 0043h          | Serial Port 1        | 003Bh          |

| External Interrupt 4 | 0053h          | External Interrupt 3 | 004Bh          |

| Watchdog Timer       | 0063h          | External Interrupt 5 | 005Bh          |

#### Table 8. Vector locations for interrupt sources

The vector table is not evenly spaced; this is to accommodate future expansions to the device family.

Execution continues from the vectored address till an RETI instruction is executed. On execution of the RETI instruction the processor pops the Stack and loads the PC with the contents at the top of the stack. The user must take care that the status of the stack is restored to what is was after the hardware LCALL, if the execution is to return to the interrupted program. The processor does not notice anything if the stack contents are modified and will proceed with execution from the address put back into PC. Note that a RET instruction would perform exactly the same process as a RETI instruction, but it would not inform the Interrupt Controller that the interrupt service routine is completed, and would leave the controller still thinking that the service routine is underway.

- 56 -

### 7. PROGRAMMABLE TIMERS/COUNTERS

The W77E516 has three 16-bit programmable timer/counters and one programmable Watchdog timer. The Watchdog timer is operationally quite different from the other two timers.

### 7.1 Timer/Counters 0 & 1

The W77E516 has two 16-bit Timer/Counters. Each of these Timer/Counters has two 8 bit registers which form the 16 bit counting register. For Timer/Counter 0 they are TH0, the upper 8 bits register, and TL0, the lower 8 bit register. Similarly Timer/Counter 1 has two 8 bit registers, TH1 and TL1. The two can be configured to operate either as timers, counting machine cycles or as counters counting external inputs.

When configured as a "Timer", the timer counts clock cycles. The timer clock can be programmed to be thought of as 1/12 of the system clock or 1/4 of the system clock. In the "Counter" mode, the register is incremented on the falling edge of the external input pin, T0 in case of Timer 0, and T1 for Timer 1. The T0 and T1 inputs are sampled in every machine cycle at C4. If the sampled value is high in one machine cycle and low in the next, then a valid high to low transition on the pin is recognized and the count register is incremented. Since it takes two machine cycles to recognize a negative transition on the pin, the maximum rate at which counting will take place is 1/24 of the master clock frequency. In either the "Timer" or "Counter" mode, the count register will be updated at C3. Therefore, in the "Timer" mode, the recognized negative transition on pin T0 and T1 can cause the count register value to be updated only in the machine cycle following the one in which the negative edge was detected.

The "Timer" or "Counter" function is selected by the "C/ $\overline{T}$ " bit in the TMOD Special Function Register. Each Timer/Counter has one selection bit for its own; bit 2 of TMOD selects the function for Timer/Counter 0 and bit 6 of TMOD selects the function for Timer/Counter 1. In addition each Timer/Counter can be set to operate in any one of four possible modes. The mode selection is done by bits M0 and M1 in the TMOD SFR.

- 58 -

# nuvoTon

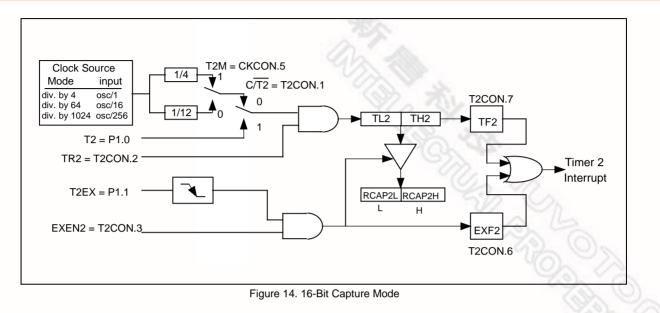

### 7.3.2 Auto-reload Mode, Counting Up

The auto-reload mode as an up counter is enabled by clearing the CP/ $\overline{RL2}$  bit in the T2CON register and clearing the DCEN bit in T2MOD register. In this mode, Timer/Counter 2 is a 16 bit up counter. When the counter rolls over from FFFFh, a reload is generated that causes the contents of the RCAP2L and RCAP2H registers to be reloaded into the TL2 and TH2 registers. The reload action also sets the TF2 bit. If the EXEN2 bit is set, then a negative transition of T2EX pin will also cause a reload. This action also sets the EXF2 bit in T2CON.

- 62 -

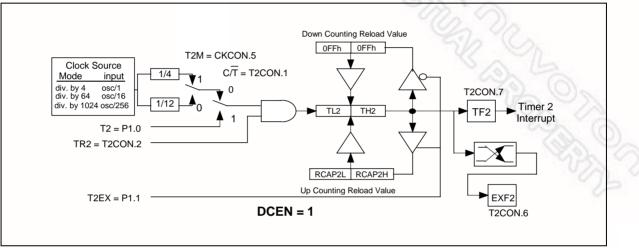

#### 7.3.3 Auto-reload Mode, Counting Up/Down

Timer/Counter 2 will be in auto-reload mode as an up/down counter if CP/RL2 bit in T2CON is cleared and the DCEN bit in T2MOD is set. In this mode, Timer/Counter 2 is an up/down counter whose direction is controlled by the T2EX pin. A 1 on this pin cause the counter to count up. An overflow while counting up will cause the counter to be reloaded with the contents of the capture registers. The next down count following the case where the contents of Timer/Counter equal the capture registers will load an FFFFh into Timer/Counter 2. In either event a reload will set the TF2 bit. A reload will also toggle the EXF2 bit. However, the EXF2 bit can not generate an interrupt while in this mode.

Figure 16. 16-Bit Auto-reload Up/Down Counter

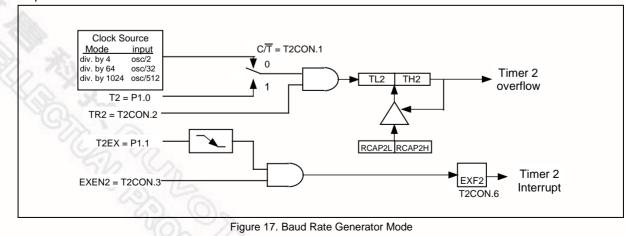

### 7.3.4 Baud Rate Generator Mode

The baud rate generator mode is enabled by setting either the RCLK or TCLK bits in T2CON register. While in the baud rate generator mode, Timer/Counter 2 is a 16 bit counter with auto reload when the count rolls over from FFFFh. However, rolling over does not set the TF2 bit. If EXEN2 bit is set, then a negative transition of the T2EX pin will set EXF2 bit in the T2CON register and cause an interrupt request.

- 63 -

Publication Release Date: November 19, 2007 Revision A9

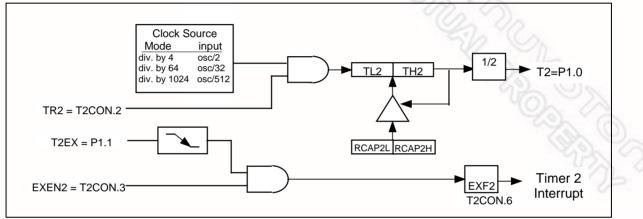

#### 7.3.5 Programmable Clock-out

Timer 2 is equipped with a new clock-out feature which outputs a 50% duty cycle clock on P1.0. It can be invoked as a programmable clock generator. To configure Timer 2 with clock-out mode, software must initiate it by setting bit T2OE = 1, C/T2 = 0 and CP/RL = 0. Setting bit TR2 will start the timer. This mode is similar to the baud rate generator mode, it will not generate an interrupt while Timer 2 overflow. So it is possible to use Timer 2 as a baud rate generator and a clock generator at the same time. The clock-out frequency is determined by the following equation:

The Clock-out Frequency = Oscillator Frequency / [4 X (65536-RCAP2H, RCAP2L)]

Figure 18. Programmable Clock-Out Mode

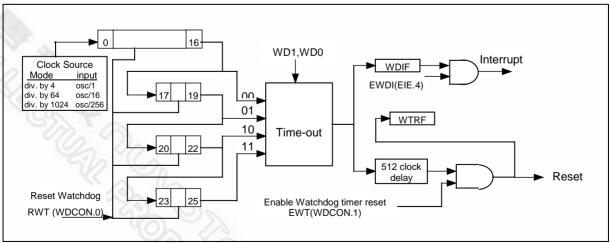

### 7.4 Watchdog Timer

The Watchdog timer is a free-running timer which can be programmed by the user to serve as a system monitor, a time-base generator or an event timer. It is basically a set of dividers that divide the system clock. The divider output is selectable and determines the time-out interval. When the time-out occurs a flag is set, which can cause an interrupt if enabled, and a system reset can also be caused if it is enabled. The interrupt will occur if the individual interrupt enable and the global enable are set. The interrupt and reset functions are independent of each other and may be used separately or together depending on the users software.

Figure 19. Watchdog Timer

- WTRF: WDCON.2 Watchdog Timer Reset flag. This bit is set whenever a watchdog reset occurs. This bit is useful for determined the cause of a reset. Software must read it, and clear it manually. A Power-fail reset will clear this bit. If EWT = 0, then this bit will not be affected by the watchdog timer.

- EWT: WDCON.1 Enable Watchdog timer Reset. This bit when set to 1 will enable the Watchdog timer reset function. Setting this bit to 0 will disable the Watchdog timer reset function, but will leave the timer running

- RWT: WDCON.0 Reset Watchdog Timer. This bit is used to clear the Watchdog timer and to restart it. This bit is self-clearing, so after the software writes 1 to it the hardware will automatically clear it. If the Watchdog timer reset is enabled, then the RWT has to be set by the user within 512 clocks of the time-out. If this is not done then a Watchdog timer reset will occur.

### 7.4.2 Clock Control

WD1, WD0: CKCON.7, CKCON.6 – Watchdog Timer Mode select bits. These two bits select the time-out interval for the watchdog timer. The reset time is 512 clock longer than the interrupt time-out value.

The default Watchdog time-out is 2<sup>17</sup> clocks, which is the shortest time-out period. The EWT, WDIF and RWT bits are protected by the Timed Access procedure. This prevents software from accidentally enabling or disabling the watchdog timer. More importantly, it makes it highly improbable that errant code can enable or disable the watchdog timer.

### 7.5 Serial Port

Serial port in the W77E516 is a full duplex port. The W77E516 provides the user with additional features such as the Frame Error Detection and the Automatic Address Recognition. The serial ports are capable of synchronous as well as asynchronous communication. In Synchronous mode the W77E516 generates the clock and operates in a half duplex mode. In the asynchronous mode, full duplex operation is available. This means that it can simultaneously transmit and receive data. The transmit register and the receive buffer are both addressed as SBUF Special Function Register. However any write to SBUF will be to the transmit register, while a read from SBUF will be from the receive buffer register. The serial port can operate in four different modes as described below.

### 7.5.1 Mode 0

This mode provides synchronous communication with external devices. In this mode serial data is transmitted and received on the RXD line. TXD is used to transmit the shift clock. The TxD clock is provided by the W77E516 whether the device is transmitting or receiving. This mode is therefore a half duplex mode of serial communication. In this mode, 8 bits are transmitted or received per frame. The LSB is transmitted/received first. The baud rate is fixed at 1/12 or 1/4 of the oscillator frequency. This baud rate is determined by the SM2 bit (SCON.5). When this bit is set to 0, then the serial port runs at 1/12 of the clock. When set to 1, the serial port runs at 1/4 of the clock. This additional facility of programmable baud rate in mode 0 is the only difference between the standard 8051 and the W77E516.

The functional block diagram is shown below. Data enters and leaves the Serial port on the RxD line. The TxD line is used to output the shift clock. The shift clock is used to shift data into and out of the

### **10. ELECTRICAL CHARACTERISTICS**

### **10.1 Absolute Maximum Ratings**

| PARAMETER             | SYMBOL    | CONDITION | RATING   | UNIT |

|-----------------------|-----------|-----------|----------|------|

| DC Power Supply       | VDD – VSS | -0.3      | +7.0     | V    |

| Input Voltage         | VIN       | Vss -0.3  | VDD +0.3 | V    |

| Operating Temperature | ТА        | 0         | +70      | °C   |

| Storage Temperatute   | Tst       | -55       | +150     | °C   |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

### **10.2 DC Characteristics**

(VDD–Vss = 5V  $\pm$ 10%, TA = 25°C, Fosc = 20 MHz, unless otherwise specified.)

|  | PARAMETER                                     | SYM.    | SPECIFICATION |          |      | TEST CONDITIONS               |

|--|-----------------------------------------------|---------|---------------|----------|------|-------------------------------|

|  | PARAMETER                                     | 5 T WI. | MIN.          | MAX.     | UNIT | TEST CONDITIONS               |

|  | Operating Voltage                             | Vdd     | 4.5           | 5.5      | V    | 4                             |

|  | Operating Current                             | IDD     | -             | 50       | mA   | No load<br>VDD = RST = 5.5V   |

|  | Idle Current                                  | lidle   | -             | 24       | mA   | Idle mode<br>VDD = 5.5V       |

|  | Power Down Current                            | IPWDN   | -             | 50       | μA   | Power-down mode<br>VDD = 5.5V |

|  | Input Current<br>P1, P2, P3                   | lin1    | -50           | +10      | μΑ   | VDD = 5.5V<br>VIN = 0V or VDD |

|  | Input Current<br>RST <sup>[*1]</sup>          | lin2    | -10           | +300     | μΑ   | VDD = 5.5V<br>0 < VIN < VDD   |

|  | Input Leakage Current<br>P0, EA               | Ilk     | -10           | +10      | μA   | Vdd = 5.5V<br>0V < Vin < Vdd  |

|  | Logic 1 to 0 Transition Current<br>P1, P2, P3 | ITL[*4] | -500          | -200     | μA   | VDD = 5.5V<br>VIN = 2.0V      |

|  | Input Low Voltage<br>P0, P1, P2, P3, EA       | VIL1    | 0             | 0.8      | V    | VDD = 4.5V                    |

|  | Input Low Voltage<br>RST <sup>[*1]</sup>      | VIL2    | 0             | 0.8      | V    | VDD = 4.5V                    |

|  | Input Low Voltage<br>XTAL1 <sup>[*3]</sup>    | VIL3    | 0             | 0.8      | V    | VDD = 4.5V                    |

|  | Input High Voltage<br>P0, P1, P2, P3, EA      | VIH1    | 2.4           | VDD +0.2 | V    | VDD = 5.5V                    |

|  | Input High Voltage<br>RST                     | VIH2    | 3.5           | VDD +0.2 | V    | VDD = 5.5V                    |

|  | Input High Voltage<br>XTAL1 <sup>[3]</sup>    | VIH3    | 3.5           | VDD +0.2 | V    | VDD = 5.5V                    |

# nuvoTon

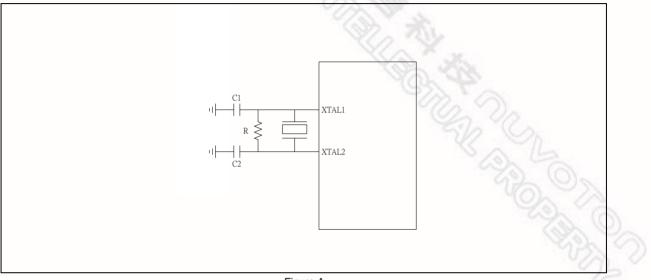

### **12. TYPICAL APPLICATION CIRCUITS**

### 12.1 Crystal connections

#### Figure A

| CRYSTAL | C1  | C2  | R    |

|---------|-----|-----|------|

| 16 MHz  | 30P | 30P | -    |

| 24 MHz  | 15P | 15P | -    |

| 33 MHz  | 5P  | 5P  | 4.7K |

| 40 MHz  | 1P  | 1P  | 3.3K |

The above table shows the reference values for crystal applications.

Note: C1, C2, R components refer to Figure A.

# nuvoTon

### 13.3 44-pin QFP