Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Package / Case Supplier Device Package | 16-TSSOP (0.173", 4.40mm Width) PG-TSSOP-16-8 |

|----------------------------------------|-----------------------------------------------|

| Mounting Type                          | Surface Mount                                 |

| Operating Temperature                  | -40°C ~ 105°C (TA)                            |

| Oscillator Type                        | Internal                                      |

| Data Converters                        | A/D 11x12b                                    |

| Voltage - Supply (Vcc/Vdd)             | 1.8V ~ 5.5V                                   |

| RAM Size                               | 16K x 8                                       |

| EEPROM Size                            | -                                             |

| Program Memory Type                    | FLASH                                         |

| Program Memory Size                    | 8KB (8K x 8)                                  |

| Number of I/O                          | 11                                            |

| Peripherals                            | Brown-out Detect/Reset, I2S, POR, PWM, WDT    |

| Connectivity                           | I <sup>2</sup> C, LINbus, SPI, UART/USART     |

| Speed                                  | 32MHz                                         |

| Core Size                              | 32-Bit Single-Core                            |

| Core Processor                         | ARM® Cortex®-M0                               |

| Product Status                         | Active                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XMC1300 AB-Step

Microcontroller Series for Industrial Applications

XMC1000 Family

ARM® Cortex®-M0 32-bit processor core

Data Sheet V1.9 2017-03

Microcontrollers

# **Summary of Features**

Configurable pad hysteresis

#### **On-Chip Debug Support**

- Support for debug features: 4 breakpoints, 2 watchpoints

- Various interfaces: ARM serial wire debug (SWD), single pin debug (SPD)

# 1.1 Ordering Information

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. The code "XMC1<DDD>-<Z><PPP><T><FFFF>" identifies:

- <DDD> the derivatives function set

- <Z> the package variant

- T: TSSOP

- Q: VQFN

- <PPP> package pin count

- <T> the temperature range:

- F: -40°C to 85°C

- X: -40°C to 105°C

- <FFFF> the Flash memory size.

For ordering codes for the XMC1300 please contact your sales representative or local distributor.

This document describes several derivatives of the XMC1300 series, some descriptions may not apply to a specific product. Please see **Table 1**.

For simplicity the term XMC1300 is used for all derivatives throughout this document.

# 1.2 Device Types

These device types are available and can be ordered through Infineon's direct and/or distribution channels.

Table 1 Synopsis of XMC1300 Device Types

| Derivative        | Package       | Flash<br>Kbytes | SRAM<br>Kbytes |

|-------------------|---------------|-----------------|----------------|

| XMC1301-T016F0008 | PG-TSSOP-16-8 | 8               | 16             |

| XMC1301-T016F0016 | PG-TSSOP-16-8 | 16              | 16             |

| XMC1301-T016F0032 | PG-TSSOP-16-8 | 32              | 16             |

| XMC1301-T016X0008 | PG-TSSOP-16-8 | 8               | 16             |

| XMC1301-T016X0016 | PG-TSSOP-16-8 | 16              | 16             |

| XMC1302-T016X0008 | PG-TSSOP-16-8 | 8               | 16             |

## **Summary of Features**

# 1.3 Device Type Features

The following table lists the available features per device type.

Table 2 Features of XMC1300 Device Types<sup>1)</sup>

| Derivative   | ADC channel | ACMP | BCCU | MATH |

|--------------|-------------|------|------|------|

| XMC1301-T016 | 11          | 2    | -    | -    |

| XMC1302-T016 | 11          | 2    | 1    | 1    |

| XMC1302-T028 | 14          | 3    | 1    | 1    |

| XMC1301-T038 | 16          | 3    | -    | -    |

| XMC1302-T038 | 16          | 3    | 1    | 1    |

| XMC1301-Q024 | 13          | 3    | -    | -    |

| XMC1302-Q024 | 13          | 3    | 1    | 1    |

| XMC1301-Q040 | 16          | 3    | -    | -    |

| XMC1302-Q040 | 16          | 3    | 1    | 1    |

<sup>1)</sup> Features that are not included in this table are available in all the derivatives

Table 3 ADC Channels 1)

| Package     | VADC0 G0 | VADC0 G1     |

|-------------|----------|--------------|

| PG-TSSOP-16 | CH0CH5   | CH0CH4       |

| PG-TSSOP-28 | CH0CH7   | CH0 CH4, CH7 |

| PG-TSSOP-38 | CH0CH7   | CH0CH7       |

| PG-VQFN-24  | CH0CH7   | CH0CH4       |

| PG-VQFN-40  | CH0CH7   | CH0CH7       |

<sup>1)</sup> Some pins in a package may be connected to more than one channel. For the detailed mapping see the Port I/O Function table.

# 1.4 Chip Identification Number

The Chip Identification Number allows software to identify the marking. It is a 8 words value with the most significant 7 words stored in Flash configuration sector 0 (CS0) at address location:  $1000~0F00_H~(MSB)$  -  $1000~0F1B_H~(LSB)$ . The least significant word and most significant word of the Chip Identification Number are the value of registers DBGROMID and IDCHIP, respectively.

# 2 General Device Information

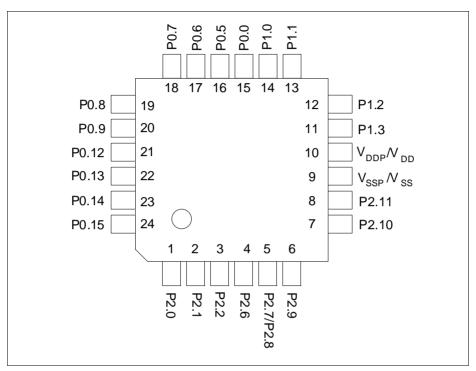

This section summarizes the logic symbols and package pin configurations with a detailed list of the functional I/O mapping.

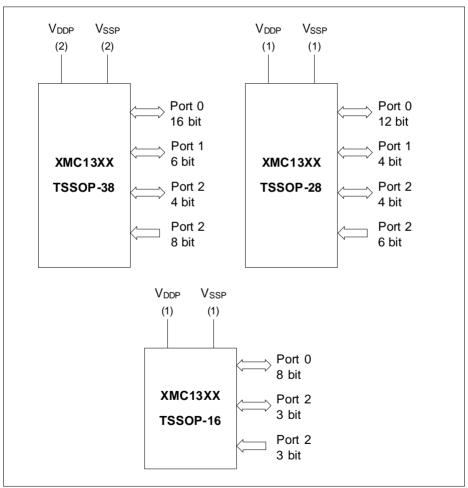

# 2.1 Logic Symbols

Figure 2 XMC1300 Logic Symbol for TSSOP-38, TSSOP-28 and TSSOP-16

Subject to Agreement on the Use of Product Information

Figure 7 XMC1300 PG-VQFN-24 Pin Configuration (top view)

Table 6 Package Pin Mapping (cont'd)

|          |            |             |             | ,          |             |                  |       |

|----------|------------|-------------|-------------|------------|-------------|------------------|-------|

| Function | VQFN<br>40 | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24 | TSSOP<br>16 | Pad<br>Type      | Notes |

| P0.7     | 30         | 24          | 17          | 18         | 10          | STD_IN<br>OUT    |       |

| P0.8     | 33         | 27          | 18          | 19         | 11          | STD_IN<br>OUT    |       |

| P0.9     | 34         | 28          | 19          | 20         | 12          | STD_IN<br>OUT    |       |

| P0.10    | 35         | 29          | 20          | -          | -           | STD_IN<br>OUT    |       |

| P0.11    | 36         | 30          | -           | -          | -           | STD_IN<br>OUT    |       |

| P0.12    | 37         | 31          | 21          | 21         | -           | STD_IN<br>OUT    |       |

| P0.13    | 38         | 32          | 22          | 22         | -           | STD_IN<br>OUT    |       |

| P0.14    | 39         | 33          | 23          | 23         | 13          | STD_IN<br>OUT    |       |

| P0.15    | 40         | 34          | 24          | 24         | 14          | STD_IN<br>OUT    |       |

| P1.0     | 22         | 16          | 12          | 14         | -           | High<br>Current  |       |

| P1.1     | 21         | 15          | 11          | 13         | -           | High<br>Current  |       |

| P1.2     | 20         | 14          | 10          | 12         | -           | High<br>Current  |       |

| P1.3     | 19         | 13          | 9           | 11         | -           | High<br>Current  |       |

| P1.4     | 18         | 12          | -           | -          | -           | High<br>Current  |       |

| P1.5     | 17         | 11          | -           | -          | -           | High<br>Current  |       |

| P1.6     | 16         | -           | -           | -          | -           | STD_IN<br>OUT    |       |

| P2.0     | 1          | 35          | 25          | 1          | 15          | STD_IN<br>OUT/AN |       |

# 2.2.3 Hardware Controlled I/O Function Description

The following general building block is used to describe the hardware I/O and pull control functions of each PORT pin:

Table 8 Hardware Controlled I/O Function Description

| Function | Outputs  | Inputs   | Pull Control |          |  |

|----------|----------|----------|--------------|----------|--|

|          | HWO0     | HWI0     | HW0_PD       | HW0_PU   |  |

| P0.0     | MODB.OUT | MODB.INA |              |          |  |

| Pn.y     |          |          | MODC.OUT     | MODC.OUT |  |

By Pn\_HWSEL, it is possible to select between different hardware "masters" (HWO0/HWI0, HWO1/HWI1). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers. Additional hardware signals HW0\_PD/HW1\_PD and HW0\_PU/HW1\_PU controlled by the peripherals can be used to control the pull devices of the pin.

Please refer to the **Hardware Controlled I/O Functions** table for the complete hardware I/O and pull control function mapping.

| Function | Outputs         | Outputs        |                |      |                 |               | Inputs                  |               |                 |                 |              |                    |                    |                    |       |       |       |

|----------|-----------------|----------------|----------------|------|-----------------|---------------|-------------------------|---------------|-----------------|-----------------|--------------|--------------------|--------------------|--------------------|-------|-------|-------|

|          | ALT1            | ALT2           | ALT3           | ALT4 | ALT5            | ALT6          | ALT7                    | Input         | Input           | Input           | Input        | Input              | Input              | Input              | Input | Input | Input |

| P2.6     |                 |                |                |      |                 |               |                         | ACMP1.I<br>NN | VADC0.<br>G0CH0 |                 | ERU0.2A<br>1 |                    |                    | USICO_C<br>H1.DX5D |       |       |       |

| P2.7     |                 |                |                |      |                 |               |                         | ACMP1.I<br>NP | VADC0.<br>G1CH1 |                 | ERU0.3A      |                    |                    | USICO_C<br>H1.DX4D |       |       |       |

| P2.8     |                 |                |                |      |                 |               |                         | ACMP0.I<br>NN | VADC0.<br>G0CH1 | VADC0.<br>G1CH0 | ERU0.3B      |                    |                    | USICO_C<br>H1.DX5C |       |       |       |

| P2.9     |                 |                |                |      |                 |               |                         | ACMP0.I<br>NP | VADC0.<br>G0CH2 | VADC0.<br>G1CH4 | ERU0.3B<br>0 |                    |                    | USICO_C<br>H1.DX4B |       |       |       |

| P2.10    | ERU0.<br>PDOUT1 | CCU40.<br>OUT2 | ERU0.<br>GOUT1 |      | CCU80.<br>OUT30 | ACMP0.<br>OUT | USICO_C<br>H1.DOUT<br>0 |               | VADC0.<br>G0CH3 | VADC0.<br>G1CH2 | ERU0.2B<br>0 |                    | USICO_C<br>H0.DX4C |                    |       |       |       |

| P2.11    | ERU0.<br>PDOUT0 | CCU40.<br>OUT3 | ERU0.<br>GOUT0 |      | CCU80.<br>OUT31 |               | USIC0_C<br>H1.DOUT<br>0 |               | VADC0.<br>G0CH4 | VADC0.<br>G1CH3 | ERU0.2B<br>1 | USICO_C<br>H1.DX0E | USIC0_C<br>H1.DX1E |                    |       |       |       |

# XMC1300 AB-Step XMC1000 Family

| Function | Outputs |                 | Inputs |                 | Pull Control |            |            |            |  |  |

|----------|---------|-----------------|--------|-----------------|--------------|------------|------------|------------|--|--|

|          | HWO0    | HWO1            | HWI0   | HWI1            | HW0_PD       | HW0_PU     | HW1_PD     | HW1_PU     |  |  |

| 20.0     |         |                 |        |                 |              |            |            |            |  |  |

| P0.1     |         |                 |        |                 |              |            |            |            |  |  |

| 20.2     |         |                 |        |                 |              |            |            |            |  |  |

| 20.3     |         |                 |        |                 |              |            |            |            |  |  |

| 20.4     |         |                 |        |                 |              |            |            |            |  |  |

| 0.5      |         |                 |        |                 |              |            |            |            |  |  |

| 20.6     |         |                 |        |                 |              |            |            |            |  |  |

| 90.7     |         |                 |        |                 |              |            |            |            |  |  |

| P0.8     |         |                 |        |                 |              |            |            |            |  |  |

| 20.9     |         |                 |        |                 |              |            |            |            |  |  |

| P0.10    |         |                 |        |                 |              |            |            |            |  |  |

| 90.11    |         |                 |        |                 |              |            |            |            |  |  |

| P0.12    |         |                 |        |                 |              |            |            |            |  |  |

| P0.13    |         |                 |        |                 |              |            |            |            |  |  |

| P0.14    |         |                 |        |                 |              |            |            |            |  |  |

| P0.15    |         |                 |        |                 |              |            |            |            |  |  |

| 21.0     |         | USIC0_CH0.DOUT0 |        | USIC0_CH0.HWIN0 | BCCU0.OUT2   | BCCU0.OUT2 |            |            |  |  |

| P1.1     |         | USIC0_CH0.DOUT1 |        | USIC0_CH0.HWIN1 | BCCU0.OUT3   | BCCU0.OUT3 |            |            |  |  |

| 21.2     |         | USIC0_CH0.DOUT2 |        | USIC0_CH0.HWIN2 | BCCU0.OUT4   | BCCU0.OUT4 |            |            |  |  |

| 21.3     |         | USIC0_CH0.DOUT3 |        | USIC0_CH0.HWIN3 | BCCU0.OUT5   | BCCU0.OUT5 |            |            |  |  |

| P1.4     |         |                 |        |                 | BCCU0.OUT6   | BCCU0.OUT6 |            |            |  |  |

| P1.5     |         |                 |        |                 | BCCU0.OUT7   | BCCU0.OUT7 |            |            |  |  |

| P1.6     |         |                 |        |                 | BCCU0.OUT8   | BCCU0.OUT8 |            |            |  |  |

| 2.0      |         |                 |        |                 | BCCU0.OUT1   | BCCU0.OUT1 |            |            |  |  |

| P2.1     |         |                 |        |                 | BCCU0.OUT6   | BCCU0.OUT6 |            |            |  |  |

| 2.2      |         |                 |        |                 | BCCU0.OUT0   | BCCU0.OUT0 | CCU40.OUT3 | CCU40.OUT3 |  |  |

| 2.3      |         |                 |        |                 | ACMP2.OUT    | ACMP2.OUT  |            |            |  |  |

| P2.4     |         |                 |        |                 | BCCU0.OUT8   | BCCU0.OUT8 |            |            |  |  |

| P2.5     |         |                 |        |                 | ACMP1.OUT    | ACMP1.OUT  |            |            |  |  |

# 3 Electrical Parameters

This section provides the electrical parameters which are implementation-specific for the XMC1300.

#### 3.1 General Parameters

# 3.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XMC1300 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

- CC

- Such parameters indicate **C**ontroller **C**haracteristics, which are distinctive feature of the XMC1300 and must be regarded for a system design.

- SR

- Such parameters indicate **S**ystem Requirements, which must be provided by the application system in which the XMC1300 is designed in.

# 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 11 Absolute Maximum Rating Parameters

| Parameter                                                            | Symb                 | Symbol |      | Va   | lues                          | Unit | Note /             |

|----------------------------------------------------------------------|----------------------|--------|------|------|-------------------------------|------|--------------------|

|                                                                      |                      |        | Min  | Тур. | Max.                          |      | Test Cond ition    |

| Junction temperature                                                 | $T_{J}$              | SR     | -40  | _    | 115                           | °C   | _                  |

| Storage temperature                                                  | $T_{ST}$             | SR     | -40  | -    | 125                           | °C   | _                  |

| Voltage on power supply pin with respect to $V_{\rm SSP}$            | $V_{DDP}$            | SR     | -0.3 | _    | 6                             | V    | -                  |

| Voltage on digital pins with respect to $V_{\rm SSP}^{\rm 1)}$       | $V_{IN}$             | SR     | -0.5 | _    | $V_{\rm DDP}$ + 0.5 or max. 6 | V    | whichever is lower |

| Voltage on P2 pins with respect to $V_{\rm SSP}^{\rm 2)}$            | $V_{INP2}$           | SR     | -0.3 | _    | $V_{\rm DDP}$ + 0.3           | V    | _                  |

| Voltage on analog input pins with respect to $V_{\rm SSP}$           | $V_{AIN} \ V_{AREF}$ | SR     | -0.5 | _    | $V_{\rm DDP}$ + 0.5 or max. 6 | V    | whichever is lower |

| Input current on any pin during overload condition                   | $I_{IN}$             | SR     | -10  | _    | 10                            | mA   | _                  |

| Absolute maximum sum of all input currents during overload condition | $\Sigma I_{IN}$      | SR     | -50  | _    | +50                           | mA   | _                  |

<sup>1)</sup> Excluding port pins P2.[1,2,6,7,8,9,11].

<sup>2)</sup> Applicable to port pins P2.[1,2,6,7,8,9,11].

# 3.2.2 Analog to Digital Converters (ADC)

Table 17 shows the Analog to Digital Converter (ADC) characteristics.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 17 ADC Characteristics (Operating Conditions apply)<sup>1)</sup>

| Parameter                                           | Symbol                     | '                       | /alues | ;                       | Unit | Note / Test Condition                               |

|-----------------------------------------------------|----------------------------|-------------------------|--------|-------------------------|------|-----------------------------------------------------|

|                                                     |                            | Min.                    | Тур.   | Max.                    |      |                                                     |

| Supply voltage range (internal reference)           | $V_{ m DD\_int}{ m SR}$    | 2.0                     | _      | 3.0                     | V    | $SHSCFG.AREF = 11_B$<br>CALCTR.CALGNSTC<br>$= 0C_H$ |

|                                                     |                            | 3.0                     | -      | 5.5                     | V    | SHSCFG.AREF = 10 <sub>B</sub>                       |

| Supply voltage range (external reference)           | $V_{ m DD\_ext} \ { m SR}$ | 3.0                     | _      | 5.5                     | V    | SHSCFG.AREF = 00 <sub>B</sub>                       |

| Analog input voltage range                          | $V_{AIN}SR$                | V <sub>SSP</sub> - 0.05 | _      | V <sub>DDP</sub> + 0.05 | V    |                                                     |

| Auxiliary analog reference ground                   | $V_{REFGND}$ SR            | V <sub>SSP</sub> - 0.05 | _      | 1.0                     | V    | G0CH0                                               |

|                                                     |                            | V <sub>SSP</sub> - 0.05 | _      | 0.2                     | V    | G1CH0                                               |

| Internal reference<br>voltage (full scale<br>value) | V <sub>REFINT</sub> CC     | 5                       |        |                         | V    |                                                     |

| Switched capacitance of an analog input             | $C_{AINS}CC$               | _                       | 1.2    | 2                       | pF   | GNCTRxz.GAINy = 00 <sub>B</sub> (unity gain)        |

|                                                     |                            | _                       | 1.2    | 2                       | pF   | GNCTRxz.GAINy=01 <sub>B</sub> (gain g1)             |

|                                                     |                            | _                       | 4.5    | 6                       | pF   | $GNCTRxz.GAINy = 10_B$ (gain g2)                    |

|                                                     |                            | _                       | 4.5    | 6                       | pF   | GNCTRxz.GAINy=11 <sub>B</sub> (gain g3)             |

| Total capacitance of an analog input                | $C_{AINT}CC$               | _                       | _      | 10                      | pF   |                                                     |

| Total capacitance of the reference input            | $C_{AREFT}$                | _                       | _      | 10                      | pF   |                                                     |

Subject to Agreement on the Use of Product Information

Table 17 ADC Characteristics (Operating Conditions apply)<sup>1)</sup> (cont'd)

| Parameter                                       | Symbol                   | '    | /alues | ;                       | Unit      | Note / Test Condition                                                |

|-------------------------------------------------|--------------------------|------|--------|-------------------------|-----------|----------------------------------------------------------------------|

|                                                 |                          | Min. | Тур.   | Max.                    |           |                                                                      |

| Maximum sample rate in 8-bit mode <sup>3)</sup> | $f_{\rm C8}$ CC          | _    | _      | f <sub>ADC</sub> / 38.5 | -         | 1 sample pending                                                     |

|                                                 |                          | _    | -      | f <sub>ADC</sub> / 54.5 | -         | 2 samples pending                                                    |

| RMS noise 4)                                    | EN <sub>RMS</sub>        | _    | 1.5    | _                       | LSB<br>12 | DC input,<br>$V_{\rm DD}$ = 5.0 V,<br>$V_{\rm AIN}$ = 2.5 V,<br>25°C |

| DNL error                                       | EA <sub>DNL</sub> CC     | _    | ±2.0   | _                       | LSB<br>12 |                                                                      |

| INL error                                       | EA <sub>INL</sub> CC     | _    | ±4.0   | _                       | LSB<br>12 |                                                                      |

| Gain error with external reference              | EA <sub>GAIN</sub> CC    | _    | ±0.5   | _                       | %         | SHSCFG.AREF = $00_B$ (calibrated)                                    |

| Gain error with internal reference 5)           | EA <sub>GAIN</sub><br>CC | _    | ±3.6   | _                       | %         | SHSCFG.AREF = 1X <sub>B</sub> (calibrated),<br>-40°C - 105°C         |

|                                                 |                          | _    | ±2.0   | _                       | %         | SHSCFG.AREF = $1X_B$ (calibrated), $0^{\circ}C - 85^{\circ}C$        |

| Offset error                                    | EA <sub>OFF</sub> CC     | _    | ±8.0   | _                       | mV        | Calibrated, $V_{\rm DD}$ = 5.0 V                                     |

<sup>1)</sup> The parameters are defined for ADC clock frequency  $f_{\rm SH}$  = 32MHz, SHSCFG.DIVS = 0000<sub>B</sub>. Usage of any other frequencies may affect the ADC performance.

<sup>2)</sup> No pending samples assumed, excluding sampling time and calibration.

<sup>3)</sup> Includes synchronization and calibration (average of gain and offset calibration).

<sup>4)</sup> This parameter can also be defined as an SNR value: SNR[dB] =  $20 \times \log(A_{\rm MAXeff} / N_{\rm RMS})$ . With  $A_{\rm MAXeff} = 2^{\rm N} / 2$ , SNR[dB] =  $20 \times \log$  (  $2048 / N_{\rm RMS}$ ) [N = 12].  $N_{\rm RMS} = 1.5$  LSB12, therefore, equals SNR =  $20 \times \log$  (2048 / 1.5) = 62.7 dB.

<sup>5)</sup> Includes error from the reference voltage.

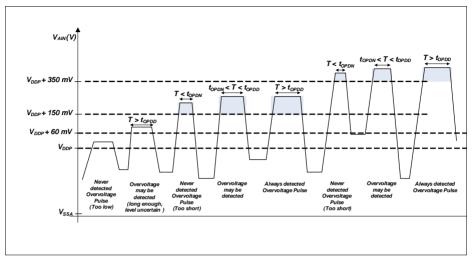

Figure 13 ORC Detection Ranges

# 3.2.4 Analog Comparator Characteristics

Table 19 below shows the Analog Comparator characteristics.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 19 Analog Comparator Characteristics (Operating Conditions apply)

| Parameter                          | Symbol           | Li | mit Val | ues   | Unit                    | Notes/ |                                                                       |

|------------------------------------|------------------|----|---------|-------|-------------------------|--------|-----------------------------------------------------------------------|

|                                    |                  |    | Min.    | Тур.  | Max.                    |        | Test Conditions                                                       |

| Input Voltage                      | $V_{CMP}$        | SR | -0.05   | -     | V <sub>DDP</sub> + 0.05 | V      |                                                                       |

| Input Offset                       | $V_{CMPOFF}$     | CC | _       | +/-3  | _                       | mV     | High power mode $\Delta~V_{\rm CMP}$ < 200 mV                         |

|                                    |                  |    | _       | +/-20 | _                       | mV     | Low power mode $\Delta~V_{\rm CMP}$ < 200 mV                          |

| Propagation<br>Delay <sup>1)</sup> | $t_{PDELAY}$     | CC | _       | 25    | _                       | ns     | High power mode, $\Delta~V_{\rm CMP}$ = 100 mV                        |

|                                    |                  |    | _       | 80    | _                       | ns     | High power mode, $\Delta~V_{\rm CMP}$ = 25 mV                         |

|                                    |                  |    | _       | 250   | _                       | ns     | Low power mode, $\Delta V_{\rm CMP}$ = 100 mV                         |

|                                    |                  |    | _       | 700   | _                       | ns     | Low power mode, $\Delta$ $V_{\rm CMP}$ = 25 mV                        |

| Current<br>Consumption             | $I_{ACMP}$       | CC | _       | 100   | _                       | μΑ     | First active ACMP in high power mode, $\Delta V_{\rm CMP} >$ 30 mV    |

|                                    |                  |    | _       | 66    | -                       | μΑ     | Each additional ACMP in high power mode, $\Delta V_{\rm CMP}$ > 30 mV |

|                                    |                  |    | _       | 10    | -                       | μΑ     | First active ACMP in low power mode                                   |

|                                    |                  |    | _       | 6     | -                       | μА     | Each additional<br>ACMP in low power<br>mode                          |

| Input Hysteresis                   | $V_{HYS}$        | CC | -       | +/-15 | _                       | mV     |                                                                       |

| Filter Delay <sup>1)</sup>         | $t_{\sf FDELAY}$ | CC | -       | 5     | _                       | ns     |                                                                       |

<sup>1)</sup> Total Analog Comparator Delay is the sum of Propagation Delay and Filter Delay.

# 3.2.5 Temperature Sensor Characteristics

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 20 Temperature Sensor Characteristics

| Parameter                     | Symbol            | Values |      |      | Unit | Note /                                                      |

|-------------------------------|-------------------|--------|------|------|------|-------------------------------------------------------------|

|                               |                   | Min.   | Тур. | Max. |      | Test Condition                                              |

| Measurement time              | t <sub>M</sub> CC | -      | _    | 10   | ms   |                                                             |

| Temperature sensor range      | $T_{\rm SR}$ SR   | -40    | _    | 115  | °C   |                                                             |

| Sensor Accuracy <sup>1)</sup> | $T_{TSAL}CC$      | -6     | _    | 6    | °C   | T <sub>J</sub> > 20°C                                       |

|                               |                   | -10    | _    | 10   | °C   | $0^{\circ}\text{C} \le T_{\text{J}} \le 20^{\circ}\text{C}$ |

|                               |                   | -      | -/+8 | _    | °C   | $T_{\rm J}$ < 0°C                                           |

| Start-up time after enabling  | $t_{TSSTE}  SR$   | _      | -    | 15   | μS   |                                                             |

<sup>1)</sup> The temperature sensor accuracy is independent of the supply voltage.

Table 30 USIC SSC Slave Mode Timing

| Parameter                                                                           | Symbol          |    | Values |      |      | Unit | Note /         |

|-------------------------------------------------------------------------------------|-----------------|----|--------|------|------|------|----------------|

|                                                                                     |                 |    | Min.   | Тур. | Max. |      | Test Condition |

| DX1 slave clock period                                                              | $t_{CLK}$       | SR | 125    | _    | _    | ns   |                |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>         | t <sub>10</sub> | SR | 10     | _    | -    | ns   |                |

| Select input DX2 hold after last clock input DX1 receive edge <sup>1)</sup>         | t <sub>11</sub> | SR | 10     | _    | _    | ns   |                |

| Receive data input DX0/DX[5:3] setup time to shift clock receive edge <sup>1)</sup> | t <sub>12</sub> | SR | 10     | _    | _    | ns   |                |

| Data input DX0/DX[5:3] hold time from clock input DX1 receive edge <sup>1)</sup>    | t <sub>13</sub> | SR | 10     | _    | _    | ns   |                |

| Data output DOUT[3:0] valid time                                                    | t <sub>14</sub> | СС | -      | _    | 80   | ns   |                |

<sup>1)</sup> These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

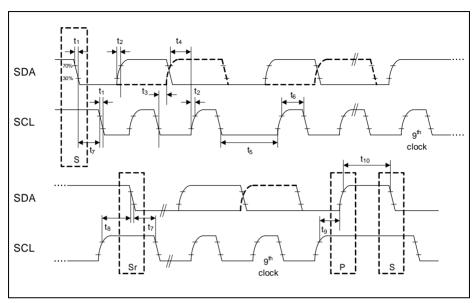

Table 32 USIC IIC Fast Mode Timing<sup>1)</sup>

| Parameter                                        | Symbol                   |                            | Values | 6    | Unit | Note /<br>Test Condition |

|--------------------------------------------------|--------------------------|----------------------------|--------|------|------|--------------------------|

|                                                  |                          | Min.                       | Тур.   | Max. |      |                          |

| Fall time of both SDA and SCL                    | t <sub>1</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                          |

| Rise time of both SDA and SCL                    | t <sub>2</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                          |

| Data hold time                                   | t <sub>3</sub><br>CC/SR  | 0                          | -      | -    | μs   |                          |

| Data set-up time                                 | t <sub>4</sub><br>CC/SR  | 100                        | -      | -    | ns   |                          |

| LOW period of SCL clock                          | t <sub>5</sub><br>CC/SR  | 1.3                        | -      | -    | μs   |                          |

| HIGH period of SCL clock                         | t <sub>6</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Hold time for (repeated)<br>START condition      | t <sub>7</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Set-up time for repeated START condition         | t <sub>8</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Set-up time for STOP condition                   | t <sub>9</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Bus free time between a STOP and START condition | t <sub>10</sub><br>CC/SR | 1.3                        | -      | -    | μs   |                          |

| Capacitive load for each bus line                | C <sub>b</sub> SR        | -                          | -      | 400  | pF   |                          |

<sup>1)</sup> Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

<sup>2)</sup> C<sub>b</sub> refers to the total capacitance of one bus line in pF.

Figure 23 USIC IIC Stand and Fast Mode Timing

# 3.3.6.3 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.  $\label{eq:using_parameters}$

Note: Operating Conditions apply.

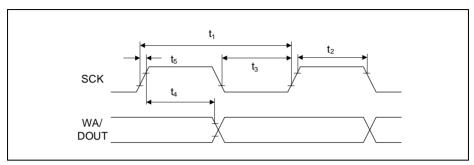

Table 33 USIC IIS Master Transmitter Timing

| Parameter       | Symbol            |                     | Values |            | Unit | Note /<br>Test Condition |

|-----------------|-------------------|---------------------|--------|------------|------|--------------------------|

|                 |                   | Min.                | Тур.   | Max.       |      |                          |

| Clock period    | t <sub>1</sub> CC | $2/f_{MCLK}$        | -      | -          | ns   | $V_{DDP} \geq 3\;V$      |

|                 |                   | 4/f <sub>MCLK</sub> | -      | -          | ns   | $V_{DDP}\!<\!3\;V$       |

| Clock HIGH      | t <sub>2</sub> CC | 0.35 x              | -      | -          | ns   |                          |

|                 |                   | $t_{1min}$          |        |            |      |                          |

| Clock Low       | t <sub>3</sub> CC | 0.35 x              | -      | -          | ns   |                          |

|                 |                   | $t_{1min}$          |        |            |      |                          |

| Hold time       | t <sub>4</sub> CC | 0                   | -      | -          | ns   |                          |

| Clock rise time | t <sub>5</sub> CC | -                   | -      | 0.15 x     | ns   |                          |

|                 |                   |                     |        | $t_{1min}$ |      |                          |

Figure 24 USIC IIS Master Transmitter Timing

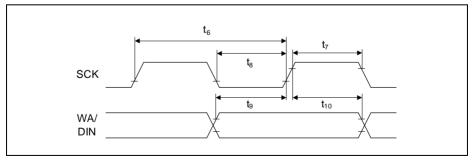

Table 34 USIC IIS Slave Receiver Timing

| Parameter    | Symbol            |                              | Values |      | Unit | Note /<br>Test Condition |

|--------------|-------------------|------------------------------|--------|------|------|--------------------------|

|              |                   | Min.                         | Тур.   | Max. |      |                          |

| Clock period | t <sub>6</sub> SR | $4/f_{MCLK}$                 | -      | -    | ns   |                          |

| Clock HIGH   | t7 SR             | 0.35 x t <sub>6min</sub>     | -      | -    | ns   |                          |

| Clock Low    | t8 SR             | 0.35 x<br>t <sub>6</sub> min | -      | -    | ns   |                          |

| Set-up time  | t9 SR             | 0.2 x<br>t <sub>6</sub> min  | -      | -    | ns   |                          |

| Hold time    | <i>t</i> 10 SR    | 10                           | -      | -    | ns   |                          |

Figure 25 USIC IIS Slave Receiver Timing