Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 32MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 27                                                                                 |

| Program Memory Size        | 32KB (32K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 40-VFQFN Exposed Pad                                                               |

| Supplier Device Package    | PG-VQFN-40-13                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1302q040x0032abxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2017-03 Published by Infineon Technologies AG 81726 Munich, Germany © 2017 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

### XMC1300 Data Sheet

### Revision History: V1.9 2017-03

Previous Version: V1.8 2016-09

| Page                | Subjects                                  |

|---------------------|-------------------------------------------|

| Page 10,<br>Page 12 | Add marking option for XMC1301-T038X0032. |

### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

ARM<sup>®</sup>, ARM Powered<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

Cortex<sup>™</sup>, CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM, Limited.

### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

### About this Document

## About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC1300 series devices.

The document describes the characteristics of a superset of the XMC1300 series devices. For simplicity, the various device types are referred to by the collective term XMC1300 throughout this document.

### **XMC1000 Family User Documentation**

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

# Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc1000 to get access to the latest versions of those documents.

### Summary of Features

- Ultra low power consumption

- Nested Vectored Interrupt Controller (NVIC)

- · Event Request Unit (ERU) for processing of external and internal service requests

- MATH Co-processor (MATH)

- CORDIC unit for trigonometric calculation

- division unit

### **On-Chip Memories**

- 8 kbytes on-chip ROM

- 16 kbytes on-chip high-speed SRAM

- up to 200 kbytes on-chip Flash program and data memory

### **Communication Peripherals**

• Two Universal Serial Interface Channels (USIC), usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

### **Analog Frontend Peripherals**

- A/D Converters

- up to 12 analog input pins

- 2 sample and hold stages with 8 analog input channels each

- fast 12-bit analog to digital converter with adjustable gain

- Up to 8 channels of out of range comparators (ORC)

- Up to 3 fast analog comparators (ACMP)

- Temperature Sensor (TSE)

### **Industrial Control Peripherals**

- Capture/Compare Units 4 (CCU4) as general purpose timers

- Capture/Compare Units 8 (CCU8) for motor control and power conversion

- · Position Interfaces (POSIF) for hall and quadrature encoders and motor positioning

- Brightness and Colour Control Unit (BCCU), for LED color and dimming application

### System Control

- Window Watchdog Timer (WDT) for safety sensitive applications

- Real Time Clock module with alarm support (RTC)

- System Control Unit (SCU) for system configuration and control

- Pseudo random number generator (PRNG) for fast random data generation

### Input/Output Lines

- Tri-stated in input mode

- Push/pull or open drain output mode

### **Summary of Features**

| Derivative        | Value                                                                                   | Marking |

|-------------------|-----------------------------------------------------------------------------------------|---------|

| XMC1301-T016F0008 | 00013032 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00003000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T016F0016 | 00013032 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00005000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T016F0032 | 00013032 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00009000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T016X0008 | 00013033 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00003000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T016X0016 | 00013033 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00005000 201ED083 <sub>H</sub> | AB      |

| XMC1302-T016X0008 | 00013033 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00003000 201ED083 <sub>H</sub> | AB      |

| XMC1302-T016X0016 | 00013033 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00005000 201ED083 <sub>H</sub> | AB      |

| XMC1302-T016X0032 | 00013033 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00009000 201ED083 <sub>H</sub> | AB      |

| XMC1302-T028X0016 | 00013023 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00005000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T038F0008 | 00013012 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00003000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T038F0016 | 00013012 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00005000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T038F0032 | 00013012 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00009000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T038X0032 | 00013013 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00009000 201ED083 <sub>H</sub> | AB      |

| XMC1301-T038F0064 | 00013012 01CF00FF 00001FF7 0000100F<br>00000C00 00001000 00011000 201ED083 <sub>H</sub> | AB      |

| XMC1302-T038X0016 | 00013013 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00005000 201ED083 <sub>H</sub> | AB      |

| XMC1302-T038X0032 | 00013013 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00009000 201ED083 <sub>H</sub> | AB      |

| XMC1302-T038X0064 | 00013013 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00011000 201ED083 <sub>H</sub> | AB      |

### Table 4 XMC1300 Chip Identification Number

### **Summary of Features**

| Derivative        | Value                                                                                   | Marking |  |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------|---------|--|--|--|--|--|--|--|

| XMC1302-Q040X0128 | 00013043 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00021000 201ED083 <sub>H</sub> | AB      |  |  |  |  |  |  |  |

| XMC1302-Q040X0200 | 00013043 01FF00FF 00001FF7 0000900F<br>00000C00 00001000 00033000 201ED083 <sub>H</sub> | AB      |  |  |  |  |  |  |  |

### Table 4 XMC1300 Chip Identification Number (cont'd)

### 2.2.1 Package Pin Summary

The following general building block is used to describe each pin:

### Table 5 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad Type |

|----------|-----------|-----------|--------------|

| Px.y     | Ν         | Ν         | Pad Class    |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type:

- STD\_INOUT(standard bi-directional pads)

- STD\_INOUT/AN (standard bi-directional pads with analog input)

- High Current (high current bi-directional pads)

- STD\_IN/AN (standard input pads with analog input)

- Power (power supply)

Details about the pad properties are defined in the Electrical Parameters.

| Function | VQFN<br>40 | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24 | TSSOP<br>16 | Pad<br>Type   | Notes |

|----------|------------|-------------|-------------|------------|-------------|---------------|-------|

| P0.0     | 23         | 17          | 13          | 15         | 7           | STD_IN<br>OUT |       |

| P0.1     | 24         | 18          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.2     | 25         | 19          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.3     | 26         | 20          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.4     | 27         | 21          | 14          | -          | -           | STD_IN<br>OUT |       |

| P0.5     | 28         | 22          | 15          | 16         | 8           | STD_IN<br>OUT |       |

| P0.6     | 29         | 23          | 16          | 17         | 9           | STD_IN<br>OUT |       |

### Table 6 Package Pin Mapping

| Table 6         Package Pin Mapping (cont'd) |            |             |             |            |             |                  |                                                                                  |  |

|----------------------------------------------|------------|-------------|-------------|------------|-------------|------------------|----------------------------------------------------------------------------------|--|

| Function                                     | VQFN<br>40 | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24 | TSSOP<br>16 | Pad<br>Type      | Notes                                                                            |  |

| P2.1                                         | 2          | 36          | 26          | 2          | -           | STD_IN<br>OUT/AN |                                                                                  |  |

| P2.2                                         | 3          | 37          | 27          | 3          | -           | STD_IN/<br>AN    |                                                                                  |  |

| P2.3                                         | 4          | 38          | -           | -          | -           | STD_IN/<br>AN    |                                                                                  |  |

| P2.4                                         | 5          | 1           | -           | -          | -           | STD_IN/<br>AN    |                                                                                  |  |

| P2.5                                         | 6          | 2           | 28          | -          | -           | STD_IN/<br>AN    |                                                                                  |  |

| P2.6                                         | 7          | 3           | 1           | 4          | 16          | STD_IN/<br>AN    |                                                                                  |  |

| P2.7                                         | 8          | 4           | 2           | 5          | 1           | STD_IN/<br>AN    |                                                                                  |  |

| P2.8                                         | 9          | 5           | 3           | 5          | 1           | STD_IN/<br>AN    |                                                                                  |  |

| P2.9                                         | 10         | 6           | 4           | 6          | 2           | STD_IN/<br>AN    |                                                                                  |  |

| P2.10                                        | 11         | 7           | 5           | 7          | 3           | STD_IN<br>OUT/AN |                                                                                  |  |

| P2.11                                        | 12         | 8           | 6           | 8          | 4           | STD_IN<br>OUT/AN |                                                                                  |  |

| VSS                                          | 13         | 9           | 7           | 9          | 5           | Power            | Supply GND,<br>ADC reference<br>GND                                              |  |

| VDD                                          | 14         | 10          | 8           | 10         | 6           | Power            | Supply VDD,<br>ADC reference<br>voltage/ ORC<br>reference voltage                |  |

| VDDP                                         | 15         | 10          | 8           | 10         | 6           | Power            | When VDD is<br>supplied, VDDP<br>has to be<br>supplied with the<br>same voltage. |  |

| Function | VQFN<br>40  | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24  | TSSOP<br>16 | Pad<br>Type | Notes                                                                                                                                                                                                                                                                               |

|----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSSP     | 31          | 25          | -           | -           | -           | Power       | I/O port ground                                                                                                                                                                                                                                                                     |

| VDDP     | 32          | 26          | -           | -           | -           | Power       | I/O port supply                                                                                                                                                                                                                                                                     |

| VSSP     | Exp.<br>Pad | -           | -           | Exp.<br>Pad | -           | Power       | Exposed Die<br>Pad<br>The exposed die<br>pad is connected<br>internally to<br>VSSP. For proper<br>operation, it is<br>mandatory to<br>connect the<br>exposed pad to<br>the board ground<br>For thermal<br>aspects, please<br>refer to the<br>Package and<br>Reliability<br>chapter. |

### Table 6Package Pin Mapping (cont'd)

### 2.2.2 Port I/O Function Description

The following general building block is used to describe the I/O functions of each PORT pin:

### Table 7 Port I/O Function Description

| Function | Outputs  |           | Inputs   |          |  |

|----------|----------|-----------|----------|----------|--|

|          | ALT1     | ALT1 ALTn |          | Input    |  |

| P0.0     |          | MODA.OUT  | MODC.INA |          |  |

| Pn.y     | MODA.OUT |           | MODA.INA | MODC.INB |  |

### 2.2.3 Hardware Controlled I/O Function Description

The following general building block is used to describe the hardware I/O and pull control functions of each PORT pin:

| Function | Outputs  | Inputs   | Pull Control |          |  |  |

|----------|----------|----------|--------------|----------|--|--|

|          | HWO0     | HWIO     | HW0_PD       | HW0_PU   |  |  |

| P0.0     | MODB.OUT | MODB.INA |              |          |  |  |

| Pn.y     |          |          | MODC.OUT     | MODC.OUT |  |  |

### Table 8 Hardware Controlled I/O Function Description

By Pn\_HWSEL, it is possible to select between different hardware "masters" (HWO0/HWI0, HWO1/HWI1). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers. Additional hardware signals HW0\_PD/HW1\_PD and HW0\_PU/HW1\_PU controlled by the peripherals can be used to control the pull devices of the pin.

Please refer to the **Hardware Controlled I/O Functions** table for the complete hardware I/O and pull control function mapping.

### 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                            | Symbol                                                     |    |      | Va   | lues                                | Unit | Note /                |

|----------------------------------------------------------------------|------------------------------------------------------------|----|------|------|-------------------------------------|------|-----------------------|

|                                                                      |                                                            |    | Min  | Тур. | Max.                                |      | Test Cond<br>ition    |

| Junction temperature                                                 | $T_{J}$                                                    | SR | -40  | _    | 115                                 | °C   | -                     |

| Storage temperature                                                  | $T_{\rm ST}$                                               | SR | -40  | -    | 125                                 | °C   | -                     |

| Voltage on power supply pin with respect to $V_{\rm SSP}$            | $V_{DDP}$                                                  | SR | -0.3 | -    | 6                                   | V    | -                     |

| Voltage on digital pins with respect to $V_{\rm SSP}^{1)}$           | $V_{\rm IN}$                                               | SR | -0.5 | -    | $V_{\text{DDP}}$ + 0.5<br>or max. 6 | V    | whichever<br>is lower |

| Voltage on P2 pins with respect to $V_{\rm SSP}^{2)}$                | $V_{INP2}$                                                 | SR | -0.3 | -    | V <sub>DDP</sub> + 0.3              | V    | -                     |

| Voltage on analog input pins with respect to $V_{\rm SSP}$           | $\begin{array}{c} V_{\rm AIN} \\ V_{\rm AREF} \end{array}$ | SR | -0.5 | -    | $V_{\text{DDP}}$ + 0.5<br>or max. 6 | V    | whichever<br>is lower |

| Input current on any pin<br>during overload condition                | I <sub>IN</sub>                                            | SR | -10  | -    | 10                                  | mA   | -                     |

| Absolute maximum sum of all input currents during overload condition | ΣI <sub>IN</sub>                                           | SR | -50  | -    | +50                                 | mA   | -                     |

### Table 11 Absolute Maximum Rating Parameters

1) Excluding port pins P2.[1,2,6,7,8,9,11].

2) Applicable to port pins P2.[1,2,6,7,8,9,11].

### 3.2 DC Parameters

### 3.2.1 Input/Output Characteristics

Table 16 provides the characteristics of the input/output pins of the XMC1300.

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

- Note: Unless otherwise stated, input DC and AC characteristics, including peripheral timings, assume that the input pads operate with the standard hysteresis.

| Parameter                                                  | Symbol            |    | Limit                      | Values                   | Unit | Test Conditions                                                                    |

|------------------------------------------------------------|-------------------|----|----------------------------|--------------------------|------|------------------------------------------------------------------------------------|

|                                                            |                   |    | Min.                       | Max.                     |      |                                                                                    |

| Output low voltage on port pins                            | V <sub>OLP</sub>  | CC | -                          | 1.0                      | V    | I <sub>OL</sub> = 11 mA (5 V)<br>I <sub>OL</sub> = 7 mA (3.3 V)                    |

| (with standard pads)                                       |                   |    | -                          | 0.4                      | V    | $I_{OL} = 5 \text{ mA} (5 \text{ V})$<br>$I_{OL} = 3.5 \text{ mA} (3.3 \text{ V})$ |

| Output low voltage on<br>high current pads                 | $V_{OLP1}$        | СС | -                          | 1.0                      | V    | I <sub>OL</sub> = 50 mA (5 V)<br>I <sub>OL</sub> = 25 mA (3.3 V)                   |

|                                                            |                   |    | -                          | 0.32                     | V    | I <sub>OL</sub> = 10 mA (5 V)                                                      |

|                                                            |                   |    | -                          | 0.4                      | V    | I <sub>OL</sub> = 5 mA (3.3 V)                                                     |

| Output high voltage on port pins                           | V <sub>OHP</sub>  | CC | V <sub>DDP</sub> -<br>1.0  | -                        | V    | I <sub>OH</sub> = -10 mA (5 V)<br>I <sub>OH</sub> = -7 mA (3.3 V)                  |

| (with standard pads)                                       |                   |    | V <sub>DDP</sub> -<br>0.4  | _                        | V    | I <sub>OH</sub> = -4.5 mA (5 V)<br>I <sub>OH</sub> = -2.5 mA (3.3 V)               |

| Output high voltage on high current pads                   | V <sub>OHP1</sub> | CC | V <sub>DDP</sub> -<br>0.32 | -                        | V    | I <sub>OH</sub> = -6 mA (5 V)                                                      |

|                                                            |                   |    | V <sub>DDP</sub> -<br>1.0  | _                        | V    | I <sub>OH</sub> = -8 mA (3.3 V)                                                    |

|                                                            |                   |    | V <sub>DDP</sub> - 0.4     | _                        | V    | I <sub>OH</sub> = -4 mA (3.3 V)                                                    |

| Input low voltage on port<br>pins<br>(Standard Hysteresis) | $V_{ILPS}$        | SR | -                          | $0.19 \times V_{ m DDP}$ | V    | CMOS Mode<br>(5 V, 3.3 V & 2.2 V)                                                  |

Table 16

Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                     | Symbol             |    | Limit Values            |                          | Unit | Test Conditions                                                         |  |

|-------------------------------------------------------------------------------|--------------------|----|-------------------------|--------------------------|------|-------------------------------------------------------------------------|--|

|                                                                               |                    |    | Min. Max.               |                          |      |                                                                         |  |

| Input Hysteresis <sup>8)</sup>                                                | HYS                | СС | $0.08 	imes V_{ m DDP}$ | -                        | V    | CMOS Mode (5 V),<br>Standard Hysteresis                                 |  |

|                                                                               |                    |    | $0.03 	imes V_{ m DDP}$ | -                        | V    | CMOS Mode (3.3 V),<br>Standard Hysteresis                               |  |

|                                                                               |                    |    | $0.02 	imes V_{ m DDP}$ | -                        | V    | CMOS Mode (2.2 V),<br>Standard Hysteresis                               |  |

|                                                                               |                    |    | $0.5 	imes V_{ m DDP}$  | $0.75 	imes V_{ m DDP}$  | V    | CMOS Mode(5 V),<br>Large Hysteresis                                     |  |

|                                                                               |                    |    | $0.4 	imes V_{ m DDP}$  | $0.75 	imes V_{ m DDP}$  | V    | CMOS Mode(3.3 V),<br>Large Hysteresis                                   |  |

|                                                                               |                    |    | $0.2 	imes V_{ m DDP}$  | $0.65 \times V_{ m DDP}$ | V    | CMOS Mode(2.2 V),<br>Large Hysteresis                                   |  |

| Pin capacitance (digital inputs/outputs)                                      | C <sub>IO</sub>    | СС | -                       | 10                       | pF   |                                                                         |  |

| Pull-up resistor on port<br>pins                                              | R <sub>PUP</sub>   | СС | 20                      | 50                       | kohm | $V_{\rm IN} = V_{\rm SSP}$                                              |  |

| Pull-down resistor on<br>port pins                                            | R <sub>PDP</sub>   | CC | 20                      | 50                       | kohm | $V_{\rm IN} = V_{\rm DDP}$                                              |  |

| Input leakage current <sup>9)</sup>                                           | I <sub>OZP</sub>   | CC | -1                      | 1                        | μA   | $0 < V_{\rm IN} < V_{\rm DDP},$<br>$T_{\rm A} \le 105 \ ^{\circ}{ m C}$ |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                          | $V_{\rm PO}$       | SR | -                       | 0.3                      | V    | 10)                                                                     |  |

| Maximum current per pin (excluding P1, $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | I <sub>MP</sub>    | SR | -10                     | 11                       | mA   | -                                                                       |  |

| Maximum current per<br>high currrent pins                                     | I <sub>MP1A</sub>  | SR | -10                     | 50                       | mA   | -                                                                       |  |

| Maximum current into<br>V <sub>DDP</sub> (TSSOP16,<br>VQFN24)                 | I <sub>MVDD1</sub> | SR | -                       | 130                      | mA   | 18)                                                                     |  |

| Maximum current into<br>V <sub>DDP</sub> (TSSOP38,<br>VQFN40)                 | I <sub>MVDD2</sub> | SR | -                       | 260                      | mA   | 18)                                                                     |  |

### Table 16 Input/Output Characteristics (Operating Conditions apply) (cont'd)

### Table 16 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                             | Symbol                | Limit | Values | Unit | Test Conditions |

|-------------------------------------------------------|-----------------------|-------|--------|------|-----------------|

|                                                       |                       | Min.  | Max.   |      |                 |

| Maximum current out of $V_{\rm SS}$ (TSSOP16, VQFN24) | I <sub>MVSS1</sub> SF | -     | 130    | mA   | 18)             |

| Maximum current out of $V_{\rm SS}$ (TSSOP38, VQFN40) | I <sub>MVSS2</sub> SF | -     | 260    | mA   | 18)             |

1) Rise/Fall time parameters are taken with 10% - 90% of supply.

2) Additional rise/fall time valid for CL = 50 pF - CL = 100 pF @ 0.150 ns/pF at 5 V supply voltage.

3) Additional rise/fall time valid for CL = 50 pF - CL = 100 pF @ 0.205 ns/pF at 3.3 V supply voltage.

4) Additional rise/fall time valid for CL = 50 pF - CL = 100 pF @ 0.445 ns/pF at 1.8 V supply voltage.

5) Additional rise/fall time valid for CL = 50 pF - CL = 100 pF @ 0.225 ns/pF at 5 V supply voltage.

6) Additional rise/fall time valid for CL = 50 pF - CL = 100 pF @ 0.288 ns/pF at 3.3 V supply voltage.

7) Additional rise/fall time valid for CL = 50 pF - CL = 100 pF @ 0.588 ns/pF at 1.8 V supply voltage.

Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

9) An additional error current  $(I_{INI})$  will flow if an overload current flows through an adjacent pin.

10) However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when V<sub>DDP</sub> is powered off.

| Table 17 | ADC Characteristics (Operating Conditions apply) <sup>1)</sup> (cont'd) |

|----------|-------------------------------------------------------------------------|

|----------|-------------------------------------------------------------------------|

| Parameter                                        | Symbol                     |      | Values | 5                          | Unit                           | Note / Test Condition                                                        |

|--------------------------------------------------|----------------------------|------|--------|----------------------------|--------------------------------|------------------------------------------------------------------------------|

|                                                  |                            | Min. | Тур.   | Max.                       | -                              |                                                                              |

| Gain settings                                    | $G_{\sf IN}  \sf CC$       | 1    | -      | 1                          | -                              | GNCTRxz.GAINy=00 <sub>B</sub><br>(unity gain)                                |

|                                                  |                            | 3    |        |                            | -                              | GNCTRxz.GAINy=01 <sub>B</sub><br>(gain g1)                                   |

|                                                  |                            | 6    |        |                            | -                              | GNCTRxz.GAINy=10 <sub>B</sub><br>(gain g2)                                   |

|                                                  |                            | 12   |        |                            | -                              | GNCTRxz.GAINy=11 <sub>B</sub><br>(gain g3)                                   |

| Sample Time                                      | t <sub>sample</sub> CC     | 3    | -      | -                          | 1 /<br><i>f</i> <sub>ADC</sub> | $V_{\rm DD}$ = 5.0 V                                                         |

|                                                  |                            | 3    | -      | -                          | 1 /<br><i>f</i> <sub>ADC</sub> | $V_{\rm DD}$ = 3.3 V                                                         |

|                                                  |                            | 30   | -      | -                          | 1 /<br><i>f</i> <sub>ADC</sub> | $V_{\rm DD}$ = 2.0 V                                                         |

| Sigma delta loop hold<br>time                    | t <sub>SD_hold</sub><br>CC | 20   | -      | -                          | μS                             | Residual charge stored<br>in an active sigma delta<br>loop remains available |

| Conversion time in fast compare mode             | t <sub>CF</sub> CC         | 9    | 1      |                            | 1 /<br><i>f</i> <sub>ADC</sub> | 2)                                                                           |

| Conversion time<br>in 12-bit mode                | <i>t</i> <sub>C12</sub> CC | 20   |        |                            | 1 /<br><i>f</i> <sub>ADC</sub> | 2)                                                                           |

| Maximum sample rate in 12-bit mode <sup>3)</sup> | $f_{C12}  \mathrm{CC}$     | -    | -      | f <sub>ADC</sub> /<br>42.5 | -                              | 1 sample<br>pending                                                          |

|                                                  |                            | -    | -      | f <sub>ADC</sub> /<br>62.5 | -                              | 2 samples<br>pending                                                         |

| Conversion time<br>in 10-bit mode                | <i>t</i> <sub>C10</sub> CC | 18   |        |                            | 1 /<br><i>f</i> <sub>ADC</sub> | 2)                                                                           |

| Maximum sample rate in 10-bit mode <sup>3)</sup> | <i>f</i> <sub>C10</sub> CC | -    | -      | f <sub>ADC</sub> /<br>40.5 | -                              | 1 sample<br>pending                                                          |

|                                                  |                            | -    | -      | f <sub>ADC</sub> /<br>58.5 | -                              | 2 samples<br>pending                                                         |

| Conversion time<br>in 8-bit mode                 | t <sub>C8</sub> CC         | 16   |        |                            | 1 /<br><i>f</i> <sub>ADC</sub> | 2)                                                                           |

### Figure 13 ORC Detection Ranges

| Parameter                                                                                                            | Symbol                |        | Values             | S    | Unit   | Note /<br>Test Condition |

|----------------------------------------------------------------------------------------------------------------------|-----------------------|--------|--------------------|------|--------|--------------------------|

|                                                                                                                      |                       | Min    | Typ. <sup>1)</sup> | Max. |        |                          |

| Sleep mode current<br>Peripherals clock disabled<br>Flash active<br>$f_{\rm MCLK}/f_{\rm PCLK}$ in MHz <sup>5)</sup> | I <sub>DDPSD</sub> CC | •<br>- | 1.8                | -    | mA     | 32 / 64                  |

|                                                                                                                      |                       |        | 1.7                | -    | mA     | 24 / 48                  |

|                                                                                                                      |                       |        | 1.6                | -    | mA     | 16 / 32                  |

|                                                                                                                      |                       |        | 1.5                | -    | mA     | 8 / 16                   |

|                                                                                                                      |                       |        | 1.4                | -    | mA     | 1/1                      |

| Sleep mode current<br>Peripherals clock disabled<br>Flash powered down<br>$f_{MCLK}/f_{PCLK}$ in MHz <sup>6</sup>    | I <sub>DDPSR</sub> CC | _      | 1.2                | -    | mA     | 32 / 64                  |

|                                                                                                                      |                       |        | 1.1                | -    | mA     | 24 / 48                  |

|                                                                                                                      |                       |        | 1.0                | -    | mA     | 16 / 32                  |

|                                                                                                                      |                       |        | 0.8                | -    | mA     | 8 / 16                   |

|                                                                                                                      |                       |        | 0.7                | -    | mA     | 1/1                      |

| Deep Sleep mode current <sup>7)</sup>                                                                                | I <sub>DDPDS</sub> CC | _      | 0.24               | -    | mA     |                          |

| Wake-up time from Sleep to Active mode <sup>8)</sup>                                                                 | t <sub>SSA</sub> CC   | _      | 6                  | -    | cycles |                          |

| Wake-up time from Deep<br>Sleep to Active mode <sup>9)</sup>                                                         | t <sub>DSA</sub> CC   | -      | 280                | -    | μsec   |                          |

### Table 21 Power Supply Parameters; V<sub>DDP</sub> = 5V

1) The typical values are measured at  $T_A = +25 \text{ °C}$  and VDDP = 5 V.

2) CPU and all peripherals clock enabled, Flash is in active mode.

3) CPU enabled, all peripherals clock disabled, Flash is in active mode.

4) CPU in sleep, all peripherals clock enabled and Flash is in active mode.

5) CPU in sleep, Flash is in active mode.

6) CPU in sleep, Flash is powered down and code executed from RAM after wake-up.

7) CPU in sleep, peripherals clock disabled, Flash is powered down and code executed from RAM after wake-up.

8) CPU in sleep, Flash is in active mode during sleep mode.

9) CPU in sleep, Flash is in powered down mode during deep sleep mode.

### 3.3.5 SPD Timing Requirements

The optimum SPD decision time between  $0_B$  and  $1_B$  is 0.75 µs. With this value the system has maximum robustness against frequency deviations of the sampling clock on tool and on device side. However it is not always possible to exactly match this value with the given constraints for the sample clock. For instance for a oversampling rate of 4, the sample clock will be 8 MHz and in this case the closest possible effective decision time is 5.5 clock cycles (0.69 µs).

| Sample<br>Freq. | Sampling<br>Factor |        | Sample<br>Clocks 1 <sub>B</sub> |                                     | Remark                                                                                   |

|-----------------|--------------------|--------|---------------------------------|-------------------------------------|------------------------------------------------------------------------------------------|

| 8 MHz           | 4                  | 1 to 5 | 6 to 12                         | <b>Time<sup>1)</sup></b><br>0.69 μs | The other closest option<br>(0.81 µs) for the effective<br>decision time is less robust. |

### Table 28 Optimum Number of Sample Clocks for SPD

1) Nominal sample frequency period multiplied with  $0.5 + (max. number of 0_B sample clocks)$

For a balanced distribution of the timing robustness of SPD between tool and device, the timing requirements for the tool are:

- Frequency deviation of the sample clock is +/- 5%

- Effective decision time is between 0.69 µs and 0.75 µs (calculated with nominal sample frequency)

62

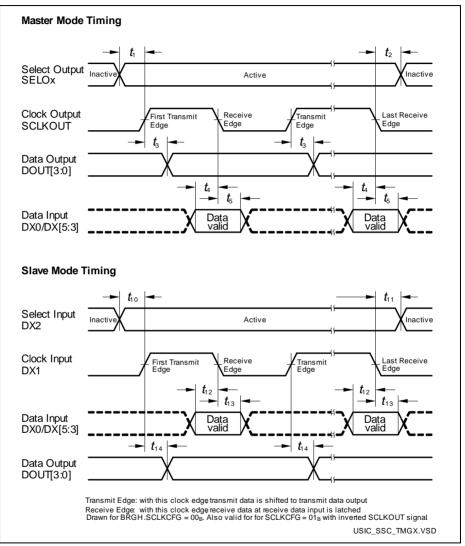

Figure 22 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration, for which the slave select signal is low-active, and the serial clock signal is not shifted and not inverted.

### **Quality Declaration**

# 5 Quality Declaration

Table 36 shows the characteristics of the quality parameters in the XMC1300.

### Table 36 Quality Parameters

| Parameter                                                             | Symbol                 | Limit V | alues | Unit | Notes                                       |

|-----------------------------------------------------------------------|------------------------|---------|-------|------|---------------------------------------------|

|                                                                       |                        | Min.    | Max.  |      |                                             |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub><br>SR | -       | 2000  | V    | Conforming to<br>EIA/JESD22-<br>A114-B      |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | $V_{\rm CDM}$ SR       | -       | 500   | V    | Conforming to JESD22-C101-C                 |

| Moisture sensitivity level                                            | MSL<br>CC              | -       | 3     | -    | JEDEC<br>J-STD-020D                         |

| Soldering temperature                                                 | $T_{ m SDR}$<br>SR     | -       | 260   | °C   | Profile according<br>to JEDEC<br>J-STD-020D |