Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 32MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I2S, POR, PWM, WDT                                         |

| Number of I/O              | 26                                                                                 |

| Program Memory Size        | 16KB (16K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

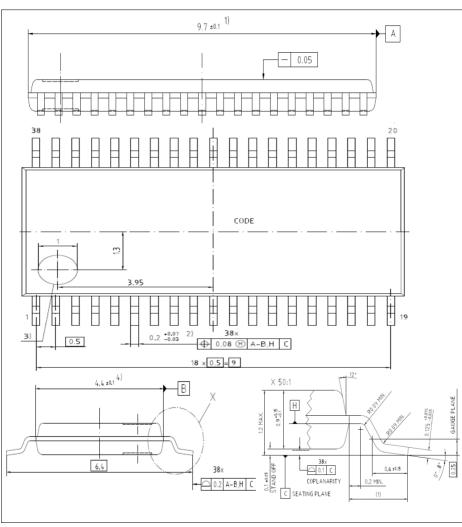

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                                    |

| Supplier Device Package    | PG-TSSOP-38-9                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1302t038x0016abxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

# **Table of Contents**

| 1<br>1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                                                    | Summary of Features8Ordering Information10Device Types10Device Type Features12Chip Identification Number12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3                                                                                                                                                                       | General Device Information16Logic Symbols16Pin Configuration and Definition18Package Pin Summary22Port I/O Function Description25Hardware Controlled I/O Function Description27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.6.1<br>3.3.6.2<br>3.3.6.3 | Electrical Parameters         33           General Parameters         33           Parameter Interpretation         33           Absolute Maximum Ratings         34           Pin Reliability in Overload         35           Operating Conditions         37           DC Parameters         38           Input/Output Characteristics         38           Analog to Digital Converters (ADC)         42           Out of Range Comparator (ORC) Characteristics         46           Analog Comparator Characteristics         48           Temperature Sensor Characteristics         49           Power Supply Current         50           Flash Memory Parameters         55           AC Parameters         55           Testing Waveforms         56           Power-Up and Supply Monitoring Characteristics         57           On-Chip Oscillator Characteristics         59           Serial Wire Debug Port (SW-DP) Timing         61           SPD Timing Requirements         62           Peripheral Timings         63           Synchronous Serial Interface (USIC SSC) Timing         63           Inter-IC (IIC) Interface Timing         66           Inter-IC Sound (IIS) Interface Timing         68 |

| <b>4</b><br>4.1<br>4.1.1<br>4.2                                                                                                                                                                                  | Package and Reliability70Package Parameters70Thermal Considerations70Package Outlines72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 2.2.1 Package Pin Summary

The following general building block is used to describe each pin:

Table 5 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad Type |

|----------|-----------|-----------|--------------|

| Px.y     | N         | N         | Pad Class    |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type:

- STD\_INOUT(standard bi-directional pads)

- STD\_INOUT/AN (standard bi-directional pads with analog input)

- High Current (high current bi-directional pads)

- STD\_IN/AN (standard input pads with analog input)

- Power (power supply)

Details about the pad properties are defined in the Electrical Parameters.

Table 6 Package Pin Mapping

| Function | VQFN<br>40 | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24 | TSSOP<br>16 | Pad<br>Type   | Notes |

|----------|------------|-------------|-------------|------------|-------------|---------------|-------|

| P0.0     | 23         | 17          | 13          | 15         | 7           | STD_IN<br>OUT |       |

| P0.1     | 24         | 18          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.2     | 25         | 19          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.3     | 26         | 20          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.4     | 27         | 21          | 14          | -          | -           | STD_IN<br>OUT |       |

| P0.5     | 28         | 22          | 15          | 16         | 8           | STD_IN<br>OUT |       |

| P0.6     | 29         | 23          | 16          | 17         | 9           | STD_IN<br>OUT |       |

Table 6 Package Pin Mapping (cont'd)

|          |            |             |             | ,          |             |                  |       |

|----------|------------|-------------|-------------|------------|-------------|------------------|-------|

| Function | VQFN<br>40 | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24 | TSSOP<br>16 | Pad<br>Type      | Notes |

| P0.7     | 30         | 24          | 17          | 18         | 10          | STD_IN<br>OUT    |       |

| P0.8     | 33         | 27          | 18          | 19         | 11          | STD_IN<br>OUT    |       |

| P0.9     | 34         | 28          | 19          | 20         | 12          | STD_IN<br>OUT    |       |

| P0.10    | 35         | 29          | 20          | -          | -           | STD_IN<br>OUT    |       |

| P0.11    | 36         | 30          | -           | -          | -           | STD_IN<br>OUT    |       |

| P0.12    | 37         | 31          | 21          | 21         | -           | STD_IN<br>OUT    |       |

| P0.13    | 38         | 32          | 22          | 22         | -           | STD_IN<br>OUT    |       |

| P0.14    | 39         | 33          | 23          | 23         | 13          | STD_IN<br>OUT    |       |

| P0.15    | 40         | 34          | 24          | 24         | 14          | STD_IN<br>OUT    |       |

| P1.0     | 22         | 16          | 12          | 14         | -           | High<br>Current  |       |

| P1.1     | 21         | 15          | 11          | 13         | -           | High<br>Current  |       |

| P1.2     | 20         | 14          | 10          | 12         | -           | High<br>Current  |       |

| P1.3     | 19         | 13          | 9           | 11         | -           | High<br>Current  |       |

| P1.4     | 18         | 12          | -           | -          | -           | High<br>Current  |       |

| P1.5     | 17         | 11          | -           | -          | -           | High<br>Current  |       |

| P1.6     | 16         | -           | -           | -          | -           | STD_IN<br>OUT    |       |

| P2.0     | 1          | 35          | 25          | 1          | 15          | STD_IN<br>OUT/AN |       |

Table 6 Package Pin Mapping (cont'd)

| Function | VQFN<br>40  | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24  | TSSOP<br>16 | Pad<br>Type | Notes                                                                                                                                                                                                                                |

|----------|-------------|-------------|-------------|-------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSSP     | 31          | 25          | -           | -           | -           | Power       | I/O port ground                                                                                                                                                                                                                      |

| VDDP     | 32          | 26          | -           | -           | -           | Power       | I/O port supply                                                                                                                                                                                                                      |

| VSSP     | Exp.<br>Pad | -           | -           | Exp.<br>Pad | -           | Power       | Exposed Die Pad The exposed die pad is connected internally to VSSP. For proper operation, it is mandatory to connect the exposed pad to the board ground. For thermal aspects, please refer to the Package and Reliability chapter. |

## 2.2.2 Port I/O Function Description

The following general building block is used to describe the I/O functions of each PORT pin:

Table 7 Port I/O Function Description

| Function | Outputs  |          | Inputs   |          |  |  |

|----------|----------|----------|----------|----------|--|--|

|          | ALT1     | ALTn     | Input    | Input    |  |  |

| P0.0     |          | MODA.OUT | MODC.INA |          |  |  |

| Pn.y     | MODA.OUT |          | MODA.INA | MODC.INB |  |  |

## 2.2.3 Hardware Controlled I/O Function Description

The following general building block is used to describe the hardware I/O and pull control functions of each PORT pin:

Table 8 Hardware Controlled I/O Function Description

| Function | Outputs  | Inputs   | Pull Control |          |

|----------|----------|----------|--------------|----------|

|          | HWO0     | HWI0     | HW0_PD       | HW0_PU   |

| P0.0     | MODB.OUT | MODB.INA |              |          |

| Pn.y     |          |          | MODC.OUT     | MODC.OUT |

By Pn\_HWSEL, it is possible to select between different hardware "masters" (HWO0/HWI0, HWO1/HWI1). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers. Additional hardware signals HW0\_PD/HW1\_PD and HW0\_PU/HW1\_PU controlled by the peripherals can be used to control the pull devices of the pin.

Please refer to the **Hardware Controlled I/O Functions** table for the complete hardware I/O and pull control function mapping.

## 3 Electrical Parameters

This section provides the electrical parameters which are implementation-specific for the XMC1300.

### 3.1 General Parameters

### 3.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XMC1300 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

- CC

- Such parameters indicate **C**ontroller **C**haracteristics, which are distinctive feature of the XMC1300 and must be regarded for a system design.

- SR

Such parameters indicate **S**ystem Requirements, which must be provided by the application system in which the XMC1300 is designed in.

## 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 11 Absolute Maximum Rating Parameters

| Parameter                                                                                                              | Symbol               |    |      | Va   | lues                          | Unit | Note /             |

|------------------------------------------------------------------------------------------------------------------------|----------------------|----|------|------|-------------------------------|------|--------------------|

|                                                                                                                        |                      |    | Min  | Тур. | Max.                          | -    | Test Cond ition    |

| Junction temperature                                                                                                   | $T_{J}$              | SR | -40  | _    | 115                           | °C   | _                  |

| Storage temperature                                                                                                    | $T_{ST}$             | SR | -40  | _    | 125                           | °C   | _                  |

| $\begin{tabular}{lll} \hline & Voltage on power supply pin \\ & with respect to $V_{\rm SSP}$ \\ \hline \end{tabular}$ | $V_{DDP}$            | SR | -0.3 | _    | 6                             | V    | -                  |

| Voltage on digital pins with respect to $V_{\rm SSP}^{\rm 1)}$                                                         | $V_{IN}$             | SR | -0.5 | _    | $V_{\rm DDP}$ + 0.5 or max. 6 | V    | whichever is lower |

| Voltage on P2 pins with respect to $V_{\rm SSP}^{\rm 2)}$                                                              | $V_{INP2}$           | SR | -0.3 | _    | $V_{\rm DDP}$ + 0.3           | V    | _                  |

| Voltage on analog input pins with respect to $V_{\rm SSP}$                                                             | $V_{AIN} \ V_{AREF}$ | SR | -0.5 | _    | $V_{\rm DDP}$ + 0.5 or max. 6 | ٧    | whichever is lower |

| Input current on any pin during overload condition                                                                     | $I_{IN}$             | SR | -10  | _    | 10                            | mA   | _                  |

| Absolute maximum sum of all input currents during overload condition                                                   | $\Sigma I_{IN}$      | SR | -50  | _    | +50                           | mA   | _                  |

<sup>1)</sup> Excluding port pins P2.[1,2,6,7,8,9,11].

<sup>2)</sup> Applicable to port pins P2.[1,2,6,7,8,9,11].

Table 16 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Symbol      |    | Limit \                                                   | /alues                    | Unit | Test Conditions                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----|-----------------------------------------------------------|---------------------------|------|---------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |    | Min.                                                      | Max.                      |      |                                                                     |

| Input Hysteresis <sup>8)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | HYS         | СС | $0.08 	imes V_{	extsf{DDP}}$                              | _                         | V    | CMOS Mode (5 V),<br>Standard Hysteresis                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |    | $0.03 	imes V_{ m DDP}$                                   | _                         | V    | CMOS Mode (3.3 V),<br>Standard Hysteresis                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |    | $\begin{array}{c} 0.02 \times \\ V_{\rm DDP} \end{array}$ | _                         | V    | CMOS Mode (2.2 V),<br>Standard Hysteresis                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |    | $0.5	imes V_{	extsf{DDP}}$                                | $0.75 \times V_{\rm DDP}$ | V    | CMOS Mode(5 V),<br>Large Hysteresis                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |    | $0.4	imes V_{	extsf{DDP}}$                                | $0.75 	imes V_{ m DDP}$   | V    | CMOS Mode(3.3 V),<br>Large Hysteresis                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |    | $0.2 	imes V_{	extsf{DDP}}$                               | $0.65 	imes V_{ m DDP}$   | V    | CMOS Mode(2.2 V),<br>Large Hysteresis                               |

| Pin capacitance (digital inputs/outputs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $C_{IO}$    | CC | _                                                         | 10                        | pF   |                                                                     |

| Pull-up resistor on port pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $R_{PUP}$   | CC | 20                                                        | 50                        | kohm | $V_{IN} = V_{SSP}$                                                  |

| Pull-down resistor on port pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $R_{PDP}$   | CC | 20                                                        | 50                        | kohm | $V_{IN} = V_{DDP}$                                                  |

| Input leakage current <sup>9)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $I_{OZP}$   | CC | -1                                                        | 1                         | μΑ   | $0 < V_{\rm IN} < V_{\rm DDP},$ $T_{\rm A} \le 105~{\rm ^{\circ}C}$ |

| Voltage on any pin during $V_{DDP}$ power off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{PO}$    | SR | _                                                         | 0.3                       | V    | 10)                                                                 |

| $\label{eq:maximum}                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $I_{MP}$    | SR | -10                                                       | 11                        | mA   | -                                                                   |

| Maximum current per high currrent pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $I_{MP1A}$  | SR | -10                                                       | 50                        | mA   | _                                                                   |

| $\begin{tabular}{ll} \hline & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $I_{MVDD1}$ | SR | _                                                         | 130                       | mA   | 18)                                                                 |

| $\begin{tabular}{ll} \hline & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & $ | $I_{MVDD2}$ | SR | _                                                         | 260                       | mA   | 18)                                                                 |

Table 17 ADC Characteristics (Operating Conditions apply)<sup>1)</sup> (cont'd)

| Parameter                                        | Symbol                        |      | Values |                         | Unit                       | Note / Test Condition                                                  |  |

|--------------------------------------------------|-------------------------------|------|--------|-------------------------|----------------------------|------------------------------------------------------------------------|--|

|                                                  |                               | Min. | Тур.   | Max.                    |                            |                                                                        |  |

| Gain settings                                    | $G_{IN}CC$                    | 1    | 1      |                         | _                          | GNCTRxz.GAINy = 00 <sub>B</sub> (unity gain)                           |  |

|                                                  |                               | 3    |        |                         | _                          | GNCTRxz.GAINy=01 <sub>B</sub> (gain g1)                                |  |

|                                                  |                               | 6    |        |                         | _                          | GNCTRxz.GAINy = 10 <sub>B</sub> (gain g2)                              |  |

|                                                  |                               | 12   |        |                         | _                          | GNCTRxz.GAINy=11 <sub>B</sub> (gain g3)                                |  |

| Sample Time                                      | t <sub>sample</sub> CC        | 3    | _      | _                       | $f_{ADC}$                  | $V_{\rm DD}$ = 5.0 V                                                   |  |

|                                                  |                               | 3    | _      | _                       | $f_{ADC}$                  | $V_{\mathrm{DD}}$ = 3.3 V                                              |  |

|                                                  |                               | 30   | _      | _                       | $\frac{1}{f_{\text{ADC}}}$ | $V_{\mathrm{DD}}$ = 2.0 V                                              |  |

| Sigma delta loop hold time                       | t <sub>SD_hold</sub>          | 20   | _      | _                       | μS                         | Residual charge stored in an active sigma delta loop remains available |  |

| Conversion time in fast compare mode             | t <sub>CF</sub> CC            | 9    | 1      |                         | $\frac{1}{f_{\text{ADC}}}$ | 2)                                                                     |  |

| Conversion time in 12-bit mode                   | t <sub>C12</sub> CC           | 20   |        |                         | $f_{ADC}$                  | 2)                                                                     |  |

| Maximum sample rate in 12-bit mode <sup>3)</sup> | $f_{\mathrm{C12}}\mathrm{CC}$ | _    | _      | f <sub>ADC</sub> / 42.5 | _                          | 1 sample pending                                                       |  |

|                                                  |                               | _    | _      | f <sub>ADC</sub> / 62.5 | _                          | 2 samples pending                                                      |  |

| Conversion time in 10-bit mode                   | <i>t</i> <sub>C10</sub> CC    | 18   |        |                         | $f_{\rm ADC}$              | 2)                                                                     |  |

| Maximum sample rate in 10-bit mode <sup>3)</sup> | $f_{\mathrm{C10}}\mathrm{CC}$ | _    | _      | f <sub>ADC</sub> / 40.5 | _                          | 1 sample pending                                                       |  |

|                                                  |                               | _    | _      | f <sub>ADC</sub> / 58.5 | _                          | 2 samples pending                                                      |  |

| Conversion time in 8-bit mode                    | t <sub>C8</sub> CC            | 16   |        |                         | $f_{\mathrm{ADC}}$         | 2)                                                                     |  |

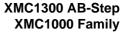

## 3.2.3 Out of Range Comparator (ORC) Characteristics

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{\rm AIN}$ ) above the  $V_{\rm DDP}$  on selected input pins (ORCx.AIN) and generates a service request trigger (ORCx.OUT).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 18 Out of Range Comparator (ORC) Characteristics (Operating Conditions apply; V<sub>DDP</sub> = 3.0 V - 5.5 V; C<sub>I</sub> = 0.25 pF)

| Parameter                 | Symbol        |    |      | Values |      |    | Note / Test Condition                     |

|---------------------------|---------------|----|------|--------|------|----|-------------------------------------------|

|                           |               |    | Min. | Тур.   | Max. |    |                                           |

| DC Switching Level        | $V_{ODC}$     | CC | 54   | _      | 183  | mV | $V$ AIN $\geq V_{DDP}$ + $V_{ODC}$        |

| Hysteresis                | $V_{OHYS}$    | CC | 15   | _      | 54   | mV |                                           |

| Always detected           | $t_{OPDD}$    | CC | 103  | _      | -    | ns | $V_{AIN} \geq V_{DDP}$ + 150 mV           |

| Overvoltage Pulse         |               |    | 88   | _      | -    | ns | $V_{AIN} \geq V_{DDP}$ + 350 mV           |

| Never detected            | $t_{OPDN}$    | CC | _    | _      | 21   | ns | $V_{AIN} \geq V_{DDP}$ + 150 mV           |

| Overvoltage Pulse         |               |    | _    | _      | 11   | ns | $V_{AIN} \geq V_{DDP}$ + 350 mV           |

| Detection Delay of a      | $t_{\sf ODD}$ | CC | 39   | _      | 132  | ns | $V_{AIN} \geq V_{DDP}$ + 150 mV           |

| persistent<br>Overvoltage |               |    | 31   | -      | 121  | ns | $V_{AIN} \geq V_{DDP}$ + 350 mV           |

| Release Delay             | $t_{ORD}$     | CC | 44   | _      | 240  | ns | $V_{AIN} \leq V_{DDP};  V_{DDP} = 5 \; V$ |

|                           |               |    | 57   | _      | 340  | ns | $V_{AIN} \leq V_{DDP};  V_{DDP} = 3.3  V$ |

| Enable Delay              | $t_{\sf OED}$ | CC | _    | _      | 300  | ns | ORCCTRL.ENORCx = 1                        |

Figure 12 ORCx.OUT Trigger Generation

Subject to Agreement on the Use of Product Information

Table 21 Power Supply Parameters;  $V_{DDP} = 5V$

| Parameter                                                                 | Symbol                | Values |                    |      | Unit   | Note /         |

|---------------------------------------------------------------------------|-----------------------|--------|--------------------|------|--------|----------------|

|                                                                           |                       | Min    | Typ. <sup>1)</sup> | Max. |        | Test Condition |

| Sleep mode current                                                        | $I_{DDPSD}CC$         | _      | 1.8                | -    | mA     | 32 / 64        |

| Peripherals clock disabled                                                |                       |        | 1.7                | -    | mA     | 24 / 48        |

| Flash active $f_{\text{MCLK}}/f_{\text{PCLK}}$ in MHz <sup>5)</sup>       |                       |        | 1.6                | -    | mA     | 16 / 32        |

| JMCLK / JPCLK III WII IZ                                                  |                       |        | 1.5                | -    | mA     | 8 / 16         |

|                                                                           |                       |        | 1.4                | -    | mA     | 1/1            |

| Sleep mode current                                                        | I <sub>DDPSR</sub> CC | _      | 1.2                | -    | mA     | 32 / 64        |

| Peripherals clock disabled                                                |                       |        | 1.1                | -    | mA     | 24 / 48        |

| Flash powered down $f_{\text{MCLK}}/f_{\text{PCLK}}$ in MHz <sup>6)</sup> |                       |        | 1.0                | -    | mA     | 16 / 32        |

| JMCLK JPCLK                                                               |                       |        | 8.0                | -    | mA     | 8 / 16         |

|                                                                           |                       |        | 0.7                | -    | mA     | 1/1            |

| Deep Sleep mode current <sup>7)</sup>                                     | $I_{DDPDS}CC$         | _      | 0.24               | -    | mA     |                |

| Wake-up time from Sleep to Active mode <sup>8)</sup>                      | t <sub>SSA</sub> CC   | _      | 6                  | -    | cycles |                |

| Wake-up time from Deep<br>Sleep to Active mode <sup>9)</sup>              | t <sub>DSA</sub> CC   | _      | 280                | -    | μsec   |                |

- 1) The typical values are measured at  $T_{\rm A}$  = + 25 °C and VDDP = 5 V.

- 2) CPU and all peripherals clock enabled, Flash is in active mode.

- 3) CPU enabled, all peripherals clock disabled, Flash is in active mode.

- 4) CPU in sleep, all peripherals clock enabled and Flash is in active mode.

- 5) CPU in sleep, Flash is in active mode.

- 6) CPU in sleep, Flash is powered down and code executed from RAM after wake-up.

- 7) CPU in sleep, peripherals clock disabled, Flash is powered down and code executed from RAM after wake-up.

- 8) CPU in sleep, Flash is in active mode during sleep mode.

- 9) CPU in sleep, Flash is in powered down mode during deep sleep mode.

**Table 22** provides the active current consumption of some modules operating at 5 V power supply at 25° C. The typical values shown are used as a reference guide on the current consumption when these modules are enabled.

Table 22 Typical Active Current Consumption

| Active Current<br>Consumption | Symbol                | Limit<br>Values | Unit | Test Condition                                                    |  |  |  |

|-------------------------------|-----------------------|-----------------|------|-------------------------------------------------------------------|--|--|--|

|                               |                       | Тур.            |      |                                                                   |  |  |  |

| Baseload current              | $I_{CPUDDC}$          | 5.04            | mA   | Modules including Core, SCU, PORT, memories, ANATOP <sup>1)</sup> |  |  |  |

| VADC and SHS                  | $I_{ADCDDC}$          | 3.4             | mA   | Set CGATCLR0.VADC to 1 <sup>2)</sup>                              |  |  |  |

| USIC0                         | $I_{\rm USICODDC}$    | 0.87            | mA   | Set CGATCLR0.USIC0 to 13)                                         |  |  |  |

| CCU40                         | $I_{\text{CCU40DDC}}$ | 0.94            | mA   | Set CGATCLR0.CCU40 to 1 <sup>4)</sup>                             |  |  |  |

| CCU80                         | $I_{\text{CCU80DDC}}$ | 0.42            | mA   | Set CGATCLR0.CCU80 to 1 <sup>5)</sup>                             |  |  |  |

| POSIF0                        | $I_{PIF0DDC}$         | 0.26            | mA   | Set CGATCLR0.POSIF0 to 16)                                        |  |  |  |

| BCCU0                         | $I_{BCCU0DDC}$        | 0.24            | mA   | Set CGATCLR0.BCCU0 to 17)                                         |  |  |  |

| MATH                          | $I_{MATHDDC}$         | 0.35            | mA   | Set CGATCLR0.MATH to 18)                                          |  |  |  |

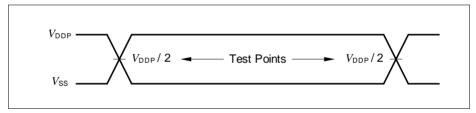

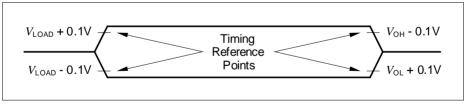

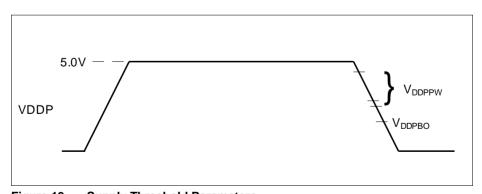

| WDT                           | $I_{WDTDDC}$          | 0.03            | mA   | Set CGATCLR0.WDT to 19)                                           |  |  |  |