Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 32MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 26                                                                                 |

| Program Memory Size        | 32KB (32K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                                    |

| Supplier Device Package    | PG-TSSOP-38-9                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1302t038x0032abxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 5 Quali | ty Declaration | 1 <del>7</del> | 77 |

|---------|----------------|----------------|----|

|---------|----------------|----------------|----|

#### Summary of Features

- Ultra low power consumption

- Nested Vectored Interrupt Controller (NVIC)

- · Event Request Unit (ERU) for processing of external and internal service requests

- MATH Co-processor (MATH)

- CORDIC unit for trigonometric calculation

- division unit

### **On-Chip Memories**

- 8 kbytes on-chip ROM

- 16 kbytes on-chip high-speed SRAM

- up to 200 kbytes on-chip Flash program and data memory

### **Communication Peripherals**

• Two Universal Serial Interface Channels (USIC), usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

## **Analog Frontend Peripherals**

- A/D Converters

- up to 12 analog input pins

- 2 sample and hold stages with 8 analog input channels each

- fast 12-bit analog to digital converter with adjustable gain

- Up to 8 channels of out of range comparators (ORC)

- Up to 3 fast analog comparators (ACMP)

- Temperature Sensor (TSE)

## **Industrial Control Peripherals**

- Capture/Compare Units 4 (CCU4) as general purpose timers

- Capture/Compare Units 8 (CCU8) for motor control and power conversion

- · Position Interfaces (POSIF) for hall and quadrature encoders and motor positioning

- Brightness and Colour Control Unit (BCCU), for LED color and dimming application

## System Control

- Window Watchdog Timer (WDT) for safety sensitive applications

- Real Time Clock module with alarm support (RTC)

- System Control Unit (SCU) for system configuration and control

- Pseudo random number generator (PRNG) for fast random data generation

## Input/Output Lines

- Tri-stated in input mode

- Push/pull or open drain output mode

### **General Device Information**

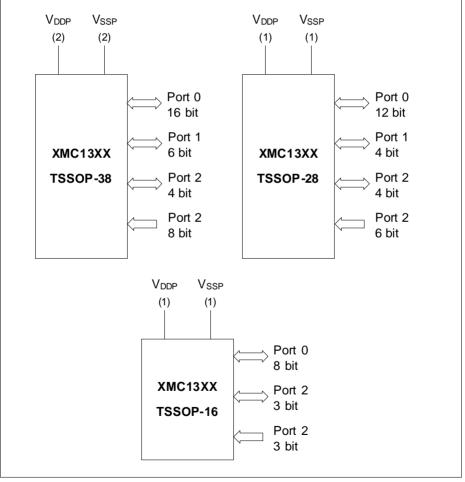

## 2 General Device Information

This section summarizes the logic symbols and package pin configurations with a detailed list of the functional I/O mapping.

## 2.1 Logic Symbols

## Figure 2 XMC1300 Logic Symbol for TSSOP-38, TSSOP-28 and TSSOP-16

### **General Device Information**

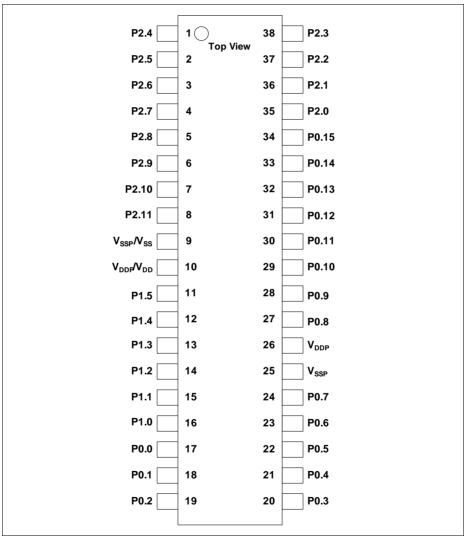

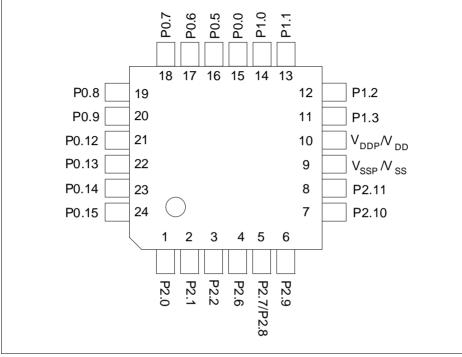

## 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the different packages.

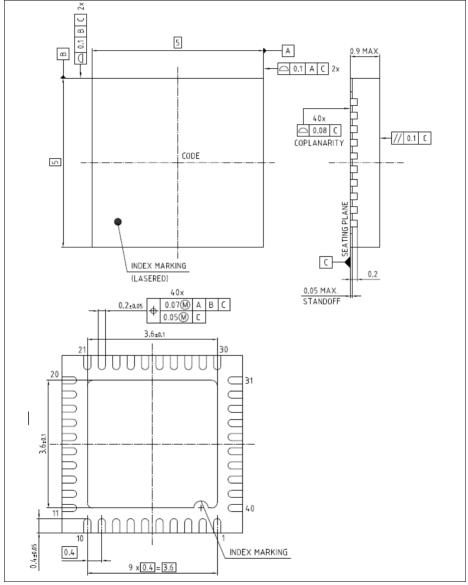

Figure 4 XMC1300 PG-TSSOP-38 Pin Configuration (top view)

## XMC1300 AB-Step XMC1000 Family

### **General Device Information**

Figure 7 XMC1300 PG-VQFN-24 Pin Configuration (top view)

#### **General Device Information**

## 2.2.1 Package Pin Summary

The following general building block is used to describe each pin:

### Table 5 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad Type |

|----------|-----------|-----------|--------------|

| Px.y     | Ν         | Ν         | Pad Class    |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type:

- STD\_INOUT(standard bi-directional pads)

- STD\_INOUT/AN (standard bi-directional pads with analog input)

- High Current (high current bi-directional pads)

- STD\_IN/AN (standard input pads with analog input)

- Power (power supply)

Details about the pad properties are defined in the Electrical Parameters.

| Function | VQFN<br>40 | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24 | TSSOP<br>16 | Pad<br>Type   | Notes |

|----------|------------|-------------|-------------|------------|-------------|---------------|-------|

| P0.0     | 23         | 17          | 13          | 15         | 7           | STD_IN<br>OUT |       |

| P0.1     | 24         | 18          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.2     | 25         | 19          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.3     | 26         | 20          | -           | -          | -           | STD_IN<br>OUT |       |

| P0.4     | 27         | 21          | 14          | -          | -           | STD_IN<br>OUT |       |

| P0.5     | 28         | 22          | 15          | 16         | 8           | STD_IN<br>OUT |       |

| P0.6     | 29         | 23          | 16          | 17         | 9           | STD_IN<br>OUT |       |

## Table 6 Package Pin Mapping

#### **General Device Information**

| Function | VQFN<br>40  | TSSOP<br>38 | TSSOP<br>28 | VQFN<br>24  | TSSOP<br>16 | Pad<br>Type | Notes                                                                                                                                                                                                                                                                               |

|----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSSP     | 31          | 25          | -           | -           | -           | Power       | I/O port ground                                                                                                                                                                                                                                                                     |

| VDDP     | 32          | 26          | -           | -           | -           | Power       | I/O port supply                                                                                                                                                                                                                                                                     |

| VSSP     | Exp.<br>Pad | -           | -           | Exp.<br>Pad | -           | Power       | Exposed Die<br>Pad<br>The exposed die<br>pad is connected<br>internally to<br>VSSP. For proper<br>operation, it is<br>mandatory to<br>connect the<br>exposed pad to<br>the board ground<br>For thermal<br>aspects, please<br>refer to the<br>Package and<br>Reliability<br>chapter. |

## Table 6Package Pin Mapping (cont'd)

## 2.2.2 Port I/O Function Description

The following general building block is used to describe the I/O functions of each PORT pin:

## Table 7 Port I/O Function Description

| Function | Outputs  |          | Inputs   |          |  |  |  |

|----------|----------|----------|----------|----------|--|--|--|

|          | ALT1     | ALTn     | Input    | Input    |  |  |  |

| P0.0     |          | MODA.OUT | MODC.INA |          |  |  |  |

| Pn.y     | MODA.OUT |          | MODA.INA | MODC.INB |  |  |  |

## Table 9 Port I/O Functions

| Function | Outputs                  |      |                |                           |                 |                           |                           | Inputs            |                |                 |                |                    |                    |                |                |                |                    |

|----------|--------------------------|------|----------------|---------------------------|-----------------|---------------------------|---------------------------|-------------------|----------------|-----------------|----------------|--------------------|--------------------|----------------|----------------|----------------|--------------------|

|          | ALT1                     | ALT2 | ALT3           | ALT4                      | ALT5            | ALT6                      | ALT7                      | Input             | Input          | Input           | Input          | Input              | Input              | Input          | Input          | Input          | Input              |

| P0.0     | ERU0.<br>PDOUT0          |      | ERU0.<br>GOUT0 | CCU40.<br>OUT0            | CCU80.<br>OUT00 | USIC0_C<br>H0.SELO<br>0   | USIC0_C<br>H1.SELO<br>0   | BCCU0.<br>TRAPINB | CCU40.<br>IN0C |                 |                | USIC0_C<br>H0.DX2A | USIC0_C<br>H1.DX2A |                |                |                |                    |

| P0.1     | ERU0.<br>PDOUT1          |      | ERU0.<br>GOUT1 | CCU40.<br>OUT1            | CCU80.<br>OUT01 | BCCU0.<br>OUT8            | SCU.<br>VDROP             |                   | CCU40.<br>IN1C |                 |                |                    |                    |                |                |                |                    |

| P0.2     | ERU0.<br>PDOUT2          |      | ERU0.<br>GOUT2 | CCU40.<br>OUT2            | CCU80.<br>OUT02 | VADC0.<br>EMUX02          | CCU80.<br>OUT10           |                   | CCU40.<br>IN2C |                 |                |                    |                    |                |                |                |                    |

| P0.3     | ERU0.<br>PDOUT3          |      | ERU0.<br>GOUT3 | CCU40.<br>OUT3            | CCU80.<br>OUT03 | VADC0.<br>EMUX01          | CCU80.<br>OUT11           |                   | CCU40.<br>IN3C |                 |                |                    |                    |                |                |                |                    |

| P0.4     | BCCU0.<br>OUT0           |      |                | CCU40.<br>OUT1            | CCU80.<br>OUT13 | VADC0.<br>EMUX00          | WWDT.<br>SERVICE<br>_OUT  |                   | CCU80.<br>IN0B |                 |                |                    |                    |                |                |                |                    |

| P0.5     | BCCU0.<br>OUT1           |      |                | CCU40.<br>OUT0            | CCU80.<br>OUT12 | ACMP2.<br>OUT             | CCU80.<br>OUT01           |                   | CCU80.<br>IN1B |                 |                |                    |                    |                |                |                |                    |

| P0.6     | BCCU0.<br>OUT2           |      |                | CCU40.<br>OUT0            | CCU80.<br>OUT11 | USIC0_C<br>H1.MCLK<br>OUT | USIC0_C<br>H1.DOUT<br>0   |                   | CCU40.<br>IN0B |                 |                | USIC0_C<br>H1.DX0C |                    |                |                |                |                    |

| P0.7     | BCCU0.<br>OUT3           |      |                | CCU40.<br>OUT1            | CCU80.<br>OUT10 | USIC0_C<br>H0.SCLK<br>OUT | USIC0_C<br>H1.DOUT<br>0   |                   | CCU40.<br>IN1B |                 |                |                    | USIC0_C<br>H1.DX0D |                |                |                |                    |

| P0.8     | BCCU0.<br>OUT4           |      |                | CCU40.<br>OUT2            | CCU80.<br>OUT20 | USIC0_C<br>H0.SCLK<br>OUT | USIC0_C<br>H1.SCLK<br>OUT |                   | CCU40.<br>IN2B |                 |                | USIC0_C<br>H0.DX1B | USIC0_C<br>H1.DX1B |                |                |                |                    |

| P0.9     | BCCU0.<br>OUT5           |      |                | CCU40.<br>OUT3            | CCU80.<br>OUT21 | USIC0_C<br>H0.SELO<br>0   | USIC0_C<br>H1.SELO<br>0   |                   | CCU40.<br>IN3B |                 |                | USIC0_C<br>H0.DX2B | USIC0_C<br>H1.DX2B |                |                |                |                    |

| P0.10    | BCCU0.<br>OUT6           |      |                | ACMP0.<br>OUT             | CCU80.<br>OUT22 | USIC0_C<br>H0.SELO<br>1   | USIC0_C<br>H1.SELO<br>1   |                   | CCU80.<br>IN2B |                 |                | USIC0_C<br>H0.DX2C | USIC0_C<br>H1.DX2C |                |                |                |                    |

| P0.11    | BCCU0.<br>OUT7           |      |                | USIC0_C<br>H0.MCLK<br>OUT | CCU80.<br>OUT23 | USIC0_C<br>H0.SELO<br>2   | USIC0_C<br>H1.SELO<br>2   |                   |                |                 |                | USIC0_C<br>H0.DX2D | USIC0_C<br>H1.DX2D |                |                |                |                    |

| P0.12    | BCCU0.<br>OUT6           |      |                |                           | CCU80.<br>OUT33 | USIC0_C<br>H0.SELO<br>3   | CCU80.<br>OUT20           | BCCU0.<br>TRAPINA | CCU40.<br>IN0A | CCU40.<br>IN1A  | CCU40.<br>IN2A | CCU40.<br>IN3A     | CCU80.<br>IN0A     | CCU80.<br>IN1A | CCU80.<br>IN2A | CCU80.<br>IN3A | USIC0_C<br>H0.DX2E |

| P0.13    | WWDT.<br>SERVICE<br>_OUT |      |                |                           | CCU80.<br>OUT32 | USIC0_C<br>H0.SELO<br>4   | CCU80.<br>OUT21           |                   | CCU80.<br>IN3B | POSIF0.<br>IN0B |                | USIC0_C<br>H0.DX2F |                    |                |                |                |                    |

Infineon

Data Sheet

XMC1300 AB-Step XMC1000 Family

## Table 9Port I/O Functions (cont'd)

| Function | Outputs          |                           |                |                           |                 |                           |                           | Inputs        |                 |                    |              |                    |                    |                    |              |       |       |

|----------|------------------|---------------------------|----------------|---------------------------|-----------------|---------------------------|---------------------------|---------------|-----------------|--------------------|--------------|--------------------|--------------------|--------------------|--------------|-------|-------|

|          | ALT1             | ALT2                      | ALT3           | ALT4                      | ALT5            | ALT6                      | ALT7                      | Input         | Input           | Input              | Input        | Input              | Input              | Input              | Input        | Input | Input |

| P0.14    | BCCU0.<br>OUT7   |                           |                |                           | CCU80.<br>OUT31 | USIC0_C<br>H0.DOUT<br>0   |                           |               |                 | POSIF0.<br>IN1B    |              | USIC0_C<br>H0.DX0A |                    |                    |              |       |       |

| P0.15    | BCCU0.<br>OUT8   |                           |                |                           | CCU80.<br>OUT30 | USIC0_C<br>H0.DOUT<br>0   | USIC0_C<br>H1.MCLK<br>OUT |               |                 | POSIF0.<br>IN2B    |              | USIC0_C<br>H0.DX0B |                    |                    |              |       |       |

| P1.0     | BCCU0.<br>OUT0   | CCU40.<br>OUT0            |                |                           | CCU80.<br>OUT00 | ACMP1.<br>OUT             | USIC0_C<br>H0.DOUT<br>0   |               |                 | POSIF0.<br>IN2A    |              | USIC0_C<br>H0.DX0C |                    |                    |              |       |       |

| P1.1     | VADC0.<br>EMUX00 | CCU40.<br>OUT1            |                |                           | CCU80.<br>OUT01 | USIC0_C<br>H0.DOUT<br>0   | USIC0_C<br>H1.SELO<br>0   |               |                 | POSIF0.<br>IN1A    |              | USIC0_C<br>H0.DX0D | USIC0_C<br>H0.DX1D | USIC0_C<br>H1.DX2E |              |       |       |

| P1.2     | VADC0.<br>EMUX01 | CCU40.<br>OUT2            |                |                           | CCU80.<br>OUT10 | ACMP2.<br>OUT             | USIC0_C<br>H1.DOUT<br>0   |               |                 | POSIF0.<br>IN0A    |              | USIC0_C<br>H1.DX0B |                    |                    |              |       |       |

| P1.3     | VADC0.<br>EMUX02 | CCU40.<br>OUT3            |                |                           | CCU80.<br>OUT11 | USIC0_C<br>H1.SCLK<br>OUT | USIC0_C<br>H1.DOUT<br>0   |               |                 |                    |              | USIC0_C<br>H1.DX0A | USIC0_C<br>H1.DX1A |                    |              |       |       |

| P1.4     | VADC0.<br>EMUX10 | USIC0_C<br>H1.SCLK<br>OUT |                |                           | CCU80.<br>OUT20 | USIC0_C<br>H0.SELO<br>0   | USIC0_C<br>H1.SELO<br>1   |               |                 |                    |              | USIC0_C<br>H0.DX5E | USIC0_C<br>H1.DX5E |                    |              |       |       |

| P1.5     | VADC0.<br>EMUX11 | USIC0_C<br>H0.DOUT<br>0   |                | BCCU0.<br>OUT1            | CCU80.<br>OUT21 | USIC0_C<br>H0.SELO<br>1   | USIC0_C<br>H1.SELO<br>2   |               |                 |                    |              | USIC0_C<br>H1.DX5F |                    |                    |              |       |       |

| P1.6     | VADC0.<br>EMUX12 | USIC0_C<br>H1.DOUT<br>0   |                | USIC0_C<br>H0.SCLK<br>OUT | BCCU0.<br>OUT2  | USIC0_C<br>H0.SELO<br>2   | USIC0_C<br>H1.SELO<br>3   |               |                 | USIC0_C<br>H0.DX5F |              |                    |                    |                    |              |       |       |

| P2.0     | ERU0.<br>PDOUT3  | CCU40.<br>OUT0            | ERU0.<br>GOUT3 |                           | CCU80.<br>OUT20 | USIC0_C<br>H0.DOUT<br>0   | USIC0_C<br>H0.SCLK<br>OUT |               | VADC0.<br>G0CH5 |                    | ERU0.0B<br>0 | USIC0_C<br>H0.DX0E | USIC0_C<br>H0.DX1E | USIC0_C<br>H1.DX2F |              |       |       |

| P2.1     | ERU0.<br>PDOUT2  | CCU40.<br>OUT1            | ERU0.<br>GOUT2 |                           | CCU80.<br>OUT21 | USIC0_C<br>H0.DOUT<br>0   | USIC0_C<br>H1.SCLK<br>OUT | ACMP2.I<br>NP | VADC0.<br>G0CH6 |                    | ERU0.1B<br>0 | USIC0_C<br>H0.DX0F | USIC0_C<br>H1.DX3A | USIC0_C<br>H1.DX4A |              |       |       |

| P2.2     |                  |                           |                |                           |                 |                           |                           | ACMP2.I<br>NN | VADC0.<br>G0CH7 |                    | ERU0.0B      | USIC0_C<br>H0.DX3A | USIC0_C<br>H0.DX4A | USIC0_C<br>H1.DX5A | ORC0.AI      |       |       |

| P2.3     |                  | 1                         |                |                           |                 |                           |                           |               | VADC0.<br>G1CH5 |                    |              |                    |                    | USIC0_C<br>H1.DX4C |              |       |       |

| P2.4     |                  |                           |                |                           |                 |                           |                           |               | VADC0.<br>G1CH6 |                    | ERU0.0A<br>1 | USIC0_C<br>H0.DX3B | USIC0_C<br>H0.DX4B | USIC0_C<br>H1.DX5B | ORC2.AI<br>N |       |       |

| P2.5     |                  |                           |                |                           |                 |                           |                           |               | VADC0.<br>G1CH7 |                    | ERU0.1A<br>1 | USIC0_C<br>H0.DX5D | USIC0_C<br>H1.DX3E | USIC0_C<br>H1.DX4E | ORC3.AI<br>N |       |       |

Infineon

XMC1300 AB-Step XMC1000 Family

Data Sheet

## Table 10 Hardware Controlled I/O Functions

| Function | Outputs |                 | Inputs |                 | Pull Control |            |            |            |  |  |

|----------|---------|-----------------|--------|-----------------|--------------|------------|------------|------------|--|--|

|          | HWO0    | HWO1            | HWIO   | HWI1            | HW0_PD       | HW0_PU     | HW1_PD     | HW1_PU     |  |  |

| P0.0     |         |                 |        |                 |              |            |            |            |  |  |

| P0.1     |         |                 |        |                 |              |            |            |            |  |  |

| P0.2     |         |                 |        |                 |              |            |            |            |  |  |

| P0.3     |         |                 |        |                 |              |            |            |            |  |  |

| P0.4     |         |                 |        |                 |              |            |            |            |  |  |

| P0.5     |         |                 |        |                 |              |            |            |            |  |  |

| P0.6     |         |                 |        |                 |              |            |            |            |  |  |

| P0.7     |         |                 |        |                 |              |            |            |            |  |  |

| P0.8     |         |                 |        |                 |              |            |            |            |  |  |

| P0.9     |         |                 |        |                 |              |            |            |            |  |  |

| P0.10    |         |                 |        |                 |              |            |            |            |  |  |

| P0.11    |         |                 |        |                 |              |            |            |            |  |  |

| P0.12    |         |                 |        |                 |              |            |            |            |  |  |

| P0.13    |         |                 |        |                 |              |            |            |            |  |  |

| P0.14    |         |                 |        |                 |              |            |            |            |  |  |

| P0.15    |         |                 |        |                 |              |            |            |            |  |  |

| P1.0     |         | USIC0_CH0.DOUT0 |        | USIC0_CH0.HWIN0 | BCCU0.OUT2   | BCCU0.OUT2 |            |            |  |  |

| P1.1     |         | USIC0_CH0.DOUT1 |        | USIC0_CH0.HWIN1 | BCCU0.OUT3   | BCCU0.OUT3 |            |            |  |  |

| P1.2     |         | USIC0_CH0.DOUT2 |        | USIC0_CH0.HWIN2 | BCCU0.OUT4   | BCCU0.OUT4 |            |            |  |  |

| P1.3     |         | USIC0_CH0.DOUT3 |        | USIC0_CH0.HWIN3 | BCCU0.OUT5   | BCCU0.OUT5 |            |            |  |  |

| P1.4     |         |                 |        |                 | BCCU0.OUT6   | BCCU0.OUT6 |            |            |  |  |

| P1.5     |         |                 |        |                 | BCCU0.OUT7   | BCCU0.OUT7 |            |            |  |  |

| P1.6     |         |                 |        |                 | BCCU0.OUT8   | BCCU0.OUT8 |            |            |  |  |

| P2.0     |         |                 |        |                 | BCCU0.OUT1   | BCCU0.OUT1 |            |            |  |  |

| 2.1      |         |                 |        |                 | BCCU0.OUT6   | BCCU0.OUT6 |            |            |  |  |

| 2.2      |         |                 |        |                 | BCCU0.OUT0   | BCCU0.OUT0 | CCU40.OUT3 | CCU40.OUT3 |  |  |

| P2.3     |         |                 |        |                 | ACMP2.OUT    | ACMP2.OUT  |            |            |  |  |

| P2.4     |         |                 |        |                 | BCCU0.OUT8   | BCCU0.OUT8 |            |            |  |  |

| P2.5     |         |                 |        |                 | ACMP1.OUT    | ACMP1.OUT  |            |            |  |  |

XMC1300 AB-Step XMC1000 Family

Data Sheet

## Table 17 ADC Characteristics (Operating Conditions apply)<sup>1)</sup> (cont'd)

| Parameter                                        | Symbol                         | ١    | /alues | 5                          | Unit      | Note / Test Condition                                                                        |  |  |

|--------------------------------------------------|--------------------------------|------|--------|----------------------------|-----------|----------------------------------------------------------------------------------------------|--|--|

|                                                  |                                | Min. | Тур.   | Max.                       | 1         |                                                                                              |  |  |

| Maximum sample rate in 8-bit mode <sup>3)</sup>  | $f_{C8}$ CC                    | -    | -      | f <sub>ADC</sub> /<br>38.5 | -         | 1 sample<br>pending                                                                          |  |  |

|                                                  |                                | -    | -      | f <sub>ADC</sub> /<br>54.5 | -         | 2 samples<br>pending                                                                         |  |  |

| RMS noise <sup>4)</sup>                          | <i>EN</i> <sub>RMS</sub><br>CC | -    | 1.5    | _                          | LSB<br>12 | DC input,<br>$V_{DD} = 5.0 \text{ V},$<br>$V_{AIN = 2.5 \text{ V}},$<br>$25^{\circ}\text{C}$ |  |  |

| DNL error                                        | EA <sub>DNL</sub> CC           | -    | ±2.0   | -                          | LSB<br>12 |                                                                                              |  |  |

| INL error                                        | EA <sub>INL</sub> CC           | -    | ±4.0   | -                          | LSB<br>12 |                                                                                              |  |  |

| Gain error with external reference               | EA <sub>GAIN</sub><br>CC       | -    | ±0.5   | -                          | %         | SHSCFG.AREF = $00_B$ (calibrated)                                                            |  |  |

| Gain error with internal reference <sup>5)</sup> | EA <sub>GAIN</sub><br>CC       | -    | ±3.6   | -                          | %         | SHSCFG.AREF = 1X <sub>B</sub><br>(calibrated),<br>-40°C - 105°C                              |  |  |

|                                                  |                                | -    | ±2.0   | -                          | %         | SHSCFG.AREF = 1X <sub>B</sub><br>(calibrated),<br>0°C - 85°C                                 |  |  |

| Offset error                                     | EA <sub>OFF</sub> CC           | -    | ±8.0   | -                          | mV        | Calibrated,<br>$V_{\rm DD}$ = 5.0 V                                                          |  |  |

1) The parameters are defined for ADC clock frequency  $f_{SH}$  = 32MHz, SHSCFG.DIVS = 0000<sub>B</sub>. Usage of any other frequencies may affect the ADC performance.

2) No pending samples assumed, excluding sampling time and calibration.

3) Includes synchronization and calibration (average of gain and offset calibration).

4) This parameter can also be defined as an SNR value: SNR[dB] =  $20 \times \log(A_{MAXeff} / N_{RMS})$ . With  $A_{MAXeff} = 2^N / 2$ , SNR[dB] =  $20 \times \log (2048 / N_{RMS})$  [N = 12].  $N_{RMS} = 1.5$  LSB12, therefore, equals SNR =  $20 \times \log (2048 / 1.5) = 62.7$  dB.

5) Includes error from the reference voltage.

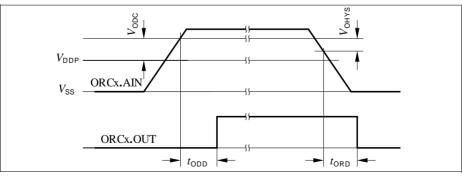

## 3.2.3 Out of Range Comparator (ORC) Characteristics

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{AIN}$ ) above the  $V_{DDP}$  on selected input pins (ORCx.AIN) and generates a service request trigger (ORCx.OUT).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                 | Symb              | ol |      | Value | 5    | Unit | Note / Test Condition                                              |

|---------------------------|-------------------|----|------|-------|------|------|--------------------------------------------------------------------|

|                           |                   |    | Min. | Тур.  | Max. |      |                                                                    |

| DC Switching Level        | $V_{ODC}$         | CC | 54   | _     | 183  | mV   | $VAIN \ge V_{DDP} + V_{ODC}$                                       |

| Hysteresis                | $V_{\rm OHYS}$    | СС | 15   | _     | 54   | mV   |                                                                    |

| Always detected           | t <sub>OPDD</sub> | СС | 103  | _     | -    | ns   | $V_{\text{AIN}} \ge V_{\text{DDP}}$ + 150 mV                       |

| Overvoltage Pulse         |                   |    | 88   | _     | -    | ns   | $V_{\text{AIN}} \ge V_{\text{DDP}}$ + 350 mV                       |

| Never detected            | t <sub>OPDN</sub> | СС | -    | -     | 21   | ns   | $V_{\text{AIN}} \ge V_{\text{DDP}}$ + 150 mV                       |

| Overvoltage Pulse         |                   |    | -    | _     | 11   | ns   | $V_{\text{AIN}} \ge V_{\text{DDP}}$ + 350 mV                       |

| Detection Delay of a      | t <sub>ODD</sub>  | CC | 39   | _     | 132  | ns   | $V_{\text{AIN}} \ge V_{\text{DDP}}$ + 150 mV                       |

| persistent<br>Overvoltage |                   |    | 31   | -     | 121  | ns   | $V_{\text{AIN}} \ge V_{\text{DDP}}$ + 350 mV                       |

| Release Delay             | t <sub>ORD</sub>  | CC | 44   | -     | 240  | ns   | $V_{\text{AIN}} \leq V_{\text{DDP}}; V_{\text{DDP}} = 5 \text{ V}$ |

|                           |                   |    | 57   | -     | 340  | ns   | $V_{\text{AIN}} \le V_{\text{DDP}}; V_{\text{DDP}} = 3.3$          |

| Enable Delay              | t <sub>OED</sub>  | CC | -    | -     | 300  | ns   | ORCCTRL.ENORCx =                                                   |

## Table 18Out of Range Comparator (ORC) Characteristics (Operating<br/>Conditions apply; V<sub>DDP</sub> = 3.0 V - 5.5 V; C<sub>1</sub> = 0.25 pF)

Figure 12 ORCx.OUT Trigger Generation

## 3.2.4 Analog Comparator Characteristics

Table 19 below shows the Analog Comparator characteristics.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Table 19 | Analog Comparator Characteristics (Operating Conditions apply) |

|----------|----------------------------------------------------------------|

|----------|----------------------------------------------------------------|

| Parameter                          | Symbol              |    | Li    | mit Val | ues                     | Unit | Notes/<br>Test Conditions                                               |  |

|------------------------------------|---------------------|----|-------|---------|-------------------------|------|-------------------------------------------------------------------------|--|

|                                    |                     |    | Min.  | Тур.    | Max.                    |      |                                                                         |  |

| Input Voltage                      | V <sub>CMP</sub>    | SR | -0.05 | -       | V <sub>DDP</sub> + 0.05 | V    |                                                                         |  |

| Input Offset                       | $V_{CMPOFF}$        | CC | -     | +/-3    | -                       | mV   | High power mode $\Delta V_{\rm CMP}$ < 200 mV                           |  |

|                                    |                     |    | -     | +/-20   | -                       | mV   | Low power mode $\Delta V_{\rm CMP}$ < 200 mV                            |  |

| Propagation<br>Delay <sup>1)</sup> | t <sub>PDELAY</sub> | CC | -     | 25      | -                       | ns   | High power mode, $\Delta V_{\rm CMP}$ = 100 mV                          |  |

|                                    |                     |    | -     | 80      | -                       | ns   | High power mode,<br>$\Delta V_{\rm CMP}$ = 25 mV                        |  |

|                                    |                     |    | -     | 250     | -                       | ns   | Low power mode,<br>$\Delta V_{\rm CMP}$ = 100 mV                        |  |

|                                    |                     |    | -     | 700     | -                       | ns   | Low power mode,<br>$\Delta V_{\rm CMP}$ = 25 mV                         |  |

| Current<br>Consumption             | I <sub>ACMP</sub>   | CC | _     | 100     | -                       | μA   | First active ACMP in high power mode, $\Delta V_{\rm CMP}$ > 30 mV      |  |

|                                    |                     |    | -     | 66      | _                       | μA   | Each additional<br>ACMP in high power<br>mode, $\Delta V_{CMP}$ > 30 mV |  |

|                                    |                     |    | -     | 10      | -                       | μA   | First active ACMP in low power mode                                     |  |

|                                    |                     |    | -     | 6       | -                       | μA   | Each additional<br>ACMP in low power<br>mode                            |  |

| Input Hysteresis                   | $V_{\rm HYS}$       | СС | -     | +/-15   | -                       | mV   |                                                                         |  |

| Filter Delay <sup>1)</sup>         | t <sub>FDELAY</sub> | CC | -     | 5       | -                       | ns   |                                                                         |  |

1) Total Analog Comparator Delay is the sum of Propagation Delay and Filter Delay.

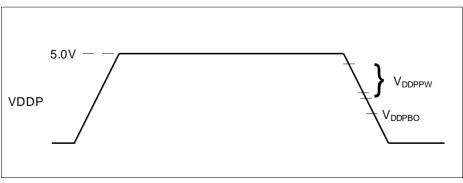

## 3.3.2 Power-Up and Supply Monitoring Characteristics

Table 24 provides the characteristics of the power-up and supply monitoring inXMC1300.

The guard band between the lowest valid operating voltage and the brownout reset threshold provides a margin for noise immunity and hysteresis. The electrical parameters may be violated while  $V_{\text{DDP}}$  is outside its operating range.

The brownout detection triggers a reset within the defined range. The prewarning detection can be used to trigger an early warning and issue corrective and/or fail-safe actions in case of a critical supply voltage drop.

| Parameter                       | Symbol                         | V                                                                | /alues |                 | Unit | Note /<br>Test Condition                                                    |

|---------------------------------|--------------------------------|------------------------------------------------------------------|--------|-----------------|------|-----------------------------------------------------------------------------|

|                                 |                                | Min.                                                             | Тур.   | Max.            |      |                                                                             |

| $V_{\text{DDP}}$ ramp-up time   | <i>t</i> <sub>RAMPUP</sub> SR  | $\begin{array}{c} V_{\rm DDP} / \\ S_{\rm VDDPrise} \end{array}$ | -      | 10 <sup>7</sup> | μS   |                                                                             |

| $V_{\rm DDP}$ slew rate         | $S_{\rm VDDPOP} \ {\sf SR}$    | 0                                                                | -      | 0.1             | V/µs | Slope during<br>normal operation                                            |

|                                 | S <sub>VDDP10</sub> SR         | 0                                                                | -      | 10              | V/µs | Slope during fast transient within +/- 10% of V <sub>DDP</sub>              |

|                                 | $S_{\rm VDDPrise}~{ m SR}$     | 0                                                                | -      | 10              | V/µs | Slope during<br>power-on or<br>restart after<br>brownout event              |

|                                 | $S_{\text{VDDPfall}}^{(1)}$ SR | 0                                                                | -      | 0.25            | V/µs | Slope during<br>supply falling out<br>of the +/-10%<br>limits <sup>2)</sup> |

| $V_{ m DDP}$ prewarning voltage | V <sub>DDPPW</sub> CC          | 2.1                                                              | 2.25   | 2.4             | V    | ANAVDEL.VDEL_<br>SELECT = 00 <sub>B</sub>                                   |

|                                 |                                | 2.85                                                             | 3      | 3.15            | V    | ANAVDEL.VDEL_<br>SELECT = 01 <sub>B</sub>                                   |

|                                 |                                | 4.2                                                              | 4.4    | 4.6             | V    | ANAVDEL.VDEL_<br>SELECT = 10 <sub>B</sub>                                   |

# Table 24 Power-Up and Supply Monitoring Parameters (Operating Conditions apply)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Table 24 | Power-Up and Supply Monitoring Parameters (Operating Conditions |

|----------|-----------------------------------------------------------------|

|          | apply) (cont'd)                                                 |

| Parameter                                                   | Symbol                |      | Values |      | Unit | Note /<br>Test Condition                                                                         |

|-------------------------------------------------------------|-----------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------|

|                                                             |                       | Min. | Тур.   | Max. |      |                                                                                                  |

| $V_{\text{DDP}}$ brownout reset voltage                     | V <sub>DDPBO</sub> CC | 1.55 | 1.62   | 1.75 | V    | calibrated, before<br>user code starts<br>running                                                |

| $V_{\text{DDP}}$ voltage to<br>ensure defined pad<br>states | V <sub>DDPPA</sub> CC | -    | 1.0    | -    | V    |                                                                                                  |

| Start-up time from power-on reset                           | t <sub>SSW</sub> SR   | _    | 320    | -    | μs   | Time to the first<br>user code<br>instruction <sup>3)</sup>                                      |

| BMI program time                                            | t <sub>BMI</sub> SR   | -    | 8.25   | -    | ms   | Time taken from a<br>user-triggered<br>system reset after<br>BMI installation is<br>is requested |

1) A capacitor of at least 100 nF has to be added between VDDP and VSSP to fulfill the requirement as stated for this parameter.

2) Valid for a 100 nF buffer capacitor connected to supply pin where current from capacitor is forwarded only to the chip. A larger capacitor value has to be chosen if the power source sink a current.

3) This values does not include the ramp-up time. During startup firmware execution, MCLK is running at 32 MHz and the clocks to peripheral as specified in register CGATSTAT0 are gated.

Figure 19 Supply Threshold Parameters

## 3.3.5 SPD Timing Requirements

The optimum SPD decision time between  $0_B$  and  $1_B$  is 0.75 µs. With this value the system has maximum robustness against frequency deviations of the sampling clock on tool and on device side. However it is not always possible to exactly match this value with the given constraints for the sample clock. For instance for a oversampling rate of 4, the sample clock will be 8 MHz and in this case the closest possible effective decision time is 5.5 clock cycles (0.69 µs).

| Sample<br>Freq. | Sampling<br>Factor |        | Sample<br>Clocks 1 <sub>B</sub> |                                     | Remark                                                                                   |

|-----------------|--------------------|--------|---------------------------------|-------------------------------------|------------------------------------------------------------------------------------------|

| 8 MHz           | 4                  | 1 to 5 | 6 to 12                         | <b>Time<sup>1)</sup></b><br>0.69 μs | The other closest option<br>(0.81 µs) for the effective<br>decision time is less robust. |

## Table 28 Optimum Number of Sample Clocks for SPD

1) Nominal sample frequency period multiplied with  $0.5 + (max. number of 0_B sample clocks)$

For a balanced distribution of the timing robustness of SPD between tool and device, the timing requirements for the tool are:

- Frequency deviation of the sample clock is +/- 5%

- Effective decision time is between 0.69 µs and 0.75 µs (calculated with nominal sample frequency)

62

## 3.3.6.2 Inter-IC (IIC) Interface Timing

The following parameters are applicable for a USIC channel operated in IIC mode. *Note: Operating Conditions apply.*

| Table 31 | USIC IIC | Standard | Mode | Timing <sup>1)</sup> |

|----------|----------|----------|------|----------------------|

|----------|----------|----------|------|----------------------|

| Parameter                                              | Symbol                   |      | Values | 5    | Unit | Note /<br>Test Condition |

|--------------------------------------------------------|--------------------------|------|--------|------|------|--------------------------|

|                                                        |                          | Min. | Тур.   | Max. |      |                          |

| Fall time of both SDA and SCL                          | t <sub>1</sub><br>CC/SR  | -    | -      | 300  | ns   |                          |

| Rise time of both SDA and SCL                          | t <sub>2</sub><br>CC/SR  | -    | -      | 1000 | ns   |                          |

| Data hold time                                         | t <sub>3</sub><br>CC/SR  | 0    | -      | -    | μs   |                          |

| Data set-up time                                       | t <sub>4</sub><br>CC/SR  | 250  | -      | -    | ns   |                          |

| LOW period of SCL clock                                | t <sub>5</sub><br>CC/SR  | 4.7  | -      | -    | μs   |                          |

| HIGH period of SCL clock                               | t <sub>6</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                          |

| Hold time for (repeated)<br>START condition            | t <sub>7</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                          |

| Set-up time for repeated START condition               | t <sub>8</sub><br>CC/SR  | 4.7  | -      | -    | μs   |                          |

| Set-up time for STOP condition                         | t <sub>9</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                          |

| Bus free time between a<br>STOP and START<br>condition | t <sub>10</sub><br>CC/SR | 4.7  | -      | -    | μs   |                          |

| Capacitive load for each bus line                      | $C_{\rm b}{\rm SR}$      | -    | -      | 400  | pF   |                          |

Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximalely 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

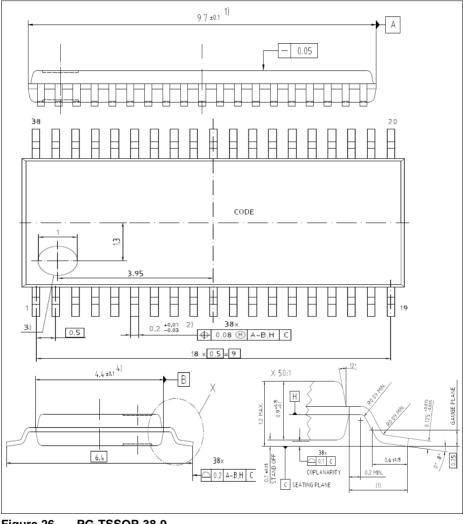

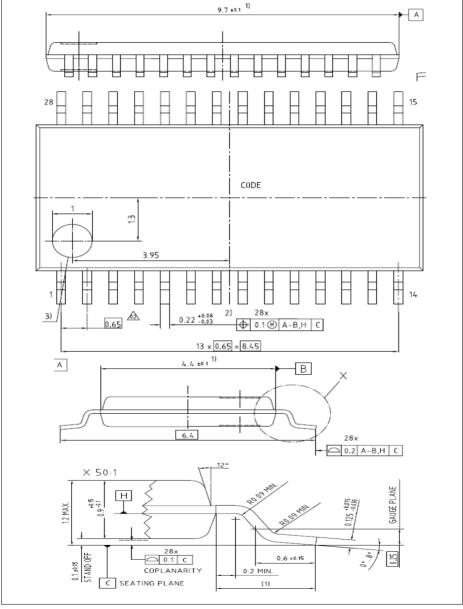

Package and Reliability

#### 4.2 **Package Outlines**

## XMC1300 AB-Step XMC1000 Family

## Package and Reliability

Figure 27 PG-TSSOP-28-16

## XMC1300 AB-Step XMC1000 Family

## Package and Reliability

## Figure 30 PG-VQFN-40-13

All dimensions in mm.