Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Core Size                  | 16-Bit                                                                          |

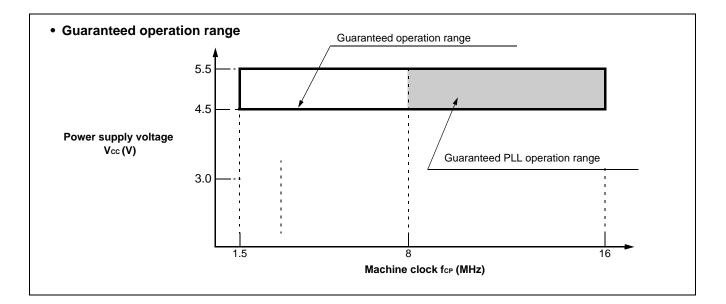

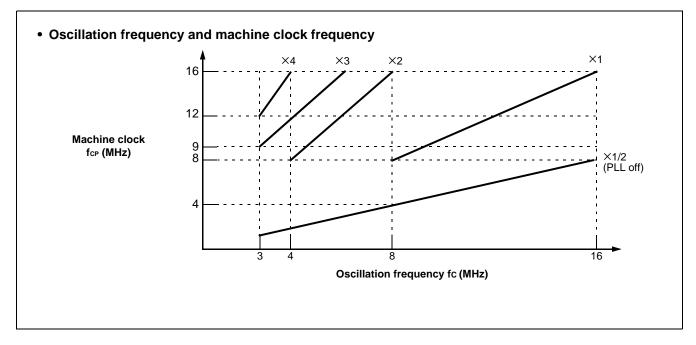

| Speed                      | 16MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                                    |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 78                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | Mask ROM                                                                        |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-BQFP                                                                        |

| Supplier Device Package    | 100-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90598gpf-g-142-bnd |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Pin Description

| Pin no.  | Pin name     | Circuit type | Function                                      |  |  |  |  |

|----------|--------------|--------------|-----------------------------------------------|--|--|--|--|

| 82       | X0           | ٨            |                                               |  |  |  |  |

| 83       | X1           | A            | Oscillator pin                                |  |  |  |  |

| 77       | RST          | В            | Reset input                                   |  |  |  |  |

| 52       | HST          | С            | Hardware standby input                        |  |  |  |  |

| 85 to 88 | P00 to P03   | G            | General purpose IO                            |  |  |  |  |

| 00 10 00 | IN0 to IN3   | 6            | Inputs for the Input Captures                 |  |  |  |  |

| 89 to 92 | P04 to P07   | G            | General purpose IO                            |  |  |  |  |

| 09 10 92 | OUT0 to OUT3 | 9            | Outputs for the Output Compares.              |  |  |  |  |

| 93 to 98 | P10 to P15   | D            | General purpose IO                            |  |  |  |  |

| 93 10 98 | PPG0 to PPG5 | d            | Outputs for the Programmable Pulse Generators |  |  |  |  |

| 99       | P16          | D            | General purpose IO                            |  |  |  |  |

| 33       | TIN1         | d            | TIN input for the 16-bit Reload Timer 1       |  |  |  |  |

| 100      | P17          | D            | General purpose IO                            |  |  |  |  |

| 100      | TOT1         | d            | TOT output for the 16-bit Reload Timer 1      |  |  |  |  |

| 1 to 8   | P20 to P27   | G            | General purpose IO                            |  |  |  |  |

| 9 to 10  | P30 to P31   | G            | General purpose IO                            |  |  |  |  |

| 12 to 16 | P32 to P36   | G            | General purpose IO                            |  |  |  |  |

| 17       | P37          | D            | General purpose IO                            |  |  |  |  |

| 18       | P40          | G            | General purpose IO                            |  |  |  |  |

| 10       | SOT0         | 0            | SOT output for UART 0                         |  |  |  |  |

| 19       | P41          | G            | General purpose IO                            |  |  |  |  |

| 19       | SCK0         | 0            | SCK input/output for UART 0                   |  |  |  |  |

| 20       | P42          | G            | General purpose IO                            |  |  |  |  |

| 20       | SIN0         | 0            | SIN input for UART 0                          |  |  |  |  |

| 21       | P43          | G            | General purpose IO                            |  |  |  |  |

| 21       | SIN1         | 0            | SIN input for UART 1                          |  |  |  |  |

| 22       | P44          | G            | General purpose IO                            |  |  |  |  |

| 22       | SCK1         | 0            | SCK input/output for UART 1                   |  |  |  |  |

| 24       | P45          | G            | General purpose IO                            |  |  |  |  |

| 24       | SOT1         | 6            | SOT output for UART 1                         |  |  |  |  |

| 25       | P46          | G            | General purpose IO                            |  |  |  |  |

| 20       | SOT2         | 5            | SOT output for the Serial IO                  |  |  |  |  |

| 26       | P47          | G            | General purpose IO                            |  |  |  |  |

| 20       | SCK2         | 5            | SCK input/output for the Serial IO            |  |  |  |  |

| Pin no.  | Pin name                             | Circuit type | Function                                            |

|----------|--------------------------------------|--------------|-----------------------------------------------------|

| 20       | P50                                  | D            | General purpose IO                                  |

| 28       | SIN2                                 | D            | SIN Input for the Serial IO                         |

| 29 to 32 | P51 to P54                           | D            | General purpose IO                                  |

| 291032   | INT4 to INT7                         | D            | External interrupt input for INT4 to INT7           |

| 33       | P55                                  | D            | General purpose IO                                  |

|          | ADTG                                 | ם            | Input for the external trigger of the A/D Converter |

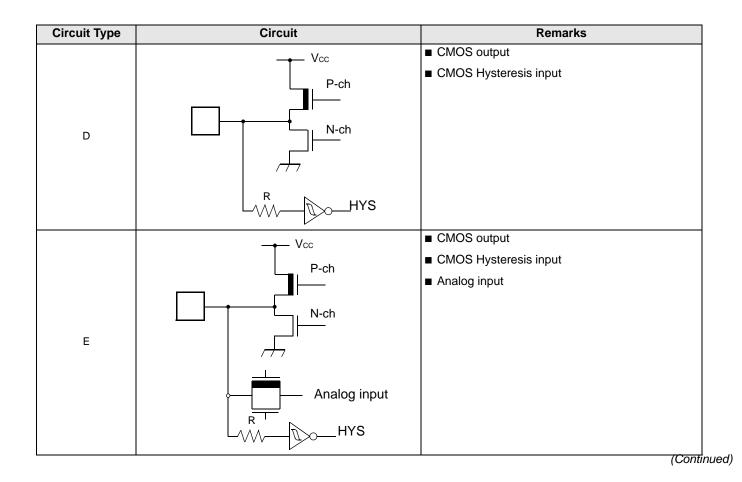

| 38 to 41 | P60 to P63                           | E            | General purpose IO                                  |

| 30 10 41 | AN0 to AN3                           | L            | Inputs for the A/D Converter                        |

| 43 to 46 | P64 to P67                           | E            | General purpose IO                                  |

| 43 10 40 | AN4 to AN7                           | L            | Inputs for the A/D Converter                        |

| 47       | P56                                  | D            | General purpose IO                                  |

| 47       | TIN0                                 | ם            | TIN input for the 16-bit Reload Timer 0             |

| 48       | P57                                  | D            | General purpose IO                                  |

| 40       | ΤΟΤΟ                                 | D            | TOT output for the 16-bit Reload Timer 0            |

|          | P70 to P73                           |              | General purpose IO                                  |

| 54 to 57 | PWM1P0<br>PWM1M0<br>PWM2P0<br>PWM2M0 | F            | Output for Stepper Motor Controller channel 0       |

|          | P74 to P77                           |              | General purpose IO                                  |

| 59 to 62 | PWM1P1<br>PWM1M1<br>PWM2P1<br>PWM2M1 | F            | Output for Stepper Motor Controller channel 1       |

|          | P80 to P83                           |              | General purpose IO                                  |

| 64 to 67 | PWM1P2<br>PWM1M2<br>PWM2P2<br>PWM2M2 | F            | Output for Stepper Motor Controller channel 2       |

|          | P84 to P87                           |              | General purpose IO                                  |

| 69 to 72 | PWM1P3<br>PWM1M3<br>PWM2P3<br>PWM2M3 | F            | Output for Stepper Motor Controller channel 3       |

| 74       | P90                                  | 5            | General purpose IO                                  |

| 74       | ТХ                                   | D            | TX output for CAN Interface                         |

| 75       | P91                                  | 6            | General purpose IO                                  |

| 75       | RX                                   | D            | RX input for CAN Interface                          |

# 5. Handling Devices

#### (1) Make Sure that the Voltage not Exceed the Maximum Rating (to Avoid a Latch-up).

In CMOS ICs, a latch-up phenomenon is caused when an voltage exceeding Vcc or an voltage below Vss is applied to input or output pins or a voltage exceeding the rating is applied across Vcc and Vss.

When a latch-up is caused, the power supply current may be dramatically increased causing resultant thermal break-down of devices. To avoid the latch-up, make sure that the voltage not exceed the maximum rating.

In turning on/turning off the analog power supply, make sure the analog power voltage (AVcc, AVRH, DVcc) and analog input voltages not exceed the digital voltage (Vcc).

#### (2) Treatment of Unused Pins

Unused input pins left open may cause abnormal operation, or latch-up leading to permanent damage. Unused input pins should be pulled up or pulled down through at least 2 k $\Omega$  resistance.

Unused input/output pins may be left open in output state, but if such pins are in input state they should be handled in the same way as input pins.

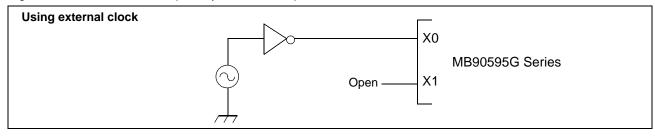

### (3) Using external clock

In using the external clock, drive X0 pin only and leave X1 pin unconnected.

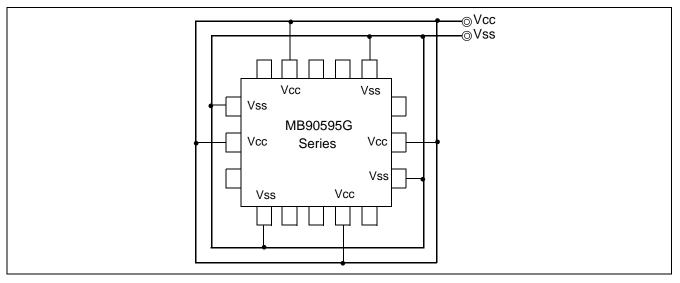

#### (4) Power supply pins (Vcc/Vss)

In products with multiple V<sub>cc</sub> or V<sub>ss</sub> pins, pins with the same potential are internally connected in the device to avoid abnormal operations including latch-up. However, you must connect the pins to an external power and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total current rating (See the figure below.)

Make sure to connect  $V_{cc}$  and  $V_{ss}$  pins via lowest impedance to power lines.

It is recommended to provide a bypass capacitor of around 0.1  $\mu$ F between V<sub>cc</sub> and V<sub>ss</sub> pins near the device.

## (5) Pull-up/down resistors

The MB90595G Series does not support internal pull-up/down resistors. Use external components where needed.

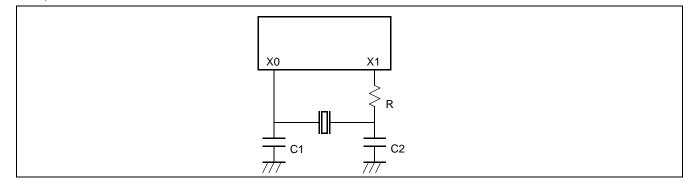

#### (6) Crystal Oscillator Circuit

Noises around X0 or X1 pins may cause abnormal operations. Make sure to provide bypass capacitors via shortest distance from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure that lines of oscillation circuit not cross the lines of other circuits.

A printed circuit board artwork surrounding the X0 and X1 pins with ground area for stabilizing the operation is highly recommended.

#### (7) Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

Make sure to turn on the A/D converter power supply (AVcc, AVRH, AVRL) and analog inputs (AN0 to AN7) after turning-on the digital power supply (Vcc).

Turn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure that the voltage does not exceed AVRH or AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

### (8) Connection of Unused Pins of A/D Converter

Connect unused pins of A/D converter to AVcc = Vcc, AVss = AVRH = DVcc = Vss.

#### (9) N.C. Pin

The N.C. (internally connected) pin must be opened for use.

#### (10) Notes on Energization

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at

50 µs or more (0.2 V to 2.7 V).

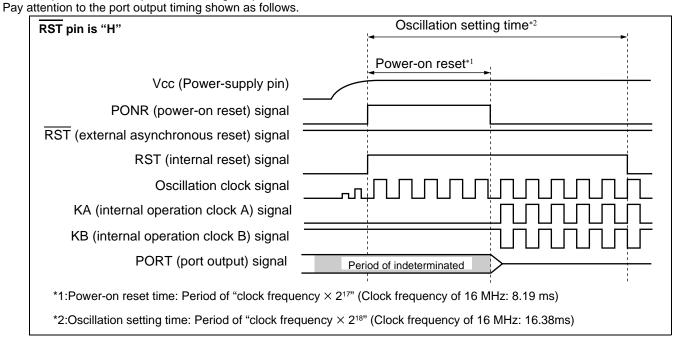

#### (11) Indeterminate outputs from ports 0 and 1 (MB90V595G only)

During oscillation setting time of step-down circuit (during a power-on reset) after the power is turned on, the outputs from ports 0 and 1 become following state.

■ If RST pin is "H", the outputs become indeterminate.

If  $\overline{RST}$  pin is "L", the outputs become high-impedance.

# 8. I/O Map

| Address     | Register                            | Abbreviation | Access | Peripheral  | Initial value |

|-------------|-------------------------------------|--------------|--------|-------------|---------------|

| 00н         | Port 0 Data Register                | PDR0         | R/W    | Port 0      | XXXXXXXXB     |

| 01н         | Port 1 Data Register                | PDR1         | R/W    | Port 1      | XXXXXXXXB     |

| 02н         | Port 2 Data Register                | PDR2         | R/W    | Port 2      | XXXXXXXXB     |

| 03н         | Port 3 Data Register                | PDR3         | R/W    | Port 3      | XXXXXXXXB     |

| 04н         | Port 4 Data Register                | PDR4         | R/W    | Port 4      | XXXXXXXXB     |

| 05н         | Port 5 Data Register                | PDR5         | R/W    | Port 5      | XXXXXXXXB     |

| 06н         | Port 6 Data Register                | PDR6         | R/W    | Port 6      | XXXXXXXXB     |

| 07н         | Port 7 Data Register                | PDR7         | R/W    | Port 7      | XXXXXXXXB     |

| 08н         | Port 8 Data Register                | PDR8         | R/W    | Port 8      | XXXXXXXXB     |

| 09н         | Port 9 Data Register                | PDR9         | R/W    | Port 9      | XXXXXXB       |

| 0Ан to 0Fн  |                                     | Reserv       | ed     |             |               |

| 10н         | Port 0 Direction Register           | DDR0         | R/W    | Port 0      | 00000000      |

| 11н         | Port 1 Direction Register           | DDR1         | R/W    | Port 1      | 00000000      |

| 12н         | Port 2 Direction Register           | DDR2         | R/W    | Port 2      | 00000000      |

| 13н         | Port 3 Direction Register           | DDR3         | R/W    | Port 3      | 00000000      |

| 14н         | Port 4 Direction Register           | DDR4         | R/W    | Port 4      | 00000000      |

| 15н         | Port 5 Direction Register           | DDR5         | R/W    | Port 5      | 00000000      |

| 16н         | Port 6 Direction Register           | DDR6         | R/W    | Port 6      | 00000000      |

| <b>17</b> н | Port 7 Direction Register           | DDR7         | R/W    | Port 7      | 00000000      |

| <b>18</b> н | Port 8 Direction Register           | DDR8         | R/W    | Port 8      | 00000000      |

| 19н         | Port 9 Direction Register           | DDR9         | R/W    | Port 9      | 000000в       |

| 1Ан         |                                     | Reserv       | ed     |             | •             |

| 1Bн         | Analog Input Enable Register        | ADER         | R/W    | Port 6, A/D | 1111111       |

| 1Cн to 1Fн  |                                     | Reserv       | ed     |             | ·             |

| 20н         | Serial Mode Control Register 0      | UMC0         | R/W    |             | 00000100в     |

| 21н         | Serial status Register 0            | USR0         | R/W    |             | 0001000в      |

| 22н         | Serial Input/Output Data Register 0 | UIDR0/UODR0  | R/W    | UART0       | XXXXXXXXB     |

| 23н         | Rate and Data Register 0            | URD0         | R/W    |             | 0000000 Хв    |

| 24н         | Serial Mode Register 1              | SMR1         | R/W    |             | 00000000      |

| 25н         | Serial Control Register 1           | SCR1         | R/W    |             | 00000100в     |

| 26н         | Serial Input/Output Data Register 1 | SIDR1/SODR1  | R/W    | UART1       | XXXXXXXXB     |

| 27н         | Serial Status Register 1            | SSR1         | R/W    |             | 00001_00в     |

| 28н         | UART1 Prescaler Control Register    | U1CDCR       | R/W    | 1           | 01111в        |

| Address      | Register                                  | Abbreviation | Access | Peripheral                     | Initial value                            |

|--------------|-------------------------------------------|--------------|--------|--------------------------------|------------------------------------------|

| 4Сн          | PPGA Operation Mode Control Register      | PPGCA        | R/W    | 16-bit                         | 0_000_1B                                 |

| 4Dн          | PPGB Operation Mode Control Register      | PPGCB        | R/W    | Programmable Pulse             | 0_00001B                                 |

| 4Eн          | PPGA, B Output Pin Control Register       | PPGAB        | R/W    | Generator A/B                  | 0 0 0 0 0 0 0B                           |

| 4Fн          |                                           | Reserved     | •      |                                |                                          |

| 50н          | Timer Control Status Register 0           | TMCSR0       | R/W    |                                | 00000000 <sub>B</sub>                    |

| <b>51</b> н  | Timer Control Status Register 0           | TMCSR0       | R/W    | 16-bit                         | 0 0 0 0 <sub>B</sub>                     |

| <b>52</b> н  | Timer 0/Reload Register 0                 | TMR0/TMRLR0  | R/W    | Reload Timer 0                 | XXXXXXXX <sub>B</sub>                    |

| 53н          | Timer 0/Reload Register 0                 | TMR0/TMRLR0  | R/W    |                                | XXXXXXXX <sub>B</sub>                    |

| <b>54</b> H  | Timer Control Status Register 1           | TMCSR1       | R/W    |                                | $0\; 0\; 0\; 0\; 0\; 0\; 0\; 0_{\rm B}$  |

| <b>55</b> H  | Timer Control Status Register 1           | TMCSR1       | R/W    | 16-bit                         | 0 0 0 0 <sub>B</sub>                     |

| <b>56</b> H  | Timer Register 1/Reload Register 1        | TMR1/TMRLR1  | R/W    | Reload Timer 1                 | XXXXXXXXB                                |

| <b>57</b> н  | Timer Register 1/Reload Register 1        | TMR1/TMRLR1  | R/W    |                                | XXXXXXXX <sub>B</sub>                    |

| <b>58</b> H  | Output Compare Control Status Register 0  | OCS0         | R/W    | Output                         | $0\; 0\; 0\; 0\; 0\; \_\; 0\; 0_{\rm B}$ |

| 59н          | Output Compare Control Status Register 1  | OCS1         | R/W    | Compare 0/1                    | 00000 <sub>B</sub>                       |

| 5Ан          | Output Compare Control Status Register 2  | OCS2         | R/W    | Output                         | 0 0 0 0 0 0 <sub>B</sub>                 |

| <b>5В</b> н  | Output Compare Control Status Register 3  | OCS3         | R/W    | Compare 2/3                    | 00000B                                   |

| 5Сн          | Input Capture Control Status Register 0/1 | ICS01        | R/W    | Input Capture 0/1              | 00000000                                 |

| 5Dн          | Input Capture Control Status Register 2/3 | ICS23        | R/W    | Input Capture 2/3              | 0 0 0 0 0 0 0 0 0 <sub>B</sub>           |

| 5 <b>Е</b> н | PWM Control Register 0                    | PWC0         | R/W    | Stepping Motor<br>Controller 0 | 0 0 0 0 0 0 <sub>B</sub>                 |

| 5FH          |                                           | Reserved     |        |                                |                                          |

| 60н          | PWM Control Register 1                    | PWC1         | R/W    | Stepping Motor<br>Controller 1 | $0\ 0\ 0\ 0\ 0\ 0\ _{}0_{B}$             |

| 61н          |                                           | Reserved     |        |                                |                                          |

| 62н          | PWM Control Register 2                    | PWC2         | R/W    | Stepping Motor<br>Controller 2 | $0\ 0\ 0\ 0\ 0\ 0\ _{}0_{B}$             |

| 63н          |                                           | Reserved     |        |                                |                                          |

| 64н          | PWM Control Register 3                    | PWC3         | R/W    | Stepping Motor<br>Controller 3 | 0 0 0 0 0 0 <sub>B</sub>                 |

| <b>65</b> H  |                                           | Reserved     |        |                                |                                          |

| 66н          | Timer Data Register (low-order)           | TCDT         | R/W    |                                | 0 0 0 0 0 0 0 0 0 <sub>B</sub>           |

| 67н          | Timer Data Register (high-order)          | TCDT         | R/W    | 16-bit Free-run Timer          | 00000000                                 |

| <b>68</b> H  | Timer Control Status Register             | TCCS         | R/W    |                                | 0 0 0 0 0 0 0 0 0 <sub>B</sub>           |

| 69н to 6Ен   |                                           | Reserved     |        |                                | (Conti                                   |

\_\_\_\_

| Address      | Register                                                                                 | Abbreviation         | Access       | Peripheral                          | Initial value                  |

|--------------|------------------------------------------------------------------------------------------|----------------------|--------------|-------------------------------------|--------------------------------|

| 6 <b>F</b> н | ROM Mirror Function Selection Register                                                   | ROMM                 | R/W          | ROM Mirror                          | 1в                             |

| <b>70</b> н  | PWM1 Compare Register 0                                                                  | PWC10                | R/W          |                                     | XXXXXXXXAB                     |

| 71н          | PWM2 Compare Register 0                                                                  | PWC20                | R/W          | Stepping Motor                      | XXXXXXXXAB                     |

| 72н          | PWM1 Select Register 0                                                                   | PWS10                | R/W          | Controller 0                        | 000000B                        |

| 73н          | PWM2 Select Register 0                                                                   | PWS20                | R/W          |                                     | _ 0 0 0 0 0 0 0 0 <sub>B</sub> |

| <b>74</b> H  | PWM1 Compare Register 1                                                                  | PWC11                | R/W          |                                     | XXXXXXXXAB                     |

| <b>75</b> н  | PWM2 Compare Register 1                                                                  | PWC21                | R/W          | Stepping Motor                      | XXXXXXXXAB                     |

| 76н          | PWM1 Select Register 1                                                                   | PWS11                | R/W          | Controller 1                        | 000000B                        |

| 77н          | PWM2 Select Register 1                                                                   | PWS21                | R/W          |                                     | _ 0 0 0 0 0 0 0 0 <sub>B</sub> |

| <b>78</b> H  | PWM1 Compare Register 2                                                                  | PWC12                | R/W          |                                     | XXXXXXXX                       |

| 79н          | PWM2 Compare Register 2                                                                  | PWC22                | R/W          | Stepping Motor                      | XXXXXXXX                       |

| 7Ан          | PWM1 Select Register 2                                                                   | PWS12                | R/W          | Controller 2                        | 000000B                        |

| 7Вн          | PWM2 Select Register 2                                                                   | PWS22                | R/W          |                                     | _ 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 7Сн          | PWM1 Compare Register 3                                                                  | PWC13                | R/W          |                                     | XXXXXXXX <sub>B</sub>          |

| 7Dн          | PWM2 Compare Register 3                                                                  | PWC23                | R/W          | Stepping Motor                      | XXXXXXXX <sub>B</sub>          |

| 7Ен          | PWM1 Select Register 3                                                                   | PWS13                | R/W          | Controller 3                        | 000000B                        |

| <b>7</b> Fн  | PWM2 Select Register 3                                                                   | PWS23                | R/W          |                                     | _ 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 80н to 8Fн   | CAN Controll                                                                             | er. Refer to section | about CAN    | Controller                          |                                |

| 90н to 9Dн   |                                                                                          | Reserved             |              |                                     |                                |

| 9Eн          | Program Address Detection Control Status<br>Register                                     | PACSR                | R/W          | Address Match<br>Detection Function | 0 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 9 <b>F</b> н | Delayed Interrupt/Request Register                                                       | DIRR                 | R/W          | Delayed Interrupt                   | 0                              |

| АОн          | Low-Power Mode Control Register                                                          | LPMCR                | R/W          | Low Power<br>Controller             | 00011000в                      |

| А1н          | Clock Selection Register                                                                 | CKSCR                | R/W          | Low Power<br>Controller             | 1111100в                       |

| A2H to A7H   |                                                                                          | Reserved             |              |                                     |                                |

| А8н          | Watchdog Timer Control Register                                                          | WDTC                 | R/W          | Watchdog Timer                      | ХХХХХ 1 1 1в                   |

| А9н          | Time Base Timer Control Register                                                         | TBTC                 | R/W          | Time Base Timer                     | 100100в                        |

| AAH to ADH   |                                                                                          | Reserved             |              |                                     | •                              |

| АЕн          | Flash Memory Control Status Register<br>(MB90F598G only. FMCS R/W<br>Otherwise reserved) |                      | Flash Memory | 0 0 0 X 0 0 0 <sub>B</sub>          |                                |

| AFн          |                                                                                          | Reserved             |              |                                     |                                |

# 9.3 List of Message Buffers (DLC Registers and Data Registers)

| Address                  | Register                  | Abbreviation | Access  | Initial Value               |  |

|--------------------------|---------------------------|--------------|---------|-----------------------------|--|

| 001A60н                  |                           | DI ODO       | D 444   | ~~~~~                       |  |

| <b>001А61</b> н          | DLC register 0            | DLCR0        | R/W     | XXXXB                       |  |

| 001A62н                  |                           |              | DAA     |                             |  |

| 001A63н                  | DLC register 1            | DLCR1        | R/W     | ХХХХв                       |  |

| 001A64н                  |                           |              | DAA     | VVV-                        |  |

| 001A65н                  | DLC register 2            | DLCR2        | R/W     | ХХХХв                       |  |

| 001A66н                  | - DLC register 3          | DLCR3        | R/W     | ХХХХв                       |  |

| <b>001А67</b> н          | DLC register 3            | DLCR3        | R/VV    | XXXAB                       |  |

| 001A68н                  | DLC register 4            |              | DAM     | VVV-                        |  |

| 001A69н                  | DLC register 4            | DLCR4        | R/W     | ХХХХв                       |  |

| 001А6Ан                  | DLC register 5            | DLCR5        | R/W     | ХХХХв                       |  |

| 001A6Bн                  | DLC register 5            | DLCRS        | r./vv   |                             |  |

| 001A6Cн                  | DLC register 6            | DLCR6        | R/W     |                             |  |

| 001A6DH                  | DLC register o            | DLCRO        | r./vv   | ХХХХв                       |  |

| 001A6Eн                  | DLC register 7            | DLCR7        | R/W     | XXXXB                       |  |

| 001A6Fн                  |                           | DLCR7        | r./vv   |                             |  |

| <b>001А70</b> н          | DLC register 8            | DLCR8        | R/W     | XXXX                        |  |

| <b>001A71</b> н          | DLC register o            | DECKO        |         | ^                           |  |

| <b>001А72</b> н          | DLC register 9            | DLCR9        | R/W     | XXXXB                       |  |

| <b>001А73</b> н          | DLC register 9            | DLCK9        | FN/ V V |                             |  |

| 001A74н                  | DLC register 10           | DLCR10       | R/W     | XXXXB                       |  |

| 001A75н                  |                           | DECKTO       | 10/00   |                             |  |

| 001A76н                  | DLC register 11           | DLCR11       | R/W     | XXXXB                       |  |

| <b>001А77</b> н          |                           | DECKT        | 10/00   |                             |  |

| 001A78н                  | DLC register 12           | DLCR12       | R/W     | XXXXB                       |  |

| 001A79н                  |                           | DEORTZ       | 10,00   |                             |  |

| 001А7Ан                  | DLC register 13           | DLCR13       | R/W     | XXXXB                       |  |

| 001A7Bн                  |                           | DEORIG       |         |                             |  |

| 001A7Cн                  | DLC register 14           | DLCR14       | R/W     | ХХХХв                       |  |

| 001A7DH                  |                           | DLOR 14      |         |                             |  |

| 001A7Eн                  | DLC register 15           | DLCR15       | R/W     | XXXXB                       |  |

| 001A7Fн                  |                           | DEORIG       |         | /////6                      |  |

| 001А80н<br>to<br>001А87н | Data register 0 (8 bytes) | DTR0         | R/W     | XXXXXXXXB<br>to<br>XXXXXXXB |  |

(Continued)

| Address                  | Register                   | Abbreviation | Access | Initial Value                |

|--------------------------|----------------------------|--------------|--------|------------------------------|

| 001А88н<br>to<br>001А8Fн | Data register 1 (8 bytes)  | DTR1         | R/W    | XXXXXXXxB<br>to<br>XXXXXXXB  |

| 001А90н<br>to<br>001А97н | Data register 2 (8 bytes)  | DTR2         | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 001А98н<br>to<br>001А9Fн | Data register 3 (8 bytes)  | DTR3         | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 001AA0н<br>to<br>001AA7н | Data register 4 (8 bytes)  | DTR4         | R/W    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 001AA8н<br>to<br>001AAFн | Data register 5 (8 bytes)  | DTR5         | R/W    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 001АВ0н<br>to<br>001АВ7н | Data register 6 (8 bytes)  | DTR6         | R/W    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 001AB8н<br>to<br>001ABFн | Data register 7 (8 bytes)  | DTR7         | R/W    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 001AC0н<br>to<br>001AC7н | Data register 8 (8 bytes)  | DTR8         | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 001AC8н<br>to<br>001ACFн | Data register 9 (8 bytes)  | DTR9         | R/W    | XXXXXXXB<br>to<br>XXXXXXXB   |

| 001AD0н<br>to<br>001AD7н | Data register 10 (8 bytes) | DTR10        | R/W    | XXXXXXXB<br>to<br>XXXXXXXB   |

| 001AD8н<br>to<br>001ADFн | Data register 11 (8 bytes) | DTR11        | R/W    | XXXXXXXB<br>to<br>XXXXXXXB   |

| 001АЕ0н<br>to<br>001АЕ7н | Data register 12 (8 bytes) | DTR12        | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 001AE8⊦<br>to<br>001AEF⊦ | Data register 13 (8 bytes) | DTR13        | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 001AF0н<br>to<br>001AF7н | Data register 14 (8 bytes) | DTR14        | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 001AF8н<br>to<br>001AFFн | Data register 15 (8 bytes) | DTR15        | R/W    | XXXXXXXB<br>to<br>XXXXXXXB   |

\_\_\_\_\_

Notes:

- For a peripheral module with two interrupt for a single interrupt number, both interrupt request flags are cleared by the El<sup>2</sup>OS interrupt clear signal.

- At the end of EI<sup>2</sup>OS, the EI<sup>2</sup>OS clear signal will be asserted for all the interrupt flags assigned to the same interrupt number. If one interrupt flag starts the EI<sup>2</sup>OS and in the meantime another interrupt flag is set by hardware event, the later event is lost because the flag is cleared by the EI<sup>2</sup>OS clear signal caused by the first event. So it is recommended not to use the EI<sup>2</sup>OS for this interrupt number.

- If EI<sup>2</sup>OS is enabled, EI<sup>2</sup>OS is initiated when one of the two interrupt signals in the same interrupt control register (ICR) is asserted. This means that different interrupt sources share the same EI<sup>2</sup>OS Descriptor which should be unique for each interrupt source. For this reason, when one interrupt source uses the EI<sup>2</sup>OS, the other interrupt should be disabled.

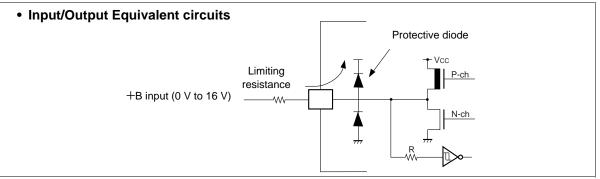

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller current is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on result.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits :

Note: : Average output current = operating current × operating efficiency

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

# Example of Oscillation circuit

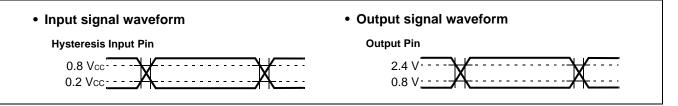

AC characteristics are set to the measured reference voltage values below.

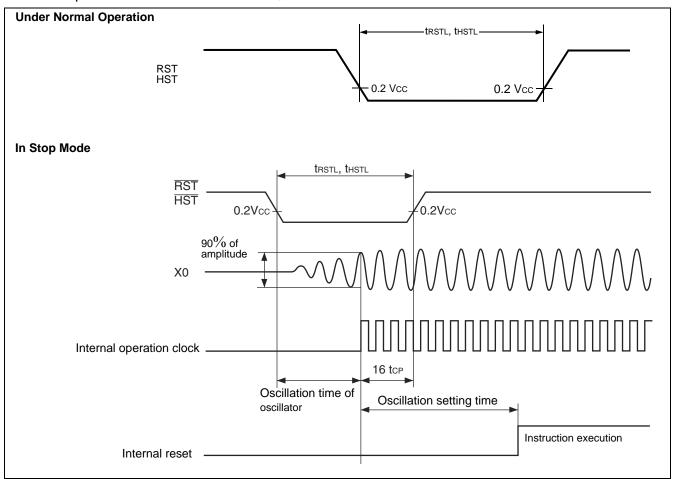

## 11.4.2 Reset and Hardware Standby Input

| $(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ Vss} = \text{AVss} = 0.0 \text{ V}, \text{ T}_{\text{A}} = -40 ^{\circ}\text{C} \text{ to}$ |               |            |                                                                          |     |      |                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|--------------------------------------------------------------------------|-----|------|------------------------|--|--|--|

| Parameter                                                                                                                             | Symbol        | Pin name   | Value                                                                    |     | Unit | Remarks                |  |  |  |

| Falametei                                                                                                                             | Symbol        | Finitianie | Min                                                                      | Max | Unit | Remarks                |  |  |  |

| Reset input time                                                                                                                      | <b>t</b> RSTL | RST        | 16 tcp*1                                                                 | —   | ns   | Under normal operation |  |  |  |

|                                                                                                                                       |               |            | Oscillation time of oscillator <sup>*2</sup> + 16 $t_{CP}$ <sup>*1</sup> | —   | ms   | In stop mode           |  |  |  |

|                                                                                                                                       |               |            | 16 tcp*1                                                                 | —   | ns   | Under normal operation |  |  |  |

| Hardware standby input time                                                                                                           | tнsт∟         | HST        | Oscillation time of oscillator <sup>*2</sup> + 16 $t_{CP}^{*1}$          | —   | ms   | In stop mode           |  |  |  |

\*1: "tcp" represents one cycle time of the machine clock.

No reset can fully initialize the Flash Memory if it is performing the automatic algorithm.

\*2: Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

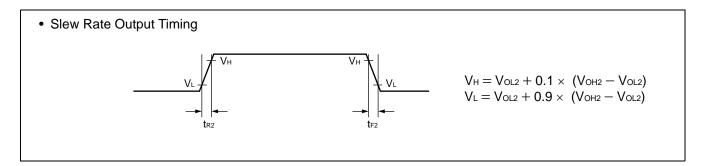

| 11.4.6 Slew Rate High Current Outputs (MB90598G, MB90F598G only)<br>( $V_{CC} = 5.0 V \pm 10 \%$ , $V_{SS} = AV_{SS} = 0.0 V$ , $T_A = -40 \degree C$ to $+85 \degree C$ ) |            |                                     |           |                      |    |      |         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------|-----------|----------------------|----|------|---------|--|--|--|

| Parameter                                                                                                                                                                  | Symbol     | Pin name                            | Condition | Value<br>Min Typ Max |    | Unit | Remarks |  |  |  |

| Output Rise/Fall time                                                                                                                                                      | tR2<br>tF2 | Port P70 to P77,<br>Port P80 to P87 | _         | 15                   | 40 | 150  | ns      |  |  |  |

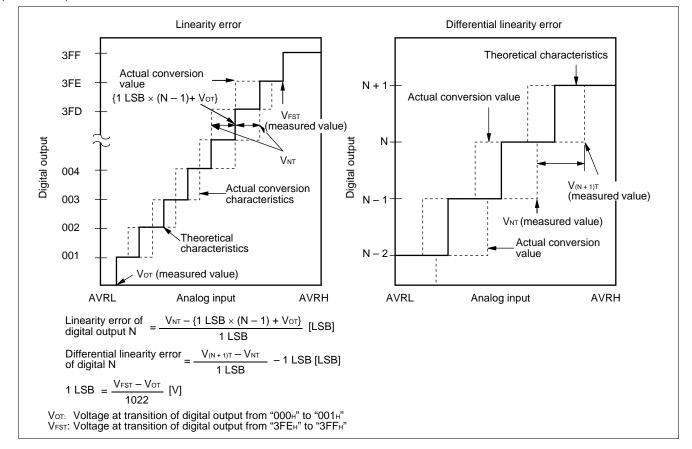

# 11.5 A/D Converter

$(V_{CC} = AV_{CC} = 5.0 \text{ V} \pm 10\%, \text{ V}_{SS} = AV_{SS} = 0.0 \text{ V}, 3.0 \text{ V} \le AV_{RH} - AV_{RL}, \text{ T}_{A} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C})$

| Parameter                     | Sym- | Pin name   |                   | Value             | Unit              | Remarks |         |

|-------------------------------|------|------------|-------------------|-------------------|-------------------|---------|---------|

| Faiameter                     | bol  | Fin hame   | Min               | Тур               | Max               | Unit    | Remarks |

| Resolution                    | —    | —          | —                 |                   | 10                | bit     |         |

| Conversion error              | —    | —          | —                 | _                 | ±5.0              | LSB     |         |

| Nonlinearity error            | _    | —          | —                 | _                 | ±2.5              | LSB     |         |

| Differential linearity error  | —    | —          | —                 | _                 | ±1.9              | LSB     |         |

| Zero transition voltage       | Vот  | AN0 to AN7 | AVRL —<br>3.5 LSB | AVRL +<br>0.5 LSB | AVRL +<br>4.5 LSB | V       |         |

| Full scale transition voltage | Vfst | AN0 to AN7 | AVRH —<br>6.5 LSB | AVRH —<br>1.5 LSB | AVRH +<br>1.5 LSB | V       |         |

| Conversion time               | _    | —          | _                 | 352tcp            | —                 | ns      |         |

| Sampling time                 | —    | —          | —                 | 64tcp             | —                 | ns      |         |

| Analog port input current     | Iain | AN0 to AN7 | -10               | —                 | 10                | μA      |         |

| Analog input voltage range    | Vain | AN0 to AN7 | AVRL              | _                 | AVRH              | V       |         |

| Parameter                     | Sym- | Pin name   | Value      |     |            |      | Remarks                 |

|-------------------------------|------|------------|------------|-----|------------|------|-------------------------|

| Faiametei                     | bol  | Pin name   | Min        | Тур | Max        | Unit | Reillarks               |

| Reference voltage range       | —    | AVRH       | AVRL + 3.0 | —   | AVcc       | V    |                         |

| Reference voltage range       | —    | AVRL       | 0          | —   | AVRH - 3.0 | V    |                         |

| Power supply current          | la   | AVcc       | _          | 5   | —          | mA   |                         |

|                               | Іан  | AVcc       | _          |     | 5          | μA   | *                       |

|                               | lr   | AVRH       | _          | 400 | 600        | μΑ   | MB90V595G,<br>MB90F598G |

| Reference voltage current     |      |            | _          | 140 | 600        | μA   | MB90598G                |

|                               | Irh  | AVRH       |            |     | 5          | μA   | *                       |

| Offset between input channels | _    | AN0 to AN7 | _          | _   | 4          | LSB  |                         |

\*: When not operating A/D converter, this is the current ( $V_{CC} = AV_{CC} = AVRH = 5.0$  V) when the CPU is stopped.

# (Continued)

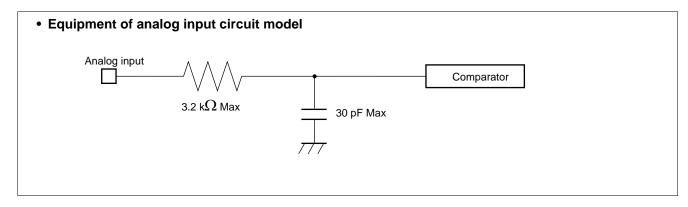

## 11.7 Notes on Using A/D Converter

Select the output impedance value for the external circuit of analog input according to the following conditions,:

- Output impedance values of the external circuit of 15 k $\Omega$  or lower are recommended.

- When capacitors are connected to external pins, the capacitance of several thousand times the internal capacitor value is recommended to minimized the effect of voltage distribution between the external capacitor and internal capacitor.

When the output impedance of the external circuit is too high, the sampling period for analog voltages may not be sufficient (sampling period =  $4.00 \ \mu s$  @machine clock of 16 MHz).

## Error

The smaller the |AVRH - AVRL|, the greater the error would become relatively.

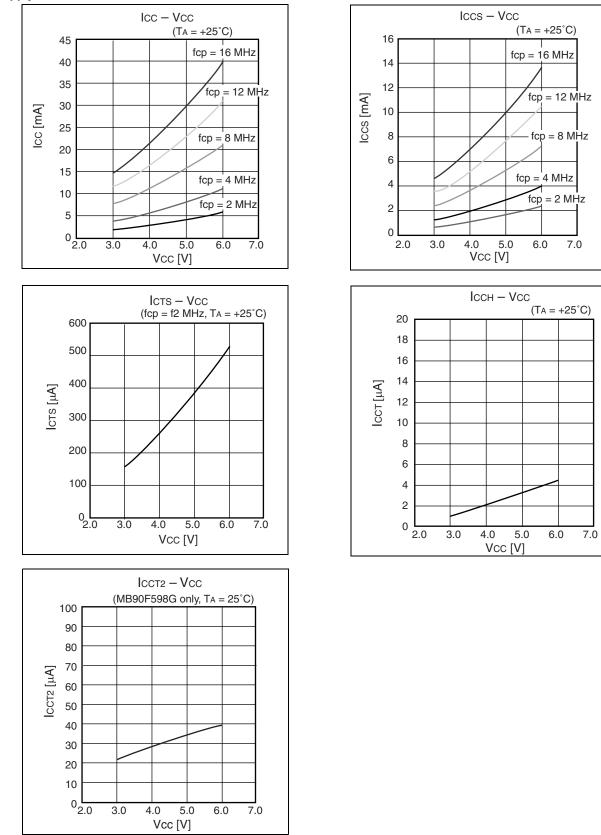

# **12. Example Characteristics**

# **Supply Current**