Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                                    |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 78                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | Mask ROM                                                                        |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-BQFP                                                                        |

| Supplier Device Package    | 100-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90598gpf-g-146-bnd |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Product Lineup

|                                                                                                                                                                                                                                                                                                                                                                                                      | Features                  | MB90598G                                                                                                                                                                                                                                                                                                                               | MB90F598G                                                                                    | MB90V595G              |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|--|--|--|

| Classific                                                                                                                                                                                                                                                                                                                                                                                            | ation                     | Mask ROM product                                                                                                                                                                                                                                                                                                                       | Flash ROM product                                                                            | Evaluation product     |  |  |  |

| ROM siz                                                                                                                                                                                                                                                                                                                                                                                              | e                         | 128 Kbytes                                                                                                                                                                                                                                                                                                                             | 128 Kbytes<br>Boot block<br>Hard-wired reset vector                                          | None                   |  |  |  |

| RAM size                                                                                                                                                                                                                                                                                                                                                                                             | e                         | 4 Kbytes                                                                                                                                                                                                                                                                                                                               | 4 Kbytes                                                                                     | 6 Kbytes               |  |  |  |

| Emulator                                                                                                                                                                                                                                                                                                                                                                                             | r-specific power supply   | -                                                                                                                                                                                                                                                                                                                                      |                                                                                              | None                   |  |  |  |

| CPU fun                                                                                                                                                                                                                                                                                                                                                                                              | ctions                    | The number of instructions: 351<br>Instruction bit length: 8 bits, 16 bits<br>Instruction length: 1 byte to 7 bytes<br>Data bit length: 1 bit, 8 bits, 16 bits<br>Minimum execution time: 62.5 ns (at machine clock frequency of 16 MHz)<br>Interrupt processing time: 1.5 µs<br>(at machine clock frequency of 16 MHz, minimum value) |                                                                                              |                        |  |  |  |

| UART0                                                                                                                                                                                                                                                                                                                                                                                                |                           | Clock synchronized transmission (500 K/1 M/2 Mbps)<br>Clock asynchronized transmission (4808/5208/9615/10417/19230/38460/62500<br>/500000 bps at machine clock frequency of 16 MHz)<br>Transmission can be performed by bi-directional serial transmission or by master/slave connection.                                              |                                                                                              |                        |  |  |  |

| UART1(                                                                                                                                                                                                                                                                                                                                                                                               | SCI)                      | Clock synchronized transmission (62.5 K/125<br>Clock asynchronized transmission (1202/240<br>Transmission can be performed by bi-directio                                                                                                                                                                                              | 4/4808/9615/31250 bps)                                                                       | ster/slave connection. |  |  |  |

| 8/10-bit /                                                                                                                                                                                                                                                                                                                                                                                           | A/D converter             | Conversion precision: 8/10-bit can be selectiv<br>Number of inputs: 8<br>One-shot conversion mode (converts selecte<br>Scan conversion mode (converts two or more<br>up to 8 chann<br>Continuous conversion mode (converts select<br>Stop conversion mode (converts selected cha                                                       | d channel once only)<br>e successive channels and can p<br>els)<br>ted channel continuously) | 0                      |  |  |  |

| 8/16-bit PPG timers       Number of channels: 6 (8/16-bit × 6 channels)         8/16-bit PPG timers       PPG operation of 8-bit or 16-bit         (6 channels)       A pulse wave of given intervals and given duty ratios can be output.         Pulse interval: fsys, fsys/2², fsys/2², fsys/2², fsys/2² (fsys = system clock frequency)         128μs (fosc = 4MHz: oscillation clock frequency) |                           |                                                                                                                                                                                                                                                                                                                                        |                                                                                              |                        |  |  |  |

| 16-bit Re                                                                                                                                                                                                                                                                                                                                                                                            | eload timer               | Number of channels: 2<br>Operation clock frequency: fsys/2 <sup>1</sup> , fsys/2 <sup>3</sup> , fs<br>Supports External Event Count function                                                                                                                                                                                           | ys/2 <sup>5</sup> (fsys = System clock frequ                                                 | ency)                  |  |  |  |

| 16-bit                                                                                                                                                                                                                                                                                                                                                                                               | 16-bit<br>Output compares | Number of channels: 4<br>Pin input factor: A match signal of compare re                                                                                                                                                                                                                                                                | egister                                                                                      |                        |  |  |  |

| I/O tim-<br>er                                                                                                                                                                                                                                                                                                                                                                                       | Input captures            | Number of channels: 4<br>Rewriting a register value upon a pin input (ri                                                                                                                                                                                                                                                               | sing, falling, or both edges)                                                                |                        |  |  |  |

| Features                                  | MB90598G                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MB90F598G                                                                                                                         | MB90V595G |  |  |  |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| CAN Interface                             | Jumber of channels: 1<br>Conforms to CAN Specification Version 2.0 Part A and B<br>Automatic re-transmission in case of error<br>Automatic transmission responding to Remote Frame<br>Prioritized 16 message buffers for data and ID's<br>Supports multiple messages<br>Texible configuration of acceptance filtering:<br>Full bit compare / Full bit mask / Two partial bit masks<br>Supports up to 1Mbps<br>CAN bit timing setting:<br>MB90598G/F598G:TSEG2 ≥ RSJW |                                                                                                                                   |           |  |  |  |  |  |

| Stepping motor controller (4 channels)    | Four high current outputs for each channel<br>Synchronized two 8-bit PWM's for each channel                                                                                                                                                                                                                                                                                                                                                                          | ur high current outputs for each channel<br>nchronized two 8-bit PWM's for each channel                                           |           |  |  |  |  |  |

| External interrupt circuit                | Number of inputs: 8<br>Started by a rising edge, a falling edge, an "H" le                                                                                                                                                                                                                                                                                                                                                                                           | lumber of inputs: 8<br>itarted by a rising edge, a falling edge, an "H" level input, or an "L" level input.                       |           |  |  |  |  |  |

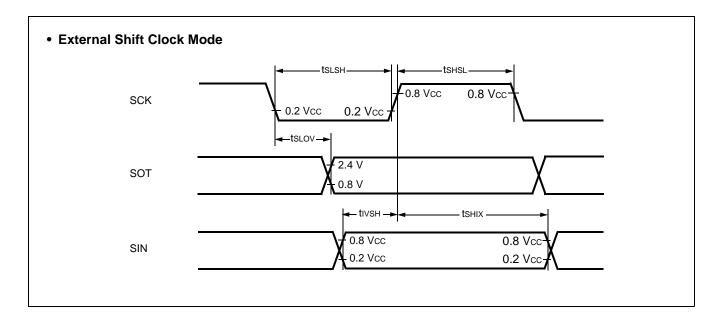

| Serial IO                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Clock synchronized transmission (31.25 K/62.5 K/125 K/500 K/1 Mbps at system clock<br>frequency of 16 MHz)<br>LSB first/MSB first |           |  |  |  |  |  |

| Watchdog timer                            | Reset generation interval: 3.58 ms, 14.33 ms, 57<br>(at oscillation of 4 MHz, minimum value)                                                                                                                                                                                                                                                                                                                                                                         | 7.23 ms, 458.75 ms                                                                                                                |           |  |  |  |  |  |

| Flash Memory                              | Supports automatic programming, Embedded Algorithm and<br>Write/Erase/Erase-Suspend/Resume commands<br>A flag indicating completion of the algorithm<br>Hard-wired reset vector available in order to point to a fixed boot sector in Flash<br>Memory<br>Boot block configuration<br>Erase can be performed on each block<br>Block protection with external programming voltage<br>Flash Writer from Minato Electronics. Inc.                                        |                                                                                                                                   |           |  |  |  |  |  |

| Low-power consumption (stand-by) mode     | Sleep/stop/CPU intermittent operation/watch time                                                                                                                                                                                                                                                                                                                                                                                                                     | er/hardware stand-by                                                                                                              |           |  |  |  |  |  |

| Process                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CMOS                                                                                                                              |           |  |  |  |  |  |

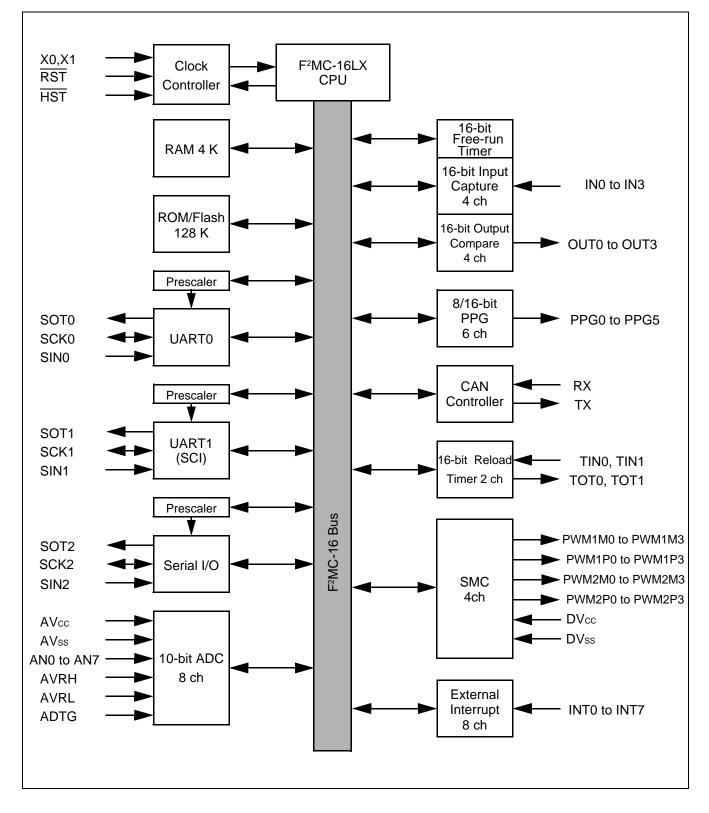

| Power supply voltage for opera-<br>tion*2 | +                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -5 V±10 %                                                                                                                         |           |  |  |  |  |  |

| Package                                   | QFP-100                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   | PGA-256   |  |  |  |  |  |

\*1: It is setting of DIP switch S2 when Emulation pod (MB2145-507) is used.

Please refer to the MB2145-507 hardware manual (2.7 Emulator-specific Power Pin) about details.

\*2: Varies with conditions such as the operating frequency. (See "Electrical Characteristics.")

# 3. Pin Description

| Pin no.  | Pin name     | Circuit type | Function                                      |  |  |  |

|----------|--------------|--------------|-----------------------------------------------|--|--|--|

| 82       | X0           | ٨            |                                               |  |  |  |

| 83       | X1           | A            | Oscillator pin                                |  |  |  |

| 77       | RST          | В            | Reset input                                   |  |  |  |

| 52       | HST          | С            | Hardware standby input                        |  |  |  |

| 85 to 88 | P00 to P03   | G            | General purpose IO                            |  |  |  |

| 00 10 00 | IN0 to IN3   | 6            | Inputs for the Input Captures                 |  |  |  |

| 89 to 92 | P04 to P07   | G            | General purpose IO                            |  |  |  |

| 09 10 92 | OUT0 to OUT3 | 9            | Outputs for the Output Compares.              |  |  |  |

| 93 to 98 | P10 to P15   | D            | General purpose IO                            |  |  |  |

| 93 10 98 | PPG0 to PPG5 | d            | Outputs for the Programmable Pulse Generators |  |  |  |

| 99       | P16          | D            | General purpose IO                            |  |  |  |

| 33       | TIN1         | d            | TIN input for the 16-bit Reload Timer 1       |  |  |  |

| 100      | P17          | D            | General purpose IO                            |  |  |  |

| 100      | TOT1         | d            | TOT output for the 16-bit Reload Timer 1      |  |  |  |

| 1 to 8   | P20 to P27   | G            | General purpose IO                            |  |  |  |

| 9 to 10  | P30 to P31   | G            | General purpose IO                            |  |  |  |

| 12 to 16 | P32 to P36   | G            | General purpose IO                            |  |  |  |

| 17       | P37          | D            | General purpose IO                            |  |  |  |

| 18       | P40          | G            | General purpose IO                            |  |  |  |

| 10       | SOT0         | 0            | SOT output for UART 0                         |  |  |  |

| 19       | P41          | G            | General purpose IO                            |  |  |  |

| 19       | SCK0         | 0            | SCK input/output for UART 0                   |  |  |  |

| 20       | P42          | G            | General purpose IO                            |  |  |  |

| 20       | SIN0         | 0            | SIN input for UART 0                          |  |  |  |

| 21       | P43          | G            | General purpose IO                            |  |  |  |

| 21       | SIN1         | 0            | SIN input for UART 1                          |  |  |  |

| 22       | P44          | G            | General purpose IO                            |  |  |  |

| 22       | SCK1         | 0            | SCK input/output for UART 1                   |  |  |  |

| 24       | P45          | G            | General purpose IO                            |  |  |  |

| 24       | SOT1         | 6            | SOT output for UART 1                         |  |  |  |

| 25       | P46          | G            | General purpose IO                            |  |  |  |

| 20       | SOT2         | 5            | SOT output for the Serial IO                  |  |  |  |

| 26       | P47          | G            | General purpose IO                            |  |  |  |

| 20       | SCK2         | 5            | SCK input/output for the Serial IO            |  |  |  |

| Circuit Type | Circuit            | Remarks                                                 |

|--------------|--------------------|---------------------------------------------------------|

|              |                    | CMOS high current output                                |

|              |                    | CMOS Hysteresis input                                   |

|              | P-ch               |                                                         |

|              |                    |                                                         |

|              | High current       |                                                         |

| F            | N-ch               |                                                         |

|              |                    |                                                         |

|              |                    |                                                         |

|              |                    |                                                         |

|              | R                  |                                                         |

|              | L <sub>W</sub> HYS |                                                         |

|              |                    | ■ CMOS output                                           |

|              | Vcc                | CMOS Hysteresis input                                   |

|              | P-ch               | ■ TTL input                                             |

|              |                    | (MB90F598G, only in Flash mode)                         |

|              | N-ch               |                                                         |

| G            |                    |                                                         |

| Ũ            |                    |                                                         |

|              | R                  |                                                         |

|              | HYS                |                                                         |

|              | R                  |                                                         |

|              |                    |                                                         |

|              |                    | <ul> <li>Hysteresis input</li> </ul>                    |

|              |                    | ■ Hysteresis input<br>Pull-down Resistor: 50 kΩ approx. |

|              |                    | (except MB90F598G)                                      |

| н            |                    |                                                         |

|              | R                  |                                                         |

|              |                    |                                                         |

|              | · · · ·            |                                                         |

### (12) Initialization

The device contains internal registers which are initialized only by a power-on reset. To initialize these registers, please turn on the power again.

#### (13) Directions of "DIV A, Ri" and "DIVW A, RWi" instructions

In the signed multiplication and division instructions ("DIV A, Ri" and "DIVW A, RWi"), the value of the corresponding bank register (DTB, ADB, USB, SSB) is set in "00H".

If the values of the corresponding bank register (DTB,ADB,USB,SSB) are set to other than "00<sub>H</sub>", the remainder by the execution result of the instruction is not stored in the register of the instruction operand.

### (14) Using REALOS

The use of El<sup>2</sup>OS is not possible with the REALOS real time operating system.

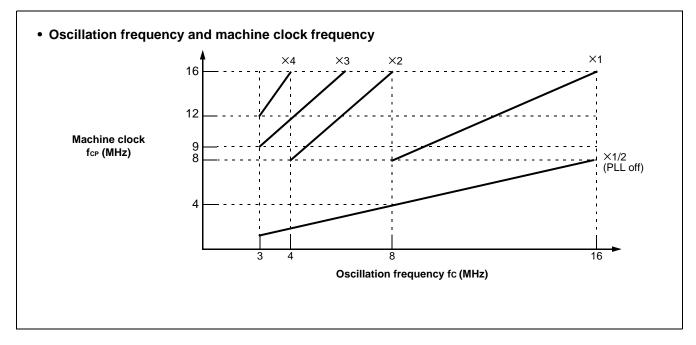

#### (15) Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected in the microcontroller, it may attempt to continue the operation using the free-running frequency of the automatic oscillating circuit in the PLL circuitry even if the oscillator is out of place or the clock input is stopped. Performance of this operation, however, cannot be guaranteed.

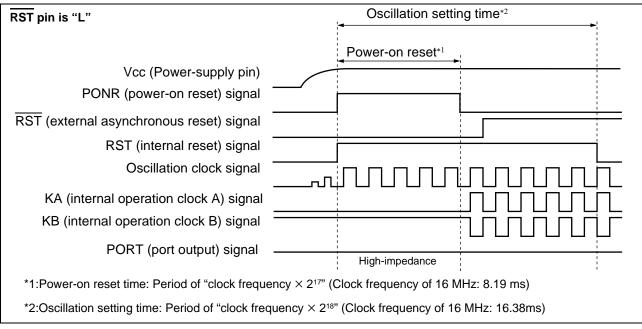

## 6. Block Diagram

| Address         | Register                                  | Abbreviation | Access | Peripheral                   | Initial value |

|-----------------|-------------------------------------------|--------------|--------|------------------------------|---------------|

| 29н to 2Ан      |                                           | Reserved     |        |                              |               |

| 2Вн             | Serial IO Prescaler                       | SCDCR        | R/W    |                              | 01111в        |

| 2Сн             | Serial Mode Control Register (low-order)  | SMCS         | R/W    |                              | 0000в         |

| 2Dн             | Serial Mode Control Register (high-order) | SMCS         | R/W    | Serial IO                    | 00000010в     |

| 2Ен             | Serial Data Register                      | SDR          | R/W    |                              | XXXXXXXXB     |

| <b>2</b> Fн     | Edge Selector                             | SES          | R/W    |                              | 0в            |

| 30н             | External Interrupt Enable Register        | ENIR         | R/W    |                              | 000000000     |

| 31н             | External Interrupt Request Register       | EIRR         | R/W    | External Interrupt           | XXXXXXXXB     |

| 32н             | External Interrupt Level Register         | ELVR         | R/W    | External Interrupt           | 000000000     |

| 33н             | External Interrupt Level Register         | ELVR         | R/W    |                              | 000000000     |

| 34н             | A/D Control Status Register 0             | ADCS0        | R/W    |                              | 000000000     |

| 35н             | A/D Control Status Register 1             | ADCS1        | R/W    |                              | 000000000     |

| 36н             | A/D Data Register 0                       | ADCR0        | R      | A/D Converter                | XXXXXXXXB     |

| 37н             | A/D Data Register 1                       | ADCR1        | R/W    |                              | 00001_XXв     |

| 38н             | PPG0 Operation Mode Control Register      | PPGC0        | R/W    | 16-bit Programmable          | 0_000_1в      |

| 39н             | PPG1 Operation Mode Control Register      | PPGC1        | R/W    | Pulse                        | 0_00001в      |

| ЗАн             | PPG0, 1 Output Pin Control Register       | PPG01        | R/W    | Generator 0/1                | 00000в        |

| 3Вн             |                                           | Reserved     |        |                              |               |

| 3Сн             | PPG2 Operation Mode Control Register      | PPGC2        | R/W    | 16-bit Programmable          | 0_000_1в      |

| 3Dн             | PPG3 Operation Mode Control Register      | PPGC3        | R/W    | Pulse                        | 0_00001в      |

| 3Ен             | PPG2, 3 Output Pin Control Register       | PPG23        | R/W    | Generator 2/3                | 000000в       |

| 3Fн             |                                           | Reserved     |        |                              |               |

| 40н             | PPG4 Operation Mode Control Register      | PPGC4        | R/W    | 16 bit Brogrommoble          | 0_000_1в      |

| 41н             | PPG5 Operation Mode Control Register      | PPGC5        | R/W    | 16-bit Programmable<br>Pulse | 0_00001в      |

| <b>42</b> H     | PPG4, 5 Output Pin Control Register       | PPG45        | R/W    | Generator 4/5                | 000000в       |

| 43н             |                                           | Reserved     |        |                              |               |

| 44 <sub>H</sub> | PPG6 Operation Mode Control Register      | PPGC6        | R/W    | 16 bit Drogrommakia          | 0_000_1в      |

| <b>45</b> H     | PPG7 Operation Mode Control Register      | PPGC7        | R/W    | 16-bit Programmable<br>Pulse | 0_00001в      |

| <b>46</b> H     | PPG6, 7 Output Pin Control Register       | PPG67        | R/W    | Generator 6/7                |               |

| <b>47</b> н     |                                           | Reserved     |        | 1                            |               |

| <b>48</b> H     | PPG8 Operation Mode Control Register      | PPGC8        | R/W    | 16 bit Drogsommet L          | 0_000_1в      |

| <b>49</b> н     | PPG9 Operation Mode Control Register      | PPGC9        | R/W    | 16-bit Programmable<br>Pulse | 0_00001в      |

| 4Ан             | PPG8, 9 Output Pin Control Register       | PPG89        | R/W    | Generator 8/9                |               |

| 4Bн             |                                           | Reserved     |        | 1                            |               |

| Address           | Register                                  | Abbreviation | Access | Peripheral                | Initial value         |

|-------------------|-------------------------------------------|--------------|--------|---------------------------|-----------------------|

| 1910н             | Reload Register L                         | PRLL8        | R/W    |                           | XXXXXXXX              |

| 1911н             | Reload Register H                         | PRLH8        | R/W    | 16-bit Programmable Pulse | XXXXXXXX              |

| 1912н             | Reload Register L                         | PRLL9        | R/W    | Generator 8/9             | XXXXXXXX              |

| 1913н             | Reload Register H                         | PRLH9        | R/W    |                           | XXXXXXXX <sub>B</sub> |

| 1914 <sub>H</sub> | Reload Register L                         | PRLLA        | R/W    | 16-bit Programmable Pulse | XXXXXXXX <sub>B</sub> |

| 1915 <sub>H</sub> | Reload Register H                         | PRLHA        | R/W    | Generator A/B             | XXXXXXXX <sub>B</sub> |

| 1916 <sub>H</sub> | Reload Register L                         | PRLLB        | R/W    | 16-bit Programmable Pulse | XXXXXXXX <sub>B</sub> |

| <b>1917</b> н     | Reload Register H                         | PRLHB        | R/W    | Generator A/B             | XXXXXXXX <sub>B</sub> |

| 1918н to 191Fн    |                                           | Re           | served |                           |                       |

| 1920н             | Input Capture Register 0<br>(low-order)   | IPCP0        | R      |                           | XXXXXXXX <sub>B</sub> |

| 1921н             | Input Capture Register 0<br>(high-order)  | IPCP0        | R      |                           | XXXXXXXXAB            |

| 1922н             | Input Capture Register 1<br>(low-order)   | IPCP1        | R      | Input Capture 0/1         | XXXXXXXX <sub>B</sub> |

| 1923н             | Input Capture Register 1<br>(high-order)  | IPCP1        | R      |                           | XXXXXXXX <sub>B</sub> |

| <b>1924</b> н     | Input Capture Register 2<br>(low-order)   | IPCP2        | R      |                           | XXXXXXXX              |

| 1925н             | Input Capture Register 2<br>(high-order)  | IPCP2        | R      |                           | XXXXXXXX              |

| 1926н             | Input Capture Register 3<br>(low-order)   | IPCP3        | R      | Input Capture 2/3         | XXXXXXXX              |

| <b>1927</b> н     | Input Capture Register 3<br>(high-order)  | IPCP3        | R      |                           | XXXXXXXX              |

| 1928 <sub>H</sub> | Output Compare Register 0<br>(low-order)  | OCCP0        | R/W    |                           | XXXXXXXX              |

| 1929н             | Output Compare Register 0<br>(high-order) | OCCP0        | R/W    |                           | XXXXXXXX              |

| 192Ан             | Output Compare Register 1<br>(low-order)  | OCCP1        | R/W    | Output Compare 0/1        | XXXXXXXX              |

| 192Bн             | Output Compare Register 1<br>(high-order) | OCCP1        | R/W    |                           | XXXXXXXX              |

(Continued)

## 9.3 List of Message Buffers (DLC Registers and Data Registers)

| Address                  | Register                  | Initial Value |         |                             |  |

|--------------------------|---------------------------|---------------|---------|-----------------------------|--|

| 001A60н                  |                           |               | D 444   | ~~~~~                       |  |

| <b>001А61</b> н          | DLC register 0            | DLCR0         | R/W     | XXXXB                       |  |

| 001A62н                  |                           |               | DAA     |                             |  |

| 001A63н                  | DLC register 1            | DLCR1         | R/W     | ХХХХв                       |  |

| 001A64н                  |                           |               | DAA     | VVV-                        |  |

| 001A65н                  | DLC register 2            | DLCR2         | R/W     | ХХХХв                       |  |

| 001A66н                  | - DLC register 3          | DLCR3         | R/W     | ХХХХв                       |  |

| <b>001А67</b> н          | DLC register 3            | DLCR3         | R/VV    | XXXAB                       |  |

| 001A68н                  | DLC register 4            |               | DAM     | VVV-                        |  |

| 001A69н                  | DLC register 4            | DLCR4         | R/W     | ХХХХв                       |  |

| 001А6Ан                  | DLC register 5            | DLCR5         | R/W     | ХХХХв                       |  |

| 001A6Bн                  | DLC register 5            | DLCRS         | r./vv   |                             |  |

| 001A6Cн                  | DLC register 6            | DLCR6         | R/W     |                             |  |

| 001A6DH                  | DLC register o            | DLCRO         | r./vv   | XXXX <sub>B</sub>           |  |

| 001A6Eн                  | DLC register 7            | DLCR7         | R/W     | ХХХХв                       |  |

| 001A6Fн                  |                           | DLCR7         | r./vv   |                             |  |

| <b>001А70</b> н          | DLC register 8            | DLCR8         | R/W     | XXXX                        |  |

| <b>001A71</b> н          | DLC register o            | DECKO         |         | ^                           |  |

| <b>001А72</b> н          | DLC register 9            | DLCR9         | R/W     | XXXXB                       |  |

| <b>001А73</b> н          | DLC register 9            | DLCK9         | FN/ V V |                             |  |

| 001A74н                  | DLC register 10           | DLCR10        | R/W     | XXXXB                       |  |

| 001A75н                  |                           | DECKTO        | 10/00   |                             |  |

| 001A76н                  | DLC register 11           | DLCR11        | R/W     | XXXXB                       |  |

| <b>001А77</b> н          |                           | DECKT         | 10/00   |                             |  |

| 001A78н                  | DLC register 12           | DLCR12        | R/W     | XXXXB                       |  |

| 001A79н                  |                           | DEORTZ        | 10,00   |                             |  |

| 001А7Ан                  | DLC register 13           | DLCR13        | R/W     | XXXXB                       |  |

| 001A7Bн                  |                           | DEORIG        |         |                             |  |

| 001A7Cн                  | DLC register 14           | DLCR14        | R/W     | ХХХХв                       |  |

| 001A7DH                  |                           | DLOR 14       |         |                             |  |

| 001A7Eн                  | DLC register 15           | DLCR15        | R/W     | XXXXB                       |  |

| 001A7Fн                  |                           | DEORIG        |         | /////6                      |  |

| 001А80н<br>to<br>001А87н | Data register 0 (8 bytes) | DTR0          | R/W     | XXXXXXXXB<br>to<br>XXXXXXXB |  |

(Continued)

# 10. Interrupt Source, Interrupt Vector, and Interrupt Control Register

|                                | El <sup>2</sup> OS | Interru | pt vector           | Interrupt control register |                  |  |

|--------------------------------|--------------------|---------|---------------------|----------------------------|------------------|--|

| Interrupt source               | clear              | Number  | Address             | Number                     | Address          |  |

| Reset                          | N/A                | # 08    | FFFFDCH             |                            |                  |  |

| INT9 instruction               | N/A                | # 09    | FFFFD8H             |                            |                  |  |

| Exception                      | N/A                | # 10    | FFFFD4H             |                            |                  |  |

| CAN RX                         | N/A                | # 11    | FFFFD0H             | 10000                      | 0000000          |  |

| CAN TX/NS                      | N/A                | # 12    | FFFFCC <sub>H</sub> | ICR00                      | 0000В0н          |  |

| External Interrupt (INT0/INT1) | *1                 | # 13    | FFFFC8 <sub>H</sub> | 10001                      | 0000B1н          |  |

| Time Base Timer                | N/A                | # 14    | FFFFC4 <sub>H</sub> | ICR01                      | 0000011          |  |

| 16-bit Reload Timer 0          | *1                 | # 15    | FFFFC0H             | ICR02                      | 0000000          |  |

| 8/10-bit A/D Converter         | *1                 | # 16    | <b>FFFFBC</b> H     | ICR02                      | 0000В2н          |  |

| 16-bit Free-run Timer          | N/A                | # 17    | FFFFB8H             | 10000                      | 0000000          |  |

| External Interrupt (INT2/INT3) | *1                 | # 18    | FFFFB4H             | ICR03                      | 0000ВЗн          |  |

| Serial I/O                     | *1                 | # 19    | FFFFB0H             | ICR04                      | 0000B4н          |  |

| External Interrupt (INT4/INT5) | *1                 | # 20    | <b>FFFFAC</b> H     | ICK04                      |                  |  |

| Input Capture 0                | *1                 | # 21    | FFFFA8H             | ICR05                      | 0000 <b>B</b> 5н |  |

| 8/16-bit PPG 0/1               | N/A                | # 22    | FFFFA4H             | ICR05                      | 0000638          |  |

| Output Compare 0               | *1                 | # 23    | FFFFA0H             | ICR06                      | 0000 <b>В6</b> н |  |

| 8/16-bit PPG 2/3               | N/A                | # 24    | FFFF9CH             | ICRUO                      | OOODDOH          |  |

| External Interrupt (INT6/INT7) | *1                 | # 25    | FFFF98н             | ICR07                      | 0000 <b>B7</b> н |  |

| Input Capture 1                | *1                 | # 26    | FFFF94н             |                            | 0000071          |  |

| 8/16-bit PPG 4/5               | N/A                | # 27    | FFFF90н             | ICR08                      | 0000B8н          |  |

| Output Compare 1               | *1                 | # 28    | FFFF8CH             | 101000                     | 0000B0H          |  |

| 8/16-bit PPG 6/7               | N/A                | # 29    | FFFF88 <sub>H</sub> | ICR09                      | 0000 <b>В</b> 9н |  |

| Input Capture 2                | *1                 | # 30    | FFFF84 <sub>H</sub> | 101(09                     | 0000898          |  |

| 8/16-bit PPG 8/9               | N/A                | # 31    | FFFF80н             | ICR10                      | 0000ВАн          |  |

| Output Compare 2               | *1                 | # 32    | FFFF7C <sub>H</sub> |                            | UUUUDAH          |  |

| Input Capture 3                | *1                 | # 33    | FFFF78⊦             | ICR11                      | 0000BBн          |  |

| 8/16-bit PPG A/B               | N/A                | # 34    | FFFF74 <sub>H</sub> | юкт                        | COCOBBA          |  |

| Output Compare 3               | *1                 | # 35    | FFFF70н             | ICR12                      | 0000BCH          |  |

| 16-bit Reload Timer 1          | *1                 | # 36    | FFFF6C <sub>H</sub> | 101(12                     | 0000000          |  |

| UART 0 RX                      | *2                 | # 37    | FFFF68н             | ICR13                      | 0000BDн          |  |

| UART 0 TX                      | *1                 | # 38    | FFFF64⊦             |                            | UUUUBDH          |  |

| UART 1 RX                      | *2                 | # 39    | FFFF60н             | ICR14                      | 0000BEн          |  |

| UART 1 TX                      | *1                 | # 40    | FFFF5C <sub>H</sub> |                            |                  |  |

| Flash Memory                   | N/A                | # 41    | FFFF58⊦             | ICR15                      | 0000BFн          |  |

| Delayed interrupt              | N/A                | # 42    | FFFF54н             |                            | UUUUDI'H         |  |

\*1: The interrupt request flag is cleared by the El<sup>2</sup>OS interrupt clear signal.

\*2: The interrupt request flag is cleared by the El<sup>2</sup>OS interrupt clear signal. A stop request is available.

N/A:The interrupt request flag is not cleared by the EI2OS interrupt clear signal.

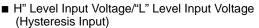

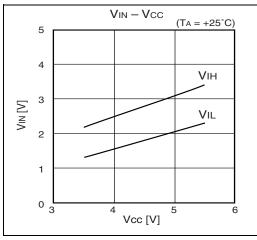

## **11. Electrical Characteristics**

### 11.1 Absolute Maximum Ratings

(Vss = AVss = 0.0 V)

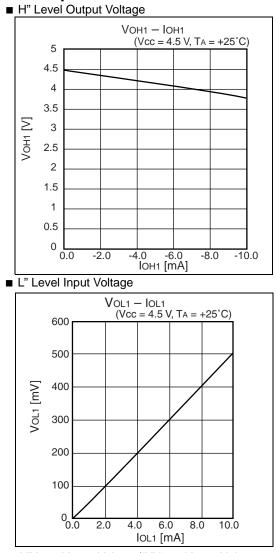

| Parameter                             | Symbol           | Rating                |           | Unit | Remarks                                  |    |

|---------------------------------------|------------------|-----------------------|-----------|------|------------------------------------------|----|

| Parameter                             | Symbol           | Min                   | Max       | Unit | Remarks                                  |    |

|                                       | Vcc              | Vss - 0.3             | Vss + 6.0 | V    |                                          |    |

|                                       | AVcc             | $V_{SS} - 0.3$        | Vss + 6.0 | V    | Vcc = AVcc                               | *1 |

| Power supply voltage                  | AVRH,<br>AVRL    | V <sub>SS</sub> - 0.3 | Vss + 6.0 | V    | AVcc ≥ AVRH/L,<br>AVRH ≥ AVRL            | *1 |

|                                       | DVcc             | $V_{SS} - 0.3$        | Vss + 6.0 | V    | Vcc ≥ DVcc                               |    |

| Input voltage                         | Vi               | $V_{SS} - 0.3$        | Vss + 6.0 | V    |                                          | *2 |

| Output voltage                        | Vo               | $V_{SS} - 0.3$        | Vss + 6.0 | V    |                                          | *2 |

| Maximum Clamp Current                 |                  | -2.0                  | 2.0       | mA   | *6                                       |    |

| Maximum Total Clamp Current           | ∑ Iclamp         | —                     | 20        | mA   | *6                                       |    |

| "L" level Max. output current         | IOL1             | _                     | 15        | mA   | Normal output                            | *3 |

| "L" level Avg. output current         | IOLAV1           | _                     | 4         | mA   | Normal output, average value             | *4 |

| "L" level Max. output current         | IOL2             | _                     | 40        | mA   | High current output                      | *3 |

| "L" level Avg. output current         | IOLAV2           | _                     | 30        | mA   | High current output, average value       | *4 |

| "L" level Max. overall output current | ∑lol1            | _                     | 100       | mA   | Total normal output                      |    |

| "L" level Max. overall output current | ∑lol2            | —                     | 330       | mA   | Total high current output                |    |

| "L" level Avg. overall output current | $\sum$ IOLAV1    | _                     | 50        | mA   | Total normal output, average value       | *5 |

| "L" level Avg. overall output current | $\sum$ Iolav2    | _                     | 250       | mA   | Total high current output, average value | *5 |

| "H" level Max. output current         | Іон1             | _                     | -15       | mA   | Normal output                            | *3 |

| "H" level Avg. output current         | IOHAV1           | _                     | -4        | mA   | Normal output, average value             | *4 |

| "H" level Max. output current         | Іон2             | _                     | -40       | mA   | High current output                      | *3 |

| "H" level Avg. output current         | IOHAV2           | _                     | -30       | mA   | High current output, average value       | *4 |

| "H" level Max. overall output current | ∑Іон1            | _                     | -100      | mA   | Total normal output                      |    |

| "H" level Max. overall output current | ∑Іон₂            | _                     | -330      | mA   | Total high current output                |    |

| "H" level Avg. overall output current | ∑lohav1          | _                     | -50       | mA   | Total normal output, average value       | *5 |

| "H" level Avg. overall output current | ∑ <b>I</b> OHAV2 | _                     | -250      | mA   | Total high current output, average value | *5 |

| Power concumption                     | Pp               | —                     | 500       | mW   | MB90F598G                                |    |

| Power consumption                     | PD               | _                     | 400       | mW   | MB90598G                                 |    |

| Operating temperature                 | TA               | -40                   | +85       | °C   |                                          |    |

| Storage temperature                   | Tstg             | -55                   | +150      | °C   |                                          |    |

\*1: AVcc, AVRH, AVRL and DVcc shall not exceed Vcc. AVRH and AVRL shall not exceed AVcc. Also, AVRL shall never exceed AVRH.

\*2: VI and Vo should not exceed Vcc + 0.3V. VI should not exceed the specified ratings. However if the maximum current to/from an input is limited by some means with external components, the IcLAMP rating supersedes the VI rating.

\*3: The maximum output current is a peak value for a corresponding pin.

\*4: Average output current is an average current value observed for a 100 ms period for a corresponding pin.

\*5: Total average current is an average current value observed for a 100 ms period for all corresponding pins.

\*6:

- Applicable to pins : P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P70 to P77, P80 to P87, P90 to P95

- Use within recommended operating conditions.

- Use at DC voltage (current) .

- The +B signal should always be applied with a limiting resistance placed between the +B signal and the microcontroller.

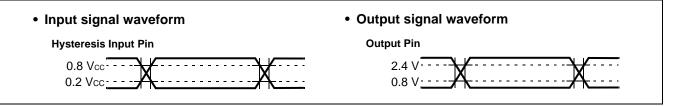

AC characteristics are set to the measured reference voltage values below.

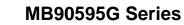

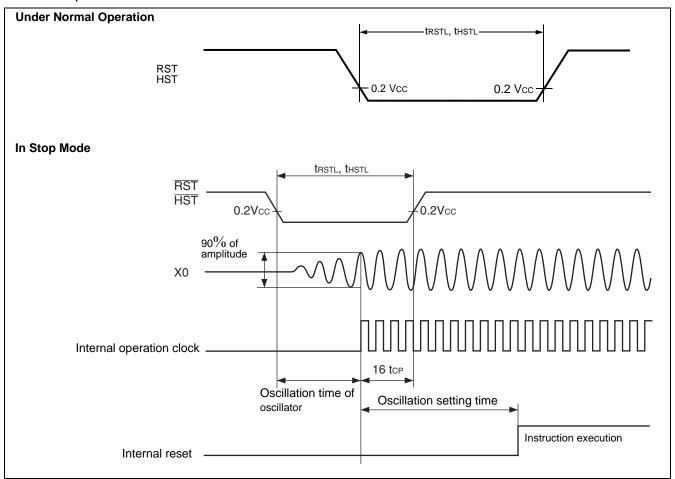

#### 11.4.2 Reset and Hardware Standby Input

| $(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ Vss} = \text{AVss} = 0.0 \text{ V}, \text{ T}_{\text{A}} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C})$ |               |            |                                                                          |     |      |                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|--------------------------------------------------------------------------|-----|------|------------------------|--|

| Parameter                                                                                                                                                    | Symbol        | Pin name   | Value                                                                    |     | Unit | Remarks                |  |

|                                                                                                                                                              | Symbol        | Finitianie | Min                                                                      | Max | Unit | Reinarks               |  |

| Reset input time                                                                                                                                             |               | trstl RST  | 16 tcp*1                                                                 | —   | ns   | Under normal operation |  |

|                                                                                                                                                              | <b>t</b> RSTL |            | Oscillation time of oscillator <sup>*2</sup> + 16 $t_{CP}$ <sup>*1</sup> | —   | ms   | In stop mode           |  |

|                                                                                                                                                              |               |            | 16 tcp*1                                                                 | —   | ns   | Under normal operation |  |

| Hardware standby input time                                                                                                                                  | tнsт∟         | there HST  | Oscillation time of oscillator <sup>*2</sup> + 16 $t_{CP}^{*1}$          | —   | ms   | In stop mode           |  |

\*1: "tcp" represents one cycle time of the machine clock.

No reset can fully initialize the Flash Memory if it is performing the automatic algorithm.

\*2: Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

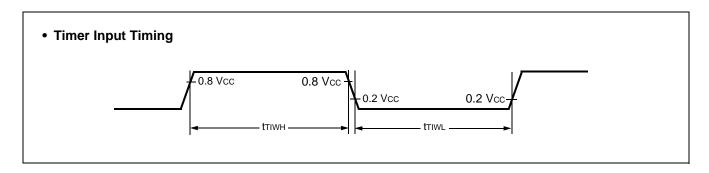

### (5) Timer Input Timing

$(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ V}_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, \text{ T}_{A} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C})$

| Parameter         | Symbol | Pin name   | Condition | Va                | Value |      | Remarks |

|-------------------|--------|------------|-----------|-------------------|-------|------|---------|

| Falameter         | Symbol | Fin hame   | Condition | Min               | Max   | Unit | Remarks |

| Input pulse width | tтіwн  | TIN0, TIN1 |           | 4 t <sub>CP</sub> |       | 20   |         |

| mput puise width  | t⊤ıw∟  | IN0 to IN3 |           | 4 ICP             | _     | ns   |         |

### 11.4.5 Trigger Input Timing

$(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ V}_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, \text{ T}_{A} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C})$

| Parameter         | Symbol | Pin name      | Condition | Value |     | Unit | Remarks                |  |

|-------------------|--------|---------------|-----------|-------|-----|------|------------------------|--|

| Farameter         | Symbol | Fill Hallie   | Condition | Min   | Мах | Unit | Relliarks              |  |

| Input pulse width |        | INT0 to INT7, | _         | 5 tcp | _   | ns   | Under normal operation |  |

| input puise width |        | ADTG          |           | 1     |     | μs   | In stop mode           |  |

| Parameter                     | Sym- | Pin name   | Value      |     |            |                | Remarks                 |

|-------------------------------|------|------------|------------|-----|------------|----------------|-------------------------|

| Faiametei                     | bol  | Fin hame   | Min        | Тур | Max        | mA<br>μA<br>μA | Reillarks               |

| Poforonoo voltago rango       | —    | AVRH       | AVRL + 3.0 | —   | AVcc       | V              |                         |

| Reference voltage range       | —    | avrL       | 0          | —   | AVRH - 3.0 | V              |                         |

| Power supply current          | la   | AVcc       | _          | 5   | —          | mA             |                         |

|                               | Іан  | AVcc       | _          |     | 5          | μA             | *                       |

| Reference voltage current     | Ir   | AVRH       | _          | 400 | 600        | μΑ             | MB90V595G,<br>MB90F598G |

|                               |      |            | _          | 140 | 600        | μA             | MB90598G                |

|                               | Irh  | AVRH       | _          |     | 5          | μA             | *                       |

| Offset between input channels | _    | AN0 to AN7 | _          | _   | 4          | LSB            |                         |

\*: When not operating A/D converter, this is the current ( $V_{CC} = AV_{CC} = AVRH = 5.0$  V) when the CPU is stopped.

### (Continued)

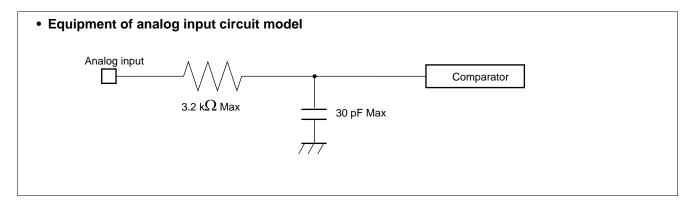

### 11.7 Notes on Using A/D Converter

Select the output impedance value for the external circuit of analog input according to the following conditions,:

- Output impedance values of the external circuit of 15 k $\Omega$  or lower are recommended.

- When capacitors are connected to external pins, the capacitance of several thousand times the internal capacitor value is recommended to minimized the effect of voltage distribution between the external capacitor and internal capacitor.

When the output impedance of the external circuit is too high, the sampling period for analog voltages may not be sufficient (sampling period =  $4.00 \ \mu s$  @machine clock of 16 MHz).

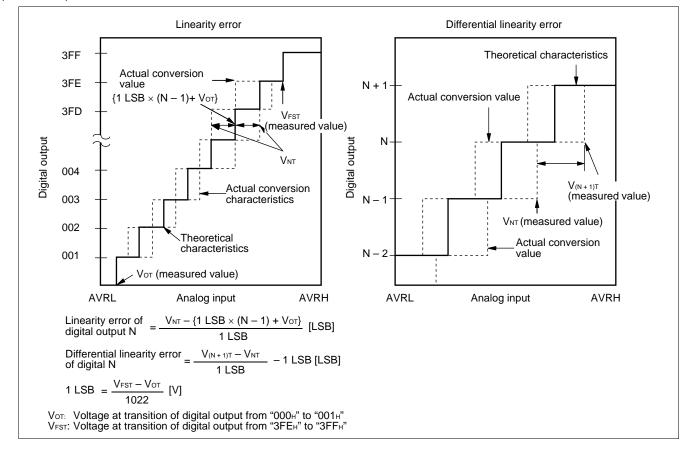

### Error

The smaller the |AVRH - AVRL|, the greater the error would become relatively.

## **12. Example Characteristics**

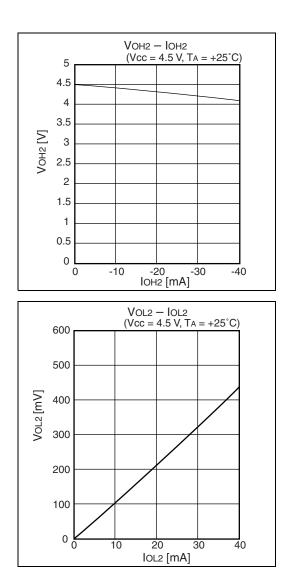

# **13. Ordering Information**

| Part number               | Package                               | Remarks        |

|---------------------------|---------------------------------------|----------------|

| MB90598GPF<br>MB90F598GPF | 100-pin Plastic QFP<br>(FPT-100P-M06) |                |

| MB90V595GCR               | 256-pin Ceramic PGA<br>(PGA-256C-A01) | For evaluation |

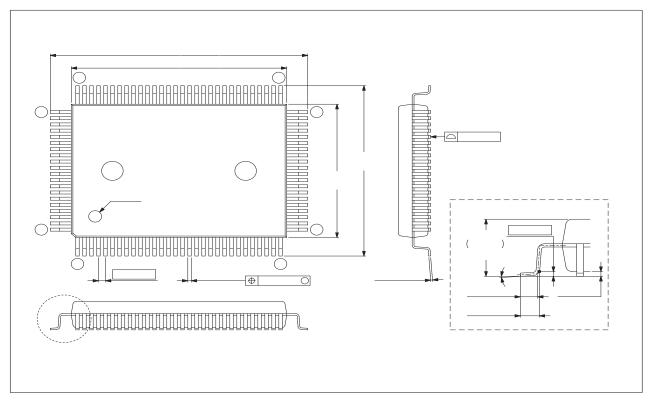

# 14. Package Dimensions

### 15. Major Changes

#### Spansion Publication Number: DS07-13705-7E

| Section                                          | Change Results                                                                                                         |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| -                                                | Deleted the old products, MB90598, MB90F598, and MB90V595.                                                             |

| -                                                | Changed the series name;<br>MB90595/595G series ? MB90595G series                                                      |

| -                                                | Changed the following erroneous name. I/O timer $\rightarrow$ 16-bit Free-run Timer                                    |

| PRODUCT LINEUP                                   | One of Standby mode name is changed. Clock mode $\rightarrow$ Watch mode                                               |

| I/O CIRCUIT TYPE                                 | Changed Pull-down resistor value of circuit type H.                                                                    |

| ELECTRICAL CHARACTERISTICS<br>AC Characteristics | Add the "External clock input" and "Flash Read cycle time" in (1) Clock Timing                                         |

|                                                  | Figure in (2) Reset and Hardware Standby Input<br>RST/HST input level of "In Stop Mode" is changed.<br>0.6 Vcc 0.2 Vcc |

| ELECTRICAL CHARACTERISTICS<br>5. A/D Converter   | Changed the items of "Zero transition voltage" and "Full scale transition voltage".                                    |

NOTE: Please see "Document History" about later revised information.

# **Document History**

Document Title: MB90598G/F598G/V595G F<sup>2</sup>MC-16LX MB90595G Series CMOS 16-bit Proprietary Microcontroller Document Number: 002-07700 Orig. of Change Submission Revision ECN **Description of Change** Date \*\* \_ AKIH 09/26/2008 Migrated to Cypress and assigned document number 002-07700. No change to document contents or format. \*A 5537128 AKIH 11/30/2016 Updated to Cypress template

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers cypress. | oonii/anni |

|----------------------------------------------------------------|------------|

| Automotive cypress.com/au                                      | Itomotive  |

| Clocks & Buffers cypress.co                                    | m/clocks   |

| Interface cypress.com/                                         | /interface |

| Internet of Things cypres                                      | s.com/iot  |

| Lighting & Power Control cypress.com/pc                        | owerpsoc   |

| Memory cypress.com                                             | /memory    |

| PSoC cypress.c                                                 | com/psoc   |

| Touch Sensing cypress.co                                       | om/touch   |

| USB Controllers cypress.                                       | .com/usb   |

| Wireless/RF cypress.com                                        | /wireless  |

PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Forums | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuctitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

<sup>©</sup> Cypress Semiconductor Corporation, 2008-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress bereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.