Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | F <sup>2</sup> MC-16LX                                                           |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                                     |

| Peripherals                | POR, PWM, WDT                                                                    |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | Mask ROM                                                                         |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 8x8/10b                                                                      |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-BQFP                                                                         |

| Supplier Device Package    | 100-QFP (14x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90598gpf-g-150-jne1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                               | MB90598G                                                                                                                                                                                                                                                                                                                                                                                              | MB90F598G                                                                                                                                                                                                                                                                                                                                                                    | MB90V595G |  |  |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| CAN Interface                          | Automatic re-transmission in case of error<br>Automatic transmission responding to Remote F<br>Prioritized 16 message buffers for data and ID's<br>Supports multiple messages<br>Flexible configuration of acceptance filtering:                                                                                                                                                                      | onforms to CAN Specification Version 2.0 Part A and B utomatic re-transmission in case of error utomatic transmission responding to Remote Frame rioritized 16 message buffers for data and ID's upports multiple messages lexible configuration of acceptance filtering: ull bit compare / Full bit mask / Two partial bit masks upports up to 1Mbps AN bit timing setting: |           |  |  |  |  |  |

| Stepping motor controller (4 channels) | Four high current outputs for each channel Synchronized two 8-bit PWM's for each channel                                                                                                                                                                                                                                                                                                              | ur high current outputs for each channel nchronized two 8-bit PWM's for each channel                                                                                                                                                                                                                                                                                         |           |  |  |  |  |  |

| External interrupt circuit             | Number of inputs: 8<br>Started by a rising edge, a falling edge, an "H" le                                                                                                                                                                                                                                                                                                                            | umber of inputs: 8 tarted by a rising edge, a falling edge, an "H" level input, or an "L" level input.                                                                                                                                                                                                                                                                       |           |  |  |  |  |  |

| Serial IO                              |                                                                                                                                                                                                                                                                                                                                                                                                       | Clock synchronized transmission (31.25 K/62.5 K/125 K/500 K/1 Mbps at system clock frequency of 16 MHz)  SB first/MSB first                                                                                                                                                                                                                                                  |           |  |  |  |  |  |

| Watchdog timer                         | Reset generation interval: 3.58 ms, 14.33 ms, 57 (at oscillation of 4 MHz, minimum value)                                                                                                                                                                                                                                                                                                             | 7.23 ms, 458.75 ms                                                                                                                                                                                                                                                                                                                                                           |           |  |  |  |  |  |

| Flash Memory                           | Supports automatic programming, Embedded Algorithm and Nrite/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Hard-wired reset vector available in order to point to a fixed boot sector in Flash Memory Boot block configuration Erase can be performed on each block Block protection with external programming voltage Flash Writer from Minato Electronics, Inc. |                                                                                                                                                                                                                                                                                                                                                                              |           |  |  |  |  |  |

| Low-power consumption (stand-by) mode  | Sleep/stop/CPU intermittent operation/watch timer/hardware stand-by                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                              |           |  |  |  |  |  |

| Process                                | CMOS                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                              |           |  |  |  |  |  |

| Power supply voltage for operation*2   | +                                                                                                                                                                                                                                                                                                                                                                                                     | +5 V±10 %                                                                                                                                                                                                                                                                                                                                                                    |           |  |  |  |  |  |

| Package                                | QFP-100                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                              | PGA-256   |  |  |  |  |  |

<sup>\*1:</sup> It is setting of DIP switch S2 when Emulation pod (MB2145-507) is used.

Please refer to the MB2145-507 hardware manual (2.7 Emulator-specific Power Pin) about details.

<sup>\*2:</sup> Varies with conditions such as the operating frequency. (See "Electrical Characteristics.")

# 3. Pin Description

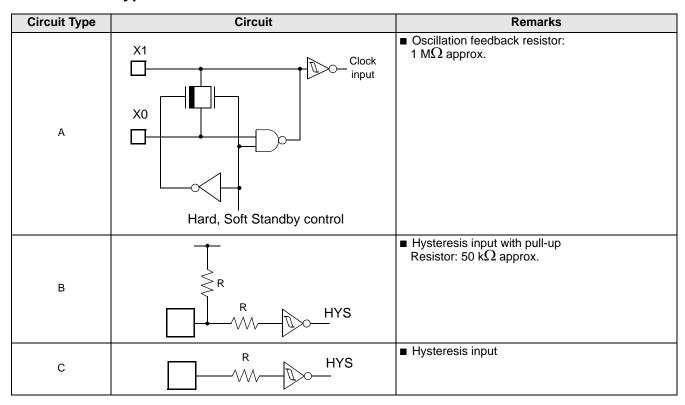

| Pin no.  | Pin name     | Circuit type | Function                                      |  |  |  |  |

|----------|--------------|--------------|-----------------------------------------------|--|--|--|--|

| 82       | X0           |              |                                               |  |  |  |  |

| 83       | X1           | А            | Oscillator pin                                |  |  |  |  |

| 77       | RST          | В            | Reset input                                   |  |  |  |  |

| 52       | HST          | С            | Hardware standby input                        |  |  |  |  |

| 05 to 00 | P00 to P03   | 0            | General purpose IO                            |  |  |  |  |

| 85 to 88 | IN0 to IN3   | G            | Inputs for the Input Captures                 |  |  |  |  |

| 89 to 92 | P04 to P07   | 0            | General purpose IO                            |  |  |  |  |

| 89 10 92 | OUT0 to OUT3 | G            | Outputs for the Output Compares.              |  |  |  |  |

| 00 to 00 | P10 to P15   | 5            | General purpose IO                            |  |  |  |  |

| 93 to 98 | PPG0 to PPG5 | D            | Outputs for the Programmable Pulse Generators |  |  |  |  |

| 00       | P16          | 5            | General purpose IO                            |  |  |  |  |

| 99       | TIN1         | D            | TIN input for the 16-bit Reload Timer 1       |  |  |  |  |

| 400      | P17          | 5            | General purpose IO                            |  |  |  |  |

| 100      | TOT1         | D            | TOT output for the 16-bit Reload Timer 1      |  |  |  |  |

| 1 to 8   | P20 to P27   | G            | General purpose IO                            |  |  |  |  |

| 9 to 10  | P30 to P31   | G            | General purpose IO                            |  |  |  |  |

| 12 to 16 | P32 to P36   | G            | General purpose IO                            |  |  |  |  |

| 17       | P37          | D            | General purpose IO                            |  |  |  |  |

| 40       | P40          | 0            | General purpose IO                            |  |  |  |  |

| 18       | SOT0         | G            | SOT output for UART 0                         |  |  |  |  |

| 40       | P41          | 0            | General purpose IO                            |  |  |  |  |

| 19       | SCK0         | G            | SCK input/output for UART 0                   |  |  |  |  |

| 200      | P42          | 0            | General purpose IO                            |  |  |  |  |

| 20       | SIN0         | G            | SIN input for UART 0                          |  |  |  |  |

| 04       | P43          | 0            | General purpose IO                            |  |  |  |  |

| 21       | SIN1         | G            | SIN input for UART 1                          |  |  |  |  |

| 00       | P44          | 0            | General purpose IO                            |  |  |  |  |

| 22       | SCK1         | G            | SCK input/output for UART 1                   |  |  |  |  |

| 24       | P45          |              | General purpose IO                            |  |  |  |  |

| 24       | 24 SOT1 G    |              | SOT output for UART 1                         |  |  |  |  |

| O.F.     | P46          |              | General purpose IO                            |  |  |  |  |

| ∠5       | 25 SOT2 G    |              | SOT output for the Serial IO                  |  |  |  |  |

| 26       | P47          |              | General purpose IO                            |  |  |  |  |

| 26       | SCK2         | G            | SCK input/output for the Serial IO            |  |  |  |  |

| Pin no.    | Pin name     | Circuit type | Function                                                                                         |

|------------|--------------|--------------|--------------------------------------------------------------------------------------------------|

| 76         | P92          | D            | General purpose IO                                                                               |

| 76         | INT0         |              | External interrupt input for INT0                                                                |

| 78 to 80   | P93 to P95   | D            | General purpose IO                                                                               |

| 78 10 80   | INT1 to INT3 | D            | External interrupt input for INT1 to INT3                                                        |

| 58, 68     | DVcc         | _            | Dedicated power supply pins for the high current output buffers (Pin No. 54 to 72)               |

| 53, 63, 73 | DVss         | _            | Dedicated ground pins for the high current output buffers (Pin No. 54 to 72)                     |

| 34         | AVcc         | Power supply | Dedicated power supply pin for the A/D Converter                                                 |

| 37         | AVss         | Power supply | Dedicated ground pin for the A/D Converter                                                       |

| 35         | AVRH         | Power supply | Upper reference voltage input for the A/D Converter                                              |

| 36         | AVRL         | Power supply | Lower reference voltage input for the A/D Converter                                              |

| 49, 50     | MD0<br>MD1   | С            | Operating mode selection input pins. These pins should be connected to Vcc or Vss.               |

| 51         | MD2          | Н            | Operating mode selection input pin. This pin should be connected to Vcc or Vss.                  |

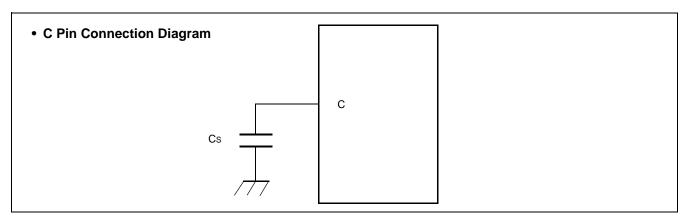

| 27         | С            | _            | External capacitor pin. A capacitor of $0.1\mu\text{F}$ should be connected to this pin and Vss. |

| 23, 84     | Vcc          | Power supply | Power supply pins (5.0 V).                                                                       |

| 11, 42, 81 | Vss          | Power supply | Ground pins (0.0 V).                                                                             |

# 4. I/O Circuit Type

### (5) Pull-up/down resistors

The MB90595G Series does not support internal pull-up/down resistors. Use external components where needed.

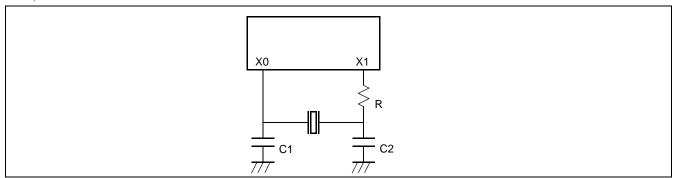

### (6) Crystal Oscillator Circuit

Noises around X0 or X1 pins may cause abnormal operations. Make sure to provide bypass capacitors via shortest distance from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure that lines of oscillation circuit not cross the lines of other circuits.

A printed circuit board artwork surrounding the X0 and X1 pins with ground area for stabilizing the operation is highly recommended.

### (7) Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

Make sure to turn on the A/D converter power supply (AVcc, AVRH, AVRL) and analog inputs (AN0 to AN7) after turning-on the digital power supply (Vcc).

Turn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure that the voltage does not exceed AVRH or AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

### (8) Connection of Unused Pins of A/D Converter

Connect unused pins of A/D converter to AVcc = Vcc, AVss = AVRH = DVcc = Vss.

#### (9) N.C. Pin

The N.C. (internally connected) pin must be opened for use.

#### (10) Notes on Energization

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at  $50 \mu s$  or more (0.2 V to 2.7 V).

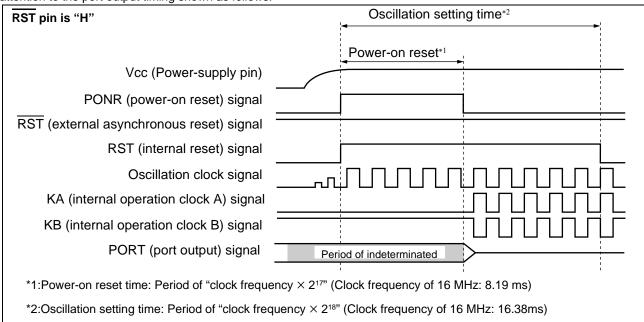

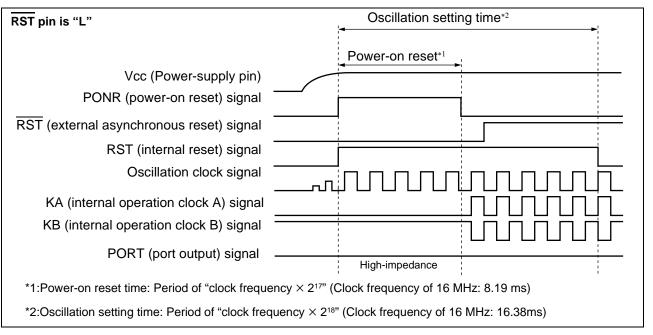

## (11) Indeterminate outputs from ports 0 and 1 (MB90V595G only)

During oscillation setting time of step-down circuit (during a power-on reset) after the power is turned on, the outputs from ports 0 and 1 become following state.

- If RST pin is "H", the outputs become indeterminate.

- If RST pin is "L", the outputs become high-impedance. Pay attention to the port output timing shown as follows.

### (12) Initialization

The device contains internal registers which are initialized only by a power-on reset. To initialize these registers, please turn on the power again.

### (13) Directions of "DIV A, Ri" and "DIVW A, RWi" instructions

In the signed multiplication and division instructions ("DIV A, Ri" and "DIVW A, RWi"), the value of the corresponding bank register (DTB, ADB, USB, SSB) is set in "00H".

If the values of the corresponding bank register (DTB,ADB,USB,SSB) are set to other than "00<sub>H</sub>", the remainder by the execution result of the instruction is not stored in the register of the instruction operand.

### (14) Using REALOS

The use of El<sup>2</sup>OS is not possible with the REALOS real time operating system.

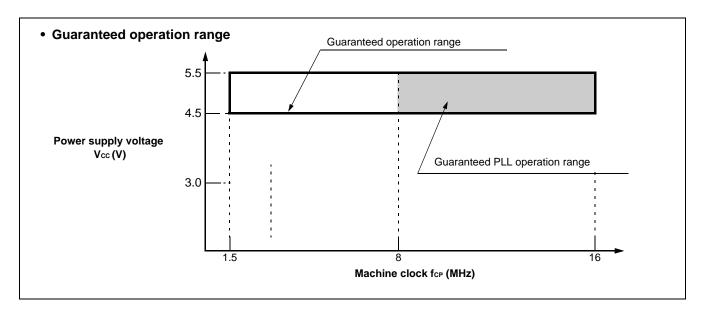

## (15) Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected in the microcontroller, it may attempt to continue the operation using the free-running frequency of the automatic oscillating circuit in the PLL circuitry even if the oscillator is out of place or the clock input is stopped. Performance of this operation, however, cannot be guaranteed.

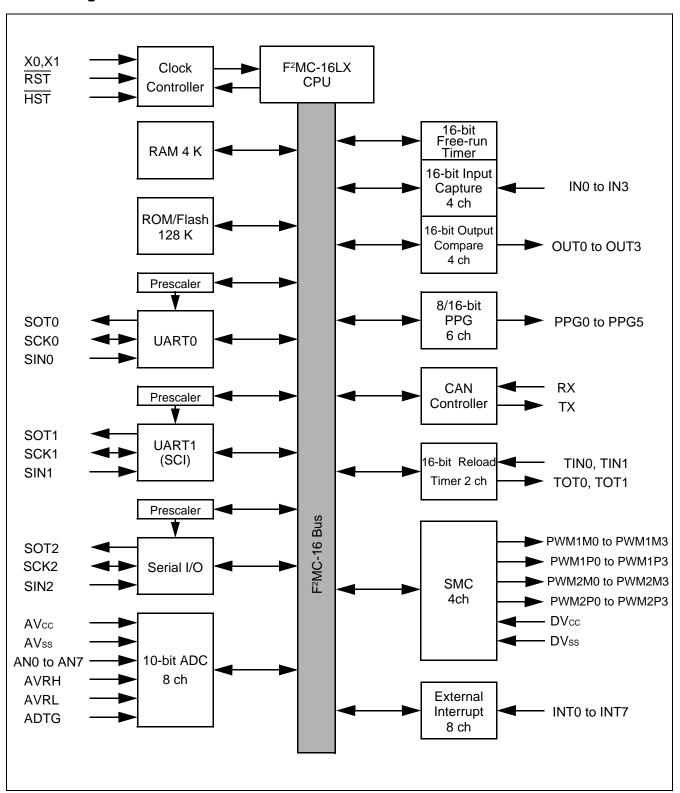

## 6. Block Diagram

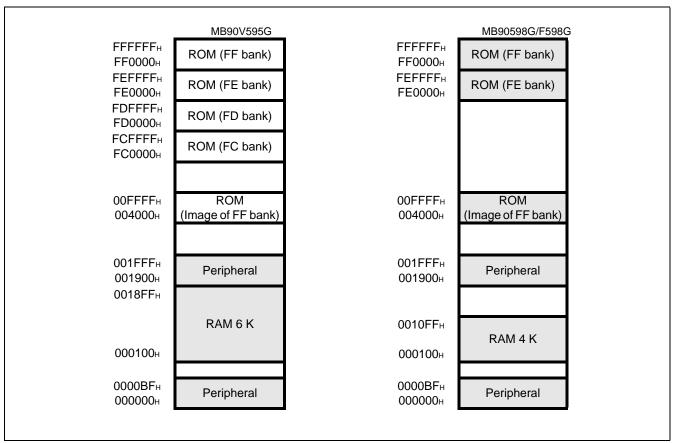

## 7. Memory Space

The memory space of the MB90595G Series is shown below

Figure 1. Memory space map

Note: The ROM data of bank FF is reflected in the upper address of bank 00, realizing effective use of the C compiler small model. The lower 16-bit of bank FF and the lower 16-bit of bank 00 are assigned to the same address, enabling reference of the table on the ROM without stating "far".

For example, if an attempt has been made to access 00C000H, the contents of the ROM at FFC000H are accessed. Since the ROM area of the FF bank exceeds 48 Kbytes, the whole area cannot be reflected in the image for the 00 bank. The ROM data at FF4000H to FFFFFH looks, therefore, as if it were the image for 004000H to 00FFFFH. Thus, it is recommended that the ROM data table be stored in the area of FF4000H to FFFFFFH.

Document Number: 002-07700 Rev. \*A

# 8. I/O Map

| Address    | Register                            | Abbreviation | Access | Peripheral  | Initial value                |

|------------|-------------------------------------|--------------|--------|-------------|------------------------------|

| 00н        | Port 0 Data Register                | PDR0         | R/W    | Port 0      | XXXXXXXXB                    |

| 01н        | Port 1 Data Register                | PDR1         | R/W    | Port 1      | XXXXXXXXB                    |

| 02н        | Port 2 Data Register                | PDR2         | R/W    | Port 2      | XXXXXXXXB                    |

| 03н        | Port 3 Data Register                | PDR3         | R/W    | Port 3      | XXXXXXXXB                    |

| 04н        | Port 4 Data Register                | PDR4         | R/W    | Port 4      | XXXXXXXXB                    |

| 05н        | Port 5 Data Register                | PDR5         | R/W    | Port 5      | XXXXXXXXB                    |

| 06н        | Port 6 Data Register                | PDR6         | R/W    | Port 6      | XXXXXXXXB                    |

| 07н        | Port 7 Data Register                | PDR7         | R/W    | Port 7      | XXXXXXXXB                    |

| 08н        | Port 8 Data Register                | PDR8         | R/W    | Port 8      | XXXXXXXXB                    |

| 09н        | Port 9 Data Register                | PDR9         | R/W    | Port 9      | XXXXXXB                      |

| 0Ан to 0Fн |                                     | Reserv       | ed     |             | •                            |

| 10н        | Port 0 Direction Register           | DDR0         | R/W    | Port 0      | 0 0 0 0 0 0 0 0в             |

| 11н        | Port 1 Direction Register           | DDR1         | R/W    | Port 1      | 0 0 0 0 0 0 0 0в             |

| 12н        | Port 2 Direction Register           | DDR2         | R/W    | Port 2      | 0 0 0 0 0 0 0 0в             |

| 13н        | Port 3 Direction Register           | DDR3         | R/W    | Port 3      | 0 0 0 0 0 0 0 0в             |

| 14н        | Port 4 Direction Register           | DDR4         | R/W    | Port 4      | 0 0 0 0 0 0 0 0в             |

| 15н        | Port 5 Direction Register           | DDR5         | R/W    | Port 5      | 0 0 0 0 0 0 0 0в             |

| 16н        | Port 6 Direction Register           | DDR6         | R/W    | Port 6      | 0 0 0 0 0 0 0 0в             |

| 17н        | Port 7 Direction Register           | DDR7         | R/W    | Port 7      | 0 0 0 0 0 0 0 0в             |

| 18н        | Port 8 Direction Register           | DDR8         | R/W    | Port 8      | 0 0 0 0 0 0 0 0в             |

| 19н        | Port 9 Direction Register           | DDR9         | R/W    | Port 9      | 000000                       |

| 1Ан        |                                     | Reserv       | ed     |             |                              |

| 1Вн        | Analog Input Enable Register        | ADER         | R/W    | Port 6, A/D | 11111111                     |

| 1Сн to 1Fн |                                     | Reserv       | ed     |             |                              |

| 20н        | Serial Mode Control Register 0      | UMC0         | R/W    |             | 0 0 0 0 0 1 0 0в             |

| 21н        | Serial status Register 0            | USR0         | R/W    | UART0       | 0 0 0 1 0 0 0 0в             |

| 22н        | Serial Input/Output Data Register 0 | UIDR0/UODR0  | R/W    | UARTO       | XXXXXXXXB                    |

| 23н        | Rate and Data Register 0            | URD0         | R/W    |             | 0 0 0 0 0 0 0 X <sub>B</sub> |

| 24н        | Serial Mode Register 1              | SMR1         | R/W    |             | 0 0 0 0 0 0 0 0в             |

| 25н        | Serial Control Register 1           | SCR1         | R/W    |             | 0 0 0 0 0 1 0 0в             |

| 26н        | Serial Input/Output Data Register 1 | SIDR1/SODR1  | R/W    | UART1       | XXXXXXXXB                    |

| 27н        | Serial Status Register 1            | SSR1         | R/W    |             | 0 0 0 0 1 _ 0 Ов             |

| 28н        | UART1 Prescaler Control Register    | U1CDCR       | R/W    |             | 01111в                       |

(Continued)

| Address     | Register                                  | Abbreviation | Access | Peripheral                     | Initial value                |  |  |  |  |

|-------------|-------------------------------------------|--------------|--------|--------------------------------|------------------------------|--|--|--|--|

| 4Сн         | PPGA Operation Mode Control Register      | PPGCA        | R/W    | 16-bit                         | 0_0001в                      |  |  |  |  |

| 4Dн         | PPGB Operation Mode Control Register      | PPGCB        | R/W    | Programmable Pulse             | 0_00001в                     |  |  |  |  |

| 4Ен         | PPGA, B Output Pin Control Register       | PPGAB        | R/W    | Generator A/B                  | 0 0 0 0 0 0B                 |  |  |  |  |

| 4Fн         |                                           | Reserved     |        |                                |                              |  |  |  |  |

| 50н         | Timer Control Status Register 0           | TMCSR0       | R/W    |                                | 0 0 0 0 0 0 0 0в             |  |  |  |  |

| 51н         | Timer Control Status Register 0           | TMCSR0       | R/W    | 16-bit                         | 0000в                        |  |  |  |  |

| 52н         | Timer 0/Reload Register 0                 | TMR0/TMRLR0  | R/W    | Reload Timer 0                 | XXXXXXXXB                    |  |  |  |  |

| 53н         | Timer 0/Reload Register 0                 | TMR0/TMRLR0  | R/W    |                                | XXXXXXXX                     |  |  |  |  |

| 54н         | Timer Control Status Register 1           | TMCSR1       | R/W    |                                | 0 0 0 0 0 0 0 0 <sub>B</sub> |  |  |  |  |

| 55н         | Timer Control Status Register 1           | TMCSR1       | R/W    | 16-bit                         | 0000 <sub>B</sub>            |  |  |  |  |

| 56н         | Timer Register 1/Reload Register 1        | TMR1/TMRLR1  | R/W    | Reload Timer 1                 | XXXXXXXXB                    |  |  |  |  |

| 57н         | Timer Register 1/Reload Register 1        | TMR1/TMRLR1  | R/W    |                                | XXXXXXXXB                    |  |  |  |  |

| 58н         | Output Compare Control Status Register 0  | OCS0         | R/W    | Output                         | 0 0 0 0 0 0 <sub>B</sub>     |  |  |  |  |

| 59н         | Output Compare Control Status Register 1  | OCS1         | R/W    | Compare 0/1                    | 00000в                       |  |  |  |  |

| 5Ан         | Output Compare Control Status Register 2  | OCS2         | R/W    | Output                         | 0 0 0 0 0 Ов                 |  |  |  |  |

| 5Вн         | Output Compare Control Status Register 3  | OCS3         | R/W    | Compare 2/3                    | 00000 <sub>B</sub>           |  |  |  |  |

| 5Сн         | Input Capture Control Status Register 0/1 | ICS01        | R/W    | Input Capture 0/1              | 0 0 0 0 0 0 0 0 <sub>B</sub> |  |  |  |  |

| 5Dн         | Input Capture Control Status Register 2/3 | ICS23        | R/W    | Input Capture 2/3              | 0 0 0 0 0 0 0 0 В            |  |  |  |  |

| 5Ен         | PWM Control Register 0                    | PWC0         | R/W    | Stepping Motor<br>Controller 0 | 0 0 0 0 0 Ов                 |  |  |  |  |

| <b>5</b> Fн |                                           | Reserved     | •      |                                |                              |  |  |  |  |

| 60н         | PWM Control Register 1                    | PWC1         | R/W    | Stepping Motor<br>Controller 1 | 0 0 0 0 0 0в                 |  |  |  |  |

| 61н         |                                           | Reserved     |        |                                |                              |  |  |  |  |

| 62н         | PWM Control Register 2                    | PWC2         | R/W    | Stepping Motor<br>Controller 2 | 0 0 0 0 0 0в                 |  |  |  |  |

| 63н         |                                           |              |        |                                |                              |  |  |  |  |

| 64н         | PWM Control Register 3                    | PWC3         | R/W    | Stepping Motor<br>Controller 3 | 0 0 0 0 0 0в                 |  |  |  |  |

| 65н         | Reserved                                  |              |        |                                |                              |  |  |  |  |

| 66н         | Timer Data Register (low-order)           | TCDT         | R/W    |                                | 0 0 0 0 0 0 0 0 В            |  |  |  |  |

| 67н         | Timer Data Register (high-order)          | TCDT         | R/W    | 16-bit Free-run Timer          | 0 0 0 0 0 0 0 0 <sub>B</sub> |  |  |  |  |

| 68н         | Timer Control Status Register             | TCCS         | R/W    |                                | 0 0 0 0 0 0 0 0 <sub>B</sub> |  |  |  |  |

| 69н to 6Eн  | Reserved                                  |              |        |                                |                              |  |  |  |  |

| Address        | Register                                            | Abbreviation         | Access       | Peripheral         | Initial value |

|----------------|-----------------------------------------------------|----------------------|--------------|--------------------|---------------|

| 192Сн          | Output Compare Register 2 (low-order)               | OCCP2                | R/W          |                    | XXXXXXXX      |

| 192Dн          | Output Compare Register 2 (high-order)              | OCCP2                | R/W          | Output Compare 2/3 | XXXXXXXX      |

| 192Ен          | Output Compare Register 3 (low-order)               | OCCP3                | R/W          | Output Compare 2/3 | XXXXXXXX      |

| 192Fн          | Output Compare Register 3 (high-order)              | OCCP3                | R/W          |                    | XXXXXXXX      |

| 1930н to 19FFн |                                                     | Re                   | served       |                    |               |

| 1A00н to 1AFFн | CAN                                                 | Controller. Refer to | section abou | ut CAN Controller  |               |

| 1В00н to 1ВFFн | CAN                                                 | Controller. Refer to | section abou | ut CAN Controller  |               |

| 1С00н to 1EFFн |                                                     | Re                   | served       |                    |               |

| 1FF0н          | Program Address Detection Register 0 (low-order)    |                      |              |                    | XXXXXXXX      |

| 1FF1н          | Program Address Detection Register 0 (middle-order) | PADR0                | R/W          |                    | XXXXXXXXB     |

| 1FF2н          | Program Address Detection Register 0 (high-order)   |                      |              | Address Match      | XXXXXXXX      |

| 1FF3н          | Program Address Detection Register 1 (low-order)    |                      |              | Detection Function | XXXXXXXX      |

| 1FF4н          | Program Address Detection Register 1 (middle-order) | PADR1                | R/W          |                    | XXXXXXXXB     |

| 1FF5н          | Program Address Detection Register 1 (high-order)   |                      |              |                    | XXXXXXXXB     |

| 1FF6н to 1FFFн |                                                     | Re                   | served       |                    |               |

■ Description for Read/Write R/W : Readable/writable

R : Read only W : Write only

■ Description of initial value

0 : the initial value of this bit is "0".

1 : the initial value of this bit is "1".

X: the initial value of this bit is undefined.

\_ : this bit is unused. the initial value is undefined.

Note: : Addresses in the range of 0000<sub>H</sub> to 00FF<sub>H</sub>, which are not listed in the table, are reserved for the primary functions of the MCU. A read access to these reserved addresses results in reading "X", and any write access should not be performed.

| Address | Register                               | Abbreviation | Access | Initial Value                           |  |

|---------|----------------------------------------|--------------|--------|-----------------------------------------|--|

| 001В08н | - IDE register                         | IDER         | R/W    | XXXXXXX XXXXXXXX                        |  |

| 001В09н | TDE register                           | IDEN         | TX/VV  | XXXXXXXX XXXXXXXX                       |  |

| 001В0Ан | Transmit RTR register                  | TRTRR        | R/W    | 0000000 00000000                        |  |

| 001В0Вн | Transmit ix rix register               | TIVITAL      | TX/VV  | 0000000 0000000в                        |  |

| 001В0Сн | Remote frame receive waiting register  | RFWTR        | R/W    | XXXXXXX XXXXXXX                         |  |

| 001В0Dн | Tremote frame receive waiting register | IXI VVIIX    | TX/VV  | XXXXXXXX XXXXXXXX                       |  |

| 001В0Ен | Transmit interrupt enable register     | TIER         | R/W    | 00000000 00000000В                      |  |

| 001В0Гн | Transmit interrupt enable register     | HEK          | IX/VV  | 00000000 00000000                       |  |

| 001В10н |                                        |              |        | XXXXXXX XXXXXXX                         |  |

| 001В11н | Acceptance mask select register        | AMSR         | R/W    | 700000000000000000000000000000000000000 |  |

| 001В12н | Acceptance mask select register        |              | IX/VV  | XXXXXXX XXXXXXXX                        |  |

| 001В13н |                                        |              |        | AAAAAAAA AAAAAAAA                       |  |

| 001В14н |                                        |              |        | XXXXXXX XXXXXXX                         |  |

| 001В15н | Acceptance mask register 0             | AMR0         | R/W    | **************************************  |  |

| 001В16н | Acceptance mask register 0             | AIVIRU       | K/VV   | XXXXX XXXXXXXXB                         |  |

| 001В17н |                                        |              |        | **************************************  |  |

| 001В18н |                                        |              |        | XXXXXXX XXXXXXX                         |  |

| 001В19н | Acceptance mask register 1             | AMR1         | R/W    | AAAAAAA AAAAAAAA                        |  |

| 001В1Ан | Acceptance mask register 1             | AIVIK I      | IK/VV  | VVVVV VVVVVVV                           |  |

| 001В1Вн |                                        |              |        | XXXXX XXXXXXXXB                         |  |

# 9.2 List of Message Buffers (ID Registers)

| Address                  | Register            | Abbreviation | Access | Initial Value                          |

|--------------------------|---------------------|--------------|--------|----------------------------------------|

| 001A00н<br>to<br>001A1Fн | General-purpose RAM |              | R/W    | XXXXXXXB<br>to<br>XXXXXXXXB            |

| 001А20н                  |                     |              |        | XXXXXXX XXXXXXXB                       |

| 001А21н                  | ID register 0       | IDR0         | R/W    | ^^^^^^                                 |

| 001А22н                  | Tib Tegister 0      | IDKU         | IX/VV  | XXXXX XXXXXXXXB                        |

| 001А23н                  |                     |              |        | VVVV VVVVVVV                           |

| 001А24н                  |                     |              |        | XXXXXXX XXXXXXXB                       |

| 001А25н                  | ID register 1       | IDR1         | R/W    | ************************************** |

| 001А26н                  | To register 1       |              | IX/VV  | XXXXX XXXXXXXX <sub>B</sub>            |

| 001А27н                  |                     |              |        | XXXX XXXXXXXB                          |

| 001А28н                  |                     |              |        | XXXXXXX XXXXXXXB                       |

| 001А29н                  | ID register 2       | IDR2         | R/W    | AAAAAAAAAAAAAAA                        |

| 001А2Ан                  | To register 2       | IDNZ         | 17/ // | XXXXX XXXXXXXX <sub>B</sub>            |

| 001А2Вн                  |                     |              |        | VVVVV VVVVVVV                          |

| Address | Register         | Abbreviation | Access | Initial Value                          |  |  |

|---------|------------------|--------------|--------|----------------------------------------|--|--|

| 001А40н |                  |              |        |                                        |  |  |

| 001А41н | IB verietes 0    | IDDs         | DAM    | XXXXXXXX XXXXXXXXB                     |  |  |

| 001А42н | ID register 8    | IDR8         | R/W    | VVVV VVVVVV                            |  |  |

| 001А43н |                  |              |        | XXXXX XXXXXXXXB                        |  |  |

| 001А44н |                  |              |        | · · · · · · · · · · · · · · · · · · ·  |  |  |

| 001А45н | ID register 0    | IDDO         | D/M    | XXXXXXX XXXXXXXXB                      |  |  |

| 001А46н | ID register 9    | IDR9         | R/W    | VVVV VVVVVV                            |  |  |

| 001А47н |                  |              |        | XXXXX XXXXXXXXB                        |  |  |

| 001А48н |                  |              |        | · · · · · · · · · · · · · · · · · · ·  |  |  |

| 001А49н | ID register 10   | IDR10        | R/W    | XXXXXXX XXXXXXXXB                      |  |  |

| 001А4Ан | - ID register 10 | IDRIU        | K/VV   | VVVV VVVVVV-                           |  |  |

| 001А4Вн |                  |              |        | XXXXX XXXXXXXXB                        |  |  |

| 001А4Сн |                  |              |        | XXXXXXX XXXXXXX                        |  |  |

| 001А4Dн | ID register 11   | IDR11        | R/W    | WWWWWWWWW                              |  |  |

| 001А4Ен | ID register 11   | IDKII        | R/VV   | XXXXX XXXXXXXXB                        |  |  |

| 001А4Гн |                  |              |        | VVVV VVVVVVV                           |  |  |

| 001А50н |                  |              |        | XXXXXXX XXXXXXX                        |  |  |

| 001А51н | ID register 12   | IDR12        | R/W    |                                        |  |  |

| 001А52н | To register 12   |              | 10,00  | XXXXX XXXXXXXXB                        |  |  |

| 001А53н |                  |              |        | XXXX XXXXXXXB                          |  |  |

| 001А54н |                  |              |        | XXXXXXXX XXXXXXXX                      |  |  |

| 001А55н | ID register 13   | IDR13        | R/W    | AAAAAAAAAAAAAA                         |  |  |

| 001А56н | Togister 10      | IDICIO       | 10,00  | XXXXX XXXXXXXXB                        |  |  |

| 001А57н |                  |              |        | WWW WWWWW                              |  |  |

| 001А58н |                  |              |        | XXXXXXX XXXXXXX                        |  |  |

| 001А59н | ID register 14   | IDR14        | R/W    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  |  |

| 001А5Ан |                  | ISIN I       | 1.7/44 | XXXXX XXXXXXXXB                        |  |  |

| 001А5Вн |                  |              |        | 70000 7000000B                         |  |  |

| 001А5Сн |                  |              |        | XXXXXXX XXXXXXXX                       |  |  |

| 001А5Дн | ID register 15   | IDR15        | R/W    | 70000007000000000000000000000000000000 |  |  |

| 001А5Ен | 15 15910101 10   | IDI(10       | 13,77  | XXXXX XXXXXXXXB                        |  |  |

| 001А5Гн |                  |              |        | ^^^^^-                                 |  |  |

### Notes:

- For a peripheral module with two interrupt for a single interrupt number, both interrupt request flags are cleared by the El²OS interrupt clear signal.

- At the end of El²OS, the El²OS clear signal will be asserted for all the interrupt flags assigned to the same interrupt number. If one interrupt flag starts the El²OS and in the meantime another interrupt flag is set by hardware event, the later event is lost because the flag is cleared by the El²OS clear signal caused by the first event. So it is recommended not to use the El²OS for this interrupt number.

- If El²OS is enabled, El²OS is initiated when one of the two interrupt signals in the same interrupt control register (ICR) is asserted. This means that different interrupt sources share the same El²OS Descriptor which should be unique for each interrupt source. For this reason, when one interrupt source uses the El²OS, the other interrupt should be disabled.

Document Number: 002-07700 Rev. \*A Page 30 of 51

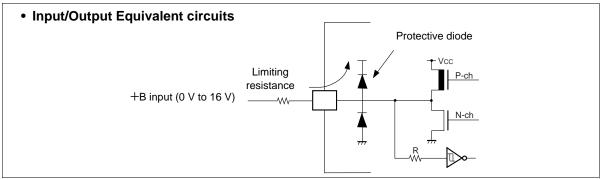

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller current is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on result.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits :

Note: : Average output current = operating current × operating efficiency

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

Document Number: 002-07700 Rev. \*A Page 32 of 51

### 11.2 Recommended Conditions

(Vss = AVss = 0.0 V)

| , I I I I I I I I I I I I I I I I I I I |          |       |     |     |       |                                 |  |  |  |

|-----------------------------------------|----------|-------|-----|-----|-------|---------------------------------|--|--|--|

| Parameter                               | Symbol   | Value |     |     | Unit  | Remarks                         |  |  |  |

| raiametei                               | Syllibol | Min   | Тур | Max | Oiiit | Kemarks                         |  |  |  |

| Power supply voltage                    | Vcc      | 4.5   | 5.0 | 5.5 | V     | Under normal operation          |  |  |  |

| Fower supply voltage                    | AVcc     | 3.0   | _   | 5.5 | V     | Maintains RAM data in stop mode |  |  |  |

| Smooth capacitor                        | Cs       | 0.022 | 0.1 | 1.0 | μF    | *                               |  |  |  |

| Operating temperature                   | TA       | -40   | _   | +85 | °C    |                                 |  |  |  |

<sup>\*:</sup> Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The smoothing capacitor to be connected to the Vcc pin must have a capacitance value higher than Cs.

WARNING:

The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

## 11.3 DC Characteristics

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 ^{\circ}C to +85 ^{\circ}C)$

| Parameter           | Symbol           | Pin name                      | Condition                                              | Value     |     |          | Unit  | Remarks |

|---------------------|------------------|-------------------------------|--------------------------------------------------------|-----------|-----|----------|-------|---------|

| raiametei           | Symbol           | riii name                     | Condition                                              | Min       | Тур | Max      | Offic | Remarks |

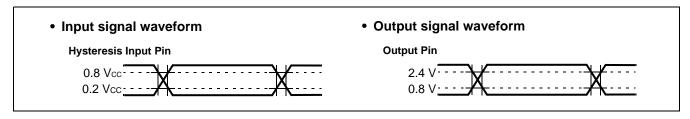

| Input H voltage     | VIHS             | CMOS hysteresis input pin     |                                                        | 0.8 Vcc   | _   | Vcc+0.3  | V     |         |

|                     | V <sub>IHM</sub> | MD input pin                  | _                                                      | Vcc - 0.3 | _   | Vcc +0.3 | V     |         |

| Input L voltage     | VILS             | CMOS hysteresis input pin     |                                                        | Vss - 0.3 | _   | 0.2 Vcc  | V     |         |

|                     | VILM             | MD input pin                  |                                                        | Vss - 0.3 | _   | Vss +0.3 | ٧     |         |

| Output H            | V <sub>OH1</sub> | Output pins except P70 to P87 | $V_{CC} = 4.5 \text{ V},$ $I_{OH1} = -4.0 \text{ mA}$  | Vcc - 0.5 | _   | -        | ٧     |         |

| voltage             | V <sub>OH2</sub> | P70 to P87                    | $V_{CC} = 4.5 \text{ V},$ $I_{OH2} = -30.0 \text{ mA}$ | Vcc - 0.5 | _   |          | ٧     |         |

| Output L<br>voltage | V <sub>OL1</sub> | Output pins except P70 to P87 | $Vcc = 4.5 \text{ V},$ $Io_{L1} = 4.0 \text{ mA}$      | _         | _   | 0.4      | V     |         |

|                     | V <sub>OL2</sub> | P70 to P87                    | Vcc = 4.5 V,<br>IoL2 = 30.0 mA                         | _         | _   | 0.5      | V     |         |

(Vcc = 5.0 V

$$\pm$$

10%, Vss = AVss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

| Parameter            | Symbol                                                                 | Pin name     | Condition |     | Value | Unit | Remarks |         |

|----------------------|------------------------------------------------------------------------|--------------|-----------|-----|-------|------|---------|---------|

| Farameter            | Syllibol                                                               | Fili lialile | Condition | Min | Тур   | Max  | Ollit   | Kemarks |

| Input capacity       | Other than C, AVcc, AVss, AVRH, AVRL, Vcc, Vss, DVcc, DVss, P70 to P87 |              | _         | _   | 5     | 15   | pF      |         |

|                      |                                                                        | P70 to P87   | _         | _   | 15    | 30   | pF      |         |

| Pull-up resistance   | Rup                                                                    | RST          | _         | 25  | 50    | 100  | kΩ      |         |

| Pull-down resistance | RDOWN                                                                  | MD2          | <u> </u>  | 25  | 50    | 100  | kΩ      |         |

<sup>\*:</sup> The power supply current testing conditions are when using the external clock.

## 11.4 AC Characteristics

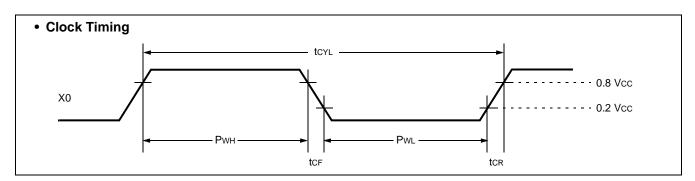

## 11.4.1 Clock Timing

(Vcc = 5.0 V±10%, Vss = AVss = 0.0 V, Ta = -40

$$^{\circ}\text{C}$$

to +85  $^{\circ}\text{C})$

| Parameter                      | Symbol      | Pin name | Value |       |     | Unit | Remarks                        |

|--------------------------------|-------------|----------|-------|-------|-----|------|--------------------------------|

| Parameter                      | Syllibol    |          | Min   | Тур   | Max | Onit | Remarks                        |

| Oscillation frequency          | fc          | X0, X1   | 3     | _     | 5   | MHz  | When using oscillation circuit |

| Oscillation cycle time         | tcyL        | X0, X1   | 200   | _     | 333 | ns   | When using oscillation circuit |

| External clock frequency       | fc          | X0, X1   | 3     | _     | 16  | MHz  | When using external clock      |

| External clock cycle time      | tcyL        | X0, X1   | 62.5  | _     | 333 | ns   | When using external clock      |

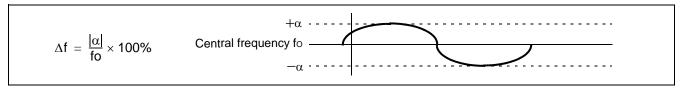

| Frequency deviation with PLL * | Δf          | _        | _     | _     | 5   | %    |                                |

| Input clock pulse width        | Pwh, PwL    | X0       | 10    | _     | _   | ns   | Duty ratio is about 30 to 70%. |

| Input clock rise and fall time | tcr, tcr    | X0       | _     | _     | 5   | ns   | When using external clock      |

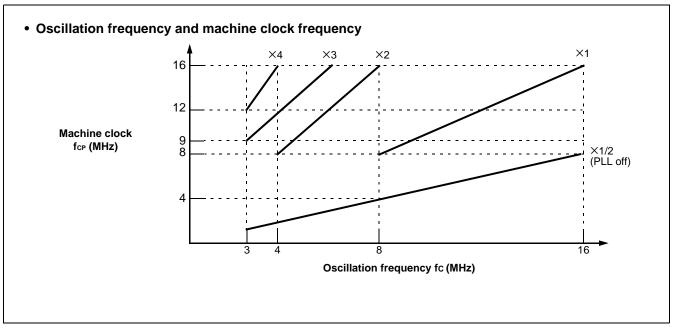

| Machine clock frequency        | fcp         | _        | 1.5   | _     | 16  | MHz  |                                |

| Machine clock cycle time       | <b>t</b> CP | _        | 62.5  | _     | 666 | ns   |                                |

| Flash Read cycle time          | tcyL        | _        | _     | 2*tcp | _   | ns   | When Flash is accessed via CPU |

<sup>\*:</sup> Frequency deviation indicates the maximum frequency difference from the target frequency when using a multiplied clock.

## ■ Example of Oscillation circuit

AC characteristics are set to the measured reference voltage values below.

## 11.4.2 Reset and Hardware Standby Input

| $(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40$ | °C to +85 | °C) |

|--------------------------------------------------------|-----------|-----|

|--------------------------------------------------------|-----------|-----|

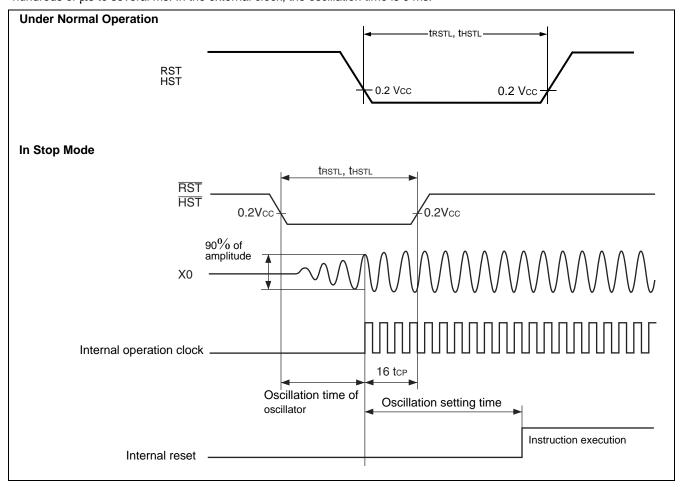

| Parameter                   | Symbol                   | Pin name     | Value                                       |     | Unit  | Remarks                |  |

|-----------------------------|--------------------------|--------------|---------------------------------------------|-----|-------|------------------------|--|

| r ai ailletei               | Symbol                   | riii iiaiiie | Min                                         | Max | Oilit |                        |  |

|                             |                          |              | 16 tcp*1                                    |     | ns    | Under normal operation |  |

| Reset input time            | <b>t</b> rstl            | RST          | Oscillation time of oscillator*2 + 16 tcp*1 | _   | ms    | In stop mode           |  |

|                             | standby input time thstl | HST          | 16 tcp*1                                    | _   | ns    | Under normal operation |  |

| Hardware standby input time |                          |              | Oscillation time of oscillator*2 + 16 tcp*1 | _   | ms    | In stop mode           |  |

<sup>\*1: &</sup>quot;t<sub>cp</sub>" represents one cycle time of the machine clock.No reset can fully initialize the Flash Memory if it is performing the automatic algorithm.

\*2: Oscillation time of oscillator is time that the amplitude reached the 90%.

In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

# 15. Major Changes

**Spansion Publication Number: DS07-13705-7E**

| Section                                          | Change Results                                                                                                   |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| _                                                | Deleted the old products, MB90598, MB90F598, and MB90V595.                                                       |

| _                                                | Changed the series name;<br>MB90595/595G series ? MB90595G series                                                |

| _                                                | Changed the following erroneous name. I/O timer → 16-bit Free-run Timer                                          |

| PRODUCT LINEUP                                   | One of Standby mode name is changed. Clock mode → Watch mode                                                     |

| I/O CIRCUIT TYPE                                 | Changed Pull-down resistor value of circuit type H.                                                              |

| ELECTRICAL CHARACTERISTICS<br>AC Characteristics | Add the "External clock input" and "Flash Read cycle time" in (1) Clock Timing                                   |

|                                                  | Figure in (2) Reset and Hardware Standby Input RST/HST input level of "In Stop Mode" is changed. 0.6 Vcc 0.2 Vcc |

| ELECTRICAL CHARACTERISTICS 5. A/D Converter      | Changed the items of "Zero transition voltage" and "Full scale transition voltage".                              |

NOTE: Please see "Document History" about later revised information.

# **Document History**

| Document Title: MB90598G/F598G/V595G F <sup>2</sup> MC-16LX MB90595G Series CMOS 16-bit Proprietary Microcontroller Document Number: 002-07700 |         |                    |                    |                                                                                                          |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Revision                                                                                                                                       | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |  |  |  |

| **                                                                                                                                             | _       | AKIH               | 09/26/2008         | Migrated to Cypress and assigned document number 002-07700.<br>No change to document contents or format. |  |  |  |

| *A                                                                                                                                             | 5537128 | AKIH               | 11/30/2016         | Updated to Cypress template                                                                              |  |  |  |

Document Number: 002-07700 Rev. \*A Page 50 of 51