Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | F <sup>2</sup> MC-16LX                                                        |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                                  |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 78                                                                            |

| Program Memory Size        | 128KB (128K x 8)                                                              |

| Program Memory Type        | Mask ROM                                                                      |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                   |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-BQFP                                                                      |

| Supplier Device Package    | 100-QFP (14x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90598gpf-g-187e1 |

| Features                               | MB90598G                                                                                                                                                                                                                                                                                                                                                                                                                                | MB90F598G                                                                                                                                                                                                               | MB90V595G |  |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

| CAN Interface                          | Number of channels: 1 Conforms to CAN Specification Version 2.0 Part A and B Automatic re-transmission in case of error Automatic transmission responding to Remote Frame Prioritized 16 message buffers for data and ID's Supports multiple messages Flexible configuration of acceptance filtering: Full bit compare / Full bit mask / Two partial bit masks Supports up to 1Mbps CAN bit timing setting: MB90598G/F598G:TSEG2 ≥ RSJW |                                                                                                                                                                                                                         |           |  |  |  |  |

| Stepping motor controller (4 channels) | Four high current outputs for each channel Synchronized two 8-bit PWM's for each channel                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                         |           |  |  |  |  |

| External interrupt circuit             | Number of inputs: 8<br>Started by a rising edge, a falling edge, an "H" le                                                                                                                                                                                                                                                                                                                                                              | evel input, or an "L" level input.                                                                                                                                                                                      |           |  |  |  |  |

| Serial IO                              |                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clock synchronized transmission (31.25 K/62.5 K/125 K/500 K/1 Mbps at system clock frequency of 16 MHz)  SB first/MSB first                                                                                             |           |  |  |  |  |

| Watchdog timer                         | Reset generation interval: 3.58 ms, 14.33 ms, 57 (at oscillation of 4 MHz, minimum value)                                                                                                                                                                                                                                                                                                                                               | 7.23 ms, 458.75 ms                                                                                                                                                                                                      |           |  |  |  |  |

| Flash Memory                           | Write/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Hard-wired reset vector available in order to poir Memory Boot block configuration Erase can be performed on each block                                                                                                                                                                                                                         | Hard-wired reset vector available in order to point to a fixed boot sector in Flash<br>Memory<br>Boot block configuration<br>Erase can be performed on each block<br>Block protection with external programming voltage |           |  |  |  |  |

| Low-power consumption (stand-by) mode  | Sleep/stop/CPU intermittent operation/watch timer/hardware stand-by                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                         |           |  |  |  |  |

| Process                                |                                                                                                                                                                                                                                                                                                                                                                                                                                         | CMOS                                                                                                                                                                                                                    |           |  |  |  |  |

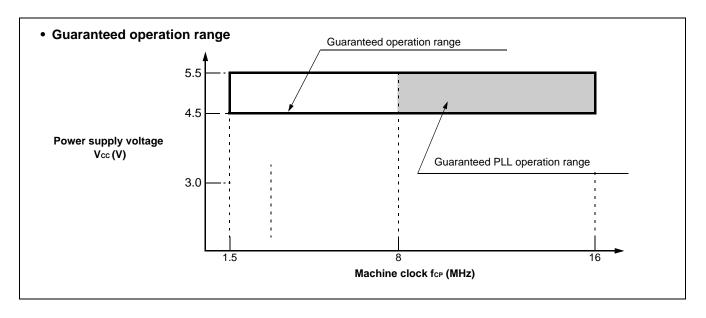

| Power supply voltage for operation*2   | +5 V±10 %                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                         |           |  |  |  |  |

| Package                                | QFP-100                                                                                                                                                                                                                                                                                                                                                                                                                                 | QFP-100 PGA-256                                                                                                                                                                                                         |           |  |  |  |  |

<sup>\*1:</sup> It is setting of DIP switch S2 when Emulation pod (MB2145-507) is used.

Please refer to the MB2145-507 hardware manual (2.7 Emulator-specific Power Pin) about details.

<sup>\*2:</sup> Varies with conditions such as the operating frequency. (See "Electrical Characteristics.")

## 3. Pin Description

| Pin no.  | Pin name     | Circuit type | Function                                      |  |  |  |

|----------|--------------|--------------|-----------------------------------------------|--|--|--|

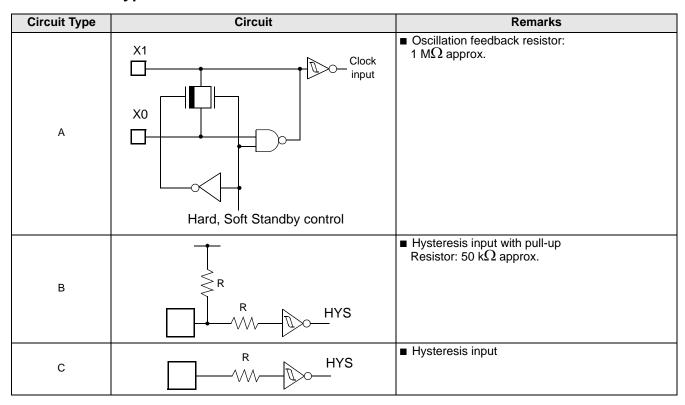

| 82       | X0           |              |                                               |  |  |  |

| 83       | X1           | А            | Oscillator pin                                |  |  |  |

| 77       | RST          | В            | Reset input                                   |  |  |  |

| 52       | HST          | С            | Hardware standby input                        |  |  |  |

| 05 to 00 | P00 to P03   | 0            | General purpose IO                            |  |  |  |

| 85 to 88 | IN0 to IN3   | G            | Inputs for the Input Captures                 |  |  |  |

| 89 to 92 | P04 to P07   | 0            | General purpose IO                            |  |  |  |

| 89 10 92 | OUT0 to OUT3 | G            | Outputs for the Output Compares.              |  |  |  |

| 00 to 00 | P10 to P15   | 5            | General purpose IO                            |  |  |  |

| 93 to 98 | PPG0 to PPG5 | D            | Outputs for the Programmable Pulse Generators |  |  |  |

| 00       | P16          | 5            | General purpose IO                            |  |  |  |

| 99       | TIN1         | D            | TIN input for the 16-bit Reload Timer 1       |  |  |  |

| 400      | P17          | 5            | General purpose IO                            |  |  |  |

| 100      | TOT1         | D            | TOT output for the 16-bit Reload Timer 1      |  |  |  |

| 1 to 8   | P20 to P27   | G            | General purpose IO                            |  |  |  |

| 9 to 10  | P30 to P31   | G            | General purpose IO                            |  |  |  |

| 12 to 16 | P32 to P36   | G            | General purpose IO                            |  |  |  |

| 17       | P37          | D            | General purpose IO                            |  |  |  |

| 40       | P40          | 0            | General purpose IO                            |  |  |  |

| 18       | SOT0         | G            | SOT output for UART 0                         |  |  |  |

| 40       | P41          | 0            | General purpose IO                            |  |  |  |

| 19       | SCK0         | G            | SCK input/output for UART 0                   |  |  |  |

| 200      | P42          | 0            | General purpose IO                            |  |  |  |

| 20       | SIN0         | G            | SIN input for UART 0                          |  |  |  |

| 04       | P43          | 0            | General purpose IO                            |  |  |  |

| 21       | SIN1         | G            | SIN input for UART 1                          |  |  |  |

| 00       | P44          | 0            | General purpose IO                            |  |  |  |

| 22       | SCK1         | G            | SCK input/output for UART 1                   |  |  |  |

| 0.4      | P45          | 0            | General purpose IO                            |  |  |  |

| 24       | SOT1         | G            | SOT output for UART 1                         |  |  |  |

| 25       | P46          |              | General purpose IO                            |  |  |  |

| 25       | SOT2         | G            | SOT output for the Serial IO                  |  |  |  |

| 26       | P47          |              | General purpose IO                            |  |  |  |

| 26       | SCK2         | G            | SCK input/output for the Serial IO            |  |  |  |

| Pin no.                                       | Pin name                             | Circuit type | Function                                            |  |  |

|-----------------------------------------------|--------------------------------------|--------------|-----------------------------------------------------|--|--|

| 00                                            | P50                                  | Г.           | General purpose IO                                  |  |  |

| 28                                            | SIN2                                 | D            | SIN Input for the Serial IO                         |  |  |

| 00.100                                        | P51 to P54                           | 1            | General purpose IO                                  |  |  |

| 29 to 32                                      | INT4 to INT7                         | D            | External interrupt input for INT4 to INT7           |  |  |

| 20                                            | P55                                  | <u> </u>     | General purpose IO                                  |  |  |

| 33                                            | ADTG                                 | D            | Input for the external trigger of the A/D Converter |  |  |

| 20 to 44                                      | P60 to P63                           |              | General purpose IO                                  |  |  |

| 38 to 41                                      | AN0 to AN3                           | E            | Inputs for the A/D Converter                        |  |  |

| 40.1- 40                                      | P64 to P67                           |              | General purpose IO                                  |  |  |

| 43 to 46                                      | AN4 to AN7                           | E            | Inputs for the A/D Converter                        |  |  |

| 47                                            | P56                                  | 2            | General purpose IO                                  |  |  |

| 47                                            | TIN0                                 | D            | TIN input for the 16-bit Reload Timer 0             |  |  |

| 40                                            | P57                                  | 2            | General purpose IO                                  |  |  |

| 48                                            | TOT0                                 | D            | TOT output for the 16-bit Reload Timer 0            |  |  |

|                                               | P70 to P73                           |              | General purpose IO                                  |  |  |

| 54 to 57 PWM1P0<br>PWM1M0<br>PWM2P0<br>PWM2M0 |                                      | F            | Output for Stepper Motor Controller channel 0       |  |  |

|                                               | P74 to P77                           |              | General purpose IO                                  |  |  |

| 59 to 62                                      | PWM1P1<br>PWM1M1<br>PWM2P1<br>PWM2M1 | F            | Output for Stepper Motor Controller channel 1       |  |  |

|                                               | P80 to P83                           |              | General purpose IO                                  |  |  |

| 64 to 67                                      | PWM1P2<br>PWM1M2<br>PWM2P2<br>PWM2M2 | F            | Output for Stepper Motor Controller channel 2       |  |  |

|                                               | P84 to P87                           |              | General purpose IO                                  |  |  |

| 69 to 72                                      | PWM1P3<br>PWM1M3<br>PWM2P3<br>PWM2M3 | F            | Output for Stepper Motor Controller channel 3       |  |  |

| 7.4                                           | P90                                  | D            | General purpose IO                                  |  |  |

| 74                                            | TX                                   | D            | TX output for CAN Interface                         |  |  |

| 75                                            | P91                                  | r.           | General purpose IO                                  |  |  |

| 75                                            | RX                                   | D            | RX input for CAN Interface                          |  |  |

| Pin no.    | Pin name     | Circuit type | Function                                                                                         |  |  |  |  |

|------------|--------------|--------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| 76         | P92          | D            | General purpose IO                                                                               |  |  |  |  |

| 76         | INTO         |              | External interrupt input for INT0                                                                |  |  |  |  |

| 78 to 80   | P93 to P95   | D            | General purpose IO                                                                               |  |  |  |  |

| 78 10 80   | INT1 to INT3 | D            | External interrupt input for INT1 to INT3                                                        |  |  |  |  |

| 58, 68     | DVcc         | _            | Dedicated power supply pins for the high current output buffers (Pin No. 54 to 72)               |  |  |  |  |

| 53, 63, 73 | DVss         | _            | Dedicated ground pins for the high current output buffers (Pin No. 54 to 72)                     |  |  |  |  |

| 34         | AVcc         | Power supply | Dedicated power supply pin for the A/D Converter                                                 |  |  |  |  |

| 37         | AVss         | Power supply | Dedicated ground pin for the A/D Converter                                                       |  |  |  |  |

| 35         | AVRH         | Power supply | Upper reference voltage input for the A/D Converter                                              |  |  |  |  |

| 36         | AVRL         | Power supply | Lower reference voltage input for the A/D Converter                                              |  |  |  |  |

| 49, 50     | MD0<br>MD1   | С            | Operating mode selection input pins. These pins should be connected to Vcc or Vss.               |  |  |  |  |

| 51         | MD2          | Н            | Operating mode selection input pin. This pin should be connected to Vcc or Vss.                  |  |  |  |  |

| 27         | С            | _            | External capacitor pin. A capacitor of $0.1\mu\text{F}$ should be connected to this pin and Vss. |  |  |  |  |

| 23, 84     | Vcc          | Power supply | Power supply pins (5.0 V).                                                                       |  |  |  |  |

| 11, 42, 81 | Vss          | Power supply | Ground pins (0.0 V).                                                                             |  |  |  |  |

## 4. I/O Circuit Type

| Circuit Type | Circuit                        | Remarks                                                                                    |

|--------------|--------------------------------|--------------------------------------------------------------------------------------------|

| D            | V <sub>cc</sub> P-ch N-ch N-ch | ■ CMOS output ■ CMOS Hysteresis input                                                      |

| E            | P-ch N-ch Analog input HYS     | <ul> <li>■ CMOS output</li> <li>■ CMOS Hysteresis input</li> <li>■ Analog input</li> </ul> |

Document Number: 002-07700 Rev. \*A

| Circuit Type | Circuit                    | Remarks                                                                 |

|--------------|----------------------------|-------------------------------------------------------------------------|

|              | V                          | ■ CMOS high current output                                              |

| F            | P-ch High current N-ch HYS | ■ CMOS Hysteresis input                                                 |

|              |                            | ■ CMOS output                                                           |

|              | —  Vcc                     | ■ CMOS Hysteresis input                                                 |

| G            | P-ch N-ch R HYS R T TTL    | ■ TTL input (MB90F598G, only in Flash mode)                             |

| Н            | R HYS                      | ■ Hysteresis input Pull-down Resistor: 50 kΩ approx. (except MB90F598G) |

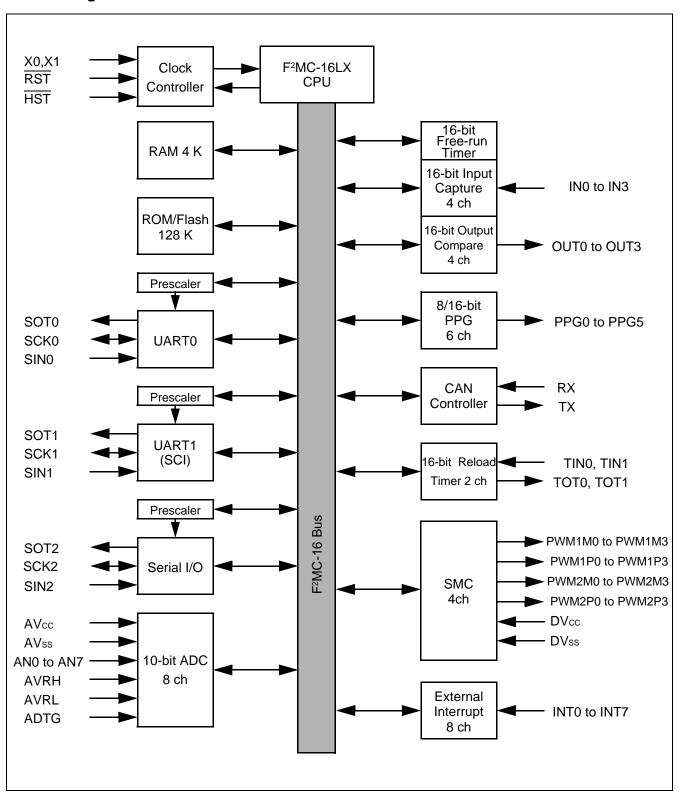

### 6. Block Diagram

## 8. I/O Map

| Address    | Register                            | Abbreviation | Access | Peripheral  | Initial value                |

|------------|-------------------------------------|--------------|--------|-------------|------------------------------|

| 00н        | Port 0 Data Register                | PDR0         | R/W    | Port 0      | XXXXXXXXB                    |

| 01н        | Port 1 Data Register                | PDR1         | R/W    | Port 1      | XXXXXXXXB                    |

| 02н        | Port 2 Data Register                | PDR2         | R/W    | Port 2      | XXXXXXXXB                    |

| 03н        | Port 3 Data Register                | PDR3         | R/W    | Port 3      | XXXXXXXXB                    |

| 04н        | Port 4 Data Register                | PDR4         | R/W    | Port 4      | XXXXXXXXB                    |

| 05н        | Port 5 Data Register                | PDR5         | R/W    | Port 5      | XXXXXXXXB                    |

| 06н        | Port 6 Data Register                | PDR6         | R/W    | Port 6      | XXXXXXXXB                    |

| 07н        | Port 7 Data Register                | PDR7         | R/W    | Port 7      | XXXXXXXXB                    |

| 08н        | Port 8 Data Register                | PDR8         | R/W    | Port 8      | XXXXXXXXB                    |

| 09н        | Port 9 Data Register                | PDR9         | R/W    | Port 9      | XXXXXXB                      |

| 0Ан to 0Fн |                                     | Reserv       | ed     |             | •                            |

| 10н        | Port 0 Direction Register           | DDR0         | R/W    | Port 0      | 0 0 0 0 0 0 0 0в             |

| 11н        | Port 1 Direction Register           | DDR1         | R/W    | Port 1      | 0 0 0 0 0 0 0 0в             |

| 12н        | Port 2 Direction Register           | DDR2         | R/W    | Port 2      | 0 0 0 0 0 0 0 0в             |

| 13н        | Port 3 Direction Register           | DDR3         | R/W    | Port 3      | 0 0 0 0 0 0 0 0в             |

| 14н        | Port 4 Direction Register           | DDR4         | R/W    | Port 4      | 0 0 0 0 0 0 0 0в             |

| 15н        | Port 5 Direction Register           | DDR5         | R/W    | Port 5      | 0 0 0 0 0 0 0 0в             |

| 16н        | Port 6 Direction Register           | DDR6         | R/W    | Port 6      | 0 0 0 0 0 0 0 0в             |

| 17н        | Port 7 Direction Register           | DDR7         | R/W    | Port 7      | 0 0 0 0 0 0 0 0в             |

| 18н        | Port 8 Direction Register           | DDR8         | R/W    | Port 8      | 0 0 0 0 0 0 0 0в             |

| 19н        | Port 9 Direction Register           | DDR9         | R/W    | Port 9      | 000000                       |

| 1Ан        |                                     | Reserv       | ed     |             |                              |

| 1Вн        | Analog Input Enable Register        | ADER         | R/W    | Port 6, A/D | 11111111                     |

| 1Сн to 1Fн |                                     | Reserv       | ed     |             |                              |

| 20н        | Serial Mode Control Register 0      | UMC0         | R/W    |             | 0 0 0 0 0 1 0 0в             |

| 21н        | Serial status Register 0            | USR0         | R/W    | UART0       | 0 0 0 1 0 0 0 0в             |

| 22н        | Serial Input/Output Data Register 0 | UIDR0/UODR0  | R/W    | UARTO       | XXXXXXXXB                    |

| 23н        | Rate and Data Register 0            | URD0         | R/W    |             | 0 0 0 0 0 0 0 X <sub>B</sub> |

| 24н        | Serial Mode Register 1              | SMR1         | R/W    |             | 0 0 0 0 0 0 0 0в             |

| 25н        | Serial Control Register 1           | SCR1         | R/W    |             | 0 0 0 0 0 1 0 0в             |

| 26н        | Serial Input/Output Data Register 1 | SIDR1/SODR1  | R/W    | UART1       | XXXXXXXXB                    |

| 27н        | Serial Status Register 1            | SSR1         | R/W    |             | 0 0 0 0 1 _ 0 Ов             |

| 28н        | UART1 Prescaler Control Register    | U1CDCR       | R/W    |             | 01111в                       |

| Address        | Register                                | Abbreviation | Access | Peripheral                | Initial value         |

|----------------|-----------------------------------------|--------------|--------|---------------------------|-----------------------|

| 1910н          | Reload Register L                       | PRLL8        | R/W    |                           | XXXXXXXXB             |

| 1911н          | Reload Register H                       | PRLH8        | R/W    | 16-bit Programmable Pulse | XXXXXXXXB             |

| 1912н          | Reload Register L                       | PRLL9        | R/W    | Generator 8/9             | XXXXXXXXB             |

| 1913н          | Reload Register H                       | PRLH9        | R/W    |                           | XXXXXXXXB             |

| 1914н          | Reload Register L                       | PRLLA        | R/W    | 16-bit Programmable Pulse | XXXXXXXXB             |

| 1915н          | Reload Register H                       | PRLHA        | R/W    | Generator A/B             | XXXXXXXXB             |

| 1916н          | Reload Register L                       | PRLLB        | R/W    | 16-bit Programmable Pulse | XXXXXXXX              |

| 1917н          | Reload Register H                       | PRLHB        | R/W    | Generator A/B             | XXXXXXXX <sub>B</sub> |

| 1918н to 191Fн |                                         | Re           | served |                           |                       |

| 1920н          | Input Capture Register 0 (low-order)    | IPCP0        | R      |                           | XXXXXXXX              |

| 1921н          | Input Capture Register 0 (high-order)   | IPCP0        | R      |                           | XXXXXXXX              |

| 1922н          | Input Capture Register 1 (low-order)    | IPCP1        | R      | Input Capture 0/1         | XXXXXXX               |

| 1923н          | Input Capture Register 1 (high-order)   | IPCP1        | R      |                           | XXXXXXXX              |

| 1924н          | Input Capture Register 2<br>(low-order) | IPCP2        | R      |                           | XXXXXXX               |

| 1925н          | Input Capture Register 2 (high-order)   | IPCP2        | R      | January Continue 0/0      | XXXXXXXX              |

| 1926н          | Input Capture Register 3 (low-order)    | IPCP3        | R      | Input Capture 2/3         | XXXXXXX               |

| 1927н          | Input Capture Register 3 (high-order)   | IPCP3        | R      |                           | XXXXXXX               |

| 1928н          | Output Compare Register 0 (low-order)   | OCCP0        | R/W    |                           | XXXXXXX               |

| 1929н          | Output Compare Register 0 (high-order)  | OCCP0        | R/W    | Output Compare 0/1        | XXXXXXXX              |

| 192Ан          | Output Compare Register 1 (low-order)   | OCCP1        | R/W    | Output Compare 0/1        | XXXXXXXX              |

| 192Вн          | Output Compare Register 1 (high-order)  | OCCP1        | R/W    |                           | XXXXXXXXB             |

| Address | Register       | Abbreviation | Access                                 | Initial Value                           |  |

|---------|----------------|--------------|----------------------------------------|-----------------------------------------|--|

| 001А40н |                |              |                                        | VVVVVV VVVVVV                           |  |

| 001А41н | ID register 8  | IDR8         | R/W                                    | XXXXXXXX XXXXXXXB                       |  |

| 001А42н | Tib register o | IDRO         | I K/VV                                 | XXXXX XXXXXXXXB                         |  |

| 001А43н |                |              | ************************************** |                                         |  |

| 001А44н |                |              |                                        | XXXXXXXX XXXXXXXX                       |  |

| 001А45н | ID register 9  | IDR9         | R/W                                    | VVVVVVV VVVVVV                          |  |

| 001А46н | ID register 9  | IDIX9        | IX/VV                                  | XXXXX XXXXXXXXB                         |  |

| 001А47н |                |              |                                        |                                         |  |

| 001А48н |                |              |                                        | XXXXXXXX XXXXXXXX                       |  |

| 001А49н | ID register 10 | IDR10        | R/W                                    | XXXXXXX XXXXXX                          |  |

| 001А4Ан | To register 10 | IDICIO       | IX/VV                                  | XXXXX XXXXXXXXB                         |  |

| 001А4Вн |                |              |                                        | XXXX XXXXXXX                            |  |

| 001А4Сн |                |              | R/W                                    | XXXXXXX XXXXXXX <sub>B</sub>            |  |

| 001А4Dн | ID register 11 | IDR11        |                                        | 7,5000000000000000000000000000000000000 |  |

| 001А4Ен | Togister 11    |              |                                        | XXXXX XXXXXXXXB                         |  |

| 001А4Гн |                |              |                                        | XXXXX XXXXXXX                           |  |

| 001А50н |                |              | R/W                                    | XXXXXXX XXXXXXX                         |  |

| 001А51н | ID register 12 | IDR12        |                                        | AAAAAAAAAAAAAA                          |  |

| 001А52н | Togister 12    |              | 10,00                                  | XXXXX XXXXXXXXB                         |  |

| 001А53н |                |              |                                        | 70000 7000000                           |  |

| 001А54н |                |              |                                        | XXXXXXXX XXXXXXXX                       |  |

| 001А55н | ID register 13 | IDR13        | R/W                                    |                                         |  |

| 001А56н |                |              |                                        | XXXXX XXXXXXXXB                         |  |

| 001А57н |                |              |                                        |                                         |  |

| 001А58н |                |              |                                        | XXXXXXXX XXXXXXXX                       |  |

| 001А59н | ID register 14 | IDR14        | R/W                                    |                                         |  |

| 001А5Ан | _              |              |                                        | XXXXX XXXXXXXXB                         |  |

| 001А5Вн |                |              |                                        |                                         |  |

| 001А5Сн |                |              |                                        | XXXXXXXX XXXXXXXX                       |  |

| 001A5Dн | ID register 15 | IDR15        | R/W                                    |                                         |  |

| 001А5Ен | .29            |              |                                        | XXXXX XXXXXXXXB                         |  |

| 001А5Гн |                |              |                                        |                                         |  |

### 10. Interrupt Source, Interrupt Vector, and Interrupt Control Register

| lutarii                        | El <sup>2</sup> OS | Interru | pt vector           | Interrupt control register |          |

|--------------------------------|--------------------|---------|---------------------|----------------------------|----------|

| Interrupt source               | clear              | Number  | Address             | Number                     | Address  |

| Reset                          | N/A                | # 08    | FFFFDCH             |                            |          |

| INT9 instruction               | N/A                | # 09    | FFFFD8 <sub>H</sub> |                            |          |

| Exception                      | N/A                | # 10    | FFFFD4 <sub>H</sub> |                            |          |

| CAN RX                         | N/A                | # 11    | FFFFD0 <sub>H</sub> | LODGO                      | 200000   |

| CAN TX/NS                      | N/A                | # 12    | FFFFCCH             | ICR00                      | 0000В0н  |

| External Interrupt (INT0/INT1) | *1                 | # 13    | FFFFC8 <sub>H</sub> | 10004                      | 0000004  |

| Time Base Timer                | N/A                | # 14    | FFFFC4 <sub>H</sub> | ICR01                      | 0000В1н  |

| 16-bit Reload Timer 0          | *1                 | # 15    | FFFFC0 <sub>H</sub> | IODOO                      | 000000   |

| 8/10-bit A/D Converter         | *1                 | # 16    | FFFFBCH             | ICR02                      | 0000В2н  |

| 16-bit Free-run Timer          | N/A                | # 17    | FFFFB8 <sub>H</sub> | LODGO                      | 200000   |

| External Interrupt (INT2/INT3) | *1                 | # 18    | FFFFB4 <sub>H</sub> | ICR03                      | 0000ВЗн  |

| Serial I/O                     | *1                 | # 19    | FFFFB0 <sub>H</sub> | 10004                      | 0000004  |

| External Interrupt (INT4/INT5) | *1                 | # 20    | FFFFACH             | ICR04                      | 0000В4н  |

| Input Capture 0                | *1                 | # 21    | FFFFA8 <sub>H</sub> | IODOS                      | 0000В5н  |

| 8/16-bit PPG 0/1               | N/A                | # 22    | FFFFA4 <sub>H</sub> | ICR05                      |          |

| Output Compare 0               | *1                 | # 23    | FFFFA0 <sub>H</sub> | LODGO                      | 0000В6н  |

| 8/16-bit PPG 2/3               | N/A                | # 24    | FFFF9C <sub>H</sub> | ICR06                      |          |

| External Interrupt (INT6/INT7) | *1                 | # 25    | FFFF98⊦             | 10007                      |          |

| Input Capture 1                | *1                 | # 26    | FFFF94 <sub>H</sub> | ICR07                      | 0000В7н  |

| 8/16-bit PPG 4/5               | N/A                | # 27    | FFFF90⊦             | LODGO                      |          |

| Output Compare 1               | *1                 | # 28    | FFFF8C <sub>H</sub> | ICR08                      | 0000В8н  |

| 8/16-bit PPG 6/7               | N/A                | # 29    | FFFF88 <sub>H</sub> |                            |          |

| Input Capture 2                | *1                 | # 30    | FFFF84 <sub>H</sub> | ICR09                      | 0000В9н  |

| 8/16-bit PPG 8/9               | N/A                | # 31    | FFFF80 <sub>H</sub> | 10040                      | 0000004  |

| Output Compare 2               | *1                 | # 32    | FFFF7C <sub>H</sub> | ICR10                      | 0000ВАн  |

| Input Capture 3                | *1                 | # 33    | FFFF78⊦             | 10044                      | 000000   |

| 8/16-bit PPG A/B               | N/A                | # 34    | FFFF74 <sub>H</sub> | ICR11                      | 0000ВВн  |

| Output Compare 3               | *1                 | # 35    | FFFF70 <sub>H</sub> | 10040                      | 000000   |

| 16-bit Reload Timer 1          | *1                 | # 36    | FFFF6C <sub>H</sub> | ICR12                      | 0000ВСн  |

| UART 0 RX                      | *2                 | # 37    | FFFF68 <sub>H</sub> | 10510                      | 000055   |

| UART 0 TX                      | *1                 | # 38    | FFFF64 <sub>H</sub> | ICR13                      | 0000ВDн  |

| UART 1 RX                      | *2                 | # 39    | FFFF60⊦             | 10044                      | 000005   |

| UART 1 TX                      | *1                 | # 40    | FFFF5C <sub>H</sub> | ICR14                      | 0000ВЕн  |

| Flash Memory                   | N/A                | # 41    | FFFF58⊦             | 10045                      | 000005   |

| Delayed interrupt              | N/A                | # 42    | FFFF54 <sub>H</sub> | ICR15                      | 0000ВFн  |

|                                |                    | 1       |                     |                            | <u> </u> |

<sup>\*1:</sup> The interrupt request flag is cleared by the El<sup>2</sup>OS interrupt clear signal.

N/A:The interrupt request flag is not cleared by the El<sup>2</sup>OS interrupt clear signal.

<sup>\*2:</sup> The interrupt request flag is cleared by the El<sup>2</sup>OS interrupt clear signal. A stop request is available.

#### Notes:

- For a peripheral module with two interrupt for a single interrupt number, both interrupt request flags are cleared by the El²OS interrupt clear signal.

- At the end of El²OS, the El²OS clear signal will be asserted for all the interrupt flags assigned to the same interrupt number. If one interrupt flag starts the El²OS and in the meantime another interrupt flag is set by hardware event, the later event is lost because the flag is cleared by the El²OS clear signal caused by the first event. So it is recommended not to use the El²OS for this interrupt number.

- If El²OS is enabled, El²OS is initiated when one of the two interrupt signals in the same interrupt control register (ICR) is asserted. This means that different interrupt sources share the same El²OS Descriptor which should be unique for each interrupt source. For this reason, when one interrupt source uses the El²OS, the other interrupt should be disabled.

Document Number: 002-07700 Rev. \*A Page 30 of 51

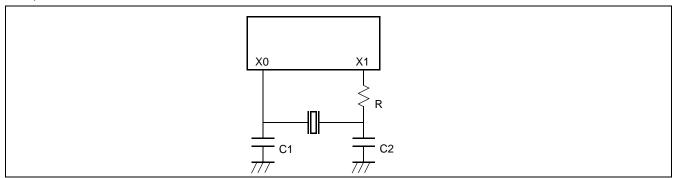

### ■ Example of Oscillation circuit

AC characteristics are set to the measured reference voltage values below.

| Parameter                     | Sym-           | Pin name   | Value      |     |            |      | Remarks                 |

|-------------------------------|----------------|------------|------------|-----|------------|------|-------------------------|

| Parameter                     | bol            | rin name   | Min        | Тур | Max        | Unit | Remarks                 |

| Poforonco voltago rango       | _              | AVRH       | AVRL + 3.0 | _   | AVcc       | V    |                         |

| Reference voltage range       | _              | AVRL       | 0          | _   | AVRH - 3.0 | V    |                         |

| Power supply current          | lΑ             | AVcc       | _          | 5   | _          | mA   |                         |

| Fower supply current          | Іан            | AVcc       | _          | _   | 5          | μΑ   | *                       |

|                               | l <sub>R</sub> | AVRH       | _          | 400 | 600        | μΑ   | MB90V595G,<br>MB90F598G |

| Reference voltage current     |                |            | _          | 140 | 600        | μΑ   | MB90598G                |

|                               | Iгн            | AVRH       |            | _   | 5          | μΑ   | *                       |

| Offset between input channels | _              | AN0 to AN7 | _          | _   | 4          | LSB  |                         |

<sup>\*:</sup> When not operating A/D converter, this is the current (Vcc = AVcc = AVRH = 5.0 V) when the CPU is stopped.

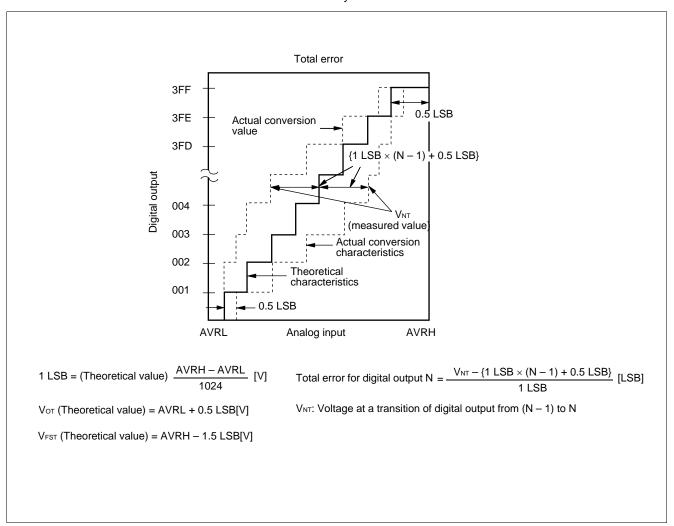

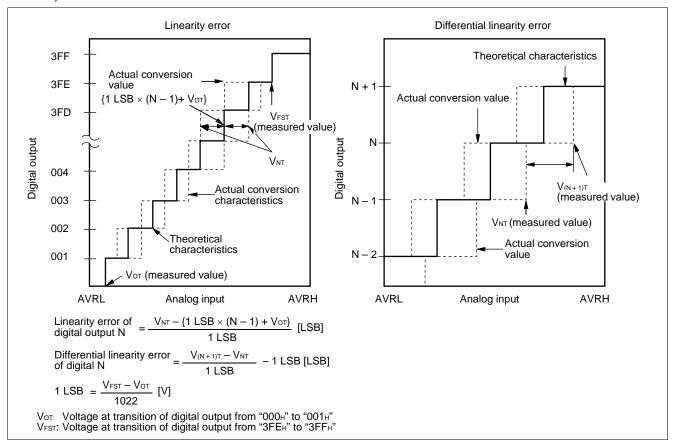

#### 11.6 A/D Converter Glossary

Resolution: Analog changes that are identifiable with the A/D converter

Linearity error: The deviation of the straight line connecting the zero transition point ("00 0000 0000"  $\leftrightarrow$  "00 0000 0001") with the full-scale transition point ("11 1111 1110"  $\leftrightarrow$  "11 1111 1111") from actual conversion characteristics

Differential linearity error: The deviation of input voltage needed to change the output code by 1 LSB from the theoretical value Total error: The total error is defined as a difference between the actual value and the theoretical value, which includes zero-transition error/full-scale transition error and linearity error.

#### (Continued)

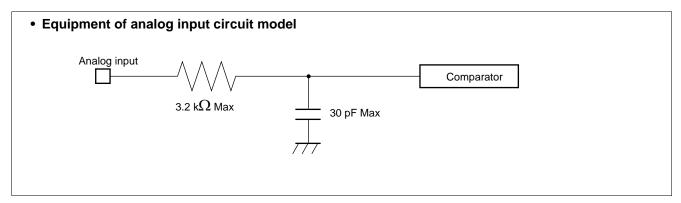

#### 11.7 Notes on Using A/D Converter

Select the output impedance value for the external circuit of analog input according to the following conditions,:

- Output impedance values of the external circuit of 15 k $\Omega$  or lower are recommended.

- When capacitors are connected to external pins, the capacitance of several thousand times the internal capacitor value is recommended to minimized the effect of voltage distribution between the external capacitor and internal capacitor. When the output impedance of the external circuit is too high, the sampling period for analog voltages may not be sufficient (sampling period = 4.00 μs @machine clock of 16 MHz).

#### ■ Error

The smaller the | AVRH - AVRL |, the greater the error would become relatively.

## 11.8 Flash memory

■ Erase and programming performance

| Parameter                         | Condition                                   | Value |     |      | Unit  | Remarks   |                                        |

|-----------------------------------|---------------------------------------------|-------|-----|------|-------|-----------|----------------------------------------|

|                                   |                                             | Min   | Тур | Max  | Onit  | Remarks   |                                        |

| Sector erase time                 |                                             | _     | 1   | 15   | s     | MB90F598G | Excludes 00H programming prior erasure |

| Chip erase time                   | $T_A = +25$ °C,<br>$V_{CC} = 5.0 \text{ V}$ | _     | 5   | _    | s     | MB90F598G | Excludes 00H programming prior         |

| Word (16-bit)<br>programming time |                                             | _     | 16  | 3600 | μs    | MB90F598G | Excludes system-level overhead         |

| Erase/Program cycle               | _                                           | 10000 | -   | _    | cycle |           |                                        |

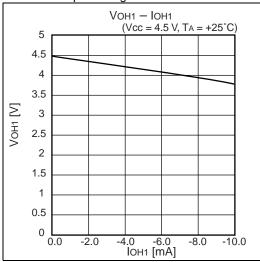

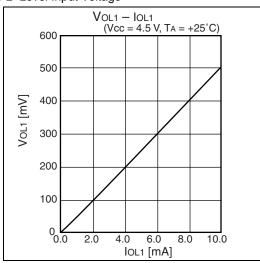

### 12. Example Characteristics

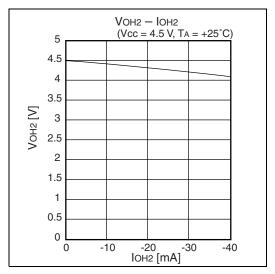

■ H" Level Output Voltage

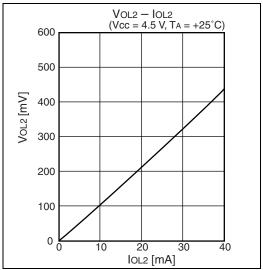

■ L" Level Input Voltage

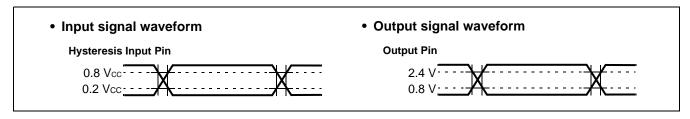

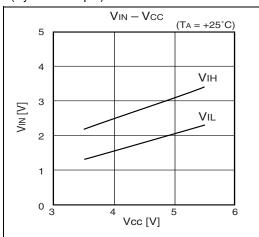

■ H" Level Input Voltage/"L" Level Input Voltage (Hysteresis Input)

## 15. Major Changes

**Spansion Publication Number: DS07-13705-7E**

| Section                                          | Change Results                                                                                                   |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| _                                                | Deleted the old products, MB90598, MB90F598, and MB90V595.                                                       |  |  |

| _                                                | Changed the series name;<br>MB90595/595G series ? MB90595G series                                                |  |  |

| _                                                | Changed the following erroneous name. I/O timer → 16-bit Free-run Timer                                          |  |  |

| PRODUCT LINEUP                                   | One of Standby mode name is changed. Clock mode → Watch mode                                                     |  |  |

| I/O CIRCUIT TYPE                                 | Changed Pull-down resistor value of circuit type H.                                                              |  |  |

| ELECTRICAL CHARACTERISTICS<br>AC Characteristics | Add the "External clock input" and "Flash Read cycle time" in (1) Clock Timing                                   |  |  |

|                                                  | Figure in (2) Reset and Hardware Standby Input RST/HST input level of "In Stop Mode" is changed. 0.6 Vcc 0.2 Vcc |  |  |

| ELECTRICAL CHARACTERISTICS 5. A/D Converter      | Changed the items of "Zero transition voltage" and "Full scale transition voltage".                              |  |  |

NOTE: Please see "Document History" about later revised information.

# **Document History**

| Document Title: MB90598G/F598G/V595G F <sup>2</sup> MC-16LX MB90595G Series CMOS 16-bit Proprietary Microcontroller Document Number: 002-07700 |         |                    |                    |                                                                                                          |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Revision                                                                                                                                       | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |  |  |  |

| **                                                                                                                                             | _       | AKIH               | 09/26/2008         | Migrated to Cypress and assigned document number 002-07700.<br>No change to document contents or format. |  |  |  |

| *A                                                                                                                                             | 5537128 | AKIH               | 11/30/2016         | Updated to Cypress template                                                                              |  |  |  |

Document Number: 002-07700 Rev. \*A Page 50 of 51