Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | F <sup>2</sup> MC-16LX                                                        |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                                  |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 78                                                                            |

| Program Memory Size        | 128KB (128K x 8)                                                              |

| Program Memory Type        | Mask ROM                                                                      |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                   |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-BQFP                                                                      |

| Supplier Device Package    | 100-QFP (14x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90598gpf-g-193e1 |

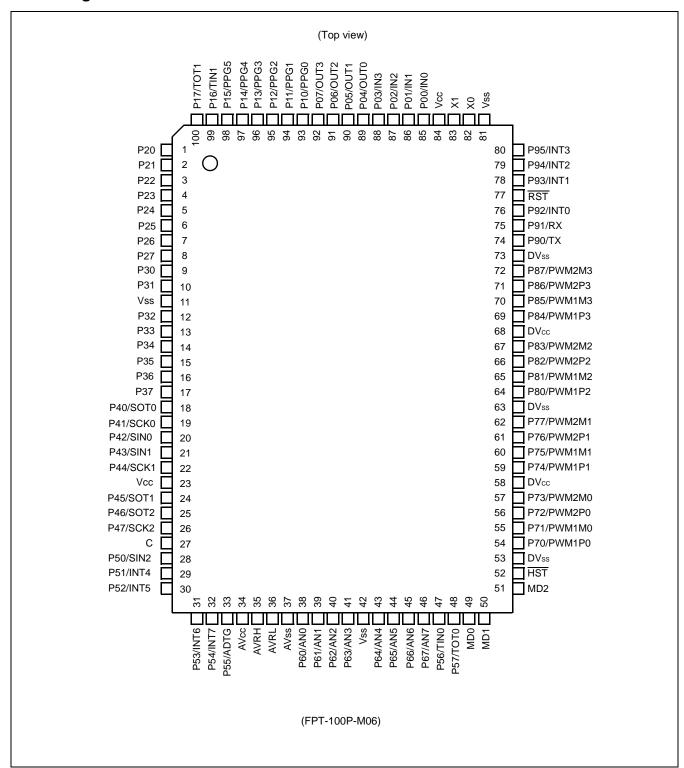

## 2. Pin Assignment

| Pin no.  | Pin name                             | Circuit type | Function                                            |  |  |  |

|----------|--------------------------------------|--------------|-----------------------------------------------------|--|--|--|

| 00       | P50                                  | Г.           | General purpose IO                                  |  |  |  |

| 28       | SIN2                                 | D            | SIN Input for the Serial IO                         |  |  |  |

| 00.100   | P51 to P54                           | 1            | General purpose IO                                  |  |  |  |

| 29 to 32 | INT4 to INT7                         | D            | External interrupt input for INT4 to INT7           |  |  |  |

| 20       | P55                                  | <u> </u>     | General purpose IO                                  |  |  |  |

| 33       | ADTG                                 | D            | Input for the external trigger of the A/D Converter |  |  |  |

| 20 to 44 | P60 to P63                           |              | General purpose IO                                  |  |  |  |

| 38 to 41 | AN0 to AN3                           | E            | Inputs for the A/D Converter                        |  |  |  |

| 40 to 40 | P64 to P67                           |              | General purpose IO                                  |  |  |  |

| 43 to 46 | AN4 to AN7                           | E            | Inputs for the A/D Converter                        |  |  |  |

| 47       | P56                                  | <u> </u>     | General purpose IO                                  |  |  |  |

| 47       | TIN0                                 | D            | TIN input for the 16-bit Reload Timer 0             |  |  |  |

| 40       | P57                                  | <u> </u>     | General purpose IO                                  |  |  |  |

| 48       | TOT0                                 | D            | TOT output for the 16-bit Reload Timer 0            |  |  |  |

|          | P70 to P73                           |              | General purpose IO                                  |  |  |  |

| 54 to 57 | PWM1P0<br>PWM1M0<br>PWM2P0<br>PWM2M0 | F            | Output for Stepper Motor Controller channel 0       |  |  |  |

|          | P74 to P77                           |              | General purpose IO                                  |  |  |  |

| 59 to 62 | PWM1P1<br>PWM1M1<br>PWM2P1<br>PWM2M1 | F            | Output for Stepper Motor Controller channel 1       |  |  |  |

|          | P80 to P83                           |              | General purpose IO                                  |  |  |  |

| 64 to 67 | PWM1P2<br>PWM1M2<br>PWM2P2<br>PWM2M2 | F            | Output for Stepper Motor Controller channel 2       |  |  |  |

|          | P84 to P87                           |              | General purpose IO                                  |  |  |  |

| 69 to 72 | PWM1P3<br>PWM1M3<br>PWM2P3<br>PWM2M3 | F            | Output for Stepper Motor Controller channel 3       |  |  |  |

| 74       | P90                                  | Ĺ            | General purpose IO                                  |  |  |  |

| 74       | TX                                   | D            | TX output for CAN Interface                         |  |  |  |

| 75       | P91                                  | r.           | General purpose IO                                  |  |  |  |

| 75       | RX                                   | D            | RX input for CAN Interface                          |  |  |  |

| Circuit Type | Circuit                        | Remarks                                                                                    |

|--------------|--------------------------------|--------------------------------------------------------------------------------------------|

| D            | V <sub>cc</sub> P-ch N-ch N-ch | ■ CMOS output ■ CMOS Hysteresis input                                                      |

| E            | P-ch N-ch Analog input HYS     | <ul> <li>■ CMOS output</li> <li>■ CMOS Hysteresis input</li> <li>■ Analog input</li> </ul> |

Document Number: 002-07700 Rev. \*A

| Circuit Type | Circuit                    | Remarks                                                                 |

|--------------|----------------------------|-------------------------------------------------------------------------|

|              | V                          | ■ CMOS high current output                                              |

| F            | P-ch High current N-ch HYS | ■ CMOS Hysteresis input                                                 |

|              |                            | ■ CMOS output                                                           |

|              | Vcc                        | ■ CMOS Hysteresis input                                                 |

| G            | P-ch N-ch R HYS R T TTL    | ■ TTL input (MB90F598G, only in Flash mode)                             |

| Н            | R HYS                      | ■ Hysteresis input Pull-down Resistor: 50 kΩ approx. (except MB90F598G) |

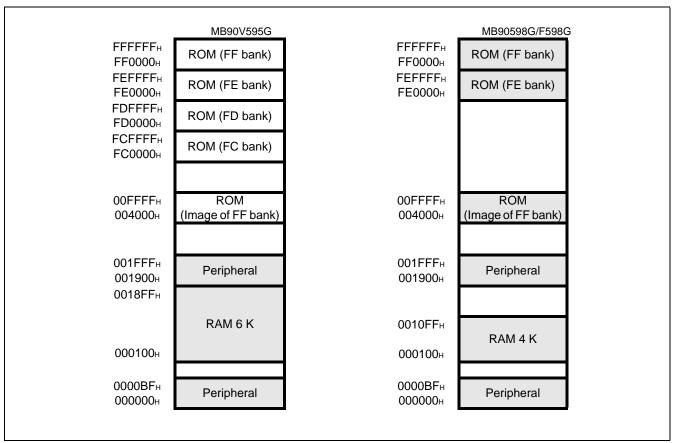

## 7. Memory Space

The memory space of the MB90595G Series is shown below

Figure 1. Memory space map

Note: The ROM data of bank FF is reflected in the upper address of bank 00, realizing effective use of the C compiler small model. The lower 16-bit of bank FF and the lower 16-bit of bank 00 are assigned to the same address, enabling reference of the table on the ROM without stating "far".

For example, if an attempt has been made to access 00C000H, the contents of the ROM at FFC000H are accessed. Since the ROM area of the FF bank exceeds 48 Kbytes, the whole area cannot be reflected in the image for the 00 bank. The ROM data at FF4000H to FFFFFH looks, therefore, as if it were the image for 004000H to 00FFFFH. Thus, it is recommended that the ROM data table be stored in the area of FF4000H to FFFFFFH.

Document Number: 002-07700 Rev. \*A

| Address    | Register                      | Abbreviation | Access | Peripheral                   | Initial value |

|------------|-------------------------------|--------------|--------|------------------------------|---------------|

| ВОн        | Interrupt Control Register 00 | ICR00        | R/W    |                              | 00000111в     |

| В1н        | Interrupt Control Register 01 | ICR01        | R/W    | latera at controller         | 00000111в     |

| В2н        | Interrupt Control Register 02 | ICR02        | R/W    | Interrupt controller         | 00000111в     |

| ВЗн        | Interrupt Control Register 03 | ICR03        | R/W    |                              | 00000111в     |

| В4н        | Interrupt Control Register 04 | ICR04        | R/W    |                              | 00000111в     |

| В5н        | Interrupt Control Register 05 | ICR05        | R/W    |                              | 00000111в     |

| В6н        | Interrupt Control Register 06 | ICR06        | R/W    |                              | 00000111в     |

| В7н        | Interrupt Control Register 07 | ICR07        | R/W    |                              | 00000111в     |

| В8н        | Interrupt Control Register 08 | ICR08        | R/W    |                              | 00000111в     |

| В9н        | Interrupt Control Register 09 | ICR09        | R/W    | latarment and solvellar      | 00000111в     |

| ВАн        | Interrupt Control Register 10 | ICR10        | R/W    | Interrupt controller         | 00000111в     |

| ВВн        | Interrupt Control Register 11 | ICR11        | R/W    |                              | 00000111в     |

| ВСн        | Interrupt Control Register 12 | ICR12        | R/W    |                              | 00000111в     |

| ВОн        | Interrupt Control Register 13 | ICR13        | R/W    |                              | 00000111в     |

| ВЕн        | Interrupt Control Register 14 | ICR14        | R/W    |                              | 00000111В     |

| ВГн        | Interrupt Control Register 15 | ICR15        | R/W    |                              | 00000111в     |

| C0н to FFн |                               | Resei        | rved   |                              |               |

| 1900н      | Reload Register L             | PRLL0        | R/W    |                              | XXXXXXXX      |

| 1901н      | Reload Register H             | PRLH0        | R/W    | 16-bit Programmable<br>Pulse | XXXXXXXX      |

| 1902н      | Reload Register L             | PRLL1        | R/W    | Generator 0/1                | XXXXXXXX      |

| 1903н      | Reload Register H             | PRLH1        | R/W    |                              | XXXXXXXX      |

| 1904н      | Reload Register L             | PRLL2        | R/W    |                              | XXXXXXXX      |

| 1905н      | Reload Register H             | PRLH2        | R/W    | 16-bit Programmable<br>Pulse | XXXXXXXX      |

| 1906н      | Reload Register L             | PRLL3        | R/W    | Generator 2/3                | XXXXXXXX      |

| 1907н      | Reload Register H             | PRLH3        | R/W    |                              | XXXXXXXX      |

| 1908н      | Reload Register L             | PRLL4        | R/W    |                              | XXXXXXXX      |

| 1909н      | Reload Register H             | PRLH4        | R/W    | 16-bit Programmable          | XXXXXXXX      |

| 190Ан      | Reload Register L             | PRLL5        | R/W    | Pulse<br>Generator 4/5       | XXXXXXXXB     |

| 190Вн      | Reload Register H             | PRLH5        | R/W    |                              | XXXXXXXX      |

| 190Сн      | Reload Register L             | PRLL6        | R/W    |                              | XXXXXXXX      |

| 190Он      | Reload Register H             | PRLH6        | R/W    | 16-bit Programmable          | XXXXXXXX      |

| 190Ен      | Reload Register L             | PRLL7        | R/W    | Pulse<br>Generator 6/7       | XXXXXXXXB     |

| 190Fн      | Reload Register H             | PRLH7        | R/W    |                              | XXXXXXXX      |

| Address        | Register                                | Abbreviation | Access | Peripheral                | Initial value |

|----------------|-----------------------------------------|--------------|--------|---------------------------|---------------|

| 1910н          | Reload Register L                       | PRLL8        | R/W    |                           | XXXXXXX       |

| 1911н          | Reload Register H                       | PRLH8        | R/W    | 16-bit Programmable Pulse | XXXXXXXXB     |

| 1912н          | Reload Register L                       | PRLL9        | R/W    | Generator 8/9             | XXXXXXXXB     |

| 1913н          | Reload Register H                       | PRLH9        | R/W    |                           | XXXXXXXXB     |

| 1914н          | Reload Register L                       | PRLLA        | R/W    | 16-bit Programmable Pulse | XXXXXXXXB     |

| 1915н          | Reload Register H                       | PRLHA        | R/W    | Generator A/B             | XXXXXXXXB     |

| 1916н          | Reload Register L                       | PRLLB        | R/W    | 16-bit Programmable Pulse | XXXXXXXXB     |

| 1917н          | Reload Register H                       | PRLHB        | R/W    | Generator A/B             | XXXXXXXXB     |

| 1918н to 191Fн |                                         | Re           | served |                           |               |

| 1920н          | Input Capture Register 0 (low-order)    | IPCP0        | R      |                           | XXXXXXX       |

| 1921н          | Input Capture Register 0 (high-order)   | IPCP0        | R      |                           | XXXXXXXX      |

| 1922н          | Input Capture Register 1 (low-order)    | IPCP1        | R      | - Input Capture 0/1       | XXXXXXX       |

| 1923н          | Input Capture Register 1 (high-order)   | IPCP1        | R      |                           | XXXXXXXXB     |

| 1924н          | Input Capture Register 2<br>(low-order) | IPCP2        | R      |                           | XXXXXXXX      |

| 1925н          | Input Capture Register 2 (high-order)   | IPCP2        | R      | January Continue 2/2      | XXXXXXX       |

| 1926н          | Input Capture Register 3 (low-order)    | IPCP3        | R      | Input Capture 2/3         | XXXXXXXXB     |

| 1927н          | Input Capture Register 3 (high-order)   | IPCP3        | R      |                           | XXXXXXXXB     |

| 1928н          | Output Compare Register 0 (low-order)   | OCCP0        | R/W    |                           | XXXXXXXXB     |

| 1929н          | Output Compare Register 0 (high-order)  | OCCP0        | R/W    | Output Compare 0/1        | XXXXXXXXB     |

| 192Ан          | Output Compare Register 1 (low-order)   | OCCP1        | R/W    | Output Compare 0/1        | XXXXXXXXB     |

| 192Вн          | Output Compare Register 1 (high-order)  | OCCP1        | R/W    |                           | XXXXXXXXB     |

| Address        | Register                                              | Abbreviation         | Access       | Peripheral         | Initial value |  |  |  |

|----------------|-------------------------------------------------------|----------------------|--------------|--------------------|---------------|--|--|--|

| 192Сн          | Output Compare Register 2 (low-order)                 | OCCP2                | R/W          |                    | XXXXXXXX      |  |  |  |

| 192Dн          | Output Compare Register 2 (high-order)                | OCCP2                | R/W          | Output Compare 2/3 | XXXXXXXX      |  |  |  |

| 192Ен          | Output Compare Register 3 (low-order)                 | OCCP3                | R/W          | Output Compare 2/3 | XXXXXXXX      |  |  |  |

| 192Fн          | Output Compare Register 3 (high-order)                | OCCP3                | R/W          |                    | XXXXXXXX      |  |  |  |

| 1930н to 19FFн |                                                       | Re                   | served       |                    |               |  |  |  |

| 1A00н to 1AFFн | CAN                                                   | Controller. Refer to | section abou | ut CAN Controller  |               |  |  |  |

| 1В00н to 1ВFFн | CAN Controller. Refer to section about CAN Controller |                      |              |                    |               |  |  |  |

| 1С00н to 1EFFн |                                                       | Re                   | served       |                    |               |  |  |  |

| 1FF0н          | Program Address Detection Register 0 (low-order)      |                      |              |                    | XXXXXXXX      |  |  |  |

| 1FF1н          | Program Address Detection Register 0 (middle-order)   | PADR0                | R/W          |                    | XXXXXXXXB     |  |  |  |

| 1FF2н          | Program Address Detection Register 0 (high-order)     |                      |              | Address Match      | XXXXXXXX      |  |  |  |

| 1FF3н          | Program Address Detection Register 1 (low-order)      |                      |              | Detection Function | XXXXXXXX      |  |  |  |

| 1FF4н          | Program Address Detection Register 1 (middle-order)   | PADR1                | R/W          |                    | XXXXXXXX      |  |  |  |

| 1FF5н          | Program Address Detection Register 1 (high-order)     |                      |              |                    | XXXXXXXXB     |  |  |  |

| 1FF6н to 1FFFн |                                                       | Reserved             |              |                    |               |  |  |  |

■ Description for Read/Write R/W : Readable/writable

R : Read only W : Write only

■ Description of initial value

0 : the initial value of this bit is "0".

1 : the initial value of this bit is "1".

X: the initial value of this bit is undefined.

\_ : this bit is unused. the initial value is undefined.

Note: : Addresses in the range of 0000<sub>H</sub> to 00FF<sub>H</sub>, which are not listed in the table, are reserved for the primary functions of the MCU. A read access to these reserved addresses results in reading "X", and any write access should not be performed.

| Address | Register      | Abbreviation | Access | Initial Value                          |  |

|---------|---------------|--------------|--------|----------------------------------------|--|

| 001А2Сн |               |              |        | XXXXXXX XXXXXXXB                       |  |

| 001А2Dн | ID register 3 | IDR3         | R/W    | ************************************** |  |

| 001А2Ен | To register 3 | IDIX5        | 17/77  | XXXXX XXXXXXXX <sub>B</sub>            |  |

| 001А2Гн |               |              |        | XXXX XXXXXXXB                          |  |

| 001А30н |               |              |        | XXXXXXX XXXXXXXB                       |  |

| 001А31н | ID register 4 | IDR4         | R/W    | AAAAAAA AAAAAAAA                       |  |

| 001А32н |               | IDI(4        | TV/ VV | XXXXX XXXXXXXX <sub>B</sub>            |  |

| 001А33н |               |              |        | VVVV VVVVVVV                           |  |

| 001А34н |               |              | R/W    | XXXXXXX XXXXXXXB                       |  |

| 001А35н | ID register 5 | IDR5         |        | AAAAAAA AAAAAAAA                       |  |

| 001А36н | To register 5 | IDIX5        |        | XXXXX XXXXXXXX <sub>B</sub>            |  |

| 001А37н |               |              |        | XXXX XXXXXXX                           |  |

| 001А38н |               |              |        | XXXXXXX XXXXXXXB                       |  |

| 001А39н | ID register 6 | IDR6         | R/W    | AAAAAAA AAAAAAAA                       |  |

| 001А3Ан | To register 0 | IDIXO        | 17/77  | XXXXX XXXXXXXX <sub>B</sub>            |  |

| 001А3Вн |               |              |        | VVVVV VVVVVVV                          |  |

| 001А3Сн |               |              |        | XXXXXXX XXXXXXXB                       |  |

| 001А3Дн | ID register 7 | IDR7         | R/W    | 7777777                                |  |

| 001А3Ен | In register / | IDK/         | IX/ VV | XXXXX XXXXXXXXB                        |  |

| 001А3Гн |               |              |        | ^^^^^- XXXXXXXB                        |  |

| Address            | Register       | Abbreviation | Access | Initial Value                           |

|--------------------|----------------|--------------|--------|-----------------------------------------|

| 001А40н            |                |              |        | VVVVVV VVVVVV                           |

| 001А41н            | ID register 8  | IDR8         | R/W    | XXXXXXXX XXXXXXXB                       |

| 001А42н            | Tegister o     |              | I K/VV | XXXXX XXXXXXXXB                         |

| 001А43н            |                |              |        | **************************************  |

| 001А44н            |                |              |        | XXXXXXX XXXXXXX                         |

| 001А45н            | ID register 9  | IDR9         | R/W    | 7/////// 7////////////////////////////  |

| 001А46н            | Togotor o      | IBIKO        | 17,77  | XXXXX XXXXXXXXB                         |

| 001А47н            |                |              |        | 70000 7000000                           |

| 001А48н            |                |              |        | XXXXXXX XXXXXXX                         |

| 001А49н            | ID register 10 | IDR10        | R/W    | 700000000000000000000000000000000000000 |

| 001А4Ан            |                | .20          | 17,77  | XXXXX XXXXXXXXB                         |

| 001А4Вн            |                |              |        |                                         |

| 001А4Сн            |                |              | R/W    | XXXXXXXX XXXXXXXX                       |

| 001A4Dн            | ID register 11 | IDR11        |        |                                         |

| 001А4Ен            |                |              |        | XXXXX XXXXXXXXB                         |

| 001А4Гн            |                |              |        |                                         |

| 001А50н            |                |              | R/W ·  | XXXXXXXX XXXXXXXX                       |

| 001А51н            | ID register 12 | IDR12        |        |                                         |

| 001А52н            |                |              |        | XXXXX XXXXXXXXB                         |

| 001А53н            |                |              |        |                                         |

| 001А54н            |                |              |        | XXXXXXX XXXXXXXX                        |

| 001А55н            | ID register 13 | IDR13        | R/W    |                                         |

| 001А56н<br>001А57н |                |              |        | XXXXX XXXXXXXXB                         |

| 001А57н            |                |              |        |                                         |

| 001А56н            |                |              |        | XXXXXXX XXXXXXXB                        |

| 001А5Ан            | ID register 14 | IDR14        | R/W    |                                         |

| 001A5Aн            |                |              |        | XXXXX XXXXXXXXB                         |

| 001/\text{1/CBH}   |                |              |        |                                         |

| 001A5Dн            |                |              |        | XXXXXXXX XXXXXXXB                       |

| 001А5Ен            | ID register 15 | IDR15        | R/W    |                                         |

| 001A5Fн            |                |              |        | XXXXX XXXXXXXXB                         |

| Address            | Register                  | Abbreviation | Access | Initial Value              |  |

|--------------------|---------------------------|--------------|--------|----------------------------|--|

| 001А60н            | DLC register 0            | DI CDO       | DAM    | VVV-                       |  |

| 001А61н            | - DLC register 0          | DLCR0        | R/W    | XXXX <sub>B</sub>          |  |

| 001А62н            | DLC register 1            | DLCR1        | R/W    | VVV <sub>2</sub>           |  |

| 001А63н            | - DEC register 1          | DLCKT        | R/VV   | XXXX <sub>B</sub>          |  |

| 001А64н            | DLC register 2            | DLCR2        | R/W    | ХХХХв                      |  |

| 001А65н            | DEG Tegister 2            | DEGINZ       | 1077   | 70000                      |  |

| 001А66н            | - DLC register 3          | DLCR3        | R/W    | XXXX <sub>B</sub>          |  |

| 001А67н            | DEC register o            | BEONO        | 1077   | 70000                      |  |

| 001А68н            | - DLC register 4          | DLCR4        | R/W    | XXXX <sub>B</sub>          |  |

| 001А69н            | 220 Tog.ioto. 1           | 5251(1       | 1011   | 7000                       |  |

| 001А6Ан            | - DLC register 5          | DLCR5        | R/W    | XXXX <sub>B</sub>          |  |

| 001А6Вн            | 220 reg.etc. 0            | 320.10       |        |                            |  |

| 001А6Сн            | - DLC register 6          | DLCR6        | R/W    | XXXX <sub>B</sub>          |  |

| 001А6Dн            | 220 reg.etc. 0            | 320.10       |        | 70000                      |  |

| 001А6Ен            | - DLC register 7          | DLCR7        | R/W    | XXXX <sub>B</sub>          |  |

| 001А6Fн            |                           |              | .,,,,  |                            |  |

| 001А70н            | DLC register 8            | DLCR8        | R/W    | XXXX                       |  |

| 001А71н            | ŭ                         |              |        |                            |  |

| 001А72н            | DLC register 9            | DLCR9        | R/W    | XXXX <sub>B</sub>          |  |

| 001А73н            |                           |              |        |                            |  |

| 001А74н            | DLC register 10           | DLCR10       | R/W    | XXXX <sub>B</sub>          |  |

| 001А75н            | -                         |              |        |                            |  |

| 001А76н            | DLC register 11           | DLCR11       | R/W    | XXXX <sub>B</sub>          |  |

| 001А77н            |                           |              |        |                            |  |

| 001А78н            | DLC register 12           | DLCR12       | R/W    | XXXX <sub>B</sub>          |  |

| 001А79н            |                           |              |        |                            |  |

| 001А7Ан            | DLC register 13           | DLCR13       | R/W    | XXXX <sub>B</sub>          |  |

| 001A7Вн            |                           |              |        |                            |  |

| 001A7CH            | DLC register 14           | DLCR14       | R/W    | XXXX <sub>B</sub>          |  |

| 001A7DH            |                           |              |        |                            |  |

| 001A7Eн            | DLC register 15           | DLCR15       | R/W    | XXXX <sub>B</sub>          |  |

| 001A7Fн<br>001A80н |                           |              |        |                            |  |

| to                 | Data register 0 (8 bytes) | DTR0         | R/W    | XXXXXXX <sub>B</sub><br>to |  |

| 001А87н            |                           |              |        | XXXXXXXXB                  |  |

# 10. Interrupt Source, Interrupt Vector, and Interrupt Control Register

| lutarroot                      | El <sup>2</sup> OS | Interru | pt vector           | Interrupt control register |         |

|--------------------------------|--------------------|---------|---------------------|----------------------------|---------|

| Interrupt source               | clear              | Number  | Address             | Number                     | Address |

| Reset                          | N/A                | # 08    | FFFFDCH             |                            |         |

| INT9 instruction               | N/A                | # 09    | FFFFD8 <sub>H</sub> |                            |         |

| Exception                      | N/A                | # 10    | FFFFD4 <sub>H</sub> |                            |         |

| CAN RX                         | N/A                | # 11    | FFFFD0 <sub>H</sub> | 10000                      | 000000  |

| CAN TX/NS                      | N/A                | # 12    | FFFFCCH             | ICR00                      | 0000В0н |

| External Interrupt (INT0/INT1) | *1                 | # 13    | FFFFC8 <sub>H</sub> | 10004                      | 0000004 |

| Time Base Timer                | N/A                | # 14    | FFFFC4 <sub>H</sub> | ICR01                      | 0000В1н |

| 16-bit Reload Timer 0          | *1                 | # 15    | FFFFC0 <sub>H</sub> | ICDOS                      | 000000  |

| 8/10-bit A/D Converter         | *1                 | # 16    | FFFFBCH             | ICR02                      | 0000В2н |

| 16-bit Free-run Timer          | N/A                | # 17    | FFFFB8 <sub>H</sub> | IODOO                      | 000000  |

| External Interrupt (INT2/INT3) | *1                 | # 18    | FFFFB4 <sub>H</sub> | ICR03                      | 0000ВЗн |

| Serial I/O                     | *1                 | # 19    | FFFFB0н             | ICD04                      | 0000004 |

| External Interrupt (INT4/INT5) | *1                 | # 20    | FFFFACH             | ICR04                      | 0000В4н |

| Input Capture 0                | *1                 | # 21    | FFFFA8 <sub>H</sub> | ICDOE                      | 0000В5н |

| 8/16-bit PPG 0/1               | N/A                | # 22    | FFFFA4 <sub>H</sub> | - ICR05                    |         |

| Output Compare 0               | *1                 | # 23    | FFFFA0 <sub>H</sub> | ICR06                      | 0000В6н |

| 8/16-bit PPG 2/3               | N/A                | # 24    | FFFF9C <sub>H</sub> |                            |         |

| External Interrupt (INT6/INT7) | *1                 | # 25    | FFFF98⊦             | 10007                      |         |

| Input Capture 1                | *1                 | # 26    | FFFF94 <sub>H</sub> | ICR07                      | 0000В7н |

| 8/16-bit PPG 4/5               | N/A                | # 27    | FFFF90⊦             | ICDOS                      | 000000  |

| Output Compare 1               | *1                 | # 28    | FFFF8C <sub>H</sub> | ICR08                      | 0000В8н |

| 8/16-bit PPG 6/7               | N/A                | # 29    | FFFF88 <sub>H</sub> | ICDOO                      | 000000  |

| Input Capture 2                | *1                 | # 30    | FFFF84 <sub>H</sub> | ICR09                      | 0000В9н |

| 8/16-bit PPG 8/9               | N/A                | # 31    | FFFF80 <sub>H</sub> | ICD40                      | 00000   |

| Output Compare 2               | *1                 | # 32    | FFFF7C <sub>H</sub> | ICR10                      | 0000ВАн |

| Input Capture 3                | *1                 | # 33    | FFFF78 <sub>H</sub> | ICR11                      | 000000  |

| 8/16-bit PPG A/B               | N/A                | # 34    | FFFF74 <sub>H</sub> | ICKII                      | 0000ВВн |

| Output Compare 3               | *1                 | # 35    | FFFF70⊦             | ICD40                      | 000000  |

| 16-bit Reload Timer 1          | *1                 | # 36    | FFFF6C <sub>H</sub> | ICR12                      | 0000ВСн |

| UART 0 RX                      | *2                 | # 37    | FFFF68⊦             | ICP42                      | OOODD   |

| UART 0 TX                      | *1                 | # 38    | FFFF64 <sub>H</sub> | ICR13                      | 0000ВDн |

| UART 1 RX                      | *2                 | # 39    | FFFF60 <sub>H</sub> | ICB14                      | 0000PF  |

| UART 1 TX                      | *1                 | # 40    | FFFF5C <sub>H</sub> | ICR14                      | 0000ВЕн |

| Flash Memory                   | N/A                | # 41    | FFFF58⊦             | ICD45                      | 00000   |

| Delayed interrupt              | N/A                | # 42    | FFFF54 <sub>H</sub> | ICR15                      | 0000ВГн |

|                                |                    |         |                     |                            |         |

<sup>\*1:</sup> The interrupt request flag is cleared by the El<sup>2</sup>OS interrupt clear signal.

N/A:The interrupt request flag is not cleared by the El<sup>2</sup>OS interrupt clear signal.

<sup>\*2:</sup> The interrupt request flag is cleared by the El<sup>2</sup>OS interrupt clear signal. A stop request is available.

#### Notes:

- For a peripheral module with two interrupt for a single interrupt number, both interrupt request flags are cleared by the El²OS interrupt clear signal.

- At the end of El²OS, the El²OS clear signal will be asserted for all the interrupt flags assigned to the same interrupt number. If one interrupt flag starts the El²OS and in the meantime another interrupt flag is set by hardware event, the later event is lost because the flag is cleared by the El²OS clear signal caused by the first event. So it is recommended not to use the El²OS for this interrupt number.

- If El²OS is enabled, El²OS is initiated when one of the two interrupt signals in the same interrupt control register (ICR) is asserted. This means that different interrupt sources share the same El²OS Descriptor which should be unique for each interrupt source. For this reason, when one interrupt source uses the El²OS, the other interrupt should be disabled.

Document Number: 002-07700 Rev. \*A Page 30 of 51

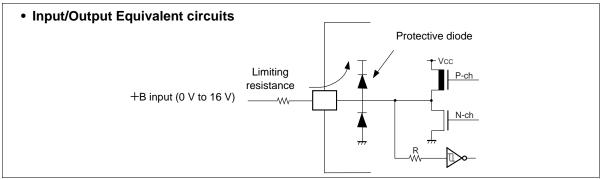

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller current is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on result.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits :

Note: : Average output current = operating current × operating efficiency

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

Document Number: 002-07700 Rev. \*A Page 32 of 51

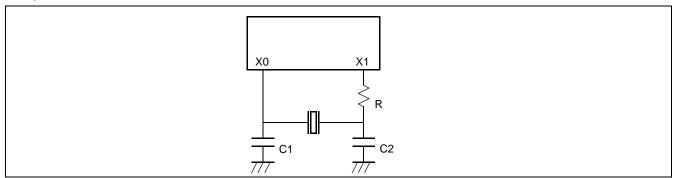

# ■ Example of Oscillation circuit

AC characteristics are set to the measured reference voltage values below.

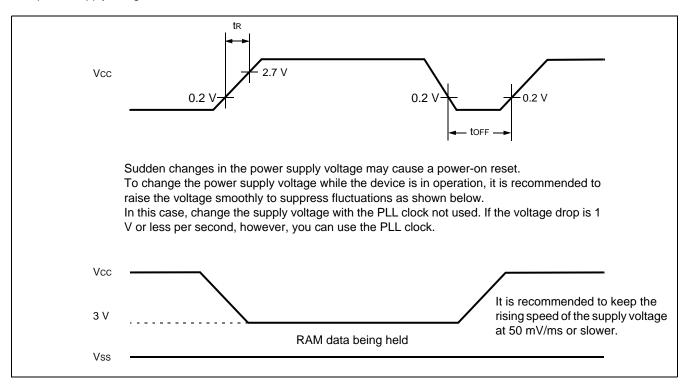

#### 11.4.3 Power On Reset

| Parameter          | Symbol         | Pin name | Condition | Value |     | Unit                        | Remarks     |  |

|--------------------|----------------|----------|-----------|-------|-----|-----------------------------|-------------|--|

|                    | Syllibol       |          | Condition | Min   | Max | Oiiit                       | iveillat K3 |  |

| Power on rise time | t <sub>R</sub> | Vcc      |           | 0.05  | 30  | ms                          | *           |  |

| Power off time     | toff           | Vcc      | _         |       |     | Due to repetitive operation |             |  |

<sup>\*:</sup> Vcc must be kept lower than 0.2 V before power-on.

#### Notes:

- The above values are used for creating a power-on reset.

- Some registers in the device are initialized only upon a power-on reset. To initialize these registers, turn on the power supply using the above values.

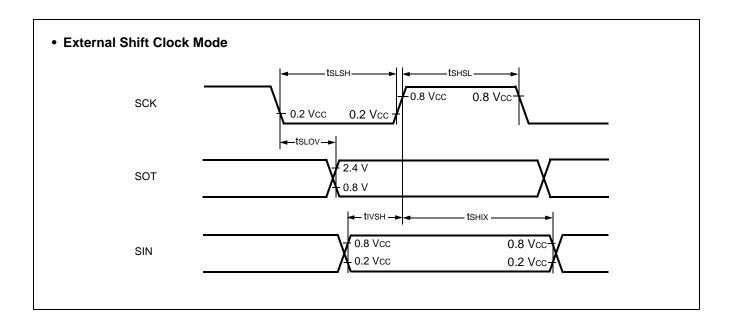

### 11.4.4 UARTO/1, Serial I/O Timing

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 ^{\circ}C to +85 ^{\circ}C)$

| Parameter                                     | Symbol        | Pin name                      | Condition                           | Value |     | Unit  | Remarks     |

|-----------------------------------------------|---------------|-------------------------------|-------------------------------------|-------|-----|-------|-------------|

| Farameter                                     | Syllibol      | Fili lialile                  | Condition                           | Min   | Max | Ollit | iveillai ks |

| Serial clock cycle time                       | tscyc         | SCK0 to SCK2                  |                                     | 8 tcp | _   | ns    |             |

| $SCK \downarrow \ \Rightarrow SOT$ delay time | tsLov         | SCK0 to SCK2,<br>SOT0 to SOT2 | Internal clock operation            | -80   | 80  | ns    |             |

| Valid SIN ⇒ SCK ↑                             | tıvsн         | SCK0 to SCK2,<br>SIN0 to SIN2 | output pins are C∟ = 80 pF + 1 TTL. | 100   | _   | ns    |             |

| SCK ↑ ⇒ Valid SIN hold time                   | <b>t</b> shix | SCK0 to SCK2,<br>SIN0 to SIN2 |                                     | 60    | _   | ns    |             |

Document Number: 002-07700 Rev. \*A Page 39 of 51

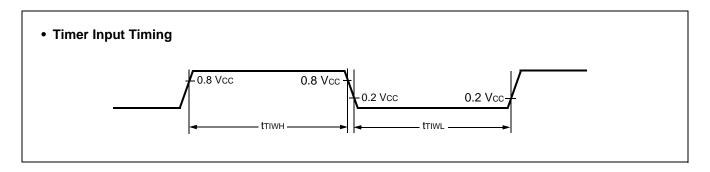

### (5) Timer Input Timing

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 ^{\circ}C to +85 ^{\circ}C)$

| Parameter         | Symbol        | Pin name   | Condition | Va    | lue | Unit | Remarks |

|-------------------|---------------|------------|-----------|-------|-----|------|---------|

|                   |               |            |           | Min   | Max |      |         |

| Input pulse width | <b>t</b> тıwн | TIN0, TIN1 | 1         | 4 tcp | _   | ns   |         |

|                   | t⊤ıw∟         | IN0 to IN3 |           |       |     |      |         |

# 11.4.5 Trigger Input Timing

(Vcc = 5.0 V $\pm$ 10%, Vss = AVss = 0.0 V, Ta = -40 °C to +85 °C)

| Parameter         | Symbol        | Pin name | Condition | Val   | lue | Unit  | Remarks                |  |

|-------------------|---------------|----------|-----------|-------|-----|-------|------------------------|--|

|                   |               |          |           | Min   | Max | Offic |                        |  |

| Input pulse width | <b>t</b> trgh |          |           | 5 tcp | _   | ns    | Under normal operation |  |

|                   | <b>t</b> TRGL |          |           | 1     | _   | μs    | In stop mode           |  |

| Parameter                     | Sym-           | Pin name   | Value      |     |            |      | Remarks                 |

|-------------------------------|----------------|------------|------------|-----|------------|------|-------------------------|

| Parameter                     | bol            |            | Min        | Тур | Max        | Unit | Remarks                 |

| Reference voltage range       | _              | AVRH       | AVRL + 3.0 | _   | AVcc       | V    |                         |

|                               | _              | AVRL       | 0          | _   | AVRH - 3.0 | V    |                         |

| Power supply current          | lΑ             | AVcc       | _          | 5   | _          | mA   |                         |

|                               | Іан            | AVcc       | _          | _   | 5          | μΑ   | *                       |

| Reference voltage current     | l <sub>R</sub> | AVRH       | _          | 400 | 600        | μΑ   | MB90V595G,<br>MB90F598G |

|                               |                |            | _          | 140 | 600        | μΑ   | MB90598G                |

|                               | Iгн            | AVRH       |            | _   | 5          | μΑ   | *                       |

| Offset between input channels | _              | AN0 to AN7 | _          | _   | 4          | LSB  |                         |

<sup>\*:</sup> When not operating A/D converter, this is the current (Vcc = AVcc = AVRH = 5.0 V) when the CPU is stopped.

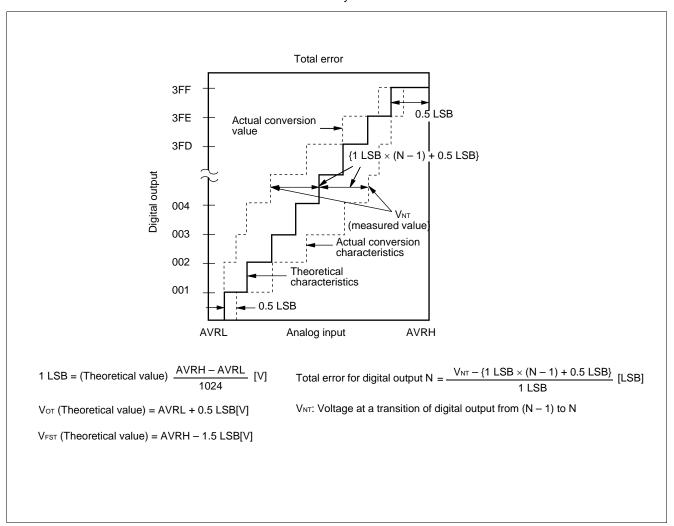

### 11.6 A/D Converter Glossary

Resolution: Analog changes that are identifiable with the A/D converter

Linearity error: The deviation of the straight line connecting the zero transition point ("00 0000 0000"  $\leftrightarrow$  "00 0000 0001") with the full-scale transition point ("11 1111 1110"  $\leftrightarrow$  "11 1111 1111") from actual conversion characteristics

Differential linearity error: The deviation of input voltage needed to change the output code by 1 LSB from the theoretical value Total error: The total error is defined as a difference between the actual value and the theoretical value, which includes zero-transition error/full-scale transition error and linearity error.