Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

|                            |                                                                         |

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 84MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                         |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 49-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 49-WLCSP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401cby6tr |

### 2.1 Compatibility with STM32F4 series

The STM32F401xB/STM32F401xC are fully software and feature compatible with the STM32F4 series (STM32F42x, STM32F43x, STM32F41x, STM32F405 and STM32F407)

The STM32F401xB/STM32F401xC can be used as drop-in replacement of the other STM32F4 products but some slight changes have to be done on the PCB board.

STM32F4x1 STM32F405/STM32F415 line STM32F407/STM32F417 line 58 PD11 57 PD10 STM32F427/STM32F437 line 56 PD9 55 PD8 54 PB15 53 PB14 STM32F429/STM32F439 line PB11 not available anymore Replaced by V<sub>CAP1</sub> 52 PB13 51 PB12 PE10 C PE11 C PE13 C PE14 C PE15 C PE15 C PB10 CAP1 PE10 E PE11 E PE13 E PE14 E PE15 E VCAP1 E VSS E VSS VDD MS31467V2

Figure 1. Compatible board design for LQFP100 package

### 3 Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices. The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F401xB/STM32F401xC devices are compatible with all ARM tools and software.

Figure 3 shows the general block diagram of the STM32F401xB/STM32F401xC.

Note: Cortex<sup>®</sup>-M4 with FPU is binary compatible with Cortex<sup>®</sup>-M3.

### 3.2 Adaptive real-time memory accelerator (ART Accelerator™)

The ART Accelerator™ is a memory accelerator which is optimized for STM32 industry-standard ARM® Cortex®-M4 with FPU processors. It balances the inherent performance advantage of the ARM® Cortex®-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 105 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 256-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 84 MHz.

### 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

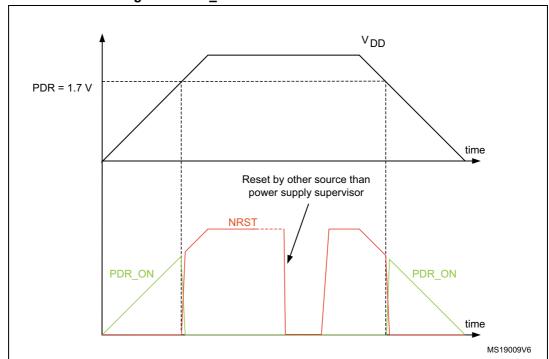

The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.7 V (see *Figure 6*).

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

Figure 6. PDR\_ON control with internal reset OFF

### 3.15 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

### 3.15.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run)

In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

- LPR is used in the Stop modes

- The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Depending on the package, one or two external ceramic capacitors should be connected on the  $V_{CAP\_1}$  and  $V_{CAP\_2}$  pins. The  $V_{CAP\_2}$  pin is only available for the LQFP100 and UFBGA100 packages.

All packages have the regulator ON feature.

### 3.15.2 Regulator OFF

The Regulator OFF is available only on the UFBGA100, which features the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V12 voltage source through  $V_{CAP-1}$  and  $V_{CAP-2}$  pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 14: General operating conditions*.

The two 2.2  $\mu$ F V<sub>CAP</sub> ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 18: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V12 logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

The RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

### 3.17 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The devices can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm/ wakeup/ tamper/ time stamp events).

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain when selected.

The devices exit the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm/ wakeup/ tamper/time stamp event occurs.

Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

### 3.18 V<sub>BAT</sub> operation

The VBAT pin allows to power the device  $V_{BAT}$  domain from an external battery, an external super-capacitor, or from  $V_{DD}$  when no external battery and an external super-capacitor are present.

V<sub>BAT</sub> operation is activated when V<sub>DD</sub> is not present.

The VBAT pin supplies the RTC and the backup registers.

Note:

When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR\_ON pin is not connected to  $V_{DD}$  (internal Reset OFF), the  $V_{BAT}$  functionality is no more available and VBAT pin should be connected to  $V_{DD}$ .

|     | 1                | 2           | 3     | 4      | 5     | 6     | 7              | 8    | 9      | 10     | 11        | 12     |

|-----|------------------|-------------|-------|--------|-------|-------|----------------|------|--------|--------|-----------|--------|

| А   | PE3              | (PE1)       | PB8   | B0070  | (PD7) | (PD5) | <br> <br>  PB4 | PB3  | PA15)  | PA14   | PA13      | (PA12) |

| В   | PE4              | (PE2)       | (PB9) | (РВ7)  | PB6   | PD6   | PD4            | PD3  | (PD1)  | C12    | PC10      | PA11   |

| С   | C13<br>NTL       | AMP PE5     | PE0   | VDD    | (PB5) |       | <br>           | PD2  | PD0    | C11    | VCAP<br>2 | PA10   |

| D   | PC14<br>OSC32_II | N (PE6)     | VSS   |        |       |       | <br>           |      |        | PA9    | PA8       | PC9    |

| E   | C15<br>OSC32     | OUT         | BYPAS | SS_REG |       |       | <br>           |      |        | PC8    | PC7       | PC6    |

| F   | PHO N            | VSS         |       |        |       |       | <br> <br> -    |      |        |        | VSS       | VSS    |

| G G | PH1<br>OSC O     | UT (VDD)    |       |        |       |       | — —<br>        |      |        |        | (VDD)     | (DD)   |

| н   | PC0              | NRS         | PDR   | DN     |       |       | <br>           |      |        | (D15)  | (D14)     | PD13   |

| J   | VSSA             | PC1         | PC2   |        |       |       |                |      |        | (D12)  | (D11)     | PD10   |

| К   | VREIT-           | PC3         | (PA2) | PA5    | PC4   |       | <br>           | PD9  | (PB11) | (PB15) | PB14      | PB13   |

| L   | VREP+            | PA0<br>WKUP | (PA3) | PA6    | PC5   | (PB2) | PE8            | PE10 | PE12   | PB10   | VCAP<br>1 | PB12   |

| М   | VDDA             | PA1         | PA4   | PA7    | (PB0) | (PB1) | PE7            | PE9  | (PE11) | PE13   | PE14      | PE15   |

<sup>1.</sup> This figure shows the package top view

## 6.3 Operating conditions

### 6.3.1 General operating conditions

Table 14. General operating conditions

| Symbol                  | Parameter                                                | Conditions                                                             | Min                 | Тур  | Max                 | Unit |

|-------------------------|----------------------------------------------------------|------------------------------------------------------------------------|---------------------|------|---------------------|------|

| ť                       | Internal ALID clock frequency                            | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01 | 0                   | -    | 60                  |      |

| f <sub>HCLK</sub>       | Internal AHB clock frequency                             | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10 | 0                   | -    | 84                  | MHz  |

| f <sub>PCLK1</sub>      | Internal APB1 clock frequency                            |                                                                        | 0                   | -    | 42                  |      |

| f <sub>PCLK2</sub>      | Internal APB2 clock frequency                            |                                                                        | 0                   | -    | 84                  |      |

| $V_{DD}$                | Standard operating voltage                               |                                                                        | 1.7 <sup>(1)</sup>  | -    | 3.6                 |      |

| V <sub>DDA</sub> (2)(3) | Analog operating voltage (ADC limited to 1.2 M samples)  | Must be the same petential as V (4)                                    | 1.7 <sup>(1)</sup>  | -    | 2.4                 |      |

| (2)(3)                  | Analog operating voltage (ADC limited to 2.4 M samples)  | Must be the same potential as V <sub>DD</sub> <sup>(4)</sup>           |                     | -    | 3.6                 |      |

| V <sub>BAT</sub>        | Backup operating voltage                                 |                                                                        | 1.65                | -    | 3.6                 |      |

| M                       | Regulator ON: 1.2 V internal                             | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 60 MHz        | 1.08 <sup>(5)</sup> | 1.14 | 1.20 <sup>(5)</sup> | V    |

| V <sub>12</sub>         | voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins   | VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz        | 1.20 <sup>(5)</sup> | 1.26 | 1.32 <sup>(5)</sup> |      |

|                         | Regulator OFF: 1.2 V external                            | Max. frequency 60 MHz.                                                 | 1.1                 | 1.14 | 1.2                 |      |

| V <sub>12</sub>         | voltage must be supplied on $V_{CAP\_1}/V_{CAP\_2}$ pins | Max. frequency 84 MHz.                                                 | 1.2                 | 1.26 | 1.32                |      |

|                         | Input voltage on RST and FT                              | $2 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$                      | -0.3                | -    | 5.5                 |      |

| $V_{IN}$                | pins <sup>(6)</sup>                                      | $V_{DD} \le 2 V$                                                       | -0.3                | -    | 5.2                 |      |

|                         | Input voltage on BOOT0 pin                               |                                                                        | 0                   | -    | 9                   |      |

|                         |                                                          | UFQFPN48                                                               | ı                   | -    | 625                 |      |

|                         | Maximum allowed package                                  | WLCSP49                                                                | ı                   | -    | 385                 | mW   |

| $P_{D}$                 | power dissipation for suffix 6                           | LQFP64                                                                 | ı                   | -    | 313                 |      |

|                         | and 7 <sup>(7)</sup>                                     | LQFP100                                                                | -                   | -    | 465                 |      |

|                         |                                                          | UFBGA100                                                               | -                   | -    | 323                 |      |

| Table 25. Typical and maximum current consumption in run mode, code with data processing |

|------------------------------------------------------------------------------------------|

| (ART accelerator enabled with prefetch) running from Flash memory                        |

|                 |                |                                                           | f <sub>HCLK</sub> |      |                        |                        |                         |      |    |    |  |

|-----------------|----------------|-----------------------------------------------------------|-------------------|------|------------------------|------------------------|-------------------------|------|----|----|--|

| Symbol          | Parameter      | Conditions                                                | (MHz)             | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |    |    |  |

|                 |                |                                                           | 84                | 31.8 | 33                     | 35                     | 36                      |      |    |    |  |

|                 |                | External clock, all peripherals enabled <sup>(2)(3)</sup> | 60                | 21.8 | 22                     | 23                     | 24                      |      |    |    |  |

|                 |                |                                                           |                   | 40   | 16.0                   | 17                     | 18                      | 19   |    |    |  |

|                 |                |                                                           | 30                | 12.9 | 14                     | 15                     | 16                      |      |    |    |  |

|                 | Supply current |                                                           | 20                | 10.4 | 11                     | 12                     | 13                      | mA   |    |    |  |

| I <sub>DD</sub> | in Run mode    |                                                           | 84                | 21.2 | 22                     | 23                     | 24                      | IIIA |    |    |  |

|                 |                |                                                           |                   |      |                        | 60                     | 15.0                    | 16   | 17 | 18 |  |

|                 |                | External clock, all peripherals disabled <sup>(3)</sup>   | 40                | 10.9 | 12                     | 13                     | 14                      |      |    |    |  |

|                 |                | P   P   1   1   1   1   1   1   1   1                     | 30                | 8.8  | 10                     | 11                     | 12                      |      |    |    |  |

|                 |                |                                                           | 20                | 7.1  | 8                      | 9                      | 10                      |      |    |    |  |

<sup>1.</sup> Guaranteed by characterization, unless otherwise specified.

Table 26. Typical and maximum current consumption in Sleep mode

| Symbol          |                      |                                                               | f                                          |                                            |                                            |                                            |                                                           |                                                           |                                           |                                           |    |     |   |    |    |  |

|-----------------|----------------------|---------------------------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------|-------------------------------------------|----|-----|---|----|----|--|

|                 | Parameter            | Conditions                                                    | f <sub>HCLK</sub><br>(MHz)                 | Тур                                        | T <sub>A</sub> = 25 °C                     | T <sub>A</sub> = 85 °C                     | T <sub>A</sub> = 105 °C                                   | Unit                                                      |                                           |                                           |    |     |   |    |    |  |

|                 |                      |                                                               | 84                                         | 16.2                                       | 17                                         | 18                                         | 19                                                        |                                                           |                                           |                                           |    |     |   |    |    |  |

|                 |                      |                                                               | 60                                         | 10.7                                       | 11                                         | 12                                         | 13                                                        |                                                           |                                           |                                           |    |     |   |    |    |  |

|                 |                      | External clock,<br>all peripherals enabled <sup>(2)</sup> (3) | all peripherals enabled <sup>(2)(3)</sup>  | External clock, all peripherals enabled <sup>(2)(3)</sup> | External clock, all peripherals enabled <sup>(2)(3)</sup> | all peripherals enabled <sup>(2)(3)</sup> | all peripherals enabled <sup>(2)(3)</sup> | 40 | 8.3 | 9 | 10 | 11 |  |

|                 |                      |                                                               | 30                                         | 6.8                                        | 7                                          | 8                                          | 9                                                         |                                                           |                                           |                                           |    |     |   |    |    |  |

| la-             | Supply current       |                                                               | 20                                         | 5.9                                        | 6                                          | 7                                          | 8                                                         | mA                                                        |                                           |                                           |    |     |   |    |    |  |

| I <sub>DD</sub> | in <b>Sleep</b> mode |                                                               | 84                                         | 5.2                                        | 6                                          | 7                                          | 8                                                         | ША                                                        |                                           |                                           |    |     |   |    |    |  |

|                 |                      |                                                               | 60                                         | 3.6                                        | 4                                          | 5                                          | 6                                                         |                                                           |                                           |                                           |    |     |   |    |    |  |

|                 |                      | External clock, all peripherals disabled <sup>(3)(4)</sup>    | all peripherals disabled <sup>(3)(4)</sup> | all peripherals disabled <sup>(3)(4)</sup> | all peripherals disabled <sup>(3)(4)</sup> | all peripherals disabled <sup>(3)(4)</sup> | all peripherals disabled <sup>(3)(4)</sup>                | 40                                                        | 2.9                                       | 3                                         | 4  | 5   |   |    |    |  |

|                 |                      |                                                               | 30                                         | 2.6                                        | 3                                          | 4                                          | 5                                                         |                                                           |                                           |                                           |    |     |   |    |    |  |

|                 |                      |                                                               | 20                                         | 2.6                                        | 3                                          | 4                                          | 5                                                         |                                                           |                                           |                                           |    |     |   |    |    |  |

<sup>1.</sup> Guaranteed by characterization, unless otherwise specified.

Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

<sup>3.</sup> When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

<sup>2.</sup> Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

<sup>4.</sup> Same current consumption for  $f_{\mbox{\scriptsize HCLK}}$  at 30 MHz and 20 MHz due to VCO running slower at 30 MHz.

Table 27. Typical and maximum current consumptions in Stop mode -  $V_{DD}$ =1.8 V

|                      |                                       |                                                | Тур                    | Max <sup>(1)</sup>     |                           |                            |      |

|----------------------|---------------------------------------|------------------------------------------------|------------------------|------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                             | Conditions                                     | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      | Main regulator usage                  | Flash in Stop mode, all                        | 109                    | 135                    | 440                       | 650                        |      |

|                      | Low power regulator usage             | oscillators OFF, no independent watchdog       | 41                     | 65                     | 310                       | 530 <sup>(2)</sup>         |      |

| I <sub>DD_STOP</sub> | Main regulator usage                  | Flash in Deep power                            |                        | 95                     | 345                       | 530                        | μΑ   |

| _                    | Low power regulator usage             | down mode, all oscillators OFF, no independent | 12                     | 36                     | 260                       | 510 <sup>(2)</sup>         |      |

|                      | Low power low voltage regulator usage | watchdog                                       | 10                     | 27                     | 230                       | 460                        |      |

- 1. Guaranteed by characterization.

- 2. Guaranteed by test in production.

Table 28. Typical and maximum current consumption in Stop mode -  $V_{DD}$ =3.3 V

| Symbol               |                                       |                                                | Тур                    | Max <sup>(1)</sup>     |                        |                            |      |

|----------------------|---------------------------------------|------------------------------------------------|------------------------|------------------------|------------------------|----------------------------|------|

|                      | Parameter                             | Conditions                                     | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      | Main regulator usage                  | Flash in Stop mode, all                        | 111                    | 140                    | 450                    | 670                        |      |

|                      | Low power regulator usage             | oscillators OFF, no independent watchdog       | 42                     | 65                     | 330                    | 560                        |      |

| I <sub>DD_STOP</sub> | Main regulator usage                  | Flash in Deep power                            | 73                     | 100                    | 360                    | 560                        | μΑ   |

|                      | Low power regulator usage             | down mode, all oscillators OFF, no independent | 12                     | 36                     | 270                    | 520                        |      |

|                      | Low power low voltage regulator usage | watchdog                                       | 10                     | 28                     | 230                    | 470                        |      |

<sup>1.</sup> Guaranteed by characterization.

Table 29. Typical and maximum current consumption in Standby mode -  $V_{DD}$ =1.8 V

|          | 7.                | •                                     |                        | •                      |                        |                         |      |

|----------|-------------------|---------------------------------------|------------------------|------------------------|------------------------|-------------------------|------|

|          |                   |                                       |                        |                        | Max <sup>(2)</sup>     | )                       |      |

| Symbol   | Parameter         | Conditions                            | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|          | Cappiy Carront in | Low-speed oscillator (LSE) and RTC ON | 2.4                    | 4.0                    | 12.0                   | 24.0                    | μA   |

| IDD_STBY | Standby mode      | RTC and LSE OFF                       | 1.8                    | 3.0 <sup>(3)</sup>     | 11.0                   | 23.0 <sup>(3)</sup>     | μΛ   |

- 1. When the PDR is OFF (internal reset is OFF), the typical current consumption is reduced by 1.2 µA.

- 2. Guaranteed by characterization, unless otherwise specified.

- 3. Guaranteed by test in production.

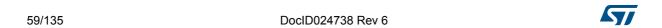

series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 24. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 38*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                    | Min | Тур  | Max  | Unit |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|------|------|------|

| R <sub>F</sub>                      | Feedback resistor                       |                               | -   | 18.4 | -    | МΩ   |

| I <sub>DD</sub>                     | LSE current consumption                 |                               | -   | -    | 1    | μA   |

| G <sub>m</sub> _crit_max            | Maximum critical crystal g <sub>m</sub> | Startup                       | -   | -    | 0.56 | μA/V |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                            | V <sub>DD</sub> is stabilized | -   | 2    | -    | s    |

Table 38. LSE oscillator characteristics ( $f_{LSE}$  = 32.768 kHz) <sup>(1)</sup>

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

<sup>1.</sup> Guaranteed by design.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is guaranteed by characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                               | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}$ = 3.3 V, LQFP100, WLCSP49,<br>$T_A$ = +25 °C, $f_{HCLK}$ = 84 MHz,<br>conforms to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP100, WLCSP49,<br>$T_A = +25$ °C, $f_{HCLK} = 84$ MHz,<br>conforms to IEC 61000-4-4 | 4A              |

Table 48. EMS characteristics for LQFP100 package

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, on LQFP100 packages and PDR ON on WLCSP49.

As a consequence, it is recommended to add a serial resistor (1  $k\Omega$  maximum) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **USB OTG full speed (FS) characteristics**

This interface is present in USB OTG FS controller.

Table 63. USB OTG FS startup time

| Symbol                              | Parameter                           | Max | Unit |

|-------------------------------------|-------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |

<sup>1.</sup> Guaranteed by design.

Table 64. USB OTG FS DC electrical characteristics

| Symbol          |                                | Parameter                       | Conditions                                      | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|-----------------|--------------------------------|---------------------------------|-------------------------------------------------|---------------------|------|---------------------|------|

|                 | $V_{DD}$                       | USB OTG FS operating voltage    |                                                 | 3.0 <sup>(2)</sup>  | -    | 3.6                 | ٧    |

| Input           | V <sub>DI</sub> <sup>(3)</sup> | Differential input sensitivity  | I(USB_FS_DP/DM)                                 | 0.2                 | -    | -                   | V    |

| levels          | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range  | Includes V <sub>DI</sub> range                  | 0.8                 | -    | 2.5                 |      |

|                 | V <sub>SE</sub> <sup>(3)</sup> | Single ended receiver threshold |                                                 | 1.3                 | i    | 2.0                 |      |

| Output          | $V_{OL}$                       | Static output level low         | $R_L$ of 1.5 k $\Omega$ to 3.6 V <sup>(4)</sup> | -                   | -    | 0.3                 | V    |

| levels          | V <sub>OH</sub>                | Static output level high        | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(4)}$        | 2.8                 | -    | 3.6                 | ٧    |

| R <sub>PD</sub> |                                | PA11, PA12<br>(USB_FS_DM/DP)    | V <sub>IN</sub> = V <sub>DD</sub>               | 17                  | 21   | 24                  |      |

|                 |                                | PA9 (OTG_FS_VBUS)               |                                                 | 0.65                | 1.1  | 2.0                 | kΩ   |

| R <sub>PU</sub> |                                | PA11, PA12<br>(USB_FS_DM/DP)    | V <sub>IN</sub> = V <sub>SS</sub>               | 1.5                 | 1.8  | 2.1                 | K22  |

|                 |                                | PA9 (OTG_FS_VBUS)               | V <sub>IN</sub> = V <sub>SS</sub>               | 0.25                | 0.37 | 0.55                |      |

<sup>1.</sup> All the voltages are measured from the local ground potential.

Note:

When VBUS sensing feature is enabled, PA9 should be left at their default state (floating input), not as alternate function. A typical 200 µA current consumption of the embedded sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 when the feature is enabled.

<sup>2.</sup> The USB OTG FS functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

<sup>3.</sup> Guaranteed by design.

<sup>4.</sup>  $R_L$  is the load connected on the USB OTG FS drivers.

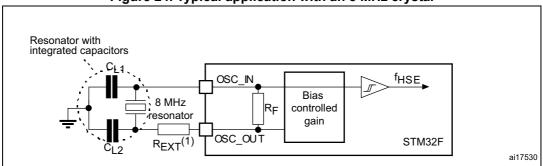

### General PCB design guidelines

Power supply decoupling should be performed as shown in Figure 42 or Figure 43, depending on whether V<sub>REF+</sub> is connected to V<sub>DDA</sub> or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

Figure 42. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

$V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA100.  $V_{REF+}$  is also available on LQFP100. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

Table 81. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

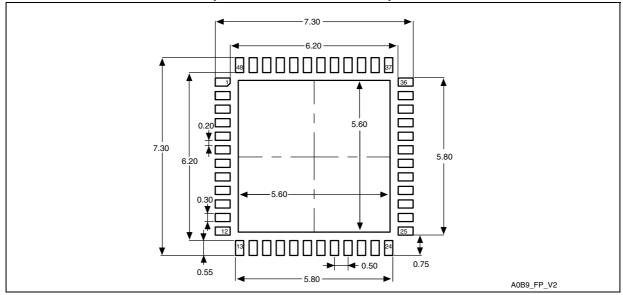

Figure 50. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat recommended footprint

1. Dimensions are in millimeters.

### 7.3 LQFP64 package information

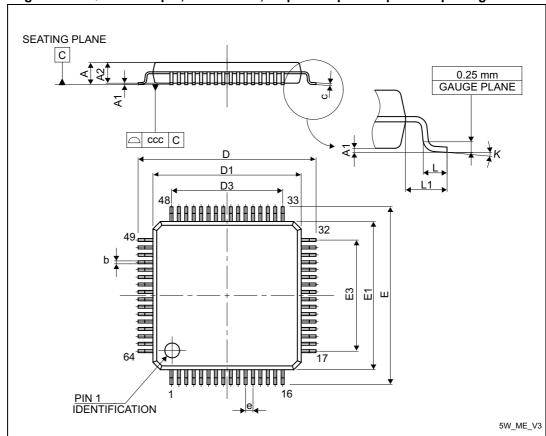

Figure 52. LQFP64 - 64-pin, 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

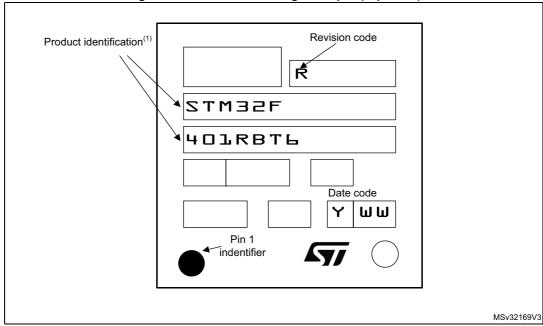

### LQFP64 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 54. LQFP64 marking example (top view)

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

Table 83. LQPF100- 100-pin, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min.        | Тур.   | Max.   | Min.                  | Тур.   | Max.   |

| Α      | -           | -      | 1.60   | -                     | -      | 0.063  |

| A1     | 0.050       | -      | 0.150  | 0.002                 | -      | 0.0059 |

| A2     | 1.350       | 1.40   | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.622                 | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| E      | 15.800      | 16.000 | 16.200 | 0.622                 | 0.6299 | 0.6378 |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| K      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |

| ccc    | 0.080       |        |        | 0.0031                |        |        |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

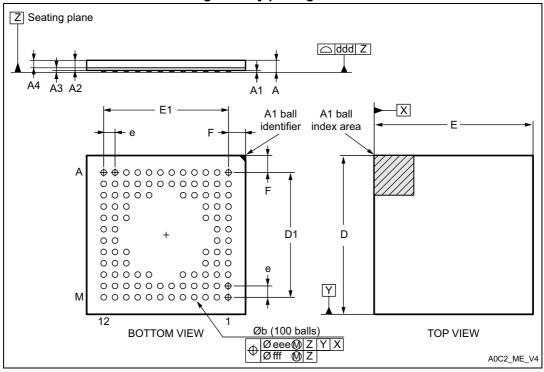

### 7.5 UFBGA100 package information

Figure 58. UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

Table 84. UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| Α      | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |

| A1     | 0.050       | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |

| A2     | 0.400       | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |

| A3     | -           | 0.130 | -     | -                     | 0.0051 | -      |

| A4     | 0.270       | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |

| b      | 0.240       | 0.290 | 0.340 | 0.0094                | 0.0114 | 0.0134 |

| D      | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |

| D1     | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |

| Е      | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |

| E1     | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| F      | 0.700       | 0.750 | 0.800 | 0.0276                | 0.0295 | 0.0315 |

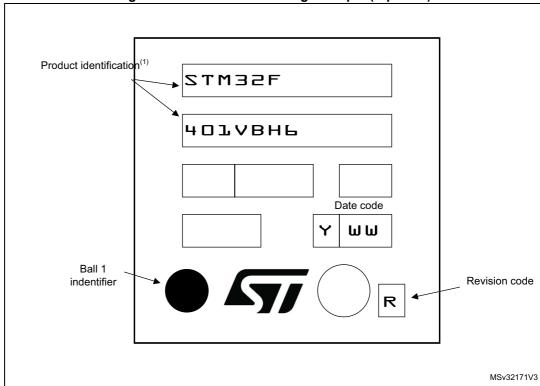

#### **UFBGA100** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 60. UFBGA100 marking example (top view)

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved