Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 84MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 49-UFBGA, WLCSP                                                          |

| Supplier Device Package    | 49-WLCSP (2.97x2.97)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401ccy6btt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

If configured as standard 16-bit timers, it has the same features as the general-purpose TIMx timers. If configured as a 16-bit PWM generator, it has full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 supports independent DMA request generation.

#### 3.19.2 General-purpose timers (TIMx)

There are seven synchronizable general-purpose timers embedded in the STM32F401xB/STM32F401xC (see *Table 4* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F401xB/STM32F401xC devices are 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit autoreload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature four independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### TIM9, TIM10 and TIM11

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

#### 3.19.3 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 3.19.4 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

| USART<br>name | Standard<br>features | Modem<br>(RTS/CTS) | LIN | SPI<br>master | irDA | Smartcard<br>(ISO 7816) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 16) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 8) | APB<br>mapping           |

|---------------|----------------------|--------------------|-----|---------------|------|-------------------------|--------------------------------------------------------|-------------------------------------------------------|--------------------------|

| USART1        | х                    | х                  | х   | х             | х    | х                       | 5.25                                                   | 10.5                                                  | APB2<br>(max.<br>84 MHz) |

| USART2        | х                    | х                  | х   | х             | х    | х                       | 2.62                                                   | 5.25                                                  | APB1<br>(max.<br>42 MHz) |

| USART6        | х                    | N.A                | х   | х             | х    | х                       | 5.25                                                   | 10.5                                                  | APB2<br>(max.<br>84 MHz) |

Table 6. USART feature comparison

# 3.22 Serial peripheral interface (SPI)

The devices feature up to four SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1 and SPI4 can communicate at up to 42 Mbit/s, SPI2 and SPI3 can communicate at up to 21 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

# 3.23 Inter-integrated sound (I<sup>2</sup>S)

Two standard  $I^2S$  interfaces (multiplexed with SPI2 and SPI3) are available. They can be operated in master or slave mode, in full duplex and simplex communication modes and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the  $I^2S$  interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I<sup>2</sup>Sx can be served by the DMA controller.

# 3.24 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for the CPU.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 kHz to 192 kHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

DocID024738 Rev 6

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4 or TIM5 timer.

# 3.29 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value. Refer to the reference manual for additional information.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

# 3.30 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.31 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F401xB/STM32F401xC through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using any high-speed channel available. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

# 4 Pinouts and pin description

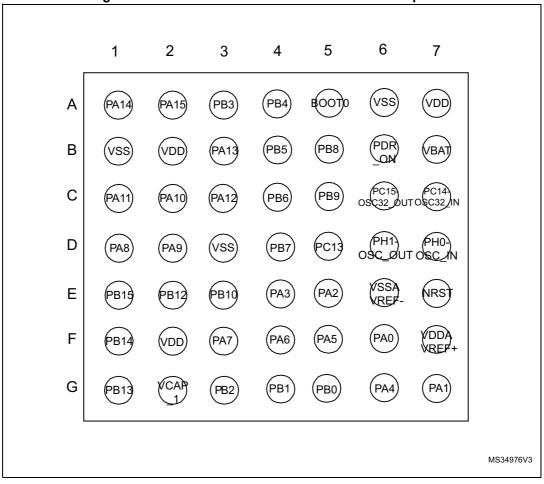

## Figure 10. STM32F401xB/STM32F401xC WLCSP49 pinout

1. The above figure shows the package top view.

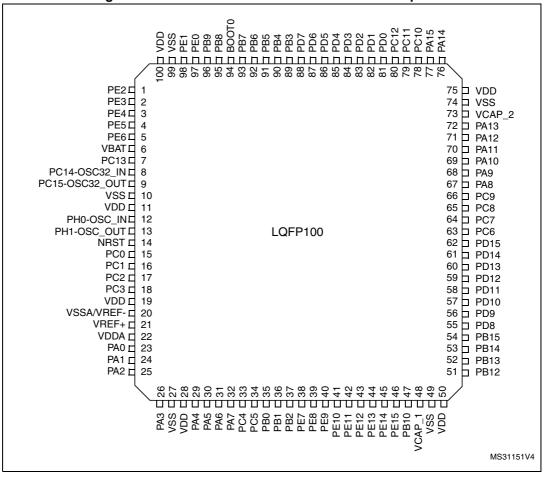

Figure 13. STM32F401xB/STM32F401xC LQFP100 pinout

1. The above figure shows the package top view.

|        | Pin     | Nun    | nber    |          |                                                      |          | e             |       |                                                                              |                         |

|--------|---------|--------|---------|----------|------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------|-------------------------|

| UQFN48 | WLCSP49 | LQFP64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                          | Additional<br>functions |

| -      | -       | 39     | 65      | E10      | PC8                                                  | I/O      | FT            | -     | USART6_CK, TIM3_CH3,<br>SDIO_D0, EVENTOUT                                    | -                       |

| -      | -       | 40     | 66      | D12      | PC9                                                  | I/O      | FT            | -     | I2S_CKIN, I2C3_SDA,<br>TIM3_CH4, SDIO_D1,<br>MCO_2, EVENTOUT                 | -                       |

| 29     | D1      | 41     | 67      | D11      | PA8                                                  | I/O      | FT            | -     | I2C3_SCL, USART1_CK,<br>TIM1_CH1, OTG_FS_SOF,<br>MCO_1, EVENTOUT             | -                       |

| 30     | D2      | 42     | 68      | D10      | PA9                                                  | I/O      | FT            | -     | I2C3_SMBA, USART1_TX,<br>TIM1_CH2, EVENTOUT                                  | OTG_FS_VBUS             |

| 31     | C2      | 43     | 69      | C12      | PA10                                                 | I/O      | FT            | -     | USART1_RX, TIM1_CH3,<br>OTG_FS_ID, EVENTOUT                                  | -                       |

| 32     | C1      | 44     | 70      | B12      | PA11                                                 | I/O      | FT            | -     | USART1_CTS, USART6_TX,<br>TIM1_CH4, OTG_FS_DM,<br>EVENTOUT                   | -                       |

| 33     | C3      | 45     | 71      | A12      | PA12                                                 | I/O      | FT            | -     | USART1_RTS, USART6_RX,<br>TIM1_ETR, OTG_FS_DP,<br>EVENTOUT                   | -                       |

| 34     | В3      | 46     | 72      | A11      | PA13 (JTMS-<br>SWDIO)                                | I/O      | FT            | -     | JTMS-SWDIO, EVENTOUT                                                         | -                       |

| -      | -       | -      | 73      | C11      | VCAP_2                                               | S        | -             | -     | -                                                                            | -                       |

| 35     | B1      | 47     | 74      | F11      | VSS                                                  | S        | -             | -     | -                                                                            | -                       |

| 36     | -       | 48     | 75      | G11      | VDD                                                  | S        | -             | -     | -                                                                            | -                       |

| -      | B2      | -      | -       | -        | VDD                                                  | S        | -             | -     | -                                                                            | -                       |

| 37     | A1      | 49     | 76      | A10      | PA14 (JTCK-<br>SWCLK)                                | I/O      | FT            | -     | JTCK-SWCLK, EVENTOUT                                                         | -                       |

| 38     | A2      | 50     | 77      | A9       | PA15 (JTDI)                                          | I/O      | FT            | -     | JTDI, SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>TIM2_CH1/TIM2_ETR, JTDI,<br>EVENTOUT | -                       |

| -      | -       | 51     | 78      | B11      | PC10                                                 | I/O      | FT            | -     | SPI3_SCK/I2S3_CK,<br>SDIO_D2, EVENTOUT                                       | -                       |

| -      | -       | 52     | 79      | C10      | PC11                                                 | I/O      | FT            | -     | I2S3ext_SD, SPI3_MISO,<br>SDIO_D3, EVENTOUT                                  | -                       |

| -      | -       | 53     | 80      | B10      | PC12                                                 | I/O      | FT            | -     | SPI3_MOSI/I2S3_SD,<br>SDIO_CK, EVENTOUT                                      | -                       |

| -      | -       | -      | 81      | C9       | PD0                                                  | I/O      | FT            | -     | EVENTOUT                                                                     | -                       |

| Table 8. STM32F401xB/STM32F401xC pin definitions (continued) |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| Bus  | Boundary address          | Peripheral          |  |  |

|------|---------------------------|---------------------|--|--|

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |  |  |

|      | 0x4000 6000 - 0x4000 6FFF | Reserved            |  |  |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |  |  |

|      | 0x4000 5800 - 0x4000 5BFF | I2C2                |  |  |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |  |  |

|      | 0x4000 4800 - 0x4000 53FF | Reserved            |  |  |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |  |  |

|      | 0x4000 4000 - 0x4000 43FF | I2S3ext             |  |  |

|      | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |  |  |

| APB1 | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |  |  |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |  |  |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |  |  |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |  |  |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |  |  |

|      | 0x4000 1000 - 0x4000 27FF | Reserved            |  |  |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |  |  |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |  |  |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |  |  |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |  |  |

# Table 10. STM32F401xB/STM32F401xC register boundary addresses (continued)

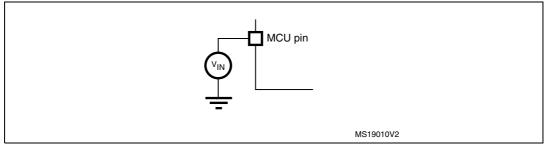

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 17*.

# 6.3 Operating conditions

# 6.3.1 General operating conditions

| Table 14 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol                     | Parameter                                                                                                               | Conditions                                                                    | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Тур  | Max                 | Unit   |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|--------|--|--|--|

| £                          |                                                                                                                         | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 60                  |        |  |  |  |

| f <sub>HCLK</sub>          | Internal AHB clock frequency                                                                                            | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 84                  | MHz    |  |  |  |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                                                                                           |                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 42                  |        |  |  |  |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                                                                                           |                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 84                  |        |  |  |  |

| $V_{DD}$                   | Standard operating voltage                                                                                              |                                                                               | 1.7 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | 3.6                 |        |  |  |  |

| V <sub>DDA</sub><br>(2)(3) | Analog operating voltage<br>(ADC limited to 1.2 M samples)                                                              | Must be the same potential as $\mathcal{V} = \begin{pmatrix} 4 \end{pmatrix}$ | 1.7 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | 2.4                 |        |  |  |  |

| (2)(3)                     | Analog operating voltage<br>(ADC limited to 2.4 M samples) Must be the same potential as V <sub>DD</sub> <sup>(4)</sup> |                                                                               | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | 3.6                 |        |  |  |  |

| V <sub>BAT</sub>           | Backup operating voltage                                                                                                |                                                                               | 1.65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 3.6                 |        |  |  |  |

|                            | Regulator ON: 1.2 V internal                                                                                            | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 60 MHz               | 1.08 <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.14 | 1.20 <sup>(5)</sup> | V      |  |  |  |

| V <sub>12</sub>            | voltage on $V_{CAP_1}/V_{CAP_2}$ pins                                                                                   | VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz               | $ \begin{array}{c c}  & 1.65 \\ \hline 01 & 1.08^{(5)} & 1 \\ \hline 10 & 1.20^{(5)} & 1 \\ \hline & 1.1 & 1 \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.26 | 1.32 <sup>(5)</sup> |        |  |  |  |

|                            | Regulator OFF: 1.2 V external                                                                                           | Max. frequency 60 MHz.                                                        | 0       -       6         0       -       8         0       -       4         0       -       8         1.7 <sup>(1)</sup> -       3         1.7 <sup>(1)</sup> -       2         2.4       -       3         1.65       -       3         1.08 <sup>(5)</sup> 1.14       1.2         1.20 <sup>(5)</sup> 1.26       1.3         1.1       1.14       1.3         1.2       1.26       1.3         0.1       1.26       1.3         0.1       1.26       1.3         0.1       1.4       1.2         1.20 <sup>(5)</sup> 1.26       1.3         0.1       1.26       1.3         0.1       1.26       1.3         0.1       1.26       1.3         0.1       1.26       1.3         0.1       5.0       5.0         -       -       62         -       -       3.4         -       -       3.4 | 1.14 | 1.2                 |        |  |  |  |

| V <sub>12</sub>            | voltage must be supplied on $V_{CAP_1}/V_{CAP_2}$ pins                                                                  | Max. frequency 84 MHz.                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.32 |                     |        |  |  |  |

|                            | Input voltage on RST and FT                                                                                             | $2 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                      | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 5.5                 |        |  |  |  |

| $V_{IN}$                   | pins <sup>(6)</sup>                                                                                                     | $V_{DD} \leq 2 V$                                                             | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 5.2                 |        |  |  |  |

|                            | Input voltage on BOOT0 pin                                                                                              |                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 9                   |        |  |  |  |

|                            |                                                                                                                         | UFQFPN48                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 625                 |        |  |  |  |

|                            | Maximum allowed package                                                                                                 | WLCSP49                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 385                 | mW     |  |  |  |

| PD                         | power dissipation for suffix 6                                                                                          | LQFP64                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 313                 |        |  |  |  |

|                            | and 7 <sup>(7)</sup>                                                                                                    | LQFP100                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 465                 | $\neg$ |  |  |  |

|                            |                                                                                                                         | UFBGA100                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 323                 |        |  |  |  |

## 6.3.4 Operating conditions at power-up / power-down (regulator OFF)

| - |                   |                                              |            |     |     |       |  |  |  |  |

|---|-------------------|----------------------------------------------|------------|-----|-----|-------|--|--|--|--|

|   | Symbol            | Parameter                                    | Conditions | Min | Max | Unit  |  |  |  |  |

|   | t                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | 8   |       |  |  |  |  |

|   | t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   | μs/V  |  |  |  |  |

|   | t                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | 8   | μ5/ ν |  |  |  |  |

|   | t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | 8   |       |  |  |  |  |

Subject to general operating conditions for T<sub>A</sub>.

## Table 18. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

To reset the internal logic at power-down, a reset must be applied on pin PA0 when V<sub>DD</sub> reach below 1.08 V.

Note: This feature is only available for UFBGA100 package.

#### 6.3.5 Embedded reset and power control block characteristics

The parameters given in *Table 19* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage @ 3.3V.

| Symbol                              | Parameter                                        | Conditions                      | Min                 | Тур  | Max    | Unit |

|-------------------------------------|--------------------------------------------------|---------------------------------|---------------------|------|--------|------|

| V <sub>PVD</sub>                    |                                                  | PLS[2:0]=000 (rising edge)      | 2.09                | 2.14 |        |      |

|                                     |                                                  | PLS[2:0]=000 (falling edge)     | 1.98                | 2.04 | 2.08   |      |

|                                     |                                                  | PLS[2:0]=001 (rising edge)      | 2.23                | 2.30 | 2.37   |      |

|                                     |                                                  | PLS[2:0]=001 (falling edge)     | 2.13                | 2.19 | 2.25   |      |

|                                     |                                                  | PLS[2:0]=010 (rising edge)      | 2.39                | 2.45 | 2.51   |      |

|                                     |                                                  | PLS[2:0]=010 (falling edge)     | 2.29                | 2.35 | 2.39   |      |

|                                     | Programmable voltage<br>detector level selection | PLS[2:0]=011 (rising edge)      | 2.54                |      |        |      |

|                                     |                                                  | PLS[2:0]=011 (falling edge)     | 2.44                |      |        |      |

|                                     |                                                  | PLS[2:0]=100 (rising edge)      | 2.70                | 2.76 | 2.82 V |      |

|                                     |                                                  | PLS[2:0]=100 (falling edge)     | 2.59                | 2.66 | 2.71   |      |

|                                     |                                                  | PLS[2:0]=101 (rising edge)      | 2.86                | 2.93 | 2.99   |      |

|                                     |                                                  | PLS[2:0]=101 (falling edge)     | 2.65                | 2.84 | 2.92   | 2    |

|                                     |                                                  | PLS[2:0]=110 (rising edge) 2.96 |                     | 3.03 | 3.10   |      |

|                                     |                                                  | PLS[2:0]=110 (falling edge)     | 2.85                | 2.93 | 3 2.99 |      |

|                                     |                                                  | PLS[2:0]=111 (rising edge)      | 3.07                | 3.14 | 3.21   |      |

|                                     |                                                  | PLS[2:0]=111 (falling edge)     |                     |      |        |      |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis                                   |                                 | -                   | 100  | -      | mV   |

| \/                                  | Power-on/power-down                              | Falling edge                    | 1.60 <sup>(1)</sup> | 1.68 | 1.76   | V    |

| V <sub>POR/PDR</sub>                | reset threshold                                  | Rising edge                     | 1.64                | 1.72 | 1.80   | v    |

#### Table 19. Embedded reset and power control block characteristics

#### **On-chip peripheral current consumption**

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- The ART accelerator is ON.

- Voltage Scale 2 mode selected, internal digital voltage V12 = 1.26 V.

- HCLK is the system clock at 84 MHz. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

| Perip                 | heral               | I <sub>DD</sub> (typ) | Unit     |

|-----------------------|---------------------|-----------------------|----------|

|                       | GPIOA               | 1.55                  |          |

|                       | GPIOB               | 1.55                  |          |

|                       | GPIOC               | 1.55                  |          |

|                       | GPIOD               | 1.55                  |          |

| AHB1<br>(up to 84MHz) | GPIOE               | 1.55                  | µA/MHz   |

| (up to o miniz)       | GPIOH               | 1.55                  |          |

|                       | CRC                 | 0.36                  |          |

|                       | DMA1                | 20.24                 |          |

|                       | DMA2                | 21.07                 |          |

|                       | TIM2                | 11.19                 |          |

|                       | TIM3                | 8.57                  |          |

|                       | TIM4                | 8.33                  |          |

|                       | TIM5                | 11.19                 |          |

|                       | PWR                 | 0.71                  |          |

| APB1                  | USART2              | 3.33                  |          |

| (up to 42MHz)         | I2C1/2/3            | 3.10                  | – μA/MHz |

|                       | SPI2 <sup>(1)</sup> | 2.62                  |          |

|                       | SPI3 <sup>(1)</sup> | 2.86                  |          |

|                       | 1282                | 1.90                  |          |

|                       | 1283                | 1.67                  |          |

|                       | WWDG                | 0.71                  |          |

| AHB2<br>(up to 84MHz) | OTG_FS              | 23.93                 | µA/MHz   |

## Table 33. Peripheral current consumption

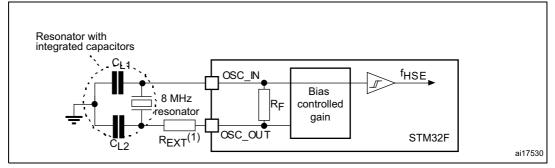

series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 38*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                    | Min | Тур  | Max  | Unit |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|------|------|------|

| R <sub>F</sub>                      | Feedback resistor                       |                               | -   | 18.4 | -    | MΩ   |

| I <sub>DD</sub>                     | LSE current consumption                 |                               | -   | -    | 1    | μA   |

| G <sub>m</sub> _crit_max            | Maximum critical crystal g <sub>m</sub> | Startup                       | -   | -    | 0.56 | μA/V |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                            | $V_{\text{DD}}$ is stabilized | -   | 2    | -    | s    |

Table 38. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is guaranteed by characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

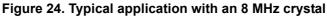

Figure 27. ACC<sub>LSI</sub> versus temperature

## 6.3.10 PLL characteristics

The parameters given in *Table 41* and *Table 42* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                             | Condition          | Conditions         |                     | Тур  | Max  | Unit |

|------------------------|---------------------------------------|--------------------|--------------------|---------------------|------|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        |                    |                    | 0.95 <sup>(2)</sup> | 1    | 2.10 | MHz  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           |                    |                    | 24                  | -    | 84   | MHz  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock |                    |                    | -                   | 48   | 75   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        |                    |                    | 192                 | -    | 432  | MHz  |

| t <sub>LOCK</sub>      | PLL lock time                         | VCO freq = 192 MHz |                    | 75                  | -    | 200  |      |

|                        |                                       | VCO freq = 432 I   | 100                | -                   | 300  | μs   |      |

|                        |                                       |                    | RMS                | -                   | 25   | -    |      |

|                        | Cycle-to-cycle jitter                 | System clock       | peak<br>to<br>peak | -                   | ±150 | -    |      |

| Jitter <sup>(3)</sup>  |                                       | 84 MHz             | RMS                | -                   | 15   | -    | ps   |

|                        | Period Jitter                         |                    | peak<br>to<br>peak | -                   | ±200 | -    |      |

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                               | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, WLCSP49,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 84 MHz,<br>conforms to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, WLCSP49,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 84 MHz,<br>conforms to IEC 61000-4-4 | 4A              |

Table 48. EMS characteristics for LQFP100 package

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, on LQFP100 packages and PDR ON on WLCSP49.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$  maximum) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol                         | Parameter                                | Conditions                                               | Min                                 | Max                | Unit |

|--------------------------------|------------------------------------------|----------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup>                                 | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = +8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V | V <sub>DD</sub> -0.4                | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup>                                  | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> =+8 mA<br>2.7 V ⊴V <sub>DD</sub> ⊴3.6 V  | 2.4                                 | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +20 mA                                 | -                                   | 1.3 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 2.7 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -1.3 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +6 mA                                  | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.8 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA                                  | -                                   | 0.4 <sup>(5)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.7 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  | v    |

Table 55. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Guaranteed by characterization.

- 5. Guaranteed by design.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 31* and *Table 56*, respectively.

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit Symbol Parameter<br>value <sup>(1)</sup> |                                                  | Conditions                                                                      | Min                                                         | Тур | Мах | Unit |     |

|----------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|------|-----|

|                                                                |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 4    |     |

|                                                                | f                                                | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 2    | MHz |

|                                                                | <sup>I</sup> max(IO)out                          |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 8    |     |

| 00                                                             |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 4    |     |

|                                                                | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V to<br>3.6 V | -   | -   | 100  | ns  |

| Table 56 | . I/O AC | characteristics <sup>(1)(2)</sup> |

|----------|----------|-----------------------------------|

|----------|----------|-----------------------------------|

#### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k-0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       | f 40 MUL                                                    | ±3  | ±4                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 |      |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                 | ±1  | ±2                 |      |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |

1. Guaranteed by characterization.

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

Table 68. ADC accuracy at f<sub>ADC</sub> = 30 MHz

1. Guaranteed by characterization.

Table 69. ADC accuracy at f<sub>ADC</sub> = 36 MHz

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REE</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |

1. Guaranteed by characterization.

|                   |                                        |             |     | - ( | in a ca, |      |

|-------------------|----------------------------------------|-------------|-----|-----|----------|------|

| Symbol            | Parameter                              | Conditions  | Min | Тур | Мах      | Unit |

| CMD, D inp        | uts (referenced to CK) in SD default n | node        |     |     |          |      |

| t <sub>ISUD</sub> | Input setup time SD                    | fpp = 24MHz | 1.5 | -   | -        |      |

| t <sub>IHD</sub>  | Input hold time SD                     | fpp = 24MHz | 0.5 | -   | -        | ns   |

| CMD, D out        | puts (referenced to CK) in SD default  | mode        |     |     |          |      |

| t <sub>OVD</sub>  | Output valid default time SD           | fpp =24MHz  | -   | 4.5 | 6.5      |      |

| t <sub>OHD</sub>  | Output hold default time SD            | fpp =24MHz  | 3.5 | -   | -        | ns   |

# Table 77. Dynamic characteristics: SD / MMC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by characterization results.

2.  $V_{DD}$  = 2.7 to 3.6 V.

## 6.3.25 RTC characteristics

#### Table 78. RTC characteristics

| Symbol | Parameter                                  | Conditions                                          | Min | Max |

|--------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

| Cumhal |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min.   | Тур.        | Max.   | Min.   | Тур.                  | Max.   |

| А      | -      | -           | 1.60   | -      | -                     | 0.063  |

| A1     | 0.050  | -           | 0.150  | 0.002  | -                     | 0.0059 |

| A2     | 1.350  | 1.40        | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.622  | 0.6299                | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| D3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| Е      | 15.800 | 16.000      | 16.200 | 0.622  | 0.6299                | 0.6378 |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| E3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |

| К      | 0.0°   | 3.5°        | 7.0°   | 0.0°   | 3.5°                  | 7.0°   |

| CCC    |        | 0.080       | •      |        | 0.0031                | •      |

#### Table 83. LQPF100- 100-pin, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

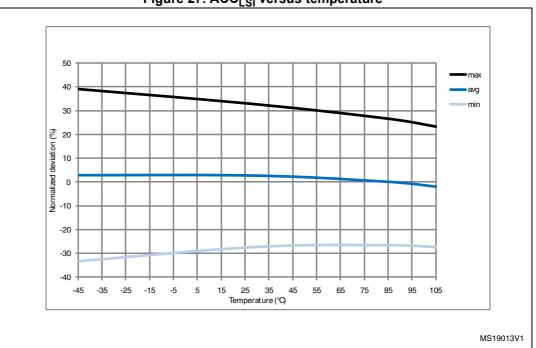

#### Figure 56. LQFP100 recommended footprint

1. Dimensions are in millimeters.

# 7.6 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 14: General operating conditions on page 59.*

The maximum chip-junction temperature,  $T_J$  max., in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (PD \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- PD max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (PD max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}\!/\!\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol | Parameter                                       | Value | Unit |

|--------|-------------------------------------------------|-------|------|

| ΘjA    | Thermal resistance junction-ambient<br>UFQFPN48 | 32    |      |

|        | Thermal resistance junction-ambient<br>WLCSP49  | 52    |      |

|        | Thermal resistance junction-ambient<br>LQFP64   | 50    | °C/W |

|        | Thermal resistance junction-ambient<br>LQFP100  | 42    |      |

|        | Thermal resistance junction-ambient<br>UFBGA100 | 56    |      |

#### Table 86. Package thermal characteristics

#### 7.6.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Date                | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>06-Aug-2015 | S        | ChangesChanged current consumption to 128 $\mu$ A/MHz on cover page.Updated Table 3: Regulator ON/OFF and internal power supplysupervisor availability for UFQFPN48.Updated Figure 10: STM32F401xB/STM32F401xC WLCSP49 pinoutto show top view instead of bump view.Renamed VCAP1/2 into VCAP 1/2 in Figure 10:STM32F401xB/STM32F401xC WLCSP49 pinout, Figure 11:STM32F401xB/STM32F401xC UFQFPN48 pinout, Figure 13:STM32F401xB/STM32F401xC UFQFPN48 pinout, Figure 13:STM32F401xB/STM32F401xC UFQFPN48 pinout,In whole Section 6: Electrical characteristics, modified notes related tocharacteristics guaranteed by design and by tests duringcharacteristics.Updated Table 39: HSI oscillator characteristics.Updated Table 39: HSI oscillator characteristics.Updated Table 39: HSI oscillator characteristics.Added tsp in Table 59: 1 <sup>2</sup> C characteristics.Added tsp in Table 59: 1 <sup>2</sup> C characteristics.Added WLCSP49 Figure 47: WLCSP49 0.4 mm pitch wafer level chipscale recommended footprint and Table 80: WLCSP49 recommendedPCB design rules (0.4 mm pitch). Added Section : WLCSP49 devicemarking.Updated Section : LQFP64 device marking.Updated Table 82: LQFP64 - 64-pin, 10 x 10 mm, 64-pin low-profilequad flat package mechanical data and Section : LQFP100device mar |