# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 84MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 96K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401ceu6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        |                     | 3.19.3                                                                                                                                    | Independent watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 27                                                                                                        |

|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

|        |                     | 3.19.4                                                                                                                                    | Window watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 27                                                                                                        |

|        |                     | 3.19.5                                                                                                                                    | SysTick timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 28                                                                                                        |

|        | 3.20                | Inter-in                                                                                                                                  | tegrated circuit interface (I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 28                                                                                                        |

|        | 3.21                | Univers                                                                                                                                   | sal synchronous/asynchronous receiver transmitters (USART) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 28                                                                                                        |

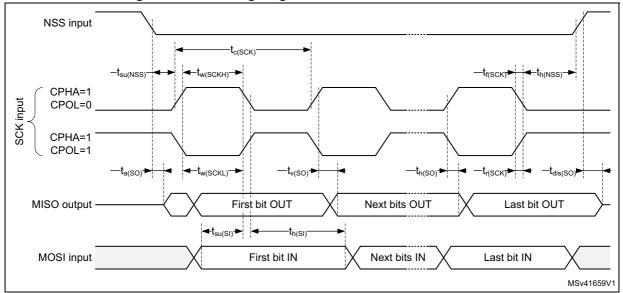

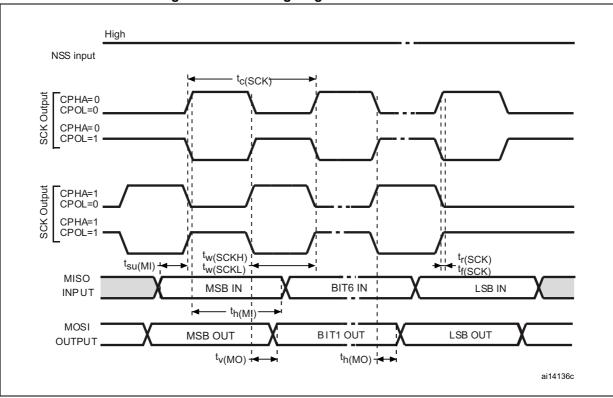

|        | 3.22                | Serial p                                                                                                                                  | peripheral interface (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 29                                                                                                        |

|        | 3.23                | Inter-in                                                                                                                                  | tegrated sound (I <sup>2</sup> S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 29                                                                                                        |

|        | 3.24                | Audio F                                                                                                                                   | PLL (PLLI2S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 29                                                                                                        |

|        | 3.25                | Secure                                                                                                                                    | e digital input/output interface (SDIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 30                                                                                                        |

|        | 3.26                | Univers                                                                                                                                   | sal serial bus on-the-go full-speed (OTG_FS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 30                                                                                                        |

|        | 3.27                | Genera                                                                                                                                    | al-purpose input/outputs (GPIOs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 30                                                                                                        |

|        | 3.28                | Analog                                                                                                                                    | -to-digital converter (ADC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 30                                                                                                        |

|        | 3.29                | Tempe                                                                                                                                     | rature sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 31                                                                                                        |

|        | 3.30                | Serial v                                                                                                                                  | wire JTAG debug port (SWJ-DP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 31                                                                                                        |

|        | 3.31                | Embed                                                                                                                                     | lded Trace Macrocell™                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 31                                                                                                        |

|        |                     |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                             |

| 4      | Pino                | uts and                                                                                                                                   | pin description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 32                                                                                                        |

|        |                     |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                             |

| 5      | Mem                 | ory map                                                                                                                                   | pping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                          |

| 5<br>6 |                     |                                                                                                                                           | pping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                             |

|        |                     | rical ch                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54                                                                                                          |

|        | Elect               | rical ch                                                                                                                                  | aracteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . <b>54</b><br>. 54                                                                                         |

|        | Elect               | rical ch<br>Parame                                                                                                                        | eter conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . <b>54</b><br>. 54<br>. 54                                                                                 |

|        | Elect               | rical ch<br>Parame<br>6.1.1                                                                                                               | eter conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . <b>54</b><br>. 54<br>. 54<br>. 54                                                                         |

|        | Elect               | Frical ch<br>Parame<br>6.1.1<br>6.1.2                                                                                                     | eter conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54<br>54<br>54<br>54<br>54                                                                                  |

|        | Elect               | Frical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3                                                                                            | eter conditions<br>Minimum and maximum values<br>Typical values<br>Typical curves                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54<br>54<br>54<br>54<br>54<br>54<br>54                                                                      |

|        | Elect               | Frical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                                   | eter conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54<br>54<br>54<br>54<br>54<br>54<br>54<br>55                                                                |

|        | Elect               | Frical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                                          | maracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage                                                                                                                                                                                                                                                                                                                                                                      | 54<br>54<br>54<br>54<br>54<br>54<br>54<br>55<br>55<br>56                                                    |

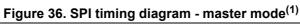

|        | Elect               | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7                                                         | naracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme                                                                                                                                                                                                                                                                                                                                          | 54<br>54<br>54<br>54<br>54<br>54<br>55<br>55<br>56<br>57                                                    |

|        | Elect               | Frical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolu                                              | <b>naracteristics</b> eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Current consumption measurement                                                                                                                                                                                                                                                                                                   | 54<br>54<br>54<br>54<br>54<br>55<br>55<br>56<br>57<br>57                                                    |

|        | <b>Elect</b><br>6.1 | rrical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolu<br>Operat<br>6.3.1                           | haracteristics         eter conditions         Minimum and maximum values         Typical values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions                                                                                                                                                                                    | 54<br>54<br>54<br>54<br>54<br>55<br>55<br>56<br>57<br>57<br>59<br>. 59                                      |

|        | <b>Elect</b><br>6.1 | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolut<br>Operat<br>6.3.1<br>6.3.2                  | maracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions         VCAP_1/VCAP_2 external capacitors                                                                                                                                                                 | . <b>54</b><br>. 54<br>. 54<br>. 54<br>. 54<br>. 55<br>. 55<br>. 57<br>. 57<br>. 59<br>. 59<br>. 61         |

|        | <b>Elect</b><br>6.1 | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolu<br>Operat<br>6.3.1<br>6.3.2<br>6.3.3          | maracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions         VCAP_1/VCAP_2 external capacitors         Operating conditions at power-up/power-down (regulator ON)                                                                                              | 54<br>54<br>54<br>54<br>54<br>55<br>55<br>57<br>57<br>57<br>59<br>59<br>59<br>61<br>59                      |

|        | <b>Elect</b><br>6.1 | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolu<br>Operat<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | maracteristics         eter conditions         Minimum and maximum values         Typical values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions         VCAP_1/VCAP_2 external capacitors         Operating conditions at power-up/power-down (regulator ON)         Operating conditions at power-up / power-down (regulator OFF) | . <b>54</b><br>. 54<br>. 54<br>. 54<br>. 55<br>. 55<br>. 55<br>. 57<br>. 59<br>. 59<br>. 59<br>. 61<br>. 61 |

|        | <b>Elect</b><br>6.1 | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolu<br>Operat<br>6.3.1<br>6.3.2<br>6.3.3          | maracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions         VCAP_1/VCAP_2 external capacitors         Operating conditions at power-up/power-down (regulator ON)                                                                                              | . <b>54</b><br>. 54<br>. 54<br>. 54<br>. 55<br>. 55<br>. 55<br>. 57<br>. 59<br>. 59<br>. 59<br>. 61<br>. 61 |

## 3.15.3 Regulator ON/OFF and internal power supply supervisor availability

| Package  | Regulator ON                    | Regulator OFF                   | Power supply supervisor ON | Power supply supervisor OFF                      |

|----------|---------------------------------|---------------------------------|----------------------------|--------------------------------------------------|

| UFQFPN48 | Yes                             | No                              | Yes                        | No                                               |

| WLCSP49  | Yes                             | No                              | Yes<br>PDR_ON set to VDD   | Yes<br>PDR_ON external<br>control <sup>(1)</sup> |

| LQFP64   | Yes                             | No                              | Yes                        | No                                               |

| LQFP100  | Yes                             | No                              | Yes                        | No                                               |

| UFBGA100 | Yes<br>BYPASS_REG set to<br>VSS | Yes<br>BYPASS_REG set to<br>VDD | Yes<br>PDR_ON set to VDD   | Yes<br>PDR_ON external<br>control <sup>(1)</sup> |

Table 3. Regulator ON/OFF and internal power supply supervisor availability

1. Refer to Section 3.14: Power supply supervisor

## 3.16 Real-time clock (RTC) and backup registers

The backup domain includes:

- The real-time clock (RTC)

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are performed automatically. The RTC features a reference clock detection, a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes. The sub-seconds value is also available in binary format.

It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.17: Low-power modes).

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

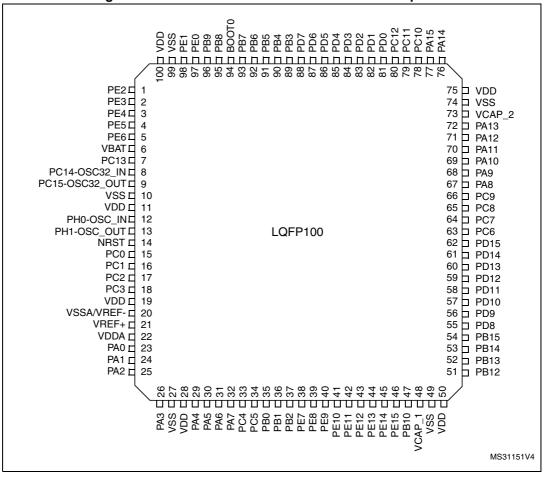

Figure 13. STM32F401xB/STM32F401xC LQFP100 pinout

1. The above figure shows the package top view.

5

DocID024738 Rev 6

45/135

|        | Table 9. Alternate function mapping (continued) |              |           |                     |                          |                    |                                       |                          |                                 |        |               |         |      |             |      |      |              |

|--------|-------------------------------------------------|--------------|-----------|---------------------|--------------------------|--------------------|---------------------------------------|--------------------------|---------------------------------|--------|---------------|---------|------|-------------|------|------|--------------|

|        |                                                 | AF00         | AF01      | AF02                | AF03                     | AF04               | AF05                                  | AF06                     | AF07                            | AF08   | AF09          | AF10    | AF11 | AF12        | AF13 | AF14 | AF15         |

|        | Port                                            | SYS_AF       | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/SPI2/<br>I2S2/SPI3/<br>I2S3/SPI4 | SPI2/I2S2/<br>SPI3/ I2S3 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6 | 12C2/<br>12C3 | OTG1_FS |      | SDIO        |      |      |              |

|        | PB0                                             | -            | TIM1_CH2N | TIM3_CH3            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB1                                             | -            | TIM1_CH3N | TIM3_CH4            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB2                                             | -            | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB3                                             | JTDO-<br>SWO | TIM2_CH2  | -                   | -                        | -                  | SPI1_SCK                              | SPI3_SCK/<br>I2S3_CK     | -                               | -      | I2C2_SDA      | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB4                                             | JTRST        | -         | TIM3_CH1            | -                        | -                  | SPI1_<br>MISO                         | SPI3_MISO                | I2S3ext_S<br>D                  | -      | I2C3_SDA      | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB5                                             | -            | -         | TIM3_CH2            | -                        | I2C1_<br>SMBA      | SPI1<br>_MOSI                         | SPI3_MOSI/<br>I2S3_SD    | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB6                                             | -            | -         | TIM4_CH1            | -                        | I2C1_SCL           | -                                     | -                        | USART1_<br>TX                   | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

| E B    | PB7                                             | -            | -         | TIM4_CH2            | -                        | I2C1_SDA           | -                                     | -                        | USART1_<br>RX                   | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

| Port B | PB8                                             | -            | -         | TIM4_CH3            | TIM10_CH1                | I2C1_SCL           | -                                     | -                        | -                               | -      | -             | -       | -    | SDIO_<br>D4 | -    | -    | EVENT<br>OUT |

|        | PB9                                             | -            | -         | TIM4_CH4            | TIM11_CH1                | I2C1_SDA           | SPI2_NSS/I<br>2S2_WS                  | -                        | -                               | -      | -             | -       | -    | SDIO_<br>D5 | -    | -    | EVENT<br>OUT |

|        | PB10                                            | -            | TIM2_CH3  | -                   | -                        | I2C2_SCL           | SPI2_SCK/I<br>2S2_CK                  | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB11                                            | -            | TIM2_CH4  | -                   | -                        | I2C2_SDA           | -                                     | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB12                                            | -            | TIM1_BKIN | -                   | -                        | I2C2_<br>SMBA      | SPI2_NSS/I<br>2S2_WS                  | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB13                                            | -            | TIM1_CH1N | -                   | -                        | -                  | SPI2_SCK/I<br>2S2_CK                  | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB14                                            | -            | TIM1_CH2N | -                   | -                        | -                  | SPI2_MISO                             | I2S2ext_SD               | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB15                                            | RTC_<br>REFN | TIM1_CH3N | -                   | -                        | -                  | SPI2_MOSI<br>/I2S2_SD                 | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6000 - 0x4000 6FFF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | I2C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 4800 - 0x4000 53FF | Reserved            |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

|      | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

|      | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

| APB1 | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 1000 - 0x4000 27FF | Reserved            |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 10. STM32F401xB/STM32F401xC register boundary addresses (continued)

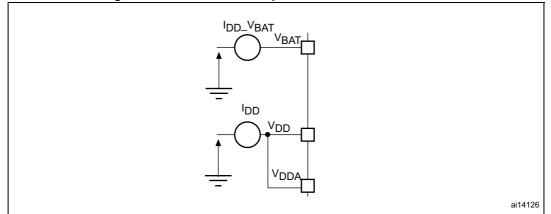

## 6.1.7 Current consumption measurement

#### Figure 19. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard. Extended mission profiles are available on demand.

| Symbol                            | Ratings                                                                        | Min                                                      | Мах                  | Unit |  |

|-----------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|------|--|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}, V_{DD}$ and $V_{BAT})^{(1)}$ | -0.3                                                     | 4.0                  |      |  |

|                                   | Input voltage on FT pins <sup>(2)</sup>                                        |                                                          | V <sub>DD</sub> +4.0 | V    |  |

| V <sub>IN</sub>                   | Input voltage on any other pin                                                 |                                                          | 4.0                  |      |  |

|                                   | Input voltage for BOOT0                                                        | V <sub>SS</sub>                                          | 9.0                  |      |  |

| $ \Delta V_{DDx} $                | Variations between different V <sub>DD</sub> power pins                        | -                                                        | 50                   |      |  |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins including V <sub>REF-</sub>   |                                                          | 50                   | mV   |  |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                             | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical  |      |  |

## Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2.  $V_{IN}$  maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

| Symbol                               | Ratings                                                                             | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------------------|-------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all V <sub>DD_x</sub> power lines (source) <sup>(1)</sup> | 160   |      |

| $\Sigma I_{VSS}$                     | Total current out of sum of all $V_{SS_x}$ ground lines (sink) <sup>(1)</sup>       | -160  |      |

| I <sub>VDD</sub>                     | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>      | 100   |      |

| I <sub>VSS</sub>                     | Maximum current out of each $V_{SS_x}$ ground line (sink) <sup>(1)</sup>            | -100  |      |

|                                      | Output current sunk by any I/O and control pin                                      | 25    |      |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/O and control pin                                   | -25   | mA   |

| ΣI                                   | Total output current sunk by sum of all I/O and control pins $^{(2)}$               |       |      |

| ΣΙ <sub>ΙΟ</sub>                     | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup>     | -120  |      |

| (3)                                  | Injected current on FT pins <sup>(4)</sup>                                          | 5/10  |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on NRST and B pins <sup>(4)</sup>                                  | _5/+0 |      |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>             | ±25   |      |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.20: 12-bit ADC characteristics.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol            | Ratings                                                                                   | Value                   | Unit |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------|------|

| T <sub>STG</sub>  | Storage temperature range                                                                 | –65 to +150             |      |

| Τ <sub>J</sub>    | Maximum junction temperature                                                              | 125                     |      |

| T <sub>LEAD</sub> | Maximum lead temperature during soldering<br>(WLCSP49, LQFP64/100, UFQFPN48,<br>UFBGA100) | see note <sup>(1)</sup> | °C   |

#### Table 13. Thermal characteristics

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb assembly), the ST ECOPACK<sup>®</sup> 7191395 specification, and the European directive on Restrictions on Hazardous Substances (ROHS directive 2011/65/EU, July 2011).

## 6.3 Operating conditions

## 6.3.1 General operating conditions

| Table 14 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol                     | Parameter                                                                           | Conditions                                                             | Min                 | Тур  | Max                 | Unit |

|----------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|------|---------------------|------|

|                            |                                                                                     | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01 | 0                   | -    | 60                  |      |

| f <sub>HCLK</sub>          | Internal AHB clock frequency                                                        | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10 | 0                   | -    | 84                  | MHz  |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                                                       |                                                                        | 0                   | -    | 42                  |      |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                                                       |                                                                        | 0                   | -    | 84                  |      |

| $V_{DD}$                   | Standard operating voltage                                                          |                                                                        | 1.7 <sup>(1)</sup>  | -    | 3.6                 |      |

| V <sub>DDA</sub><br>(2)(3) | Analog operating voltage<br>(ADC limited to 1.2 M samples)                          | Must be the same potential as $V_{DD}^{(4)}$                           | 1.7 <sup>(1)</sup>  | -    | 2.4                 |      |

| (2)(3)                     | Analog operating voltage<br>(ADC limited to 2.4 M samples)                          | Must be the same potential as $v_{DD}^{(1)}$                           | 2.4                 | -    | 3.6                 |      |

| V <sub>BAT</sub>           | Backup operating voltage                                                            |                                                                        | 1.65                | -    | 3.6                 |      |

| N/                         | Regulator ON: 1.2 V internal voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 60 MHz        | 1.08 <sup>(5)</sup> | 1.14 | 1.20 <sup>(5)</sup> | V    |

| V <sub>12</sub>            |                                                                                     | VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz        | 1.20 <sup>(5)</sup> | 1.26 | 1.32 <sup>(5)</sup> |      |

|                            | Regulator OFF: 1.2 V external                                                       | Max. frequency 60 MHz.                                                 | 1.1                 | 1.14 | 1.2                 |      |

| V <sub>12</sub>            | voltage must be supplied on $V_{CAP_1}/V_{CAP_2}$ pins                              | Max. frequency 84 MHz.                                                 | 1.2                 | 1.26 | 1.32                |      |

|                            | Input voltage on RST and FT                                                         | $2 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$               | -0.3                | -    | 5.5                 |      |

| $V_{IN}$                   | pins <sup>(6)</sup>                                                                 | $V_{DD} \leq 2 V$                                                      | -0.3                | -    | 5.2                 |      |

|                            | Input voltage on BOOT0 pin                                                          |                                                                        | 0                   | -    | 9                   |      |

|                            |                                                                                     | UFQFPN48                                                               | -                   | -    | 625                 | mW   |

|                            | Maximum allowed package                                                             | WLCSP49                                                                | -                   | -    | 385                 |      |

| PD                         | power dissipation for suffix 6                                                      | LQFP64                                                                 | -                   | -    | 313                 |      |

|                            | and 7 <sup>(7)</sup>                                                                | LQFP100                                                                | -                   | -    | 465                 | ]    |

|                            |                                                                                     | UFBGA100                                                               | -                   | -    | 323                 | ]    |

| Table 23. Typical and maximum current consumption in run mode, code with data processing      |  |

|-----------------------------------------------------------------------------------------------|--|

| (ART accelerator enabled except prefetch) running from Flash memory - V <sub>DD</sub> = 3.3 V |  |

|                 |                    |                                                              | ¢                          |      |                           | Max <sup>(1)</sup>        |                            |      |

|-----------------|--------------------|--------------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter          | Conditions                                                   | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                    |                                                              | 84                         | 22.5 | 23                        | 24                        | 25                         |      |

|                 |                    |                                                              | 60                         | 14.8 | 16                        | 17                        | 18                         |      |

|                 |                    | External clock,<br>all peripherals enabled <sup>(2)(3)</sup> | 40                         | 11.0 | 12                        | 13                        | 14                         |      |

|                 |                    |                                                              | 30                         | 8.9  | 10                        | 11                        | 12                         |      |

| 1               | Supply current     |                                                              | 20                         | 7.3  | 8                         | 9                         | 10                         | mA   |

| I <sub>DD</sub> | in <b>Run mode</b> |                                                              | 84                         | 11.8 | 13                        | 14                        | 15                         | ШA   |

|                 |                    |                                                              | 60                         | 7.9  | 9                         | 10                        | 11                         |      |

|                 |                    | External clock, all peripherals disabled <sup>(3)</sup>      | 40                         | 5.8  | 7                         | 8                         | 9                          |      |

|                 |                    |                                                              | 30                         | 4.8  | 6                         | 7                         | 8                          |      |

|                 |                    |                                                              | 20                         | 4.0  | 5                         | 6                         | 7                          |      |

1. Guaranteed by characterization, unless otherwise specified.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

# Table 24. Typical and maximum current consumption in run mode, code with data processing(ART accelerator disabled) running from Flash memory

|                 |                    |                                                           | f <sub>HCLK</sub> |      |                           | Max <sup>(1)</sup>        |                            |      |

|-----------------|--------------------|-----------------------------------------------------------|-------------------|------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter          | Conditions                                                | 'HCLK<br>(MHz)    | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                    |                                                           | 84                | 30.6 | 32                        | 34                        | 35                         |      |

|                 |                    |                                                           | 60                | 21.4 | 22                        | 24                        | 25                         |      |

|                 |                    | External clock, all peripherals enabled <sup>(2)(3)</sup> | 40                | 15.6 | 16                        | 17                        | 18                         |      |

|                 |                    |                                                           | 30                | 12.7 | 13                        | 14                        | 15                         |      |

| laa             | Supply current     |                                                           | 20                | 10.0 | 11                        | 12                        | 13                         | mA   |

| I <sub>DD</sub> | in <b>Run mode</b> |                                                           | 84                | 19.9 | 21                        | 23                        | 25                         |      |

|                 |                    |                                                           | 60                | 14.6 | 15                        | 16                        | 17                         |      |

|                 |                    | External clock, all peripherals disabled <sup>(3)</sup>   | 40                | 10.4 | 11                        | 12                        | 13                         |      |

|                 |                    |                                                           | 30                | 8.6  | 9                         | 10                        | 11                         |      |

|                 |                    |                                                           | 20                | 6.7  | 7                         | 8                         | 9                          |      |

1. Guaranteed by characterization, unless otherwise specified.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

|                      |                                       |                                                   | Тур                       | Max <sup>(1)</sup>        |                           |                            |      |

|----------------------|---------------------------------------|---------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                             | Conditions                                        | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      | Main regulator usage                  | Flash in Stop mode, all                           | 109                       | 135                       | 440                       | 650                        |      |

|                      | Low power regulator usage             | oscillators OFF, no<br>independent watchdog       | 41                        | 65                        | 310                       | 530 <sup>(2)</sup>         |      |

| I <sub>DD_STOP</sub> | Main regulator usage                  | Flash in Deep power                               | 72                        | 95                        | 345                       | 530                        | μA   |

| -                    | Low power regulator usage             | down mode, all oscillators<br>OFF, no independent | 12                        | 36                        | 260                       | 510 <sup>(2)</sup>         |      |

|                      | Low power low voltage regulator usage | watchdog                                          | 10                        | 27                        | 230                       | 460                        |      |

Table 27. Typical and maximum current consumptions in Stop mode -  $V_{DD}$ =1.8 V

1. Guaranteed by characterization.

2. Guaranteed by test in production.

| Symbol               |                                       |                                                   | Тур                       |                           | Max <sup>(1)</sup>       | Max <sup>(1)</sup>         |      |  |

|----------------------|---------------------------------------|---------------------------------------------------|---------------------------|---------------------------|--------------------------|----------------------------|------|--|

|                      | Parameter                             | Conditions                                        | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | Unit |  |

|                      | Main regulator usage                  | Flash in Stop mode, all                           | 111                       | 140                       | 450                      | 670                        |      |  |

|                      | Low power regulator usage             | oscillators OFF, no<br>independent watchdog       | 42                        | 65                        | 330                      | 560                        |      |  |

| I <sub>DD_STOP</sub> | Main regulator usage                  | Flash in Deep power                               | 73                        | 100                       | 360                      | 560                        | μA   |  |

| -                    | Low power regulator usage             | down mode, all oscillators<br>OFF, no independent | 12                        | 36                        | 270                      | 520                        |      |  |

|                      | Low power low voltage regulator usage | watchdog                                          | 10                        | 28                        | 230                      | 470                        |      |  |

Table 28. Typical and maximum current consumption in Stop mode -  $V_{DD}$ =3.3 V

1. Guaranteed by characterization.

| Table 29. Typical and maximum current | consumption in Standby mode - V <sub>DD</sub> =1.8 V |

|---------------------------------------|------------------------------------------------------|

|                                       |                                                      |

|         |                            |                                       | Typ <sup>(1)</sup>        |                           | Max <sup>(2</sup>         | )                          |      |

|---------|----------------------------|---------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol  | Symbol Parameter Condition |                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|         | cappij canonem             | Low-speed oscillator (LSE) and RTC ON | 2.4                       | 4.0                       | 12.0                      | 24.0                       | μA   |

| DD_STBY | Standby mode               | RTC and LSE OFF                       | 1.8                       | 3.0 <sup>(3)</sup>        | 11.0                      | 23.0 <sup>(3)</sup>        | μΛ   |

1. When the PDR is OFF (internal reset is OFF), the typical current consumption is reduced by 1.2  $\mu A.$

2. Guaranteed by characterization, unless otherwise specified.

3. Guaranteed by test in production.

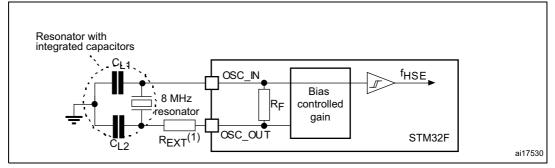

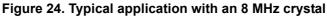

series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 38*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                    | Min | Тур  | Max  | Unit |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|------|------|------|

| R <sub>F</sub>                      | Feedback resistor                       |                               | -   | 18.4 | -    | MΩ   |

| I <sub>DD</sub>                     | LSE current consumption                 |                               | -   | -    | 1    | μA   |

| G <sub>m</sub> _crit_max            | Maximum critical crystal g <sub>m</sub> | Startup                       | -   | -    | 0.56 | μA/V |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                            | $V_{\text{DD}}$ is stabilized | -   | 2    | -    | s    |

Table 38. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is guaranteed by characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

| Symbol                               | Parameter                     | Conditions                               | Min          | Тур | Max          | Unit |

|--------------------------------------|-------------------------------|------------------------------------------|--------------|-----|--------------|------|

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD  | VCO freq = 192 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA | VCO freq = 192 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 |      |

## Table 41. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization.

| Symbol                                  | Parameter                                    | Conditions                                                              |                    | Min                 | Тур  | Мах          | Unit |

|-----------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLLI2S_IN</sub>                  | PLLI2S input clock <sup>(1)</sup>            |                                                                         |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         |      |

| f <sub>PLLI2S_OUT</sub>                 | PLLI2S multiplier output clock               |                                                                         |                    | -                   | -    | 216          | MHz  |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                            |                                                                         |                    | 192                 | -    | 432          |      |

| +                                       | PLLI2S lock time                             | VCO freq = 192 MHz                                                      | 2                  | 75                  | -    | 200          | 110  |

| t <sub>LOCK</sub>                       |                                              | VCO freq = 432 MHz                                                      | 2                  | 100                 | -    | 300          | μs   |

|                                         |                                              | Cycle to cycle at                                                       | RMS                | -                   | 90   | -            |      |

|                                         | Master I2S clock jitter                      | 12.288 MHz on<br>48 KHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -                   | ±280 | -            |      |

| Jitter <sup>(3)</sup>                   |                                              | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | f                  | -                   | 90   | -            | ps   |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48<br>on 1000 samples                                 | KHz                | -                   | 400  | -            |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{\text{DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 |      |

### Table 42. PLLI2S (audio PLL) characteristics

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization.

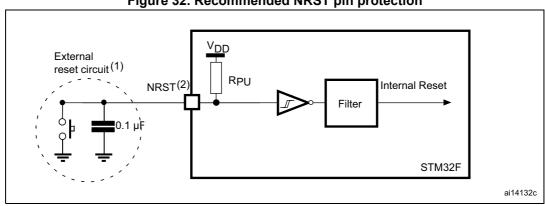

Figure 32. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- 2. The external capacitor must be placed as close as possible to the device.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in 3. Table 57. Otherwise the reset is not taken into account by the device.

#### 6.3.18 TIM timer characteristics

The parameters given in Table 58 are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                                         | Conditions <sup>(3)</sup>                   | Min    | Мах                     | Unit                 |

|------------------------|-------------------------------------------------------------------|---------------------------------------------|--------|-------------------------|----------------------|

|                        |                                                                   | AHB/APBx prescaler=1                        | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time                                             | or 2 or 4, f <sub>TIMxCLK</sub> =<br>84 MHz | 11.9   | -                       | ns                   |

|                        |                                                                   | AHB/APBx prescaler>4,                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                                   | f <sub>TIMxCLK</sub> = 84 MHz               | 11.9   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock                                              |                                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4                                           | f <sub>TIMxCLK</sub> = 84 MHz               | 0      | 42                      | MHz                  |