Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 84MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 50                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | · ·                                                                     |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401rct7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                           | 1    |

|-----------|------------------------------------------------------------------------------------------|------|

| Table 2.  | STM32F401xB/C features and peripheral counts.                                            | . 11 |

| Table 3.  | Regulator ON/OFF and internal power supply supervisor availability                       |      |

| Table 4.  | Timer feature comparison.                                                                |      |

| Table 5.  | Comparison of I2C analog and digital filters                                             | . 28 |

| Table 6.  | USART feature comparison                                                                 |      |

| Table 7.  | Legend/abbreviations used in the pinout table                                            |      |

| Table 8.  | STM32F401xB/STM32F401xC pin definitions                                                  | . 37 |

| Table 9.  | Alternate function mapping                                                               | . 44 |

| Table 10. | STM32F401xB/STM32F401xC                                                                  |      |

|           | register boundary addresses                                                              | . 51 |

| Table 11. | Voltage characteristics                                                                  | . 57 |

| Table 12. | Current characteristics                                                                  | . 58 |

| Table 13. | Thermal characteristics.                                                                 | . 58 |

| Table 14. | General operating conditions                                                             | . 59 |

| Table 15. | Features depending on the operating power supply range                                   | . 60 |

| Table 16. | VCAP_1/VCAP_2 operating conditions                                                       | . 61 |

| Table 17. | Operating conditions at power-up / power-down (regulator ON)                             | . 61 |

| Table 18. | Operating conditions at power-up / power-down (regulator OFF).                           | . 62 |

| Table 19. | Embedded reset and power control block characteristics.                                  | . 62 |

| Table 20. | Typical and maximum current consumption, code with data processing (ART                  |      |

|           | accelerator disabled) running from SRAM - V <sub>DD</sub> =1.8V                          | . 64 |

| Table 21. | Typical and maximum current consumption, code with data processing (ART                  |      |

|           | accelerator disabled) running from SRAM                                                  | . 65 |

| Table 22. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator enabled except prefetch) running from Flash memory- $V_{DD}$ = 1.8 V    | . 65 |

| Table 23. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator enabled except prefetch) running from Flash memory - $V_{DD}$ = 3.3 V . | . 66 |

| Table 24. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator disabled) running from Flash memory                                     | . 66 |

| Table 25. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator enabled with prefetch) running from Flash memory                        |      |

| Table 26. | Typical and maximum current consumption in Sleep mode                                    |      |

| Table 27. | Typical and maximum current consumptions in Stop mode - V <sub>DD</sub> =1.8 V           |      |

| Table 28. | Typical and maximum current consumption in Stop mode - V <sub>DD</sub> =3.3 V            |      |

| Table 29. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> =1.8 V         |      |

| Table 30. | Typical and maximum current consumption in Standby mode - $V_{DD}$ =3.3 V                |      |

| Table 31. | Typical and maximum current consumptions in V <sub>BAT</sub> mode                        |      |

| Table 32. | Switching output I/O current consumption                                                 |      |

| Table 33. | Peripheral current consumption                                                           | . 72 |

| Table 34. | Low-power mode wakeup timings <sup>(1)</sup>                                             |      |

| Table 35. | High-speed external user clock characteristics.                                          |      |

| Table 36. | Low-speed external user clock characteristics                                            |      |

| Table 37. | HSE 4-26 MHz oscillator characteristics                                                  | . 76 |

| Table 38. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                           |      |

| Table 39. | HSI oscillator characteristics                                                           | . 78 |

| Table 40. | LSI oscillator characteristics                                                           |      |

| Table 41. | Main PLL characteristics                                                                 | . 80 |

## 2 Description

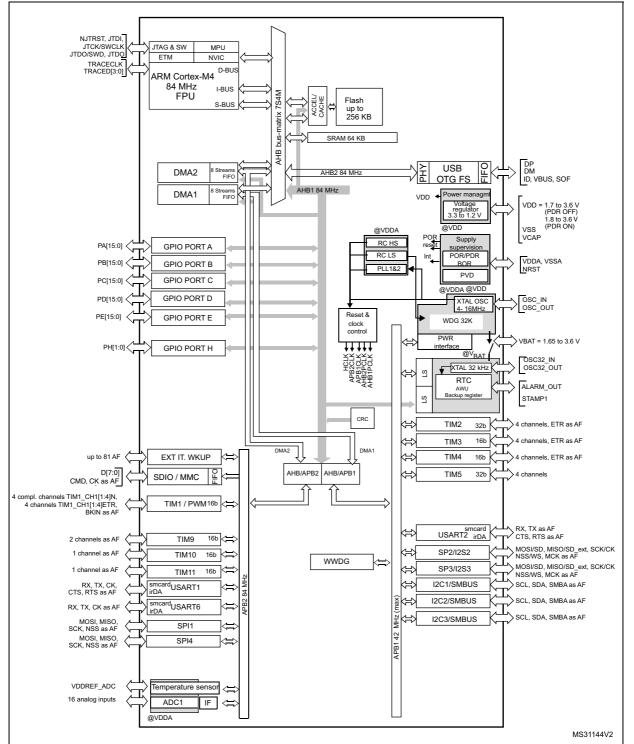

The STM32F401xB/STM32F401xC devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 84 MHz. The Cortex<sup>®</sup>-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F401xB/STM32F401xC incorporate high-speed embedded memories (up to 256 Kbytes of Flash memory, up to 64 Kbytes of SRAM), and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer one 12-bit ADC, a low-power RTC, six general-purpose 16-bit timers including one PWM timer for motor control, two general-purpose 32-bit timers. They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Up to four SPIs

- Two full duplex I<sup>2</sup>Ss. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Three USARTs

- SDIO interface

- USB 2.0 OTG full speed interface

Refer to *Table 2: STM32F401xB/C features and peripheral counts* for the peripherals available for each part number.

The STM32F401xB/STM32F401xC operate in the -40 to +105 °C temperature range from a 1.7 (PDR OFF) to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

These features make the STM32F401xB/STM32F401xC microcontrollers suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

- Mobile phone sensor hub

*Figure 3* shows the general block diagram of the devices.

| Periphe           |                       | 2. 01 11 321 4                                     | STM32F401xE | •                   | STM32F401xC         |         |                      |  |     |  |  |  |

|-------------------|-----------------------|----------------------------------------------------|-------------|---------------------|---------------------|---------|----------------------|--|-----|--|--|--|

| Flash memory in   | Kbytes                | 128                                                |             |                     | 256                 |         |                      |  | 256 |  |  |  |

| SRAM in<br>Kbytes | System                |                                                    |             | 6                   | 4                   |         |                      |  |     |  |  |  |

| Timoro            | General-<br>purpose   |                                                    |             | 7                   | ,                   |         |                      |  |     |  |  |  |

| Timers            | Advanced-<br>control  |                                                    |             | 1                   |                     |         |                      |  |     |  |  |  |

|                   | SPI/ I <sup>2</sup> S | 3/2 (full                                          | duplex)     | 4/2 (full duplex)   | 3/2 (full           | duplex) | 4/2 (full<br>duplex) |  |     |  |  |  |

| Communication     | I <sup>2</sup> C      |                                                    | 3           |                     |                     |         |                      |  |     |  |  |  |

| interfaces        | USART                 | 3                                                  |             |                     |                     |         |                      |  |     |  |  |  |

|                   | SDIO                  | -                                                  | 1           |                     | -                   |         | 1                    |  |     |  |  |  |

| USB OTG FS        |                       |                                                    |             | 1                   |                     |         |                      |  |     |  |  |  |

| GPIOs             |                       | 36                                                 | 50          | 81                  | 36                  | 50      | 81                   |  |     |  |  |  |

| 12-bit ADC        |                       |                                                    |             | 1                   |                     |         |                      |  |     |  |  |  |

| Number of chan    | nels                  | 10                                                 | 1           | 6                   | 10                  |         | 16                   |  |     |  |  |  |

| Maximum CPU f     | requency              |                                                    |             | 84 N                | MHz                 |         |                      |  |     |  |  |  |

| Operating voltag  | е                     | 1.7 to 3.6 V                                       |             |                     |                     |         |                      |  |     |  |  |  |

|                   | met une e             | Ambient temperatures: -40 to +85 °C/-40 to +105 °C |             |                     |                     |         |                      |  |     |  |  |  |

| Operating tempe   | eratures              |                                                    | Junc        | tion temperatu      | re: -40 to + 12     | 25 °C   |                      |  |     |  |  |  |

| Package           |                       | WLCSP49<br>UFQFPN48                                | LQFP64      | UFBGA100<br>LQFP100 | WLCSP49<br>UFQFPN48 | LQFP64  | UFBGA100<br>LQFP100  |  |     |  |  |  |

Table 2. STM32F401xB/C features and peripheral counts

Figure 3. STM32F401xB/STM32F401xC block diagram

1. The timers connected to APB2 are clocked from TIMxCLK up to 84 MHz, while the timers connected to APB1 are clocked from TIMxCLK up to 42 MHz.

### 3.15.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run)

In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

- LPR is used in the Stop modes

The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Depending on the package, one or two external ceramic capacitors should be connected on the V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. The V<sub>CAP\_2</sub> pin is only available for the LQFP100 and UFBGA100 packages.

All packages have the regulator ON feature.

## 3.15.2 Regulator OFF

The Regulator OFF is available only on the UFBGA100, which features the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V12 voltage source through  $V_{CAP-1}$  and  $V_{CAP-2}$  pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 14: General operating conditions*.

The two 2.2  $\mu$ F V<sub>CAP</sub> ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 18: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V12 logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4 or TIM5 timer.

## 3.29 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value. Refer to the reference manual for additional information.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

## 3.30 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

## 3.31 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F401xB/STM32F401xC through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using any high-speed channel available. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

5

| 4 |

|---|

| 7 |

| 3 |

| σ |

| Table | 9. <i>I</i> | Alternate | function | ma | apping | (C | ontinued | I) |

|-------|-------------|-----------|----------|----|--------|----|----------|----|

|       |             |           |          |    |        |    |          |    |

| _      |      |        |           |                     |                          |                    |                                       |                          |                                 |        | ,             |         |      |              |      |      |              |

|--------|------|--------|-----------|---------------------|--------------------------|--------------------|---------------------------------------|--------------------------|---------------------------------|--------|---------------|---------|------|--------------|------|------|--------------|

|        |      | AF00   | AF01      | AF02                | AF03                     | AF04               | AF05                                  | AF06                     | AF07                            | AF08   | AF09          | AF10    | AF11 | AF12         | AF13 | AF14 | AF15         |

|        | Port | SYS_AF | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/SPI2/<br>I2S2/SPI3/<br>I2S3/SPI4 | SPI2/I2S2/<br>SPI3/ I2S3 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6 | 12C2/<br>12C3 | OTG1_FS |      | SDIO         |      |      |              |

|        | PD0  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD1  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD2  | -      | -         | TIM3_ETR            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | SDIO_<br>CMD | -    | -    | EVENT<br>OUT |

|        | PD3  | -      | -         | -                   | -                        | -                  | SPI2_SCK/<br>I2S2_CK                  | -                        | USART2_<br>CTS                  |        | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD4  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>RTS                  |        | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD5  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>TX                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD6  | -      | -         | -                   | -                        | -                  | SPI3_MOSI<br>/I2S3_SD                 | -                        | USART2_<br>RX                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

| Q      | PD7  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>CK                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

| Port D | PD8  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD9  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD10 | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD11 | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD12 | -      | -         | TIM4_CH1            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD13 | -      | -         | TIM4_CH2            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD14 | -      | -         | TIM4_CH3            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD15 | -      | -         | TIM4_CH4            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

STM32F401xB STM32F401xC

Pinouts and pin description

# 6.3 Operating conditions

## 6.3.1 General operating conditions

| Table 14 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol                     | Parameter                                                  | Conditions                                                             | Min                 | Тур  | Max                 | Unit |  |  |

|----------------------------|------------------------------------------------------------|------------------------------------------------------------------------|---------------------|------|---------------------|------|--|--|

| £                          |                                                            | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01 | 0                   | -    | 60                  |      |  |  |

| f <sub>HCLK</sub>          | Internal AHB clock frequency                               | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10 | 0                   | -    | 84                  | MHz  |  |  |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                              |                                                                        | 0                   | -    | 42                  |      |  |  |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                              |                                                                        | 0                   | -    | 84                  |      |  |  |

| $V_{DD}$                   | Standard operating voltage                                 |                                                                        | 1.7 <sup>(1)</sup>  | -    | 3.6                 |      |  |  |

| V <sub>DDA</sub><br>(2)(3) | Analog operating voltage<br>(ADC limited to 1.2 M samples) | Must be the same potential as $V_{DD}^{(4)}$                           | 1.7 <sup>(1)</sup>  | -    | 2.4                 |      |  |  |

| (2)(3)                     | Analog operating voltage<br>(ADC limited to 2.4 M samples) |                                                                        | 2.4                 | -    | 3.6                 |      |  |  |

| V <sub>BAT</sub>           | Backup operating voltage                                   |                                                                        | 1.65                | -    | 3.6                 |      |  |  |

|                            | Regulator ON: 1.2 V internal                               | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 60 MHz        | 1.08 <sup>(5)</sup> | 1.14 | 1.20 <sup>(5)</sup> | V    |  |  |

| V <sub>12</sub>            | voltage on $V_{CAP_1}/V_{CAP_2}$ pins                      | VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz        | 1.20 <sup>(5)</sup> | 1.26 | 1.32 <sup>(5)</sup> |      |  |  |

|                            | Regulator OFF: 1.2 V external                              | Max. frequency 60 MHz.                                                 | 1.1                 | 1.14 | 1.2                 |      |  |  |

| V <sub>12</sub>            | voltage must be supplied on $V_{CAP_1}/V_{CAP_2}$ pins     | Max. frequency 84 MHz.                                                 | 1.2                 | 1.26 | 1.32                |      |  |  |

|                            | Input voltage on RST and FT                                | $2 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$               | -0.3                | -    | 5.5                 |      |  |  |

| $V_{IN}$                   | pins <sup>(6)</sup>                                        | $V_{DD} \leq 2 V$                                                      | -0.3                | -    | 5.2                 |      |  |  |

|                            | Input voltage on BOOT0 pin                                 |                                                                        | 0                   | -    | 9                   |      |  |  |

|                            |                                                            | UFQFPN48                                                               | -                   | -    | 625                 |      |  |  |

| P <sub>D</sub>             | Maximum allowed package                                    | WLCSP49                                                                | -                   | -    | 385                 | mW   |  |  |

|                            | power dissipation for suffix 6                             | LQFP64                                                                 | -                   | -    | 313                 |      |  |  |

|                            | and 7 <sup>(7)</sup>                                       | LQFP100                                                                | -                   | -    | 465                 |      |  |  |

|                            |                                                            | UFBGA100                                                               | -                   | -    | 323                 | ]    |  |  |

| Table 25. Typical and maximum current consumption in run mode, code with data processing |

|------------------------------------------------------------------------------------------|

| (ART accelerator enabled with prefetch) running from Flash memory                        |

|                 |                                                             |                                                         | f                                         |      |                           |                           |                            |      |    |  |

|-----------------|-------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|------|---------------------------|---------------------------|----------------------------|------|----|--|

| Symbol          | Parameter                                                   | Conditions                                              | f <sub>HCLK</sub><br>(MHz)                | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |    |  |

|                 |                                                             |                                                         | 84                                        | 31.8 | 33                        | 35                        | 36                         |      |    |  |

|                 |                                                             |                                                         | 60                                        | 21.8 | 22                        | 23                        | 24                         |      |    |  |

|                 | External clock,<br>all peripherals enabled <sup>(2)(3</sup> |                                                         | all peripherals enabled <sup>(2)(3)</sup> | 40   | 16.0                      | 17                        | 18                         | 19   |    |  |

|                 |                                                             |                                                         | 30                                        | 12.9 | 14                        | 15                        | 16                         |      |    |  |

| 1               | Supply current                                              |                                                         | 20                                        | 10.4 | 11                        | 12                        | 13                         | mA   |    |  |

| I <sub>DD</sub> | in <b>Run mode</b>                                          |                                                         | 84                                        | 21.2 | 22                        | 23                        | 24                         |      |    |  |

|                 |                                                             |                                                         |                                           |      | 60                        | 15.0                      | 16                         | 17   | 18 |  |

|                 |                                                             | External clock, all peripherals disabled <sup>(3)</sup> | 40                                        | 10.9 | 12                        | 13                        | 14                         |      |    |  |

|                 |                                                             |                                                         | 30                                        | 8.8  | 10                        | 11                        | 12                         |      |    |  |

|                 |                                                             |                                                         | 20                                        | 7.1  | 8                         | 9                         | 10                         |      |    |  |

1. Guaranteed by characterization, unless otherwise specified.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

|                 |                                                              |                                                               | £                                                                       | Тур                                                           |                                                                            |                           |                            |      |   |   |

|-----------------|--------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------|----------------------------|------|---|---|

| Symbol Paramete | Parameter                                                    | Conditions                                                    | f <sub>HCLK</sub><br>(MHz)                                              |                                                               | T <sub>A</sub> =<br>25 °C                                                  | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |   |   |

|                 |                                                              |                                                               | 84                                                                      | 16.2                                                          | 17                                                                         | 18                        | 19                         |      |   |   |

|                 |                                                              |                                                               | 60                                                                      | 10.7                                                          | 11                                                                         | 12                        | 13                         |      |   |   |

|                 | External clock,<br>all peripherals enabled <sup>(2)(3)</sup> | 40                                                            | 8.3                                                                     | 9                                                             | 10                                                                         | 11                        |                            |      |   |   |

|                 |                                                              |                                                               | 30                                                                      | 6.8                                                           | 7                                                                          | 8                         | 9                          |      |   |   |

| I               | Supply current                                               |                                                               | 20                                                                      | 5.9                                                           | 6                                                                          | 7                         | 8                          | mA   |   |   |

| I <sub>DD</sub> | in <b>Sleep</b> mode                                         |                                                               | 84                                                                      | 5.2                                                           | 6                                                                          | 7                         | 8                          |      |   |   |

|                 |                                                              | External clock,<br>all peripherals disabled <sup>(3)(4)</sup> | 60                                                                      | 3.6                                                           | 4                                                                          | 5                         | 6                          |      |   |   |

|                 |                                                              |                                                               | External clock, all peripherals disabled <sup><math>(3)(4)</math></sup> | External clock,<br>all peripherals disabled <sup>(3)(4)</sup> | External clock,<br>all peripherals disabled <sup><math>(3)(4)</math></sup> | 40                        | 2.9                        | 3    | 4 | 5 |

|                 |                                                              |                                                               | 30                                                                      | 2.6                                                           | 3                                                                          | 4                         | 5                          |      |   |   |

|                 |                                                              |                                                               | 20                                                                      | 2.6                                                           | 3                                                                          | 4                         | 5                          |      |   |   |

#### Table 26. Typical and maximum current consumption in Sleep mode

1. Guaranteed by characterization, unless otherwise specified.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

4. Same current consumption for  $f_{\mathsf{HCLK}}$  at 30 MHz and 20 MHz due to VCO running slower at 30 MHz.

DocID024738 Rev 6

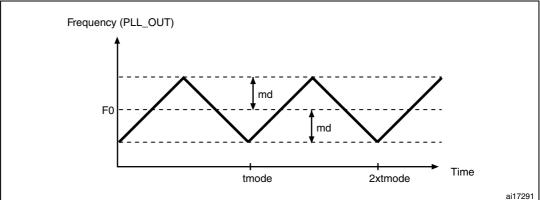

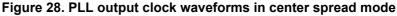

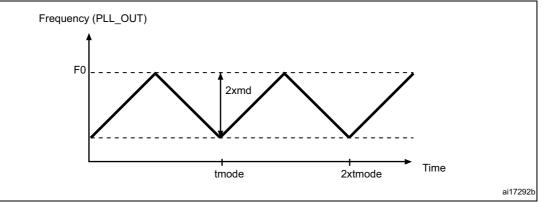

#### 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 49: EMI characteristics for WLCSP49*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP |                       | -    | -   | 2 <sup>15</sup> -1 | -    |

| Table 43 | SSCG | parameters | constraint |

|----------|------|------------|------------|

|          | 0000 | parameters | constraint |

1. Guaranteed by design.

#### Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL IN} / (4 \times f_{Mod})]$

f<sub>PLL IN</sub> and f<sub>Mod</sub> must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round  $[10^{6}/(4 \times 10^{3})] = 250$

#### Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[(

$$(2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER×INCSTEP×100×5)/ ((2<sup>15</sup>-1)×PLLN)

As a result:

$$md_{muantized}$$

% =  $(250 \times 126 \times 100 \times 5)/((2^{15} - 1) \times 240) = 2.002\%$ (peak)

DocID024738 Rev 6

*Figure 28* and *Figure 29* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

T<sub>mode</sub> is the modulation period.

md is the modulation depth.

### 6.3.12 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter      | Conditions                                  | Min | Тур | Мах | Unit |

|-----------------|----------------|---------------------------------------------|-----|-----|-----|------|

|                 |                | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 5   | -   |      |

| I <sub>DD</sub> | Supply current | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

DocID024738 Rev 6

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|--|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |  |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |  |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |  |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 4    | 8                  |      |  |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 2.75 | 5.5                | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 2    | 4                  |      |  |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |  |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                         | 2.1                | -    | 3.6                | V    |  |

|                         |                            | 8-bit program operation                          | 1.7                | -    | 3.6                | V    |  |

Table 45. Flash memory programming

1. Guaranteed by characterization.

2. The maximum programming time is measured after 100K erase operations.

| Symbol                  | Parameter                  | Conditions                   | Min <sup>(1)</sup> | Тур   | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|------------------------------|--------------------|-------|--------------------|------|

| t <sub>prog</sub>       | Double word programming    |                              | -                  | 16    | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | T <sub>A</sub> = 0 to +40 °C | -                  | 230   | -                  |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | V <sub>DD</sub> = 3.3 V      | -                  | 490   | -                  | ms   |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | V <sub>PP</sub> = 8.5 V      | -                  | 875   | -                  |      |

| t <sub>ME</sub>         | Mass erase time            |                              | -                  | 1.750 | -                  | s    |

| Tuble 40. Thas memory programming with typ voltage (continued) |                                                         |            |                    |     |                    |      |

|----------------------------------------------------------------|---------------------------------------------------------|------------|--------------------|-----|--------------------|------|

| Symbol                                                         | Parameter                                               | Conditions | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

| V <sub>prog</sub>                                              | Programming voltage                                     |            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                                                | V <sub>PP</sub> voltage range                           |            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                                                | Minimum current sunk on the $V_{PP}$ pin                |            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup>                                | Cumulative time during which V <sub>PP</sub> is applied |            | -                  | -   | 1                  | hour |

Table 46. Flash memory programming with V<sub>PP</sub> voltage (continued)

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value              | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Farameter      | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

#### Table 47. Flash memory endurance and data retention

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

### 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 48*. They are based on the EMS levels and classes defined in application note AN1709.

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter     | Conditions                                              | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ]<br>25/84 MHz | Unit |

|------------------|---------------|---------------------------------------------------------|-----------------------------|---------------------------------------------------------------|------|

|                  |               |                                                         | 0.1 to 30 MHz               | -6                                                            |      |

| 6                | MI Peak level | $V_{DD}$ = 3.3 V, T <sub>A</sub> = 25 °C, conforming to | 30 to 130 MHz               | -6                                                            | dBµV |

| S <sub>EMI</sub> |               | IEC61967-2                                              | 130 MHz to 1 GHz            | -10                                                           |      |

|                  |               |                                                         | SAE EMI Level               | 1.5                                                           | -    |

#### Table 49. EMI characteristics for WLCSP49

#### Table 50. EMI characteristics for LQFP100

| Symbol           | Parameter   | Conditions                                              | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ]<br>25/84 MHz | Unit |

|------------------|-------------|---------------------------------------------------------|-----------------------------|---------------------------------------------------------------|------|

|                  |             |                                                         | 0.1 to 30 MHz               | 18                                                            |      |

| S                | Deals lavel | $V_{DD}$ = 3.3 V, T <sub>A</sub> = 25 °C, conforming to | 30 to 130 MHz               | 23                                                            | dBµV |

| S <sub>EMI</sub> | Peak level  | IEC61967-2                                              | 130 MHz to 1 GHz            | 12                                                            |      |

|                  |             |                                                         | SAE EMI Level               | 3.5                                                           | -    |

## 6.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

٦

#### SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 61* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter                            | Conditions                                                           | Min                    | Тур               | Мах                    | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------------------|------------------------|-------------------|------------------------|------|

|                                              |                                      | Master mode, SPI1/4,<br>2.7 V < V <sub>DD</sub> < 3.6 V              |                        |                   | 42                     |      |

|                                              |                                      | Slave mode, SPI1/4,<br>2.7 V < V <sub>DD</sub> < 3.6 V               |                        |                   | 42                     |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave transmitter/full-duplex mode, SPI1/4, 2.7 V < $V_{DD}$ < 3.6 V | -                      | -                 | 38 <sup>(2)</sup>      | MHz  |

|                                              |                                      | Master mode, SPI1/2/3/4,<br>1.7 V < V <sub>DD</sub> < 3.6 V          |                        |                   | 21                     |      |

|                                              |                                      | Slave mode, SPI1/2/3/4,<br>1.7 V < V <sub>DD</sub> < 3.6 V           |                        |                   | 21                     |      |

| Duty(SCK)                                    | Duty cycle of SPI clock<br>frequency | Slave mode                                                           | 30                     | 50                | 70                     | %    |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode, SPI presc = 2                                           | T <sub>PCLK</sub> -1.5 | T <sub>PCLK</sub> | T <sub>PCLK</sub> +1.5 | ns   |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                            | 4T <sub>PCLK</sub>     | -                 | -                      | ns   |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                            | 2T <sub>PCLK</sub>     | -                 | -                      | ns   |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                                          | 0                      | -                 | -                      | ns   |

| t <sub>su(SI)</sub>                          |                                      | Slave mode                                                           | 2.5                    | -                 | -                      | ns   |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                                          | 6                      | -                 | -                      | ns   |

| t <sub>h(SI)</sub>                           | Bata input noid time                 | Slave mode                                                           | 2.5                    | -                 | -                      | ns   |

| t <sub>a(SO</sub> )                          | Data output access time              | Slave mode                                                           | 9                      | -                 | 20                     | ns   |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                                           | 8                      | -                 | 13                     | ns   |

| +                                            | Data autaut valid tima               | Slave mode (after enable edge),<br>2.7 V < $V_{DD}$ < 3.6 V          | -                      | 9.5               | 13                     | ns   |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode (after enable edge),<br>1.7 V < $V_{DD}$ < 3.6 V          | -                      | 9.5               | 17                     | ns   |

| t (ac)                                       | Data output hold time                | Slave mode (after enable edge),<br>2.7 V < V <sub>DD</sub> < 3.6 V   | 5.5                    | -                 | -                      | ns   |

| t <sub>h(SO)</sub>                           |                                      | Slave mode (after enable edge),<br>1.7 V < V <sub>DD</sub> < 3.6 V   | 3.5                    | -                 | -                      | ns   |

| Table 01. SFT uynannic characteristics | Table 61. | SPI d | ynamic | characteristics <sup>(1)</sup> |

|----------------------------------------|-----------|-------|--------|--------------------------------|

|----------------------------------------|-----------|-------|--------|--------------------------------|

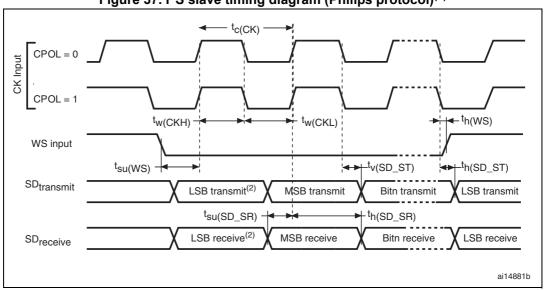

Figure 37. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

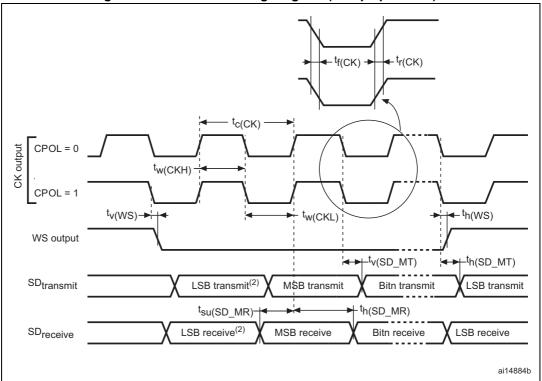

#### Figure 38. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

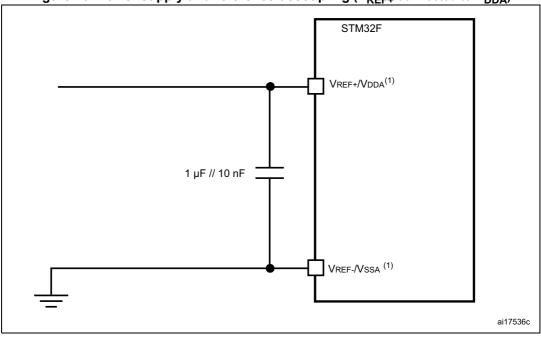

Figure 43. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

$V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA100.  $V_{REF+}$  is also available on LQFP100. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ . 1.

#### 6.3.21 **Temperature sensor characteristics**

| Table 72. | Temperature | sensor | characteristics |

|-----------|-------------|--------|-----------------|

|-----------|-------------|--------|-----------------|

| Symbol                             | Parameter                                                      |    | Тур  | Max | Unit  |

|------------------------------------|----------------------------------------------------------------|----|------|-----|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -  | ±1   | ±2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -  | 2.5  | -   | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -  | 0.76 | -   | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -  | 6    | 10  | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10 | -    | -   | μs    |

1. Guaranteed by characterization.

2. Guaranteed by design.

|    | Table 73. Temperature sensor calibration values |            |  |  |  |

|----|-------------------------------------------------|------------|--|--|--|

| ol | Parameter                                       | Memory add |  |  |  |

|    |                                                 |            |  |  |  |

| Symbol  | Parameter                                                            | Memory address            |

|---------|----------------------------------------------------------------------|---------------------------|

| TS_CAL1 | TS ADC raw data acquired at temperature of 30 °C, $V_{DDA}$ = 3.3 V  | 0x1FFF 7A2C - 0x1FFF 7A2D |

| TS_CAL2 | TS ADC raw data acquired at temperature of 110 °C, $V_{DDA}$ = 3.3 V | 0x1FFF 7A2E - 0x1FFF 7A2F |

| ······································ |                                               |  |  |  |

|----------------------------------------|-----------------------------------------------|--|--|--|

| Dimension                              | Recommended values                            |  |  |  |

| Pitch                                  | 0.4 mm                                        |  |  |  |

| Dpad                                   | 260 μm max. (circular)<br>220 μm recommended  |  |  |  |

| Dsm                                    | 300 μm min. (for 260 μm diameter pad)         |  |  |  |

| PCB pad design                         | Non-solder mask defined via underbump allowed |  |  |  |

Table 80. WLCSP49 recommended PCB design rules (0.4 mm pitch)

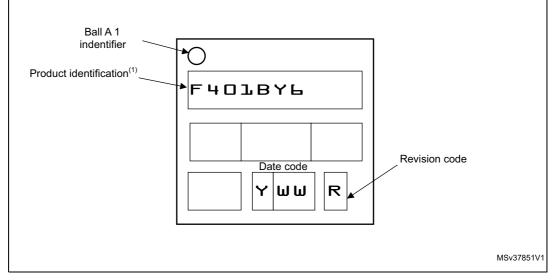

#### WLCSP49 device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 48. WLCSP49 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| quad flat package mechanical data (continued) |             |       |       |                       |        |        |  |

|-----------------------------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                                        | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|                                               | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| E2                                            | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| L                                             | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| Т                                             | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| b                                             | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |

| е                                             | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| ddd                                           | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

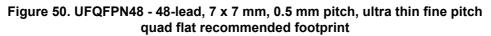

# Table 81. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitchquad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

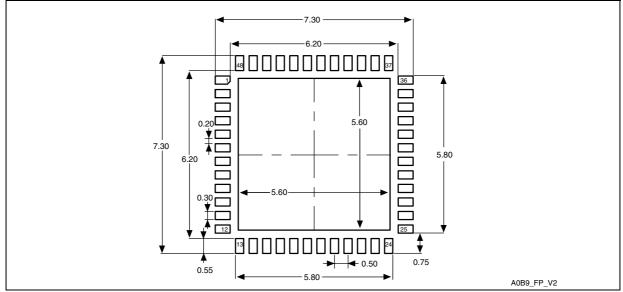

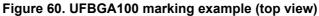

#### **UFBGA100** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.