# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 84MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 81                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 64K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401vbt6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 47.<br>Figure 48. | WLCSP49 0.4 mm pitch wafer level chip scale recommended footprint              |     |

|--------------------------|--------------------------------------------------------------------------------|-----|

| Figure 49.               | UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch              | 110 |

|                          | quad flat package outline                                                      | 117 |

| Figure 50.               | UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch              |     |

|                          | quad flat recommended footprint                                                | 118 |

| Figure 51.               | UFQFPN48 marking example (top view)                                            | 119 |

| Figure 52.               | LQFP64 - 64-pin, 10 x 10 mm, 64-pin low-profile quad flat package outline 1    | 120 |

| Figure 53.               | LQFP64 recommended footprint                                                   | 121 |

| Figure 54.               | LQFP64 marking example (top view) 1                                            |     |

| Figure 55.               | LQFP100 - 100-pin, 14 x 14 mm, 100-pin low-profile quad flat                   |     |

| -                        | package outline                                                                | 123 |

| Figure 56.               | LQFP100 recommended footprint                                                  |     |

| Figure 57.               | LQPF100 marking example (top view)                                             |     |

| Figure 58.               | UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch                 |     |

| 0                        | ball grid array package outline                                                | 126 |

| Figure 59.               | UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array |     |

| J                        | package recommended footprint                                                  | 127 |

| Figure 60.               | UFBGA100 marking example (top view)                                            |     |

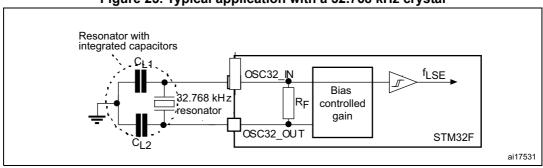

## 3.11 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy at 25 °C. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 84 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 84 MHz while the maximum frequency of the high-speed APB domains is 84 MHz. The maximum allowed frequency of the low-speed APB domain is 42 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

## 3.12 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The bootloader is located in system memory. It is used to reprogram the Flash memory by using either USART1(PA9/10), USART2(PD5/6), USB OTG FS in device mode (PA11/12) through DFU (device firmware upgrade), I2C1(PB6/7), I2C2(PB10/3), I2C3(PA8/PB4), SPI1(PA4/5/6/7), SPI2(PB12/13/14/15) or SPI3(PA15, PC10/11/12).

For more detailed information on the bootloader, refer to Application Note: AN2606, *STM32™ microcontroller system memory boot mode*.

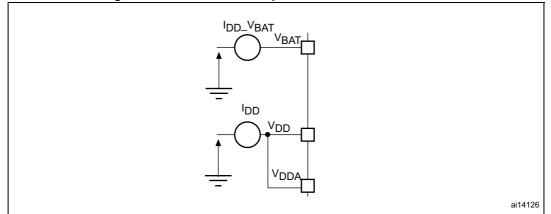

## 3.13 Power supply schemes

- V<sub>DD</sub> = 1.7 to 3.6 V: external power supply for I/Os with the internal supervisor (POR/PDR) disabled, provided externally through V<sub>DD</sub> pins. Requires the use of an external power supply supervisor connected to the VDD and PDR\_ON pins.

- V<sub>DD</sub> = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively, with decoupling technique.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to Figure 18: Power supply scheme for more details.

# 3.14 Power supply supervisor

## 3.14.1 Internal reset ON

This feature is available for  $V_{DD}$  operating voltage range 1.8 V to 3.6 V.

The internal power supply supervisor is enabled by holding PDR\_ON high.

The devices have an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR is always active, and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes.

The devices remain in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The devices also feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

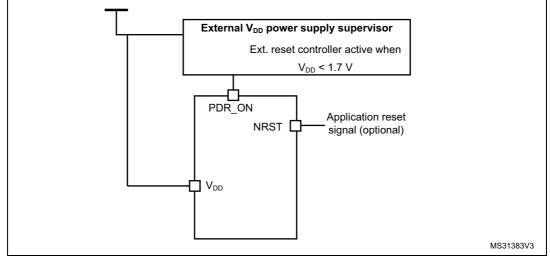

### 3.14.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled by setting the PDR\_ON pin to low.

An external power supply supervisor should monitor  $V_{DD}$  and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to this external power supply supervisor. Refer to *Figure 5: Power supply supervisor interconnection with internal reset OFF*.

Figure 5. Power supply supervisor interconnection with internal reset OFF<sup>(1)</sup>

1. The PRD\_ON pin is only available on the WLCSP49 and UFBGA100 packages.

DocID024738 Rev 6

## 3.15.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run)

In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

- LPR is used in the Stop modes

The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Depending on the package, one or two external ceramic capacitors should be connected on the V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. The V<sub>CAP\_2</sub> pin is only available for the LQFP100 and UFBGA100 packages.

All packages have the regulator ON feature.

## 3.15.2 Regulator OFF

The Regulator OFF is available only on the UFBGA100, which features the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V12 voltage source through  $V_{CAP-1}$  and  $V_{CAP-2}$  pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 14: General operating conditions*.

The two 2.2  $\mu$ F V<sub>CAP</sub> ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 18: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V12 logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

## 3.19.5 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 3.20 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the standard (up to 100 kHz) and fast (up to 400 kHz) modes. The I2C bus frequency can be increased up to 1 MHz. For more details about the complete solution, please contact your local ST sales representative. They also support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see Table 5).

|                                     | Analog filter | Digital filter                                         |

|-------------------------------------|---------------|--------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns       | Programmable length from 1 to 15 I2C peripheral clocks |

# 3.21 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART6).

These three interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 10.5 Mbit/s. The USART2 interface communicates at up to 5.25 bit/s.

USART1 and USART2 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

# 3.25 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 3.26 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 3.27 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 84 MHz.

# 3.28 Analog-to-digital converter (ADC)

One 12-bit analog-to-digital converter is embedded and shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

DocID024738 Rev 6

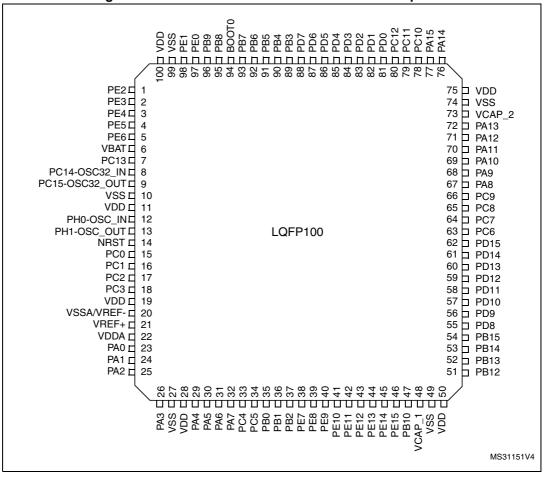

Figure 13. STM32F401xB/STM32F401xC LQFP100 pinout

1. The above figure shows the package top view.

|        | Pin     | Nur    | nber    |          |                                                      |          | e             |       |                                                         |                         |

|--------|---------|--------|---------|----------|------------------------------------------------------|----------|---------------|-------|---------------------------------------------------------|-------------------------|

| UQFN48 | WLCSP49 | LQFP64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                     | Additional<br>functions |

| 13     | E4      | 17     | 26      | L3       | PA3                                                  | I/O      | FT            | -     | USART2_RX, TIM2_CH4,<br>TIM5_CH4, TIM9_CH2,<br>EVENTOUT | ADC1_IN3                |

| -      | -       | 18     | 27      | -        | VSS                                                  | S        | -             | -     | -                                                       | -                       |

| -      | -       | 19     | 28      | -        | VDD                                                  | S        | -             | -     | -                                                       | -                       |

| -      | -       | -      | -       | E3       | BYPASS_<br>REG                                       | I        | FT            | -     | -                                                       | -                       |

| 14     | G6      | 20     | 29      | М3       | PA4                                                  | I/O      | FT            | -     | SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK, EVENTOUT   | ADC1_IN4                |

| 15     | F5      | 21     | 30      | K4       | PA5                                                  | I/O      | FT            | -     | SPI1_SCK,<br>TIM2_CH1/TIM2_ETR,<br>EVENTOUT             | ADC1_IN5                |

| 16     | F4      | 22     | 31      | L4       | PA6                                                  | I/O      | FT            | -     | SPI1_MISO, TIM1_BKIN,<br>TIM3_CH1, EVENTOUT             | ADC1_IN6                |

| 17     | F3      | 23     | 32      | M4       | PA7                                                  | I/O      | FT            | -     | SPI1_MOSI, TIM1_CH1N,<br>TIM3_CH2, EVENTOUT             | ADC1_IN7                |

| -      | -       | 24     | 33      | K5       | PC4                                                  | I/O      | FT            | -     | EVENTOUT                                                | ADC1_IN14               |

| -      | -       | 25     | 34      | L5       | PC5                                                  | I/O      | FT            | -     | EVENTOUT                                                | ADC1_IN15               |

| 18     | G5      | 26     | 35      | M5       | PB0                                                  | I/O      | FT            | -     | TIM1_CH2N, TIM3_CH3,<br>EVENTOUT                        | ADC1_IN8                |

| 19     | G4      | 27     | 36      | M6       | PB1                                                  | I/O      | FT            | -     | TIM1_CH3N, TIM3_CH4,<br>EVENTOUT                        | ADC1_IN9                |

| 20     | G3      | 28     | 37      | L6       | PB2                                                  | I/O      | FT            | -     | EVENTOUT                                                | BOOT1                   |

| -      | -       | -      | 38      | M7       | PE7                                                  | I/O      | FT            | -     | TIM1_ETR, EVENTOUT                                      | -                       |

| -      | -       | -      | 39      | L7       | PE8                                                  | I/O      | FT            | -     | TIM1_CH1N, EVENTOUT                                     | -                       |

| -      | -       | -      | 40      | M8       | PE9                                                  | I/O      | FT            | -     | TIM1_CH1, EVENTOUT                                      | -                       |

| -      | -       | -      | 41      | L8       | PE10                                                 | I/O      | FT            | -     | TIM1_CH2N, EVENTOUT                                     | -                       |

| -      | -       | -      | 42      | M9       | PE11                                                 | I/O      | FT            | -     | SPI4_NSS, TIM1_CH2,<br>EVENTOUT                         | -                       |

| -      | -       | -      | 43      | L9       | PE12                                                 | I/O      | FT            | -     | SPI4_SCK, TIM1_CH3N,<br>EVENTOUT                        | -                       |

| -      | -       | -      | 44      | M10      | PE13                                                 | I/O      | FT            | -     | SPI4_MISO, TIM1_CH3,<br>EVENTOUT                        | -                       |

Table 8. STM32F401xB/STM32F401xC pin definitions (continued)

## 6.1.7 Current consumption measurement

#### Figure 19. Current consumption measurement scheme

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard. Extended mission profiles are available on demand.

| Symbol                            | Ratings                                                                        | Min                                                                            | Мах                  | Unit |  |

|-----------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------|------|--|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}, V_{DD}$ and $V_{BAT})^{(1)}$ | -0.3                                                                           | 4.0                  |      |  |

|                                   | Input voltage on FT pins <sup>(2)</sup>                                        | V <sub>SS</sub> -0.3                                                           | V <sub>DD</sub> +4.0 | V    |  |

| V <sub>IN</sub>                   | Input voltage on any other pin                                                 | V <sub>SS</sub> -0.3                                                           | 4.0                  |      |  |

|                                   | Input voltage for BOOT0                                                        | V <sub>SS</sub>                                                                | 9.0                  |      |  |

| $ \Delta V_{DDx} $                | Variations between different V <sub>DD</sub> power pins                        | -                                                                              | 50                   |      |  |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                               |                                                                                | 50                   | mV   |  |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                             | see Section 6.3.14:<br>Absolute maximum<br>ratings (electrical<br>sensitivity) |                      |      |  |

#### Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2.  $V_{IN}$  maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

| Symbol                               | Ratings                                                                             | Max.  | Unit |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------|-------|------|--|--|--|

| $\Sigma I_{VDD}$                     | Total current into sum of all V <sub>DD_x</sub> power lines (source) <sup>(1)</sup> | 160   |      |  |  |  |

| $\Sigma I_{VSS}$                     | Total current out of sum of all $V_{SS_x}$ ground lines (sink) <sup>(1)</sup>       | -160  |      |  |  |  |

| I <sub>VDD</sub>                     | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>      | 100   |      |  |  |  |

| I <sub>VSS</sub>                     |                                                                                     |       |      |  |  |  |

|                                      | Output current sunk by any I/O and control pin                                      | 25    |      |  |  |  |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/O and control pin                                   | -25   | mA   |  |  |  |

| ΣI                                   | Total output current sunk by sum of all I/O and control pins <sup>(2)</sup>         | 120   |      |  |  |  |

| ΣΙ <sub>ΙΟ</sub>                     | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup>     | -120  |      |  |  |  |

| (3)                                  | Injected current on FT pins <sup>(4)</sup>                                          | 5/10  | 1    |  |  |  |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on NRST and B pins <sup>(4)</sup>                                  | _5/+0 |      |  |  |  |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>             | ±25   |      |  |  |  |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.20: 12-bit ADC characteristics.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol            | Ratings                                                                                   | Value                   | Unit |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------|------|

| T <sub>STG</sub>  | Storage temperature range                                                                 | –65 to +150             |      |

| Τ <sub>J</sub>    | Maximum junction temperature                                                              | 125                     |      |

| T <sub>LEAD</sub> | Maximum lead temperature during soldering<br>(WLCSP49, LQFP64/100, UFQFPN48,<br>UFBGA100) | see note <sup>(1)</sup> | °C   |

#### Table 13. Thermal characteristics

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb assembly), the ST ECOPACK<sup>®</sup> 7191395 specification, and the European directive on Restrictions on Hazardous Substances (ROHS directive 2011/65/EU, July 2011).

| Symbol                              | Parameter                                                                           | Conditions                                                                                | Min  | Тур  | Max  | Unit |

|-------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>PDRhyst</sub> <sup>(2)</sup> | PDR hysteresis                                                                      |                                                                                           | -    | 40   | -    | mV   |

| V                                   | Brownout level 1                                                                    | Falling edge                                                                              | 2.13 | 2.19 | 2.24 |      |

| V <sub>BOR1</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.23 | 2.29 | 2.33 |      |

| N.                                  | Brownout level 2                                                                    | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| VBOR2                               | V <sub>BOR2</sub> threshold                                                         | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | v    |

| N.                                  | , Brownout level 3                                                                  | Falling edge                                                                              | 2.75 | 2.83 | 2.88 |      |

| V <sub>BOR3</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.85 | 2.92 | 2.97 |      |

| V <sub>BORhyst</sub> <sup>(2)</sup> | BOR hysteresis                                                                      |                                                                                           | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub>               | POR reset timing                                                                    |                                                                                           | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(2)</sup>    | InRush current on<br>voltage regulator power-<br>on (POR or wakeup from<br>Standby) |                                                                                           | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(2)</sup>    | InRush energy on<br>voltage regulator power-<br>on (POR or wakeup from<br>Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

Table 19. Embedded reset and power control block characteristics (continued)

1. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

2. Guaranteed by design.

3. The reset timing is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is fetched by the user application code.

## 6.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 19: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

Figure 25. Typical application with a 32.768 kHz crystal

## 6.3.9 Internal clock source characteristics

The parameters given in *Table 39* and *Table 40* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

## High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

|                                     | HSI user trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

| 100                                 | Accuracy of the HSI oscillator        | $T_A = -40$ to 105 °C <sup>(3)</sup> | -8  | -   | 4.5 | %    |

| ACC <sub>HSI</sub>                  |                                       | $T_A = -10$ to 85 °C <sup>(3)</sup>  | -4  | -   | 4   | %    |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | -1  | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4   | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power<br>consumption   | -                                    | -   | 60  | 80  | μA   |

Table 39. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization.

4. Factory calibrated, parts not soldered.

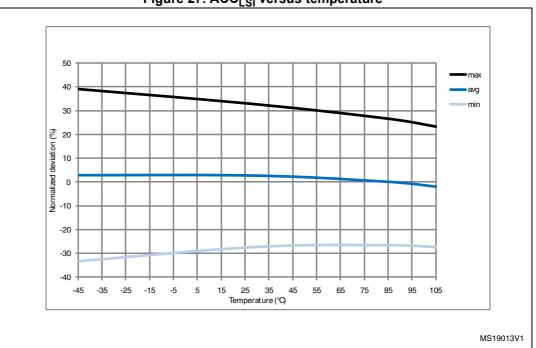

Figure 27. ACC<sub>LSI</sub> versus temperature

## 6.3.10 PLL characteristics

The parameters given in *Table 41* and *Table 42* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                             | Condition        | IS                 | Min                 | Тур  | Max  | Unit |

|------------------------|---------------------------------------|------------------|--------------------|---------------------|------|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        |                  |                    | 0.95 <sup>(2)</sup> | 1    | 2.10 | MHz  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           |                  |                    | 24                  | -    | 84   | MHz  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock |                  |                    | -                   | 48   | 75   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        |                  |                    | 192                 | -    | 432  | MHz  |

| +                      | PLL lock time                         | VCO freq = 192 I | MHz                | 75                  | -    | 200  |      |

| t <sub>LOCK</sub>      |                                       | VCO freq = 432 I | MHz                | 100                 | -    | _    | μs   |

|                        |                                       |                  | RMS                | -                   | 25   | -    |      |

| Jitter <sup>(3)</sup>  | Cycle-to-cycle jitter                 | System clock     | peak<br>to<br>peak | -                   | ±150 | -    |      |

|                        |                                       | 84 MHz           | RMS                | -                   | 15   | -    | ps   |

|                        | Period Jitter                         |                  | peak<br>to<br>peak | -                   | ±200 | -    |      |

| Tuble 40. That memory programming with the voltage (continued) |                                                         |            |                    |     |                    |      |

|----------------------------------------------------------------|---------------------------------------------------------|------------|--------------------|-----|--------------------|------|

| Symbol                                                         | Parameter                                               | Conditions | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

| V <sub>prog</sub>                                              | Programming voltage                                     |            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                                                | V <sub>PP</sub> voltage range                           |            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                                                | Minimum current sunk on the $V_{PP}$ pin                |            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup>                                | Cumulative time during which V <sub>PP</sub> is applied |            | -                  | -   | 1                  | hour |

Table 46. Flash memory programming with V<sub>PP</sub> voltage (continued)

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value | Unit    |  |

|------------------|----------------|-----------------------------------------------------------------------------------------|-------|---------|--|

| Symbol           | Farameter      | Conditions Min <sup>(1)</sup>                                                           |       | Unit    |  |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10    | kcycles |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30    |         |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10    | Years   |  |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20    |         |  |

#### Table 47. Flash memory endurance and data retention

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

## 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 48*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                               | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, WLCSP49,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 84 MHz,<br>conforms to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, WLCSP49,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 84 MHz,<br>conforms to IEC 61000-4-4 | 4A              |

Table 48. EMS characteristics for LQFP100 package

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, on LQFP100 packages and PDR ON on WLCSP49.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$  maximum) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol                         | Param                                                                                                    | eter                                              | Conditions                                                      | Min | Тур                                   | Мах   | Unit |

|--------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------|-----|---------------------------------------|-------|------|

|                                | FT and NRST I/O input hysteresis                                                                         |                                                   | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                    | -   | 10%<br>V <sub>DD</sub> <sup>(3)</sup> | -     | V    |

| V <sub>HYS</sub>               | BOOT0 I/O input                                                                                          | hystoresis                                        | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>-40 °C≤T <sub>A</sub> ≤105 °C | _   | 100                                   | _     | mV   |

|                                |                                                                                                          | Trysteresis                                       | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | -   | 100                                   | -     | IIIV |

|                                | I/O input leakage                                                                                        | current (4)                                       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>               | -   | -                                     | ±1    |      |

| l <sub>lkg</sub>               | I/O FT input leaka                                                                                       | age current <sup>(5)</sup>                        | $V_{IN} = 5 V$                                                  | -   | -                                     | 3     | μΑ   |

| R <sub>PU</sub>                | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup>                                                    | All pins<br>except for<br>PA10<br>(OTG_FS_ID<br>) | V <sub>IN</sub> = V <sub>SS</sub>                               | 30  | 40                                    | 50    |      |

|                                |                                                                                                          | PA10<br>(OTG_FS_ID<br>)                           |                                                                 | 7   | 10                                    | 14    | kΩ   |

| R <sub>PD</sub>                | All pins       except for       PA10       Weak pull-down       equivalent       resistor <sup>(7)</sup> | V <sub>IN</sub> = V <sub>DD</sub>                 | 30                                                              | 40  | 50                                    | - K22 |      |

|                                |                                                                                                          | PA10<br>(OTG_FS_ID<br>)                           |                                                                 | 7   | 10                                    | 14    |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacitan                                                                                        | се                                                | -                                                               | -   | 5                                     | -     | pF   |

| Table 54. I/O static characteristics (con | tinued) |

|-------------------------------------------|---------|

|-------------------------------------------|---------|

1. Guaranteed by design.

2. Guaranteed by test in production.

3. With a minimum of 200 mV.

- 4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 53: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 53: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 7. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT I/Os is shown in *Figure 30*.

## 6.3.17 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 54*).

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 14*. Refer to *Table 54: I/O static characteristics* for the values of VIH and VIL for NRST pin.

| Symbol                               | Parameter                                       | Conditions               | Min | Тур | Мах | Unit |

|--------------------------------------|-------------------------------------------------|--------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$        | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       |                          | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V  | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset<br>source | 20  | -   | -   | μs   |

Table 57. NRST pin characteristics

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

2. Guaranteed by design.

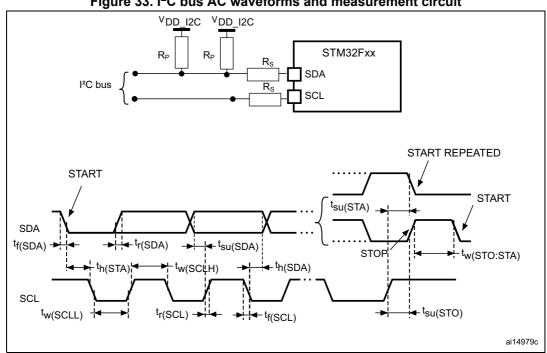

- 1. R<sub>S</sub> = series protection resistor.

- 2.  $R_P$  = external pull-up resistor.

- 3.  $V_{DD \ I2C}$  is the I2C bus power supply.

|                        | I2C_CCR value                  |

|------------------------|--------------------------------|

| f <sub>SCL</sub> (kHz) | <b>R<sub>P</sub> = 4.7 k</b> Ω |

| 400                    | 0x8019                         |

| 300                    | 0x8021                         |

| 200                    | 0x8032                         |

| 100                    | 0x0096                         |

| 50                     | 0x012C                         |

| 20                     | 0x02EE                         |

# Table 60. SCL frequency $(f_{PCLK1} = 42 \text{ MHz}, V_{DD} = V_{DD_{12C}} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

## USB OTG full speed (FS) characteristics

This interface is present in USB OTG FS controller.

| Symbol                              | Parameter                           | Max | Unit |

|-------------------------------------|-------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |

Table 63. USB OTG FS startup time

1. Guaranteed by design.

| r               |                                |                                 |                                                                  |                     |      |                     |      |

|-----------------|--------------------------------|---------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|

| Sym             | bol                            | Parameter                       | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|                 | $V_{DD}$                       | USB OTG FS operating voltage    |                                                                  | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

| Input           | $V_{DI}^{(3)}$                 | Differential input sensitivity  | I(USB_FS_DP/DM)                                                  | 0.2                 | -    | -                   |      |

| Input<br>levels | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range  | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |

|                 | $V_{SE}^{(3)}$                 | Single ended receiver threshold | iver                                                             |                     | -    | 2.0                 |      |

| Output          | V <sub>OL</sub>                | Static output level low         | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(4)}$                    | -                   | -    | 0.3                 | V    |

| levels          | V <sub>OH</sub>                | Static output level high        | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| R <sub>P</sub>  | 'D                             | PA11, PA12<br>(USB_FS_DM/DP)    | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                  | 21   | 24                  |      |

|                 |                                | PA9 (OTG_FS_VBUS)               |                                                                  | 0.65                | 1.1  | 2.0                 | kΩ   |

| R <sub>P</sub>  | ٧                              | PA11, PA12<br>(USB_FS_DM/DP)    | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 | N22  |

|                 |                                | PA9 (OTG_FS_VBUS)               | $V_{IN} = V_{SS}$                                                | 0.25                | 0.37 | 0.55                |      |

#### Table 64. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The USB OTG FS functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V V<sub>DD</sub> voltage range.

3. Guaranteed by design.

4.  $\ensuremath{\mathsf{R}_{\mathsf{L}}}$  is the load connected on the USB OTG FS drivers.

Note: When VBUS sensing feature is enabled, PA9 should be left at their default state (floating input), not as alternate function. A typical 200 µA current consumption of the embedded sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 when the feature is enabled.

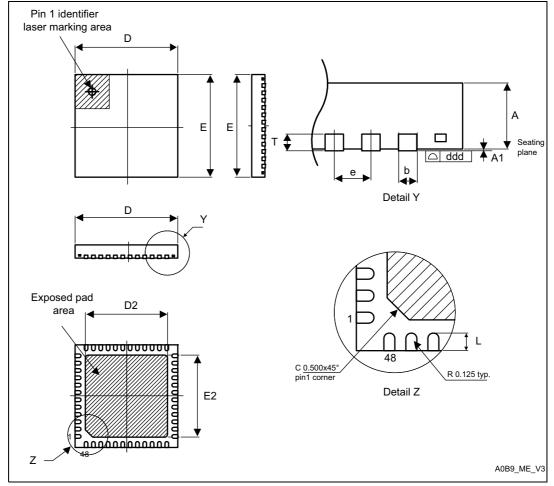

# 7.2 UFQFPN48 package information

Figure 49. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

| Table 81. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch |

|-----------------------------------------------------------------------------|

| quad flat package mechanical data                                           |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| A      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| D      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| E      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |