Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\cdot \times F$

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                               |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 20MHz                                                                                  |

| Connectivity               | I <sup>2</sup> C, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                        |

| Number of I/O              | 18                                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                            |

| Data Converters            | A/D 4x10b                                                                              |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Through Hole                                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                                |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79e825adg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 25.2   | The I2C Control Registers:                      |     |

|-----|--------|-------------------------------------------------|-----|

|     | 25.3   | Operating Modes of I2C                          |     |

| 26. | ICP(IN | I-CIRCUIT PROGRAM) FLASH PROGRAM                | 103 |

| 27. | CONF   | IG BITS                                         | 104 |

|     | 27.1   | CONFIG1                                         |     |

|     | 27.2   | CONFIG2                                         | 105 |

| 28. | ABSC   | LUTE MAXIMUM RATINGS                            | 106 |

| 29. | DC EI  | ECTRICAL CHARACTERISTICS                        | 107 |

|     | 29.1   | The ADC Converter DC ELECTRICAL CHARACTERISTICS | 108 |

|     | 29.2   | The COMPARATOR ELECTRICAL CHARACTERISTICS       | 109 |

| 30. | AC EL  | ECTRICAL CHARACTERISTICS                        | 109 |

| 31. | EXTE   | RNAL CLOCK CHARACTERISTICS                      | 109 |

| 32. | AC SF  | PECIFICATION                                    | 110 |

| 33. | TYPIC  | CAL APPLICATION CIRCUITS                        | 110 |

| 34. | PACK   | AGE DIMENSIONS                                  |     |

|     | 34.1   | 20-pin SO                                       | 111 |

|     | 34.2   | 20-pin DIP                                      | 112 |

|     | 34.3   | 24-pin SO                                       | 113 |

| 35. | REVIS  | SION HISTORY                                    | 114 |

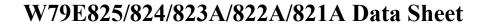

### 4. PIN CONFIGURATION

## 5. PIN DESCRIPTION

| SYMBOL      | TYPE                                                                                                                             | DESCRIPTIONS                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| RST (P1.5)  | I                                                                                                                                | RESET: A low on this pin for two machine cycles while the oscillator is running resets the device.                                          |

| XTAL1(P2.1) | L1(P2.1) I/O CRYSTAL1: This is the crystal oscillator input. This pin may be driven by a external clock or configurable I/O pin. |                                                                                                                                             |

| XTAL2(P2.0) | I/O                                                                                                                              | CRYSTAL2: This is the crystal oscillator output. It is the inversion of XTAL1 or configurable I/O pin.                                      |

| VSS         | Р                                                                                                                                | GROUND: Ground potential                                                                                                                    |

| VDD         | Р                                                                                                                                | POWER: SUPPLY: Supply voltage for operation.                                                                                                |

| P0.0-P0.7   | I/O                                                                                                                              | PORT 0: Port 0 is four mode output pin and two mode input. The P0.3~P0.6 are 4-channel input ports (ADC0-ADC3) for ADC used.                |

| P1.0-P1.7   | I/O                                                                                                                              | PORT 1: Port 1 is four mode output pin and two mode input. The P1.2(SCL) and P1.3(SDA) is only open drain circuit, and P1.5 only input pin. |

\* **TYPE:** P: power, I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open-drain.

## 6. FUNCTIONAL DESCRIPTION

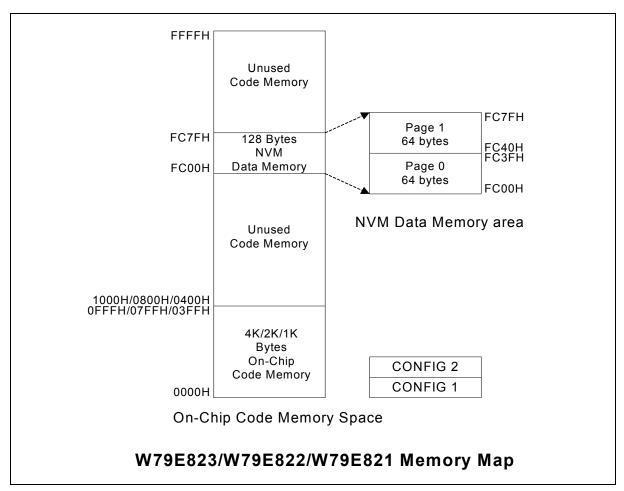

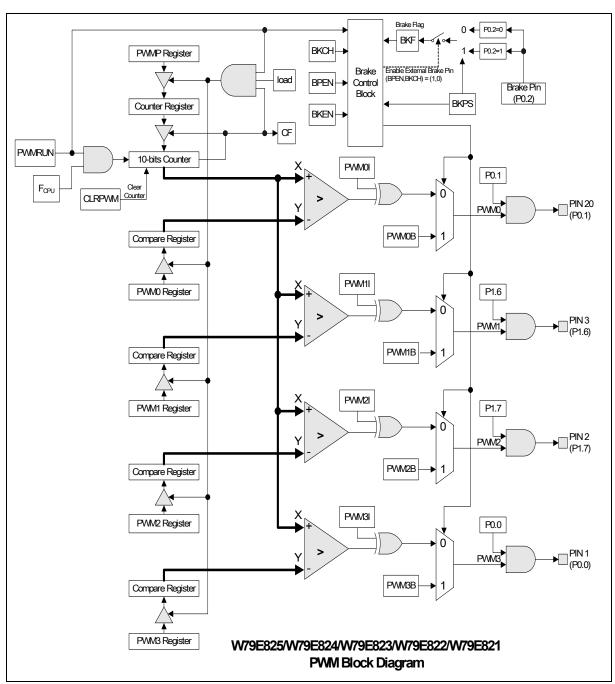

The W79E82X series architecture consist of a 4T 8051 core controller surrounded by various registers, **16K/8K/4K/2K/1K** bytes Flash EPROM, **256/128** bytes of RAM, **256/128** bytes NVM Data Flash EPROM, three general purpose I/O ports, two timer/counters, one serial port, one I2C serial I/O, 4 channel PWM with 10-bit counter, 4-channel multiplexed with 10-bit ADC analog input, Flash EPROM program by Writer and ICP.

### 6.1 On-Chip Flash EPROM

The W79E82X series include one **16K/8K/4K/2K/1K** bytes of main Flash EPROM for application program when operating the in-circuit programming features by the Flash EPROM itself which need Writer or ICP program board to program the Flash EPROM. This ICP(In-Circuit Programming) feature makes the job easy and efficient in which the application needs to update firmware frequently. In some applications, the in-circuit programming feature makes it possible that the end-user is able to easily update the system firmware by themselves without opening the chassis.

### 6.2 I/O Ports

The W79E82X series have two 8-bit and one 2-bit port, up to 18 I/O pins using on-chip oscillator & /RST is input only by reset options. All ports can be used as four outputs mode when it may set by PxM1.y and PxM2.y registers, it has strong pull-ups and pull-downs, and does not need any external pull-ups. Otherwise it can be used as general I/O port as open drain circuit. All ports can be used bidirectional and these are as I/O ports. These ports are not true I/O, but rather are pseudo-I/O ports. This is because these ports have strong pull-downs and weak pull-ups.

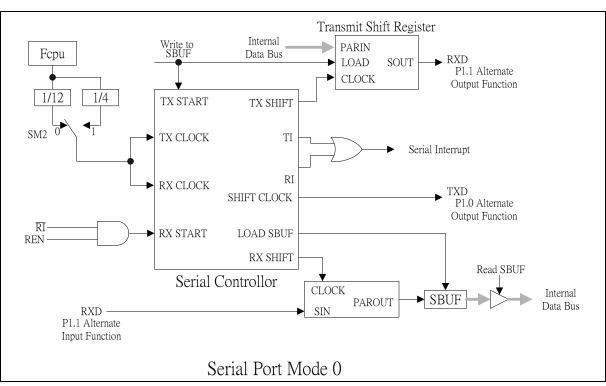

### 6.3 Serial I/O

The W79E82X series have one serial port that is functionally similar to the serial port of the original 8032 family. However the serial port on the W79E82X series can operate in different modes in order to obtain timing similarity as well. The Serial port has the enhanced features of Automatic Address recognition and Frame Error detection.

#### 6.4 Timers

The W79E82X series have two 16-bit timers that are functionally and similar to the timers of the 8052 family. When used as timers, they are set 12 or 4 clocks per count that emulates the timing of the original 8052.

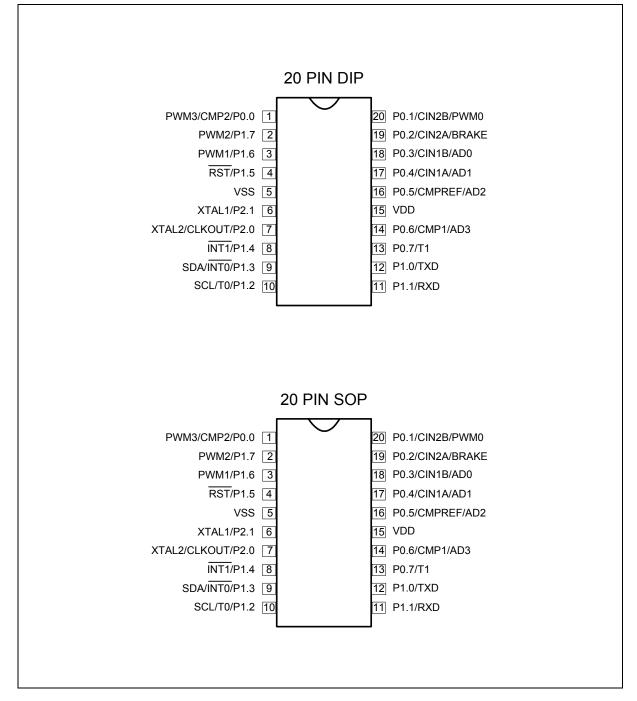

#### 6.5 Interrupts

The Interrupt structure in the W79E82X series is slightly different from that of the standard 8052. Due to the presence of additional features and peripherals, the number of interrupt sources and vectors has been increased.

#### **Bit addressable Locations**

The Scratch-pad RAM area from location 20h to 2Fh is byte as well as bit addressable. This means that a bit in this area can be individually addressed. In addition some of the SFRs are also bit addressable. The instruction decoder is able to distinguish a bit access from a byte access by the type of the instruction itself. In the SFR area, any existing SFR whose address ends in a 0 or 8 is bit addressable.

#### Stack

The scratch-pad RAM can be used for the stack. This area is selected by the Stack Pointer (SP), which stores the address of the top of the stack. Whenever a jump, call or interrupt is invoked the return address is placed on the stack. There is no restriction as to where the stack can begin in the RAM. By default however, the Stack Pointer contains 07h at reset. The user can then change this to any value desired. The SP will point to the last used value. Therefore, the SP will be incremented and then address saved onto the stack. Conversely, while popping from the stack the contents will be read first, then the SP is decreased.

| BIT | NAME   |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | FUNC        | CTION                                                                                                                          |  |  |

|-----|--------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | SM0/FE | determines<br>below. Whe                                                                       | erial port mode select bit 0 or Framing Error Flag: The SMOD0 bit in PCON SFR<br>termines whether this bit acts as SM0 or as FE. The operation of SM0 is described<br>flow. When used as FE, this bit will be set to indicate an invalid stop bit. This bit<br>ust be manually cleared in software to clear the FE condition.                                                                                                                                                                                                                                                                                                                                   |                   |             |                                                                                                                                |  |  |

|     |        | Serial port N                                                                                  | lode l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | pit 1:            |             |                                                                                                                                |  |  |

|     |        | Mode: SM0                                                                                      | SM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description       | Length      | Baud rate                                                                                                                      |  |  |

| 6   | CM4    | 0 0                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Synchronous       | 8           | 4/12 Tclk                                                                                                                      |  |  |

| 6   | SM1    | 1 0                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Asynchronous      | 10          | Variable                                                                                                                       |  |  |

|     |        | 2 1                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Asynchronous      | 11          | 64/32 Tclk                                                                                                                     |  |  |

|     |        | 3 1                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Asynchronous      | 11          | Variable                                                                                                                       |  |  |

| 5   | SM2    | communicat<br>not be active<br>will not be a<br>controls the<br>of the oscilla<br>serial clock | Multiple processors communication. Setting this bit to 1 enables the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2 is set to 1, then RI will not be activated if the received 9th data bit (RB8) is 0. In mode 1, if SM2 = 1, then RI will not be activated if a valid stop bit was not received. In mode 0, the SM2 bit controls the serial port clock. If set to 0, then the serial port runs at a divide by 12 clock of the oscillator. This gives compatibility with the standard 8052. When set to 1, the serial clock become divide by 4 of the oscillator clock. This results in faster synchronous serial communication. |                   |             |                                                                                                                                |  |  |

| 4   | REN    | Receive ena<br>disabled.                                                                       | leceive enable: When set to 1 serial reception is enabled, otherwise reception is isabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |             |                                                                                                                                |  |  |

| 3   | TB8    |                                                                                                | This is the 9th bit to be transmitted in modes 2 and 3. This bit is set and cleared by oftware as desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |             |                                                                                                                                |  |  |

| 2   | RB8    |                                                                                                | n modes 2 and 3 this is the received 9th data bit. In mode 1, if SM2 = 0, RB8 is the stop bit that was received. In mode 0 it has no function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |             |                                                                                                                                |  |  |

| 1   | TI     | mode 0, or a                                                                                   | ransmit interrupt flag: This flag is set by hardware at the end of the 8th bit time in node 0, or at the beginning of the stop bit in all other modes during serial ansmission. This bit must be cleared by software.                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |             |                                                                                                                                |  |  |

| 0   | RI     | mode 0, or h                                                                                   | nalfwa<br>owev                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ly through the st | op bits tin | ardware at the end of the 8th bit time in<br>ne in the other modes during serial<br>apply to this bit. This bit can be cleared |  |  |

### SERIAL DATA BUFFER

|     | Bit:                        | 7        | 6                                                                                                                                                                                         | 5      | 4      | 3      | 2      | 1      | 0      | _ |

|-----|-----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|---|

|     |                             | SBUF.7   | SBUF.6                                                                                                                                                                                    | SBUF.5 | SBUF.4 | SBUF.3 | SBUF.2 | SBUF.1 | SBUF.0 |   |

|     | Mnemonic: SBUF Address: 99h |          |                                                                                                                                                                                           |        |        | -      |        |        |        |   |

| BIT | NAME                        | FUNCTION |                                                                                                                                                                                           |        |        |        |        |        |        |   |

| 7 0 |                             |          | Serial data on the serial port is read from or written to this location. It actually consists of two separate internal 8-bit registers. One is the receive resister, and the other is the |        |        |        |        |        |        |   |

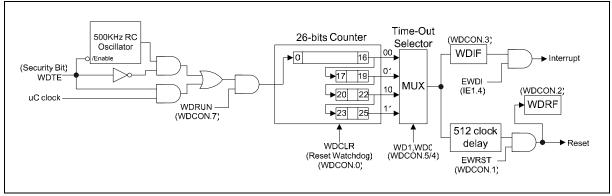

### WATCHDOG CONTROL

| IAME | IE FUNCTION                  |   |     |     |      |      |       |       |  |

|------|------------------------------|---|-----|-----|------|------|-------|-------|--|

|      | Mnemonic: WDCON Address: D8h |   |     |     |      |      |       |       |  |

|      | WDRUN                        | - | WD1 | WD0 | WDIF | WTRF | EWRST | WDCLR |  |

| Bit: | 7                            | 6 | 5   | 4   | 3    | 2    | 1     | 0     |  |

|      |                              |   |     |     |      |      |       |       |  |

| BIT | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | WDRUN | 0: The Watchdog is stopped.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| '   | WDRUN | 1: The Watchdog is running.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 6   | -     | Reserved.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 5   | WD1   | Watchdog Timer times selected.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 4   | WD0   | Vatchdog Timer times selected.                                                                                                                                                                                                                                                                                                                               |  |  |  |

|     |       | Watchdog Timer Interrupt Flag                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 3   |       | 0: If the interrupt is not enabled, then this bit indicates that the time-out period has elapsed. This bit must be cleared by software.                                                                                                                                                                                                                      |  |  |  |

|     |       | 1: If the watchdog interrupt is enabled, hardware will set this bit to indicate that the watchdog interrupt has occurred.                                                                                                                                                                                                                                    |  |  |  |

|     |       | Watchdog Timer Reset Flag                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2   |       | 1: Hardware will set this bit when the watchdog timer causes a reset. Software can read it but must clear it manually. A power-fail reset will also clear the bit. This bit helps software in determining the cause of a reset. If EWRST = 0, the watchdog timer will have no affect on this bit.                                                            |  |  |  |

| 4   | EWRST | 0: Disable Watchdog Timer Reset.                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 1   | EWRSI | 1: Enable Watchdog Timer Reset.                                                                                                                                                                                                                                                                                                                              |  |  |  |

|     |       | Reset Watchdog Timer                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0   | WDCLR | This bit helps in putting the watchdog timer into a know state. It also helps in resetting the watchdog timer before a time-out occurs. Failing to set the EWRST before time-out will cause an interrupt, if EWDI (IE1.4) is set, and 512 clocks after that a watchdog timer reset will be generated if EWRST is set. This bit is self-clearing by hardware. |  |  |  |

The WDCON SFR is set to a 0x0000x0B on an reset. WTRF (WDCON.2) is set to a 1 on a Watchdog timer reset, but to a 0 on power on/down resets. WDIF (WDCON.3) is not altered by an external reset. EWRST (WDCON.1) is set to 0 on a Power-on reset and unaffected by other resets.

All the bits in this SFR have unrestricted read access. EWRST, WDIF and WDCLR require Timed Access procedure to write. The remaining bits have unrestricted write accesses. Please refer TA register description.

| ТА    | REG | C7H |

|-------|-----|-----|

| WDCON | REG | D8H |

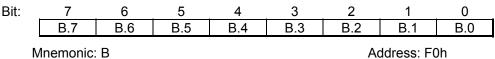

### **B REGISTER**

B.7-0: The B register is the standard 8052 register that serves as a second accumulator.

#### Port 0 Digital Input Disable

| Bit: | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

|      | P0ID.7 | P0ID.6 | P0ID.5 | P0ID.4 | P0ID.3 | P0ID.2 | P0ID.1 | P0ID.0 |

Address: F6h

Mnemonic: P0ID

| BIT | NAME           | FUNCTION                                                                                                       |

|-----|----------------|----------------------------------------------------------------------------------------------------------------|

| 7~0 | P0ID.7 ~P0ID.0 | Enable/Disable Port 0 digital inputs.<br>0: Enable Port 0 digital inputs.<br>1: Disable Port 0 digital inputs. |

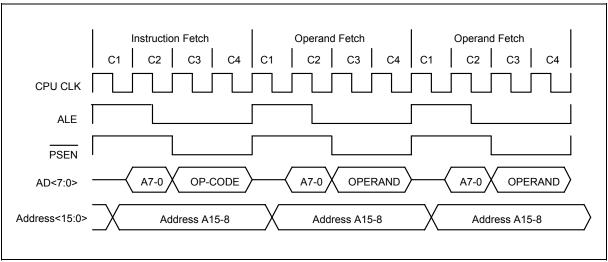

**Three Cycle Instruction Timing**

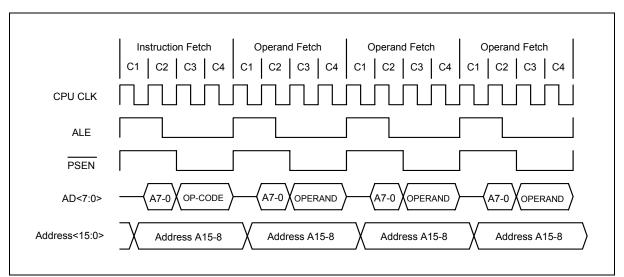

Four Cycle Instruction Timing

The WDCON SFR bits are set/cleared in reset condition depending on the source of the reset.

|       | External reset | Watchdog reset | Power on reset |

|-------|----------------|----------------|----------------|

| WDCON | 0x0x0xx0B      | 0x0x01x0B      | 0100000B       |

The WTRF bit WDCON.2 is set when the Watchdog timer causes a reset. A power on reset will also clear this bit. The EWRST bit WDCON.1 is cleared by power on resets. This disables the Watchdog timer resets. A watchdog or external reset does not affect the EWRST bit.

#### 12.3 Interrupt Response Time

The response time for each interrupt source depends on several factors, such as the nature of the

interrupt and the instruction underway. In the case of external interrupts INTO to RI+TI, they are sampled at C3 of every machine cycle and then their corresponding interrupt flags IEx will be set or reset. The Timer 0 and 1 overflow flags are set at C3 of the machine cycle in which overflow has occurred. These flag values are polled only in the next machine cycle. If a request is active and all three conditions are met, then the hardware generated LCALL is executed. This LCALL itself takes four machine cycles to be completed. Thus there is a minimum time of five machine cycles between the interrupt flag being set and the interrupt service routine being executed.

A longer response time should be anticipated if any of the three conditions are not met. If a higher or equal priority is being serviced, then the interrupt latency time obviously depends on the nature of the service routine currently being executed. If the polling cycle is not the last machine cycle of the instruction being executed, then an additional delay is introduced. The maximum response time (if no other interrupt is in service) occurs if the W79E82X series are performing a write to IE, IE1, IP0, IP0H, IP1 or IP1H and then executes a MUL or DIV instruction. From the time an interrupt source is activated, the longest reaction time is 12 machine cycles. This includes 1 machine cycle to detect the interrupt, 2 machine cycles to complete the IE, IE1, IP0, IP0H, IP1 or IP1H access, 5 machine cycles to complete the MUL or DIV instruction and 4 machine cycles to complete the hardware LCALL to the interrupt vector location.

Thus in a single-interrupt system the interrupt response time will always be more than 5 machine cycles and not more than 12 machine cycles. The maximum latency of 12 machine cycles is 48 clock cycles. Note that in the standard 8051 the maximum latency is 8 machine cycles which equals 96 machine cycles. This is a 50% reduction in terms of clock periods.

#### 12.4 Interrupt Inputs

The W79E82X series have 13 interrupts source, and two individual interrupt inputs sources, one is for IE0,IE1, BOF, KBF, WDT, ADC, CMF1 and CMF2, and other is IF0, IF1, RI+TI, SI and BKF. Two interrupt inputs are identical to those present on the standard 80C51 microcontroller as show in below figures.

If an external interrupt is enabled when the W79E82X series are put into Power Down or Idle mode, the interrupt will cause the processor to wake up and resume operation.

| BIT | NAME | FUNCTION                                                                                                           |

|-----|------|--------------------------------------------------------------------------------------------------------------------|

| 7~0 |      | The NVM address:<br>The register is indicated NVM data memory of low byte address on On-Chip<br>code memory space. |

Mnemonic: NVMADDR

Address: C6h

## 15. WATCHDOG TIMER

The Watchdog Timer is a free-running Timer which can be programmed by the user to serve as a system monitor, a time-base generator or an event timer. It is basically a set of dividers that divide the system clock. The divider output is selectable and determines the time-out interval. When the time-out occurs a flag is set, which can cause an interrupt if enabled, and a system reset can also be caused if it is enabled. The interrupt will occur if the individual interrupt enable and the global enable are set. The interrupt and reset functions are independent of each other and may be used separately or together depending on the users software.

Watchdog Timer

The Watchdog Timer should first be restarted by using WDCLR. This ensures that the timer starts from a known state. The WDCLR bit is used to restart the Watchdog Timer. This bit is self clearing, i.e. after writing a 1 to this bit the software will automatically clear it. The Watchdog Timer will now count clock cycles. The time-out interval is selected by the two bits WD1 and WD0 (WDCON.5 and WDCON.4). When the selected time-out occurs, the Watchdog interrupt flag WDIF (WDCON.3) is set. After the time-out has occurred, the Watchdog Timer waits for an additional 512 clock cycles. If the Watchdog Reset EWRST (WDCON.1) is enabled, then 512 clocks after the time-out, if there is no WDCLR, a system reset due to Watchdog Timer will occur. This will last for two machine cycles, and the Watchdog Timer reset flag WDRF (WDCON.2) will be set. This indicates to the software that the Watchdog was the cause of the reset.

When used as a simple timer, the reset and interrupt functions are disabled. The timer will set the WDIF flag each time the timer completes the selected time interval. The WDIF flag is polled to detect a time-out and the WDCLR allows software to restart the timer. The Watchdog Timer can also be used as a very long timer. The interrupt feature is enabled in this case. Every time the time-out occurs an interrupt will occur if the global interrupt enable EA is set.

The main use of the Watchdog Timer is as a system monitor. This is important in real-time control applications. In case of some power glitches or electro-magnetic interference, the processor may begin to execute errant code. If this is left unchecked the entire system may crash. Using the watchdog timer interrupt during software development will allow the user to select ideal watchdog reset locations. The code is first written without the watchdog interrupt or reset. Then the Watchdog interrupt is enabled to identify code locations where interrupt occurs. The user can now insert instructions to reset the Watchdog Timer, which will allow the code to run without any Watchdog Timer

- 63 -

Serial Port Mode 0

The TI flag is set high in C1 following the end of transmission of the last bit. The serial port will receive data when REN is 1 and RI is zero. The shift clock (TxD) will be activated and the serial port will latch data on the rising edge of shift clock. The external device should therefore present data on the falling edge on the shift clock. This process continues till all the 8 bits have been received. The RI flag is set in C1 following the last rising edge of the shift clock on TxD. This will stop reception, till the RI is cleared by software.

### 16.2 MODE 1

In Mode 1, the full duplex asynchronous mode is used. Serial communication frames are made up of 10 bits transmitted on TXD and received on RXD. The 10 bits consist of a start bit (0), 8 data bits (LSB first), and a stop bit (1). On received, the stop bit goes into RB8 in the SFR SCON. The baud rate in this mode is variable. The serial baud can be programmed to be 1/16 or 1/32 of the Timer 1 overflow. Since the Timer 1 can be set to different reload values, a wide variation in baud rates is possible.

Transmission begins with a write to SBUF. The serial data is brought out on to TxD pin at C1 following the first roll-over of divide by 16 counter. The next bit is placed on TxD pin at C1 following the next rollover of the divide by 16 counter. Thus the transmission is synchronized to the divide by 16 counter and not directly to the write to SBUF signal. After all 8 bits of data are transmitted, the stop bit is transmitted. The TI flag is set in the C1 state after the stop bit has been put out on TxD pin. This will be at the 10th rollover of the divide by 16 counter after a write to SBUF.

The all PWM control registers are PWMCON1, PWMCON2, and PWMCON3 register, and function description as below.

#### PWM Counter Low Bits Register

BIT NAME **FUNCTION** 7~0 PWM Counter low bit 7~0 register PWMP.7 ~PWMP.0

PWM Counter High Bits Register

| BI  | NAME             | FUNCTION                          |

|-----|------------------|-----------------------------------|

| 7~2 | - 2              | Reserved                          |

| 1~( | ) PWMP.9 ~PWMP.8 | PWM Counter high bit 9~8 register |

PWM 0 Low Bits Register

PWM0L(DAH)

| BIT | NAME           | FUNCTION                   |

|-----|----------------|----------------------------|

| 7~0 | PWM0.7 ~PWM0.0 | PWM 0 low bit 7~0 register |

PWM 1 Low Bits Register

PWM1L(DBH)

| BIT | NAME           | FUNCTION                   |

|-----|----------------|----------------------------|

| 7~0 | PWM1.7 ~PWM1.0 | PWM 1 low bit 7~0 register |

PWM 2 Low Bits Register

#### PWM2L(DDH)

| BIT | NAME           | FUNCTION                   |

|-----|----------------|----------------------------|

| 7~0 | PWM2.7 ~PWM2.0 | PWM 2 low bit 7~0 register |

#### PWM 3 Low Bits Register

#### PWM3L(DEH)

| BIT | NAME           | FUNCTION                  |

|-----|----------------|---------------------------|

| 7~0 | PWM3.7 ~PWM3.0 | PWM3 low bit 7~0 register |

PWMPL(D9H)

PWMPH(D1H)

selects one of 4 analog channels. An ADC conversion in progress is unaffected by an external or software ADC start. The result of a completed conversion remains unaffected provided ADCI = logic 1; a new ADC conversion already in progress is aborted when the idle or power down mode is entered. The result of a completed conversion (ADCI = logic 1) remains unaffected when entering the idle mode.

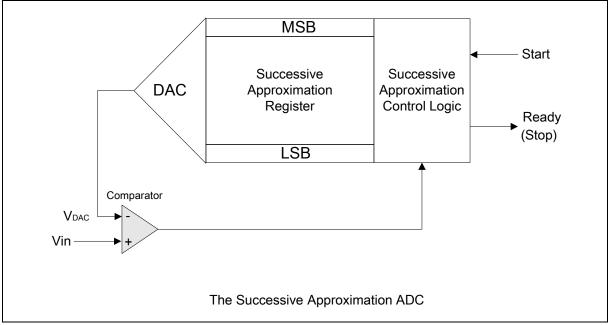

**Successive Approximation ADC**

### 24.1 ADC Resolution and Analog Supply:

The ADC circuit has its own supply pins (AVDD and AVSS) and one pins (Vref+) connected to each end of the DAC's resistance-ladder that the AVDD and Vref+ are connected to VDD and AVSS is connected to VSS. The ladder has 1023 equally spaced taps, separated by a resistance of "R". The first tap is located 0.5×R above AVSS, and the last tap is located 0.5×R below Vref+. This gives a total ladder resistance of 1024×R. This structure ensures that the DAC is monotonic and results in a symmetrical quantization error.

For input voltages between VSS and [(Vref+) +  $\frac{1}{2}$  LSB], the 10-bit result of an A/D conversion will be 000000000B = 000H. For input voltages between [(Vref+) -  $\frac{3}{2}$  LSB] and Vref+, the result of a conversion will be 111111111B = 3FFH. Vref+ and AVSS may be between AVDD + 0.2V and VSS - 0.2 V. Vref+ should be positive with respect to VSS, and the input voltage (Vin ) should be between Vref+ and VSS.

The result can always be calculated from the following formula:

Result =  $1024 \times \frac{\text{Vin}}{\text{Vref}}$  or Result =  $1024 \times \frac{\text{Vin}}{\text{VDD}}$

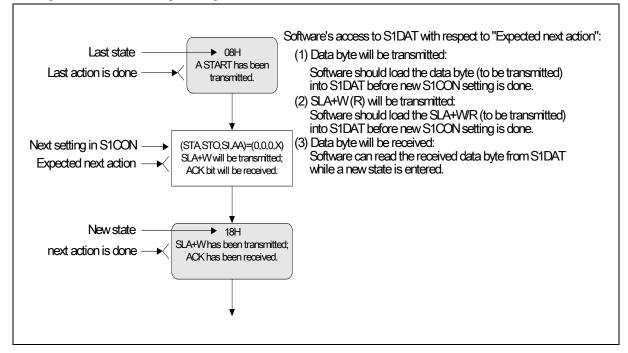

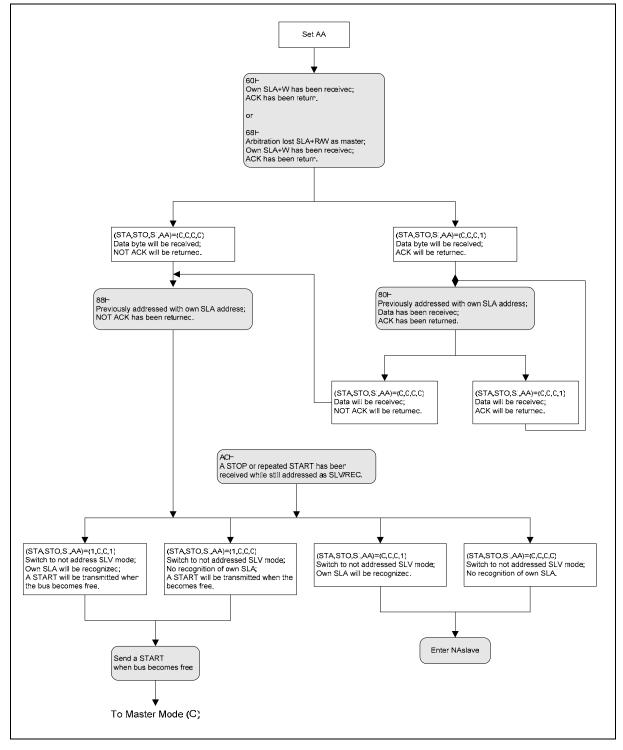

### 25.3 Operating Modes of I2C

The four operating modes are: Master/Transmitter, Master/Receiver, Slave/Transmitter and Slave/Receiver. Bits STA, STO and AA in I2CON decide the next action the SIO1 hardware will take after SI is cleared. When the next action is completed, a new status code in I2STATUS will be updated and SI will be set by hardware in the same time. Now, the interrupt service routine is entered (if the SI interrupt is enabled), the new status code can be used to decide which appropriate service routine the software is to branch. Data transfers in each mode are shown in the following figures.

#### \*\*\* Legend for the following four figures:

#### **Slave Receiver Mode**

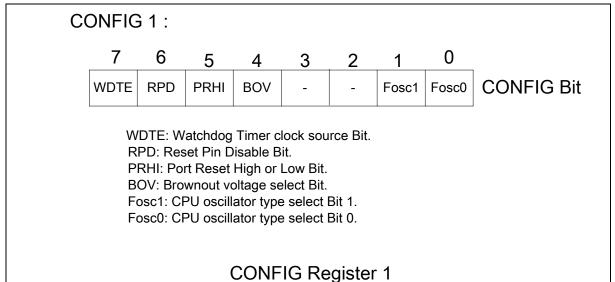

## 27. CONFIG BITS

The W79E82X series have two CONFIG bits(CONFIG1, CONFIG2) that must be define at power up and can not be set after the program start of execution. Those features are configured through the use of two flash EPROM bytes, and the flash EPROM can be programmed and verified repeatedly. Until the code inside the Flash EPROM is confirmed OK, the code can be protected. The protection of flash EPROM (CONFIG2) and those operations on it are described below. The data of these bytes may be read by the MOVC instruction at the addresses.

### 27.1 CONFIG1

| BIT | NAME | FUNCTION                                                                      |

|-----|------|-------------------------------------------------------------------------------|

| 7   | WDTE | Clock source of Watchdog Timer select bit:                                    |

|     |      | 0: The internal RC oscillator clock is for Watchdog Timer clock used.         |

|     |      | 1: The uC clock is for Watchdog Timer clock used.                             |

|     |      | Reset Pin Disable bit:                                                        |

| 6   | RPD  | 0: Enable Reset function of Pin 1.5.                                          |

|     |      | 1: Disable Reset function of Pin 1.5, and it to be used as an input port pin. |

|     | PRHI | Port Reset High or Low bit:                                                   |

| 5   |      | 0: Port reset to low state.                                                   |

|     |      | 1: Port reset to high state.                                                  |

|     |      | Brownout Voltage Select bit:                                                  |

| 4   | BOV  | 0: Brownout detect voltage is 3.8V.                                           |

|     |      | 1: Brownout detect voltage is 2.5V.                                           |