Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1933-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                    | Function | Input<br>Type    | Output<br>Type | Description                                                                                       |  |  |  |

|-----------------------------------------------------------------------------------------|----------|------------------|----------------|---------------------------------------------------------------------------------------------------|--|--|--|

| RB5/AN13/CPS5/P2B/CCP3 <sup>(1)</sup> /<br>P3A <sup>(1)</sup> /T1G <sup>(1)</sup> /COM1 | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up.    |  |  |  |

|                                                                                         | AN13     | AN               | —              | A/D Channel input.                                                                                |  |  |  |

|                                                                                         | CPS5     | AN               | _              | Capacitive sensing input.                                                                         |  |  |  |

|                                                                                         | P2B      | _                | CMOS           | PWM output.                                                                                       |  |  |  |

|                                                                                         | CCP3     | ST               | CMOS           | Capture/Compare/PWM.                                                                              |  |  |  |

|                                                                                         | P3A      | _                | CMOS           | PWM output.                                                                                       |  |  |  |

|                                                                                         | T1G      | ST               | —              | Timer1 gate input.                                                                                |  |  |  |

|                                                                                         | COM1     | _                | AN             | LCD Analog output.                                                                                |  |  |  |

| RB6/ICSPCLK/ICDCLK/SEG14                                                                | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |  |

|                                                                                         | ICSPCLK  | ST               | _              | Serial Programming Clock.                                                                         |  |  |  |

|                                                                                         | ICDCLK   | ST               | _              | In-Circuit Debug Clock.                                                                           |  |  |  |

|                                                                                         | SEG14    | _                | AN             | LCD Analog output.                                                                                |  |  |  |

| RB7/ICSPDAT/ICDDAT/SEG13                                                                | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up.    |  |  |  |

|                                                                                         | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                   |  |  |  |

|                                                                                         | ICDDAT   | ST               | CMOS           | In-Circuit Data I/O.                                                                              |  |  |  |

|                                                                                         | SEG13    | _                | AN             | LCD Analog output.                                                                                |  |  |  |

| RC0/T1OSO/T1CKI/P2B <sup>(1)</sup>                                                      | RC0      | ST               | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                                                                                         | T10SO    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                     |  |  |  |

|                                                                                         | T1CKI    | ST               | —              | Timer1 clock input.                                                                               |  |  |  |

|                                                                                         | P2B      |                  | CMOS           | PWM output.                                                                                       |  |  |  |

| RC1/T1OSI/CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup>                                       | RC1      | ST               | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                                                                                         | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                     |  |  |  |

|                                                                                         | CCP2     | ST               | CMOS           | Capture/Compare/PWM.                                                                              |  |  |  |

|                                                                                         | P2A      | _                | CMOS           | PWM output.                                                                                       |  |  |  |

| RC2/CCP1/P1A/SEG3                                                                       | RC2      | ST               | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                                                                                         | CCP1     | ST               | CMOS           | Capture/Compare/PWM.                                                                              |  |  |  |

|                                                                                         | P1A      | _                | CMOS           | PWM output.                                                                                       |  |  |  |

|                                                                                         | SEG3     | _                | AN             | LCD Analog output.                                                                                |  |  |  |

| RC3/SCK/SCL/SEG6                                                                        | RC3      | ST               | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                                                                                         | SCK      | ST               | CMOS           | SPI clock.                                                                                        |  |  |  |

|                                                                                         | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C <sup>™</sup> clock.                                                              |  |  |  |

|                                                                                         | SEG6     | _                | AN             | LCD Analog output.                                                                                |  |  |  |

| RC4/SDI/SDA/T1G <sup>(1)</sup> /SEG11                                                   | RC4      | ST               | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                                                                                         | SDI      | ST               | _              | SPI data input.                                                                                   |  |  |  |

|                                                                                         | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C™ data input/output.                                                              |  |  |  |

|                                                                                         | T1G      | ST               | _              | Timer1 gate input.                                                                                |  |  |  |

|                                                                                         | SEG11    | _                | AN             | LCD Analog output.                                                                                |  |  |  |

| RC5/SDO/SEG10                                                                           | RC5      | ST               | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                                                                                         | SDO      | —                | CMOS           | SPI data output.                                                                                  |  |  |  |

|                                                                                         | SEG10    |                  | AN             | LCD Analog output.                                                                                |  |  |  |

**TABLE 1-2:** PIC16(L)F1933 PINOUT DESCRIPTION (CONTINUED)

Note 1: Pin function is selectable via the APFCON register.

2: PIC16F1933 devices only.

### 6.11 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1     | 1  | 0   | х   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1     | 1  | 0   | х   | 0  | х  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1     | 1  | 0   | х   | х  | 0  | Illegal, PD is set on POR                                         |

| 0      | 0      | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | u1 uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

## 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | L EEDATL |    | ;                    |

|---------|----------|----|----------------------|

| MOVF    | EEDATL,  | W  | ;EEDATL not changed  |

|         |          |    | ;from previous write |

| BSF     | EECON1,  | RD | ;YES, Read the       |

|         |          |    | ;value written       |

| XORWF   | EEDATL,  | W  | ;                    |

| BTFSS   | STATUS,  | Ζ  | ;Is data the same    |

| GOTO    | WRITE_E  | RR | ;No, handle error    |

| :       |          |    | ;Yes, continue       |

|         |          |    |                      |

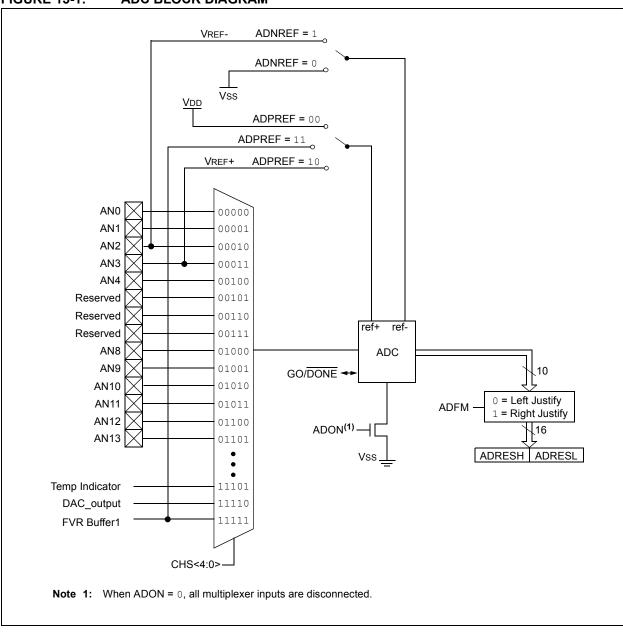

## 15.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 15-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

### FIGURE 15-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

|         | i      | i      | i      | i      |                   | i         | i          | i      | i                   |

|---------|--------|--------|--------|--------|-------------------|-----------|------------|--------|---------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3             | Bit 2     | Bit 1      | Bit 0  | Register<br>on Page |

| CM1CON0 | C10N   | C1OUT  | C10E   | C1POL  |                   | C1SP      | C1HYS      | C1SYNC | 163                 |

| CM2CON0 | C2ON   | C2OUT  | C2OE   | C2POL  | _                 | C2SP      | C2HYS      | C2SYNC | 163                 |

| CM1CON1 | C1NTP  | C1INTN | C1PCI  | H<1:0> | _                 | —         | C1NCI      | H<1:0> | 164                 |

| CM2CON1 | C2NTP  | C2INTN | C2PCI  | H<1:0> | _                 | —         | C2NCI      | H<1:0> | 164                 |

| CMOUT   | —      | _      | —      | —      | _                 | —         | MC2OUT     | MC10UT | 164                 |

| FVRCON  | FVREN  | FVRRDY | TSEN   | TSRNG  | TSRNG CDAFVR<1:0> |           | ADFVR<1:0> |        | 135                 |

| DACCON0 | DACEN  | DACLPS | DACOE  | —      | DACPS             | S<1:0>    | —          | DACNSS | 156                 |

| DACCON1 | —      | _      | —      |        |                   | DACR<4:0> |            |        | 156                 |

| INTCON  | GIE    | PEIE   | TMR0IE | INTE   | IOCIE             | TMR0IF    | INTF       | IOCIF  | 82                  |

| PIE2    | OSFIE  | C2IE   | C1IE   | EEIE   | BCLIE             | LCDIE     | —          | CCP2IE | 84                  |

| PIR2    | OSFIF  | C2IF   | C1IF   | EEIF   | BCLIF             | LCDIF     | _          | CCP2IF | 87                  |

| TRISA   | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3            | TRISA2    | TRISA1     | TRISA0 | 116                 |

| TRISB   | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3            | TRISB2    | TRISB1     | TRISB0 | 121                 |

| ANSELA  | _      | _      | ANSA5  | ANSA4  | ANSA3             | ANSA2     | ANSA1      | ANSA0  | 117                 |

| ANSELB  | _      | _      | ANSB5  | ANSB4  | ANSB3             | ANSB2     | ANSB1      | ANSB0  | 122                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

## 21.11 Register Definitions: Timer1 Control

## REGISTER 21-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u         | R/W-0/u                      | R/W-0/u                                     | R/W-0/u          | R/W-0/u          | R/W-0/u          | U-0           | R/W-0/u        |  |  |  |

|-----------------|------------------------------|---------------------------------------------|------------------|------------------|------------------|---------------|----------------|--|--|--|

| TMR1CS<1:0>     |                              | T1CKP                                       | T1CKPS<1:0>      |                  | T1SYNC           | _             | TMR10N         |  |  |  |

| bit 7           |                              |                                             |                  |                  |                  |               | bit 0          |  |  |  |

|                 |                              |                                             |                  |                  |                  |               |                |  |  |  |

| Legend:         |                              |                                             |                  |                  |                  |               |                |  |  |  |

| R = Readable    | e bit                        | W = Writable                                | bit              | U = Unimpler     | nented bit, read | as '0'        |                |  |  |  |

| u = Bit is unc  | hanged                       | x = Bit is unkn                             | iown             | -n/n = Value a   | t POR and BOI    | R/Value at al | l other Resets |  |  |  |

| '1' = Bit is se | t                            | '0' = Bit is clea                           | ared             |                  |                  |               |                |  |  |  |

| h# 7 0          | THEACE                       | Ob . Time and Class                         | le Course Cole   | at hita          |                  |               |                |  |  |  |

| bit 7-6         |                              | 0>: Timer1 Cloc                             |                  |                  |                  |               |                |  |  |  |

|                 |                              | clock source is                             |                  | -                | (CAPOSC)         |               |                |  |  |  |

|                 |                              | clock source is  <br>CEN = 0:               | pin or oscillato | Dr:              |                  |               |                |  |  |  |

|                 |                              | I clock from T10                            | CKI pin (on the  | risina edae)     |                  |               |                |  |  |  |

|                 |                              | CEN = 1:                                    |                  | , nonig eage)    |                  |               |                |  |  |  |

|                 |                              | oscillator on T1                            | OSI/T1OSO p      | ins              |                  |               |                |  |  |  |

|                 |                              | lock source is system clock (Fosc)          |                  |                  |                  |               |                |  |  |  |

|                 | 00 <b>= Timer1</b>           | clock source is i                           | instruction clo  | ck (Fosc/4)      |                  |               |                |  |  |  |

| bit 5-4         | T1CKPS<1:                    | 0>: Timer1 Inpu                             | t Clock Presca   | ale Select bits  |                  |               |                |  |  |  |

|                 | 11 = 1:8 Pre                 |                                             |                  |                  |                  |               |                |  |  |  |

|                 |                              | scale value                                 |                  |                  |                  |               |                |  |  |  |

|                 | 01 = 1:2 Pre<br>00 = 1:1 Pre |                                             |                  |                  |                  |               |                |  |  |  |

| bit 3           |                              | _P Oscillator En                            | able Control b   | bit              |                  |               |                |  |  |  |

|                 |                              | ed Timer1 oscilla                           |                  |                  |                  |               |                |  |  |  |

|                 |                              | ed Timer1 oscilla                           |                  |                  |                  |               |                |  |  |  |

| bit 2           | T1SYNC: Tir                  | mer1 External C                             | lock Input Syr   | nchronization Co | ontrol bit       |               |                |  |  |  |

|                 | <u>TMR1CS&lt;1:</u>          | 0>=1X                                       |                  |                  |                  |               |                |  |  |  |

|                 |                              | 1 = Do not synchronize external clock input |                  |                  |                  |               |                |  |  |  |

|                 | 0 = Synchro                  | onize external clo                          | ock input with   | system clock (F  | OSC)             |               |                |  |  |  |

|                 | <u>TMR1CS&lt;1:</u>          | <b>0&gt; =</b> <u>0X</u>                    |                  |                  |                  |               |                |  |  |  |

|                 | This bit is igr              | nored.                                      |                  |                  |                  |               |                |  |  |  |

| bit 1           | 1 Unimplemented: Read as '0' |                                             |                  |                  |                  |               |                |  |  |  |

| bit 0           | TMR1ON: T                    | imer1 On bit                                |                  |                  |                  |               |                |  |  |  |

|                 | 1 = Enables Timer1           |                                             |                  |                  |                  |               |                |  |  |  |

|                 | 1 = Enables                  | Timer1                                      |                  |                  |                  |               |                |  |  |  |

### 23.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

### 23.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see Section 12.1 "Alternate Pin Function" for more information.

| Name    | Bit 7                                                                      | Bit 6               | Bit 5        | Bit 4          | Bit 3            | Bit 2      | Bit 1  | Bit 0   | Register<br>on Page |

|---------|----------------------------------------------------------------------------|---------------------|--------------|----------------|------------------|------------|--------|---------|---------------------|

| APFCON  | —                                                                          | CCP3SEL             | T1GSEL       | P2BSEL         | SRNQSEL          | C2OUTSEL   | SSSEL  | CCP2SEL | 114                 |

| CCPxCON | PxM<                                                                       | 1:0> <sup>(1)</sup> | DCxB         | <1:0>          |                  | CCPxM<     | :3:0>  |         | 214                 |

| CCPRxL  | Capture/Co                                                                 | mpare/PWM           | Register x l | Low Byte (LS   | SB)              |            |        |         | 192                 |

| CCPRxH  | Capture/Co                                                                 | mpare/PWM           | Register x I | High Byte (M   | ISB)             |            |        |         | 192                 |

| INTCON  | GIE                                                                        | PEIE                | TMR0IE       | INTE           | IOCIE            | TMR0IF     | INTF   | IOCIF   | 82                  |

| PIE1    | TMR1GIE                                                                    | ADIE                | RCIE         | TXIE           | SSPIE            | CCP1IE     | TMR2IE | TMR1IE  | 83                  |

| PIE2    | OSFIE                                                                      | C2IE                | C1IE         | EEIE           | BCLIE            | LCDIE      | _      | CCP2IE  | 84                  |

| PIE3    |                                                                            | CCP5IE              | CCP4IE       | CCP3IE         | TMR6IE           |            | TMR4IE | —       | 85                  |

| PIR1    | TMR1GIF                                                                    | ADIF                | RCIF         | TXIF           | SSPIF            | CCP1IF     | TMR2IF | TMR1IF  | 86                  |

| PIR2    | OSFIF                                                                      | C2IF                | C1IF         | EEIF           | BCLIF            | LCDIF      |        | CCP2IF  | 87                  |

| PIR3    | —                                                                          | CCP5IF              | CCP4IF       | CCP3IF         | TMR6IF           | —          | TMR4IF | —       | 88                  |

| T1CON   | TMR1C                                                                      | S<1:0>              | T1CKP        | S<1:0>         | T1OSCEN          | T1SYNC     | _      | TMR10N  | 183                 |

| T1GCON  | TMR1GE                                                                     | T1GPOL              | T1GTM        | T1GSPM         | T1GGO/DONE       | T1GVAL     | T1GS   | S<1:0>  | 184                 |

| TMR1L   | Holding Reg                                                                | gister for the      | Least Signif | ficant Byte of | f the 16-bit TMR | 1 Register |        |         | 179                 |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                     |              |                |                  |            |        |         | 179                 |

| TRISA   | TRISA7                                                                     | TRISA6              | TRISA5       | TRISA4         | TRISA3           | TRISA2     | TRISA1 | TRISA0  | 116                 |

| TRISB   | TRISB7                                                                     | TRISB6              | TRISB5       | TRISB4         | TRISB3           | TRISB2     | TRISB1 | TRISB0  | 121                 |

| TRISC   | TRISC7                                                                     | TRISC6              | TRISC5       | TRISC4         | TRISC3           | TRISC2     | TRISC1 | TRISC0  | 125                 |

### TABLE 23-4: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Compare mode.

Note 1: Applies to ECCP modules only.

### 24.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see Section 24.5.6 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

### 24.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPCON3 register is set, the BCLIF bit of the PIR register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

### 24.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 24-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPIF bit.

- 4. Slave hardware generates an ACK and sets SSPIF.

- 5. SSPIF bit is cleared by user.

- 6. Software reads the received address from SSPBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

### REGISTER 24-2: SSPCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/0        | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0/0                                                                                                           | R/W-0/0                                                                                       | R/W-0/0                                                                                                                      | R/W-0/0                                                      | R/W-0/0                                                              | R/W-0/0                                            |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------|--|

| WCOL              | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SSPEN                                                                                                             | CKP                                                                                           |                                                                                                                              | SSPN                                                         | /<3:0>                                                               |                                                    |  |

| bit 7             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |                                                                                               |                                                                                                                              |                                                              |                                                                      | bit                                                |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |                                                                                               |                                                                                                                              |                                                              |                                                                      |                                                    |  |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |                                                                                               |                                                                                                                              |                                                              |                                                                      |                                                    |  |

| R = Readable b    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | W = Writable bi                                                                                                   |                                                                                               | •                                                                                                                            | nted bit, read as                                            |                                                                      | <b>.</b> .                                         |  |

| u = Bit is unchar | nged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | x = Bit is unkno                                                                                                  |                                                                                               |                                                                                                                              |                                                              | /alue at all other F                                                 |                                                    |  |

| '1' = Bit is set  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '0' = Bit is clear                                                                                                | ed                                                                                            | HS = Bit is set I                                                                                                            | by hardware                                                  | C = User cleare                                                      | d                                                  |  |

| bit 7             | Master mode:<br>1 = A write to a<br>started<br>0 = No collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                 |                                                                                               | pted while the I <sup>2</sup> C                                                                                              | conditions were                                              | not valid for a tra                                                  | nsmission to b                                     |  |

|                   | 0 = No collisio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | on                                                                                                                |                                                                                               | ll transmitting the p                                                                                                        | revious word (mu                                             | st be cleared in sof                                                 | tware)                                             |  |

| bit 6             | $\frac{\text{In SPI mode:}}{1 = \text{A new byte}}$ $\frac{1 = \text{A new byte}}{\text{SSPSR is}}$ $\frac{1}{\text{ion} (\text{and tr})}$ $\frac{1 = \text{No overflo}}{1 = \text{A byte is for }}$                                                                                                                                                                                                                                                                                                                                                                                                                        | lost. Overflow can<br>mitting data, to av<br>ransmission) is ini<br>w<br>received while th<br>node (must be cl    | e the SSPBUF r<br>n only occur in s<br>oid setting over<br>titated by writing<br>ne SSPBUF re | egister is still holdir<br>Slave mode. In Sla<br>flow. In Master mo<br>g to the SSPBUF re<br>gister is still holdin<br>are). | ve mode, the use<br>de, the overflow b<br>egister (must be o | er must read the S<br>bit is not set since of<br>cleared in software | SPBUF, even if<br>each new rece <sub>l</sub><br>). |  |

| bit 5             | <ul> <li>SSPEN: Synchronous Serial Port Enable bit</li> <li>In both modes, when enabled, these pins must be properly configured as input or output In SPI mode:</li> <li>1 = Enables serial port and configures SCK, SDO, SDI and SS as the source of the serial port pins<sup>(2)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> <li>In I<sup>2</sup>C mode:</li> <li>1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<sup>(3)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                                                                                                                   |                                                                                               |                                                                                                                              |                                                              |                                                                      |                                                    |  |

| bit 4             | 0 = Idle state for<br>$\frac{\ln l^2C}{SCL}$ so $\frac{1}{1}$ = Enable close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | or clock is a high<br>or clock is a low l<br>o <u>ode:</u><br>ontrol<br>ck<br>k low (clock streto<br><u>node:</u> | evel                                                                                          | nsure data setup t                                                                                                           | ime.)                                                        |                                                                      |                                                    |  |

### REGISTER 24-3: SSPCON2: SSP CONTROL REGISTER 2

| R/W-0/0          | R-0/0                                                                                                                                                        | R/W-0/0                                           | R/S/HS-0/0                     | R/S/HS-0/0                   | R/S/HS-0/0        | R/S/HS-0/0       | R/W/HS-0/0   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|------------------------------|-------------------|------------------|--------------|

| GCEN             | ACKSTAT                                                                                                                                                      | ACKDT                                             | ACKEN                          | RCEN                         | PEN               | RSEN             | SEN          |

| bit 7            |                                                                                                                                                              |                                                   |                                |                              |                   |                  | bit C        |

|                  |                                                                                                                                                              |                                                   |                                |                              |                   |                  |              |

| Legend:          |                                                                                                                                                              |                                                   |                                |                              |                   |                  |              |

| R = Readable     | e bit                                                                                                                                                        | W = Writable                                      | bit                            | U = Unimpler                 | mented bit, read  | 1 as '0'         |              |

| u = Bit is unc   | hanged                                                                                                                                                       | x = Bit is unk                                    | nown                           | -n/n = Value a               | at POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is set | t                                                                                                                                                            | '0' = Bit is cle                                  | eared                          | HC = Cleared                 | d by hardware     | S = User set     |              |

| bit 7            | 1 = Enable in                                                                                                                                                | nterrupt when a                                   | •                              | .,                           | or 00h) is receiv | red in the SSPS  | SR           |

|                  |                                                                                                                                                              | call address di                                   |                                |                              |                   |                  |              |

| bit 6            | 1 = Acknowle                                                                                                                                                 | cknowledge Si<br>edge was not r<br>edge was recei |                                | mode only)                   |                   |                  |              |

| bit 5            |                                                                                                                                                              | -                                                 | ı bit (in I <sup>2</sup> C moo | de only)                     |                   |                  |              |

|                  | In Receive m                                                                                                                                                 | i <u>ode:</u><br>litted when the<br>lowledge      | ·                              | • •                          | le sequence at    | the end of a re  | ceive        |

| bit 4            | ACKEN: Ack                                                                                                                                                   | nowledge Seq                                      | uence Enable                   | bit (in I <sup>2</sup> C Mas | ter mode only)    |                  |              |

|                  | In Master Re                                                                                                                                                 | ceive mode:                                       |                                | ,                            |                   |                  |              |

|                  | Automat                                                                                                                                                      | Acknowledge<br>ically cleared b<br>edge sequenc   | y hardware.                    | SDA and S                    | CL pins, and      | transmit ACF     | KDT data bit |

| bit 3            | RCEN: Rece                                                                                                                                                   | ive Enable bit                                    | (in I <sup>2</sup> C Master i  | mode only)                   |                   |                  |              |

|                  |                                                                                                                                                              | Receive mode                                      | · _                            | .,                           |                   |                  |              |

| bit 2            | PEN: Stop Co                                                                                                                                                 | ondition Enabl                                    | e bit (in I <sup>2</sup> C Ma  | ster mode only               | y)                |                  |              |

|                  |                                                                                                                                                              | Release Contro                                    | _                              |                              |                   |                  |              |

|                  | 0 = Stop cond                                                                                                                                                | dition Idle                                       |                                |                              | atically cleared  |                  |              |

| bit 1            |                                                                                                                                                              |                                                   |                                |                              | ster mode only)   |                  |              |

|                  | <ul> <li>1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = Repeated Start condition Idle</li> </ul> |                                                   |                                |                              |                   |                  |              |

| bit 0            | SEN: Start C                                                                                                                                                 | ondition Enabl                                    | e/Stretch Enab                 | le bit                       |                   |                  |              |

|                  | <u>In Master mo</u><br>1 = Initiate St<br>0 = Start con                                                                                                      | tart condition o                                  | n SDA and SC                   | L pins. Autom                | atically cleared  | by hardware.     |              |

|                  |                                                                                                                                                              |                                                   |                                | ave transmit ar              | nd slave receive  | e (stretch enab  | led)         |

| Note 1: Fo       | or bits ACKEN, F                                                                                                                                             | RCEN, PEN, R                                      | SEN, SEN: If ti                | he I <sup>2</sup> C module   | is not in the IdI | e mode, this bi  | t may not be |

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

### 27.11 LCD Interrupts

The LCD module provides an interrupt in two cases. An interrupt when the LCD controller goes from active to inactive controller. An interrupt also provides unframe boundaries for Type B waveform. The LCD timing generation provides an interrupt that defines the LCD frame timing.

#### 27.11.1 LCD INTERRUPT ON MODULE SHUTDOWN

An LCD interrupt is generated when the module completes shutting down (LCDA goes from '1' to '0').

### 27.11.2 LCD FRAME INTERRUPTS

A new frame is defined to begin at the leading edge of the COM0 common signal. The interrupt will be set immediately after the LCD controller completes accessing all pixel data required for a frame. This will occur at a fixed interval before the frame boundary (TFINT), as shown in Figure 27-19. The LCD controller will begin to access data for the next frame within the interval from the interrupt to when the controller begins to access data after the interrupt (TFWR). New data must be written within TFWR, as this is when the LCD controller will begin to access the data for the next frame.

When the LCD driver is running with Type-B waveforms and the LMUX<1:0> bits are not equal to '00' (static drive), there are some additional issues that must be addressed. Since the DC voltage on the pixel takes two frames to maintain zero volts, the pixel data must not change between subsequent frames. If the pixel data were allowed to change, the waveform for the odd frames would not necessarily be the complement of the waveform generated in the even frames and a DC component would be introduced into the panel. Therefore, when using Type-B waveforms, the user must synchronize the LCD pixel updates to occur within a subframe after the frame interrupt.

To correctly sequence writing while in Type-B, the interrupt will only occur on complete phase intervals. If the user attempts to write when the write is disabled, the WERR bit of the LCDCON register is set and the write does not occur.

| Note: | The LCD frame interrupt is not generated |

|-------|------------------------------------------|

|       | when the Type-A waveform is selected     |

|       | and when the Type-B with no multiplex    |

|       | (static) is selected.                    |

## 29.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

### TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| n     | FSR or INDF number. (0-1)                                                                                                                                                            |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                          |

### TABLE 29-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-out bit    |

| С     | Carry bit       |

| DC    | Digit carry bit |

| Z     | Zero bit        |

| PD    | Power-down bit  |

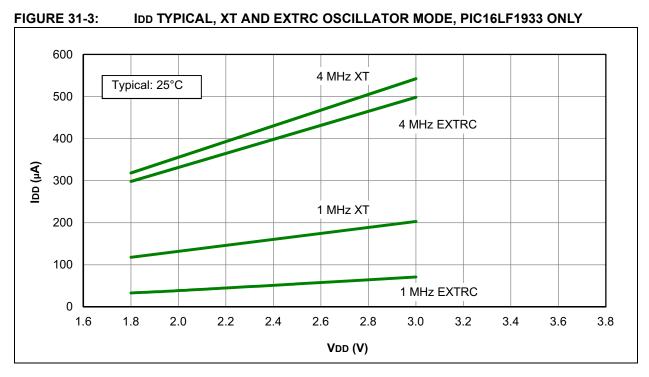

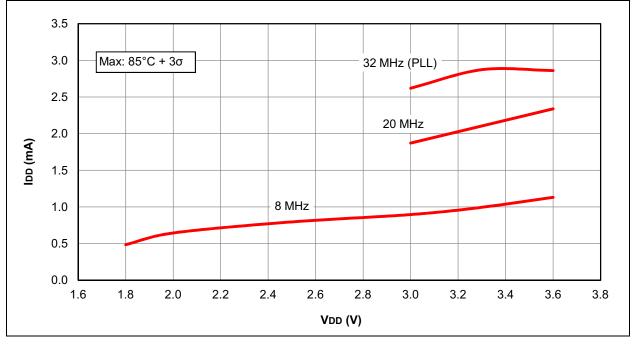

## 30.2 DC Characteristics: Supply Currents (IDD)

| PIC16LF1933 |                                     |      | Operating temperature |      |                                                                                                                                | itions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                 |  |

|-------------|-------------------------------------|------|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|

| PIC16F1933  |                                     |      |                       |      | litions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                                                               |                                                                                 |  |

| Param       | Device                              |      |                       |      |                                                                                                                                |                                                                                                                               | Conditions                                                                      |  |

| No.         | Characteristics                     | Min. | Тур†                  | Max. | Units                                                                                                                          | VDD                                                                                                                           | Note                                                                            |  |

|             | Supply Current (IDD) <sup>(1)</sup> | , 2) |                       |      |                                                                                                                                |                                                                                                                               |                                                                                 |  |

| D009        | LDO Regulator                       | -    | 350                   | —    | μA                                                                                                                             | —                                                                                                                             | HS, EC OR INTOSC/INTOSCIO (8-16 MHz)<br>Clock modes with all VCAP pins disabled |  |

|             |                                     |      | 50                    | _    | μA                                                                                                                             |                                                                                                                               | All VCAP pins disabled                                                          |  |

|             |                                     |      | 30                    | —    | μΑ                                                                                                                             |                                                                                                                               | VCAP enabled                                                                    |  |

|             |                                     | —    | 5                     | —    | μA                                                                                                                             | —                                                                                                                             | LP Clock mode and Sleep<br>(requires FVR and BOR to be disabled)                |  |

| D010        |                                     | _    | 8                     | 14   | μA                                                                                                                             | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |

|             |                                     | -    | 12                    | 18   | μA                                                                                                                             | 3.0                                                                                                                           | LP Oscillator mode (Note 4),<br>$-40^{\circ}C \le TA \le +85^{\circ}C$          |  |

| D010        |                                     | _    | 23                    | 63   | μA                                                                                                                             | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |

|             |                                     |      | 28                    | 74   | μA                                                                                                                             | 3.0                                                                                                                           | LP Oscillator mode (Note 4, Note 5),                                            |  |

|             |                                     | —    | 33                    | 79   | μA                                                                                                                             | 5.0                                                                                                                           | $-40^{\circ}C \le TA \le +85^{\circ}C$                                          |  |

| D010A       |                                     | _    | 10                    | 18   | μA                                                                                                                             | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |

|             |                                     | -    | 15                    | 20   | μΑ                                                                                                                             | 3.0                                                                                                                           | LP Oscillator mode (Note 4)<br>-40°C $\leq$ TA $\leq$ +125°C                    |  |

| D010A       |                                     | —    | 24                    | 79   | μA                                                                                                                             | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |

|             |                                     | _    | 30                    | 93   | μA                                                                                                                             | 3.0                                                                                                                           | LP Oscillator mode (Note 4, Note 5)                                             |  |

|             |                                     | —    | 35                    | 99   | μA                                                                                                                             | 5.0                                                                                                                           | $-40^{\circ}C \le TA \le +125^{\circ}C$                                         |  |