Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1933-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                | Name    | Bit 7                                                                                                     | Bit 6                                                    | Bit 5          | Bit 4         | Bit 3        | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------|---------------|--------------|-------------|-------|-------|----------------------|---------------------------------|

| Bank 4                 |         |                                                                                                           |                                                          |                |               |              |             |       |       |                      |                                 |

| 200h <sup>(2)</sup>    | INDF0   | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                                                          |                |               |              |             |       |       | XXXX XXXX            | **** ****                       |

| 201h <sup>(2)</sup>    | INDF1   |                                                                                                           | this location ical register)                             | uses contents  | s of FSR1H/F  | SR1L to addr | ess data me | mory  |       | XXXX XXXX            | **** ****                       |

| 202h <sup>(2)</sup>    | PCL     | Program C                                                                                                 | ounter (PC) L                                            | east Significa | nt Byte       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 203h <sup>(2)</sup>    | STATUS  | _                                                                                                         | _                                                        | _              | TO            | PD           | Z           | DC    | С     | 1 1000               | q quuu                          |

| 204h <sup>(2)</sup>    | FSR0L   | Indirect Dat                                                                                              | ta Memory Ac                                             | dress 0 Low    | Pointer       |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 205h <sup>(2)</sup>    | FSR0H   | Indirect Dat                                                                                              | ta Memory Ac                                             | dress 0 High   | Pointer       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 206h <sup>(2)</sup>    | FSR1L   | Indirect Dat                                                                                              | ta Memory Ac                                             | dress 1 Low    | Pointer       |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 207h <sup>(2)</sup>    | FSR1H   | Indirect Dat                                                                                              | ta Memory Ac                                             | dress 1 High   | Pointer       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 208h <sup>(2)</sup>    | BSR     | _                                                                                                         | _                                                        | _              |               |              | BSR<4:0>    |       |       | 0 0000               | 0 0000                          |

| 209h <sup>(2)</sup>    | WREG    | Working Re                                                                                                | Working Register                                         |                |               |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 20Ah <sup>(1, 2)</sup> | PCLATH  | _                                                                                                         | Write Buffer for the upper 7 bits of the Program Counter |                |               |              |             |       |       | -000 0000            | -000 0000                       |

| 20Bh <sup>(2)</sup>    | INTCON  | GIE                                                                                                       | PEIE                                                     | TMR0IE         | INTE          | IOCIE        | TMR0IF      | INTF  | IOCIF | 0000 0000            | 0000 0000                       |

| 20Ch                   | _       | Unimpleme                                                                                                 | Unimplemented                                            |                |               |              |             |       |       | _                    | _                               |

| 20Dh                   | WPUB    | WPUB7                                                                                                     | WPUB6                                                    | WPUB5          | WPUB4         | WPUB3        | WPUB2       | WPUB1 | WPUB0 | 1111 1111            | 1111 1111                       |

| 20Eh                   | _       | Unimpleme                                                                                                 | nted                                                     |                |               |              |             |       |       | _                    | _                               |

| 20Fh                   | _       | Unimpleme                                                                                                 | ented                                                    |                |               |              |             |       |       | _                    | _                               |

| 210h                   | WPUE    | _                                                                                                         | _                                                        | _              | _             | WPUE3        | _           | _     | _     | 1                    | 1                               |

| 211h                   | SSPBUF  | Synchrono                                                                                                 | us Serial Port                                           | Receive Buff   | er/Transmit R | Register     |             |       |       | XXXX XXXX            | uuuu uuuu                       |

| 212h                   | SSPADD  |                                                                                                           |                                                          |                | ADD<          | :7:0>        |             |       |       | 0000 0000            | 0000 0000                       |

| 213h                   | SSPMSK  |                                                                                                           |                                                          |                | MSK<          | :7:0>        |             |       |       | 1111 1111            | 1111 1111                       |

| 214h                   | SSPSTAT | SMP                                                                                                       | CKE                                                      | D/A            | Р             | S            | R/W         | UA    | BF    | 0000 0000            | 0000 0000                       |

| 215h                   | SSPCON1 | WCOL                                                                                                      | SSPOV                                                    | SSPEN          | СКР           |              | SSPM        | <3:0> |       | 0000 0000            | 0000 0000                       |

| 216h                   | SSPCON2 | GCEN                                                                                                      | ACKSTAT                                                  | ACKDT          | ACKEN         | RCEN         | PEN         | RSEN  | SEN   | 0000 0000            | 0000 0000                       |

| 217h                   | SSPCON3 | ACKTIM                                                                                                    | PCIE                                                     | SCIE           | BOEN          | SDAHT        | SBCDE       | AHEN  | DHEN  | 0000 0000            | 0000 0000                       |

| 218h                   | _       | Unimpleme                                                                                                 | nted                                                     |                |               |              | •           |       | •     | _                    | _                               |

| 219h                   | _       | Unimpleme                                                                                                 | ented                                                    |                |               |              |             |       |       | _                    | _                               |

| 21Ah                   | —       | Unimpleme                                                                                                 | nted                                                     |                |               |              |             |       |       | _                    | _                               |

| 21Bh                   | —       | Unimpleme                                                                                                 | ented                                                    |                |               |              |             |       |       | _                    | _                               |

| 21Ch                   | —       | Unimpleme                                                                                                 | ented                                                    |                |               |              |             |       |       | _                    | _                               |

| 21Dh                   | —       | Unimpleme                                                                                                 | ented                                                    |                |               |              |             |       |       | _                    | _                               |

| 21Eh                   | —       | Unimpleme                                                                                                 | nted                                                     |                |               |              |             |       |       | _                    | _                               |

| 21Fh                   |         | Unimpleme                                                                                                 | ented                                                    |                |               |              |             |       |       | _                    | _                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-9**:

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter. Note 1: 2:

These registers can be addressed from any bank.

3: Unimplemented, read as '1'.

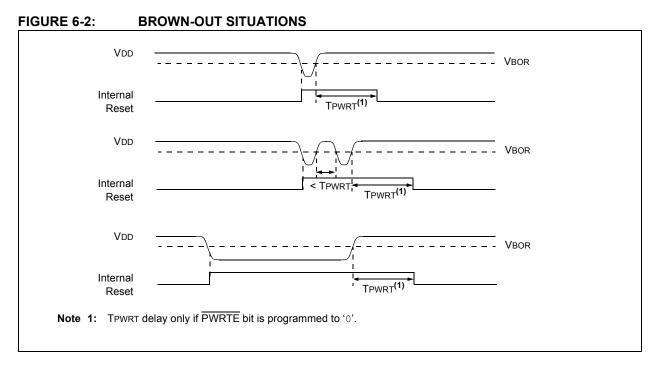

### 6.3 Register Definitions: BOR Control

### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN  | —   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |     |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit         |

|---------|-----------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words ≠ 01:         |

|         | SBOREN is read/write, but has no effect on the BOR. |

|         | If BOREN <1:0> in Configuration Words = 01:         |

|         | 1 = BOR Enabled                                     |

|         | 0 = BOR Disabled                                    |

| bit 6-1 | Unimplemented: Read as '0'                          |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit    |

|         | 1 = The Brown-out Reset circuit is active           |

|         | 0 = The Brown-out Reset circuit is inactive         |

### 6.11 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1     | 1  | 0   | х   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1     | 1  | 0   | х   | 0  | х  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1     | 1  | 0   | х   | х  | 0  | Illegal, PD is set on POR                                         |

| 0      | 0      | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | u1 uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

### 7.6.4 PIR1 REGISTER

### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0              | ) R/W-0/0                             | R-0/0                        | R-0/0           | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|----------------------|---------------------------------------|------------------------------|-----------------|-------------------|------------------|------------------|-------------|

| TMR1GI               | F ADIF                                | RCIF                         | TXIF            | SSPIF             | CCP1IF           | TMR2IF           | TMR1IF      |

| bit 7                |                                       |                              |                 |                   |                  | •                | bit (       |

|                      |                                       |                              |                 |                   |                  |                  |             |

| Legend:<br>R = Reada | ble bit                               | W = Writable                 | hit             | II – I Inimpler   | nented bit, read | 1 as 'O'         |             |

| u = Bit is u         |                                       | x = Bit is unk               |                 |                   |                  | R/Value at all c | thar Pasata |

| '1' = Bit is s       | •                                     | '0' = Bit is cle             |                 |                   | at FOR and BO    |                  |             |

| 1 - Dit 13 (         | 501                                   |                              |                 |                   |                  |                  |             |

| bit 7                | TMR1GIF: ⊤                            | imer1 Gate Inte              | errupt Flag bit |                   |                  |                  |             |

|                      | 1 = Interrupt                         |                              |                 |                   |                  |                  |             |

|                      | -                                     | is not pending               |                 |                   |                  |                  |             |

| bit 6                |                                       | onverter Interru             | upt Flag bit    |                   |                  |                  |             |

|                      | 1 = Interrupt<br>0 = Interrupt        | is penaing<br>is not pending |                 |                   |                  |                  |             |

| bit 5                |                                       | T Receive Inte               | rrupt Flag bit  |                   |                  |                  |             |

|                      | 1 = Interrupt                         |                              |                 |                   |                  |                  |             |

|                      | 0 = Interrupt                         | is not pending               |                 |                   |                  |                  |             |

| bit 4                |                                       | T Transmit Inte              | rrupt Flag bit  |                   |                  |                  |             |

|                      | 1 = Interrupt                         | is pending<br>is not pending |                 |                   |                  |                  |             |

| bit 3                | -                                     |                              | Port (MSSP)     | Interrupt Flag b  | sit              |                  |             |

| DIL J                | 1 = Interrupt                         |                              |                 | interrupt i lag i | Л                |                  |             |

|                      |                                       | is not pending               |                 |                   |                  |                  |             |

| bit 2                | CCP1IF: CC                            | P1 Interrupt Fla             | ag bit          |                   |                  |                  |             |

|                      | 1 = Interrupt                         |                              |                 |                   |                  |                  |             |

|                      | -                                     | is not pending               |                 |                   |                  |                  |             |

| bit 1                |                                       | er2 to PR2 Int               | errupt Flag bit |                   |                  |                  |             |

|                      | 1 = Interrupt                         | is pending<br>is not pending |                 |                   |                  |                  |             |

| bit 0                | -                                     | er1 Overflow I               | nterrunt Elan k | hit               |                  |                  |             |

| bit o                | 1 = Interrupt                         |                              | incirupt ridg i |                   |                  |                  |             |

|                      |                                       | is not pending               |                 |                   |                  |                  |             |

| Note:                | Interrupt flag bits a                 | are set when ar              | n interrupt     |                   |                  |                  |             |

|                      | condition occurs,                     |                              |                 |                   |                  |                  |             |

|                      | its corresponding<br>Enable bit, GIE, |                              |                 |                   |                  |                  |             |

|                      | User software                         | should ens                   |                 |                   |                  |                  |             |

|                      | appropriate interru                   | pt flag bits are             |                 |                   |                  |                  |             |

|                      | to enabling an inte                   | errupt.                      |                 |                   |                  |                  |             |

### **10.1** Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See the Electrical Specifications Chapters for the LFINTOSC tolerances.

### 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| TABLE 10-1: | WDT OPERATING MODES |

|-------------|---------------------|

|-------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | V      | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 01        | 1      | Х              | Active      |

| UI        | 0      | х              | Disabled    |

| 00        | Х      | Х              | Disabled    |

### TABLE 10-2: WDT CLEARING CONDITIONS

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

### 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail

- · WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 10-2 for more information.

### 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0** "Memory Organization" and STATUS register (Register 3-1) for more information.

| Conditions                                               | WDT                          |  |

|----------------------------------------------------------|------------------------------|--|

| WDTE<1:0> = 00                                           |                              |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |  |

| CLRWDT Command                                           | Cleared                      |  |

| Oscillator Fail Detected                                 |                              |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |

| Name   | Bit 7  | Bit 6 | Bit 5        | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|--------|-------|--------------|-------|-------|-------|----------|--------|---------------------|

| OSCCON | SPLLEN |       | IRCF<3:0>    |       |       | —     | SCS<1:0> |        | 66                  |

| STATUS | —      | -     | —            | TO    | PD    | Z     | DC       | С      | 18                  |

| WDTCON | _      | _     | — WDTPS<4:0> |       |       |       |          | SWDTEN | 97                  |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2       | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------------|---------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> CPI |         | CPD     | 10                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | FOSC<2:0>      |         |         | 46                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

### 11.3.2 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the EEADRH:EEADRL register pair with the address of new row to be erased.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD, FREE and WREN bits of the EECON1 register.

- 4. Write 55h, then AAh, to EECON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the EECON1 register to begin the erase operation.

- Poll the FREE bit in the EECON1 register to determine when the row erase has completed.

#### See Example 11-4.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

### 11.3.3 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the starting address of the word(s) to be programmed.

- 2. Load the write latches with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 11-2 (block writes to program memory with eight write latches) for more details. The write latches are aligned to the address boundary defined by EEADRL as shown in Table 11-1. Write operations do not cross these boundaries. At the completion of a program memory write operation, the write latches are reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a block of program memory. These steps are divided into two parts. First, all write latches are loaded with data except for the last program memory location. Then, the last write latch is loaded and the programming sequence is initiated. A special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. This unlock sequence should not be interrupted.

- 1. Set the EEPGD and WREN bits of the EECON1 register.

- 2. Clear the CFGS bit of the EECON1 register.

- Set the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the EEADRH:EEADRL register pair with the address of the location to be written.

- 5. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The write latch is now loaded.

- 7. Increment the EEADRH:EEADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- 11. Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The entire latch block is now written to Flash program memory.

It is not necessary to load the entire write latch block with user program data. However, the entire write latch block will be written to program memory.

An example of the complete write sequence for eight words is shown in Example 11-5. The initial address is loaded into the EEADRH:EEADRL register pair; the eight words of data are loaded using indirect addressing.

Note: The code sequence provided in Example 11-5 must be repeated multiple times to fully program an erased program memory row.

NOTES:

|         | i      | i      | i      | i         |                        | i      | i      | i      | i                   |

|---------|--------|--------|--------|-----------|------------------------|--------|--------|--------|---------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4     | Bit 3                  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

| CM1CON0 | C10N   | C10UT  | C10E   | C1POL     |                        | C1SP   | C1HYS  | C1SYNC | 163                 |

| CM2CON0 | C2ON   | C2OUT  | C2OE   | C2POL     | _                      | C2SP   | C2HYS  | C2SYNC | 163                 |

| CM1CON1 | C1NTP  | C1INTN | C1PCI  | H<1:0>    | _                      | —      | C1NCI  | H<1:0> | 164                 |

| CM2CON1 | C2NTP  | C2INTN | C2PCI  | H<1:0>    | — — C2NCH<1:0>         |        | H<1:0> | 164    |                     |

| CMOUT   | —      | _      | —      | —         | _                      | —      | MC2OUT | MC10UT | 164                 |

| FVRCON  | FVREN  | FVRRDY | TSEN   | TSRNG     | CDAFVR<1:0> ADFVR<1:0> |        | R<1:0> | 135    |                     |

| DACCON0 | DACEN  | DACLPS | DACOE  | —         | DACPS                  | S<1:0> | —      | DACNSS | 156                 |

| DACCON1 | —      | _      | —      | DACR<4:0> |                        |        |        |        | 156                 |

| INTCON  | GIE    | PEIE   | TMR0IE | INTE      | IOCIE                  | TMR0IF | INTF   | IOCIF  | 82                  |

| PIE2    | OSFIE  | C2IE   | C1IE   | EEIE      | BCLIE                  | LCDIE  | —      | CCP2IE | 84                  |

| PIR2    | OSFIF  | C2IF   | C1IF   | EEIF      | BCLIF                  | LCDIF  | —      | CCP2IF | 87                  |

| TRISA   | TRISA7 | TRISA6 | TRISA5 | TRISA4    | TRISA3                 | TRISA2 | TRISA1 | TRISA0 | 116                 |

| TRISB   | TRISB7 | TRISB6 | TRISB5 | TRISB4    | TRISB3                 | TRISB2 | TRISB1 | TRISB0 | 121                 |

| ANSELA  | _      | _      | ANSA5  | ANSA4     | ANSA3                  | ANSA2  | ANSA1  | ANSA0  | 117                 |

| ANSELB  | _      | _      | ANSB5  | ANSB4     | ANSB3                  | ANSB2  | ANSB1  | ANSB0  | 122                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

### 19.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- · Programmable input selection

- SR latch output is available externally

- Separate Q and  $\overline{Q}$  outputs

- · Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

### 19.1 Latch Operation

The latch is a Set-Reset Latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be set or reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync\_C2OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either comparator can be synchronized to the Timer1 clock source. See Section 18.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source is available that can periodically set or reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR latch, respectively.

### 19.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to an I/O pin at the same time. The  $\overline{Q}$  latch output pin function can be moved to an alternate pin using the SRNQSEL bit of the APFCON register.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

### 19.3 Effects of a Reset

Upon any device Reset, the SR latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

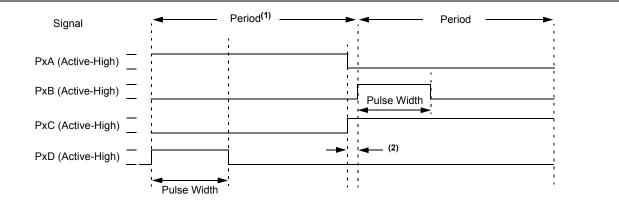

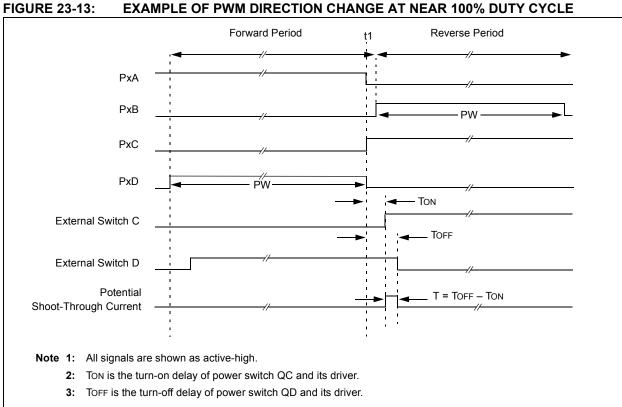

### 23.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the PxM1 bit in the CCPxCON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the PxM1 bit of the CCPxCON register. The following sequence occurs four Timer cycles prior to the end of the current PWM period:

- The modulated outputs (PxB and PxD) are placed in their inactive state.

- The associated unmodulated outputs (PxA and PxC) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 23-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn off time of the power switch, including the power device and driver circuit, is greater than the turn on time.

Figure 23-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output PxA and PxD become inactive, while output PxC becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices QC and QD (see Figure 23-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

### FIGURE 23-12: EXAMPLE OF PWM DIRECTION CHANGE

- **Note 1:** The direction bit PxM1 of the CCPxCON register is written any time during the PWM cycle.

- 2: When changing directions, the PxA and PxC signals switch before the end of the current PWM cycle. The modulated PxB and PxD signals are inactive at this time. The length of this time is four Timer counts.

### 23.4.6.1 Steering Synchronization

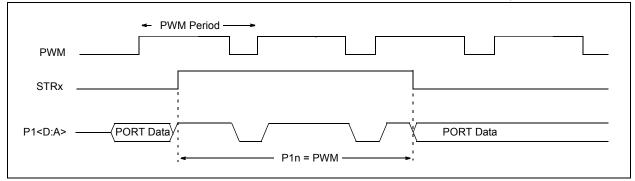

The STRxSYNC bit of the PSTRxCON register gives the user two selections of when the steering event will happen. When the STRxSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the Px<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

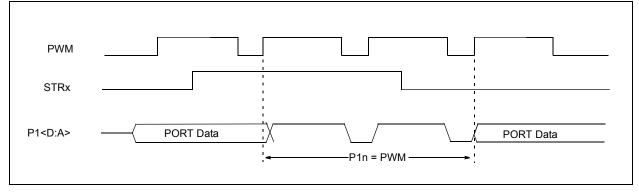

When the STRxSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 23-19 and 23-20 illustrate the timing diagrams of the PWM steering depending on the STRxSYNC setting.

### 23.4.7 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

The CCPxM<1:0> bits of the CCPxCON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (PxA/PxC and PxB/PxD). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The PxA, PxB, PxC and PxD output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMRxIF bit of the PIRx register being set as the second PWM period begins.

**Note:** When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the Off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

### FIGURE 23-19: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRxSYNC = 0)

### FIGURE 23-20: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRxSYNC = 1)

### 24.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  Slave in 10-bit Addressing mode.

Figure 24-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSPSTAT register is set.

- 4. Slave sends ACK and SSPIF is set.

- 5. Software clears the SSPIF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. Slave loads low address into SSPADD, releasing SCL.

- 8. Master sends matching low address byte to the Slave; UA bit is set.

**Note:** Updates to the SSPADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPIF is set.

**Note:** If the low address does not match, SSPIF and UA are still set so that the slave software can set SSPADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPIF.

- 11. Slave reads the received matching address from SSPBUF clearing BF.

- 12. Slave loads high address into SSPADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSPIF is set.

- 14. If SEN bit of SSPCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPIF.

- 16. Slave reads the received byte from SSPBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 24.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 24-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 24-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

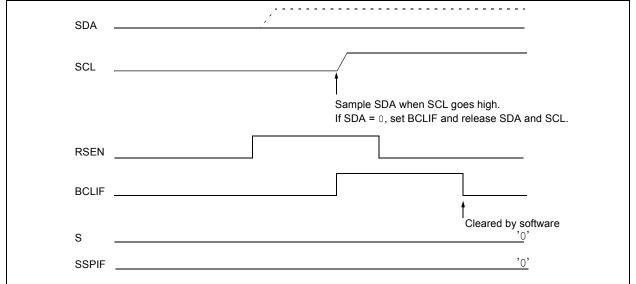

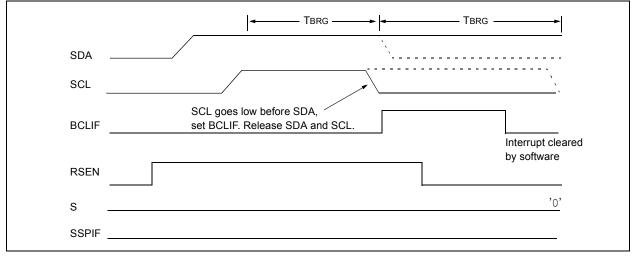

### 24.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from a low level to a high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 24-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 24-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 24-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### 26.5 Timer Resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

### 26.6 Fixed Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

| Note: | The fixed time base can not be generated  |

|-------|-------------------------------------------|

|       | by the timer resource that the capacitive |

|       | sensing oscillator is clocking.           |

### 26.6.1 TIMER0

To select Timer0 as the timer resource for the capacitive sensing module:

- Set the T0XCS bit of the CPSCON0 register.

- Clear the TMR0CS bit of the OPTION\_REG register.

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 20.0 "Timer0 Module"** for additional information.

### 26.6.2 TIMER1

To select Timer1 as the timer resource for the Capacitive Sensing module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified by using the Timer0 overflow flag.

It is recommend that the Timer0 overflow flag, in conjunction with the Toggle mode of the Timer1 gate, be used to develop the fixed time base required by the software portion of the Capacitive Sensing module. Refer to Section 21.11 "Register Definitions: Timer1 Control" for additional information.

TABLE 26-2: TIMER1 ENABLE FUNCTION

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

### 26.7 Software Control

The software portion of the capacitive sensing module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed time base to acquire counts on Timer0 or Timer1.

- Establishing the nominal frequency for the capacitive sensing oscillator.

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load.

- Set the frequency threshold.

### 26.7.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin.

- At the start of the fixed time base, clear the timer resource.

- At the end of the fixed time base save the value in the timer resource.

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base.

### 26.7.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin.

- Use the same fixed time base as the nominal frequency measurement.

- At the start of the fixed time base, clear the timer resource.

- At the end of the fixed time base save the value in the timer resource.

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base. This frequency should be less than the value obtained during the nominal frequency measurement.

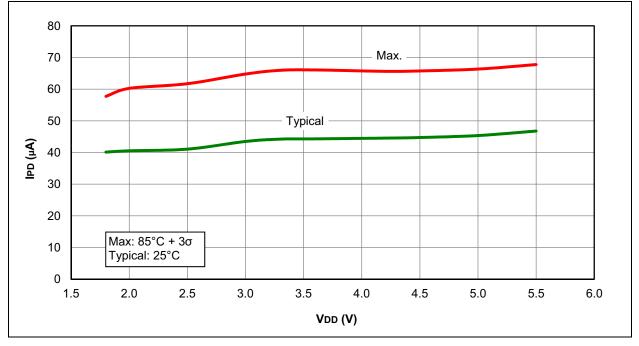

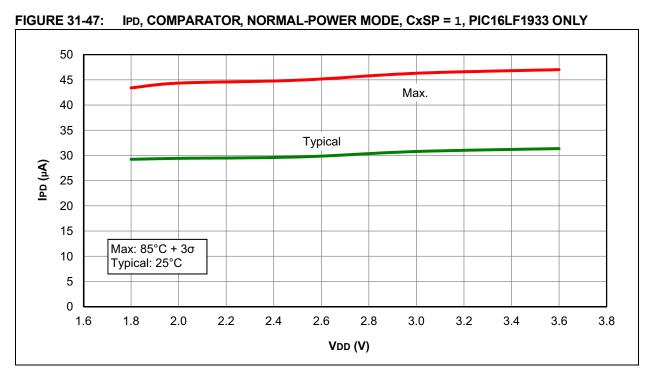

FIGURE 31-48: IPD, COMPARATOR, NORMAL-POWER MODE, CxSP = 1, PIC16F1933 ONLY