#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1933-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>TABLE 1-2:</b> | PIC16(L)F1933 PINOUT DESCRIPTION (CONTINUED) |

|-------------------|----------------------------------------------|

|-------------------|----------------------------------------------|

| Name                    | Function | Input<br>Type | Output<br>Type | Description                         |

|-------------------------|----------|---------------|----------------|-------------------------------------|

| RC6/TX/CK/CCP3/P3A/SEG9 | RC6      | ST            | CMOS           | General purpose I/O.                |

|                         | TX       | _             | CMOS           | USART asynchronous transmit.        |

|                         | СК       | ST            | CMOS           | USART synchronous clock.            |

|                         | CCP3     | ST            | CMOS           | Capture/Compare/PWM.                |

|                         | P3A      | _             | CMOS           | PWM output.                         |

|                         | SEG9     | _             | AN             | LCD Analog output.                  |

| RC7/RX/DT/P3B/SEG8      | RC7      | ST            | CMOS           | General purpose I/O.                |

|                         | RX       | ST            | _              | USART asynchronous input.           |

|                         | DT       | ST            | CMOS           | USART synchronous data.             |

|                         | P3B      | _             | CMOS           | PWM output.                         |

|                         | SEG8     | _             | AN             | LCD Analog output.                  |

| RE3/MCLR/VPP            | RE3      | TTL           | _              | General purpose input.              |

|                         | MCLR     | ST            | _              | Master Clear with internal pull-up. |

|                         | VPP      | HV            | _              | Programming voltage.                |

| VDD                     | Vdd      | Power         | _              | Positive supply.                    |

| Vss                     | Vss      | Power         | _              | Ground reference.                   |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C<sup>™</sup> = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

Note 1: Pin function is selectable via the APFCON register.

2: PIC16F1933 devices only.

### TABLE 3-4: PIC16(L)F1933 MEMORY MAP, BANKS 8-15

|      | BANK 8                       |      | BANK 9                       |      | BANK 10                      |      | BANK 11                      |      | BANK 12                      |      | BANK 13                      |      | BANK 14                      |      | BANK 15               |

|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|-----------------------|

| 400h | INDF0                        | 480h | INDF0                        | 500h | INDF0                        | 580h | INDF0                        | 600h | INDF0                        | 680h | INDF0                        | 700h | INDF0                        | 780h | INDF0                 |

| 401h | INDF1                        | 481h | INDF1                        | 501h | INDF1                        | 581h | INDF1                        | 601h | INDF1                        | 681h | INDF1                        | 701h | INDF1                        | 781h | INDF1                 |

| 402h | PCL                          | 482h | PCL                          | 502h | PCL                          | 582h | PCL                          | 602h | PCL                          | 682h | PCL                          | 702h | PCL                          | 782h | PCL                   |

| 403h | STATUS                       | 483h | STATUS                       | 503h | STATUS                       | 583h | STATUS                       | 603h | STATUS                       | 683h | STATUS                       | 703h | STATUS                       | 783h | STATUS                |

| 404h | FSR0L                        | 484h | FSR0L                        | 504h | FSR0L                        | 584h | FSR0L                        | 604h | FSR0L                        | 684h | FSR0L                        | 704h | FSR0L                        | 784h | FSR0L                 |

| 405h | FSR0H                        | 485h | FSR0H                        | 505h | FSR0H                        | 585h | FSR0H                        | 605h | FSR0H                        | 685h | FSR0H                        | 705h | FSR0H                        | 785h | FSR0H                 |

| 406h | FSR1L                        | 486h | FSR1L                        | 506h | FSR1L                        | 586h | FSR1L                        | 606h | FSR1L                        | 686h | FSR1L                        | 706h | FSR1L                        | 786h | FSR1L                 |

| 407h | FSR1H                        | 487h | FSR1H                        | 507h | FSR1H                        | 587h | FSR1H                        | 607h | FSR1H                        | 687h | FSR1H                        | 707h | FSR1H                        | 787h | FSR1H                 |

| 408h | BSR                          | 488h | BSR                          | 508h | BSR                          | 588h | BSR                          | 608h | BSR                          | 688h | BSR                          | 708h | BSR                          | 788h | BSR                   |

| 409h | WREG                         | 489h | WREG                         | 509h | WREG                         | 589h | WREG                         | 609h | WREG                         | 689h | WREG                         | 709h | WREG                         | 789h | WREG                  |

| 40Ah | PCLATH                       | 48Ah | PCLATH                       | 50Ah | PCLATH                       | 58Ah | PCLATH                       | 60Ah | PCLATH                       | 68Ah | PCLATH                       | 70Ah | PCLATH                       | 78Ah | PCLATH                |

| 40Bh | INTCON                       | 48Bh | INTCON                       | 50Bh | INTCON                       | 58Bh | INTCON                       | 60Bh | INTCON                       | 68Bh | INTCON                       | 70Bh | INTCON                       | 78Bh | INTCON                |

| 40Ch | —                            | 48Ch | —                            | 50Ch |                              | 58Ch |                              | 60Ch |                              | 68Ch | —                            | 70Ch |                              | 78Ch | _                     |

| 40Dh | —                            | 48Dh | —                            | 50Dh | —                            | 58Dh | —                            | 60Dh | —                            | 68Dh | —                            | 70Dh | _                            | 78Dh | —                     |

| 40Eh | —                            | 48Eh | —                            | 50Eh |                              | 58Eh |                              | 60Eh |                              | 68Eh | —                            | 70Eh | _                            | 78Eh | —                     |

| 40Fh | —                            | 48Fh | —                            | 50Fh | —                            | 58Fh | —                            | 60Fh | —                            | 68Fh | —                            | 70Fh | _                            | 78Fh | —                     |

| 410h | —                            | 490h | —                            | 510h | —                            | 590h | —                            | 610h | —                            | 690h | —                            | 710h | _                            | 790h | —                     |

| 411h | —                            | 491h | —                            | 511h | —                            | 591h | —                            | 611h | —                            | 691h | —                            | 711h | _                            | 791h |                       |

| 412h | —                            | 492h | —                            | 512h | _                            | 592h |                              | 612h |                              | 692h | —                            | 712h |                              | 792h |                       |

| 413h | _                            | 493h | _                            | 513h |                              | 593h |                              | 613h |                              | 693h |                              | 713h | _                            | 793h |                       |

| 414h | —                            | 494h | _                            | 514h |                              | 594h |                              | 614h |                              | 694h |                              | 714h | _                            | 794h |                       |

| 415h | TMR4                         | 495h | —                            | 515h |                              | 595h |                              | 615h |                              | 695h |                              | 715h |                              | 795h |                       |

| 416h | PR4                          | 496h | —                            | 516h |                              | 596h |                              | 616h |                              | 696h | _                            | 716h |                              | 796h |                       |

| 417h | T4CON                        | 497h | —                            | 517h | —                            | 597h | _                            | 617h |                              | 697h | _                            | 717h | _                            | 797h |                       |

| 418h | —                            | 498h | —                            | 518h | —                            | 598h |                              | 618h | —                            | 698h | —                            | 718h | _                            | 798h |                       |

| 419h | _                            | 499h | —                            | 519h | —                            | 599h | _                            | 619h | _                            | 699h | _                            | 719h | _                            | 799h |                       |

| 41Ah | _                            | 49Ah |                              | 51Ah |                              | 59Ah |                              | 61Ah |                              | 69Ah |                              | 71Ah |                              | 79Ah |                       |

| 41Bh | —                            | 49Bh | —                            | 51Bh | —                            | 59Bh |                              | 61Bh |                              | 69Bh |                              | 71Bh | _                            | 79Bh | See Table 3-7         |

| 41Ch | TMR6                         | 49Ch |                              | 51Ch |                              | 59Ch |                              | 61Ch |                              | 69Ch |                              | 71Ch |                              | 79Ch |                       |

| 41Dh | PR6                          | 49Dh | —                            | 51Dh | —                            | 59Dh | _                            | 61Dh | _                            | 69Dh | —                            | 71Dh | _                            | 79Dh |                       |

| 41Eh | T6CON                        | 49Eh |                              | 51Eh |                              | 59Eh |                              | 61Eh |                              | 69Eh |                              | 71Eh |                              | 79Eh |                       |

| 41Fh | _                            | 49Fh | —                            | 51Fh | —                            | 59Fh |                              | 61Fh |                              | 69Fh |                              | 71Fh | _                            | 79Fh |                       |

| 420h |                              | 4A0h |                              | 520h |                              | 5A0h |                              | 620h |                              | 6A0h |                              | 720h |                              | 7A0h |                       |

|      | Unimplemented<br>Read as '0' |      |                       |

| 46Fh |                              | 4EFh |                              | 56Fh |                              | 5EFh |                              | 66Fh |                              | 6EFh |                              | 76Fh |                              | 7EFh |                       |

| 470h |                              | 4F0h |                              | 570h |                              | 5F0h |                              | 670h |                              | 6F0h |                              | 770h |                              | 7F0h |                       |

|      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh |

| 47Fh |                              | 4FFh |                              | 57Fh |                              | 5FFh |                              | 67Fh |                              | 6FFh |                              | 77Fh |                              | 7FFh |                       |

Legend: = Unimplemented data memory locations, read as '0'.

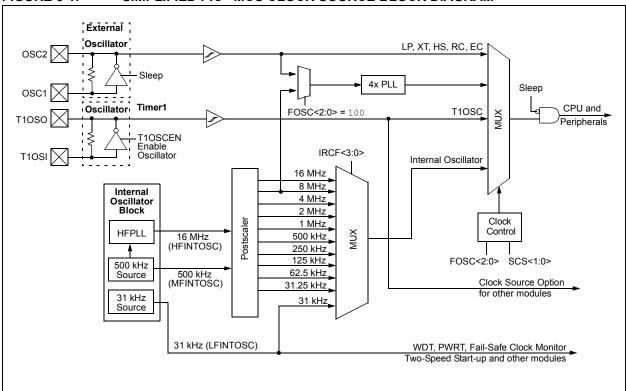

#### FIGURE 5-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

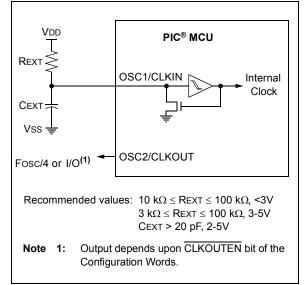

#### FIGURE 5-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

### 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables in Section 30.0 "Electrical Specifications".

### 5.6 Register Definitions: Oscillator Control

#### REGISTER 5-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0/0          | R/W-0/0                                                                                                       | R/W-1/1                                                                                                                                                                                                         | R/W-1/1                            | R/W-1/1         | U-0             | R/W-0/0         | R/W-0/0      |

|------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|-----------------|-----------------|--------------|

| SPLLEN           |                                                                                                               | IRCF                                                                                                                                                                                                            | <3:0>                              |                 | _               | SCS             | <1:0>        |

| bit 7            |                                                                                                               |                                                                                                                                                                                                                 |                                    |                 |                 |                 | bit 0        |

|                  |                                                                                                               |                                                                                                                                                                                                                 |                                    |                 |                 |                 |              |

| Legend:          |                                                                                                               |                                                                                                                                                                                                                 |                                    |                 |                 |                 |              |

| R = Readable     |                                                                                                               | W = Writable                                                                                                                                                                                                    |                                    | U = Unimplem    |                 |                 |              |

| u = Bit is unch  | nanged                                                                                                        | x = Bit is unkr                                                                                                                                                                                                 | iown                               | -n/n = Value a  | t POR and BO    | OR/Value at all | other Resets |

| '1' = Bit is set |                                                                                                               | '0' = Bit is clea                                                                                                                                                                                               | ared                               |                 |                 |                 |              |

| bit 7            | If PLLEN in (<br>SPLLEN bit i                                                                                 | Configuration W                                                                                                                                                                                                 | ords = <u>1:</u><br>LL is always e | nabled (subject | to oscillator r | equirements)    |              |

| bit 6-3          | 1111 = 16 M<br>1110 = 8 M<br>1101 = 4 M<br>1100 = 2 M<br>1011 = 1 M<br>1010 = 500<br>1001 = 250<br>1000 = 125 | Hz or 32 MHz H<br>Hz HF<br>Hz HF<br>kHz HF <sup>(1)</sup><br>kHz HF <sup>(1)</sup><br>kHz HF <sup>(1)</sup><br>kHz MF (defau<br>kHz MF<br>kHz MF<br>kHz MF<br>5 kHz MF<br>25 kHz HF <sup>(1)</sup><br>25 kHz MF | IF(see <mark>Sectio</mark>         | n 5.2.2.1 "HFIN | ITOSC")         |                 |              |

| bit 2            | Unimpleme                                                                                                     | nted: Read as '                                                                                                                                                                                                 | 0'                                 |                 |                 |                 |              |

| bit 1-0          | 1x = Internal<br>01 = Timer1                                                                                  |                                                                                                                                                                                                                 |                                    | Configuration W | /ords.          |                 |              |

Note 1: Duplicate frequency derived from HFINTOSC.

| R/W-x/u                               | R/W-x/u     | R/W-x/u         | R/W-x/u             | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|---------------------------------------|-------------|-----------------|---------------------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| RA7                                   | RA6         | RA5             | RA4                 | RA3                                                   | RA2     | RA1     | RA0     |  |  |  |

| bit 7                                 |             |                 |                     |                                                       |         |         | bit 0   |  |  |  |

|                                       |             |                 |                     |                                                       |         |         |         |  |  |  |

| Legend:                               |             |                 |                     |                                                       |         |         |         |  |  |  |

| R = Readable                          | e bit       | W = Writable    | bit                 | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unch                       | nanged      | x = Bit is unkr | iown                | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared |             |                 | ared                |                                                       |         |         |         |  |  |  |

|                                       |             |                 |                     |                                                       |         |         |         |  |  |  |

| bit 7-0                               | RA<7:0>: PC | ORTA I/O Value  | bits <sup>(1)</sup> |                                                       |         |         |         |  |  |  |

1 = Port pin is > VIH

0 = Port pin is < VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bits

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

### REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATA<7:0>: PORTA Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

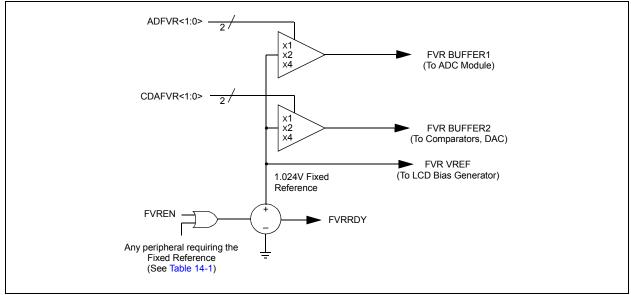

#### FIGURE 14-1: VOLTAGE REFERENCE BLOCK DIAGRAM

| R/W-0/0         | R/W-0/0                                               | R/W-0/0                                                  | R/W-0/0                         | U-0             | R/W-0/0          | R/W-0/0             | R/W-0/0      |

|-----------------|-------------------------------------------------------|----------------------------------------------------------|---------------------------------|-----------------|------------------|---------------------|--------------|

| ADFM            |                                                       | ADCS<2:0>                                                |                                 | _               | ADNREF           | ADPRE               | EF<1:0>      |

| bit 7           |                                                       |                                                          |                                 |                 |                  |                     | bit C        |

|                 |                                                       |                                                          |                                 |                 |                  |                     |              |

| Legend:         |                                                       |                                                          |                                 |                 |                  |                     |              |

| R = Readabl     | le bit                                                | W = Writable                                             | bit                             | U = Unimpler    | mented bit, read | l as '0'            |              |

| u = Bit is und  | changed                                               | x = Bit is unkr                                          | nown                            | -n/n = Value a  | at POR and BO    | R/Value at all      | other Resets |

| '1' = Bit is se | et                                                    | '0' = Bit is clea                                        | ared                            |                 |                  |                     |              |

| bit 7           | 1 = Right ju:<br>loaded.                              | Result Format S<br>stified. Six Most<br>ified. Six Least | Significant bi                  |                 |                  |                     |              |

| bit 6-4         | 111 = FRC (<br>110 = Fosc<br>101 = Fosc<br>100 = Fosc | /16<br>/4<br>/clock supplied f<br>/32<br>/8              | rom a dedicat                   | ed RC oscillato |                  |                     |              |

| bit 3           | Unimpleme                                             | nted: Read as '                                          | 0'                              |                 |                  |                     |              |

| bit 2           | 1 = VREF- i                                           | /D Negative Vol<br>s connected to<br>s connected to      | external VREF                   |                 | n bit            |                     |              |

| bit 1-0         | 11 = VREF+                                            |                                                          | internal Fixed<br>external VREF | Voltage Refere  |                  | dule <sup>(1)</sup> |              |

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 30.0 "Electrical Specifications**" for details.

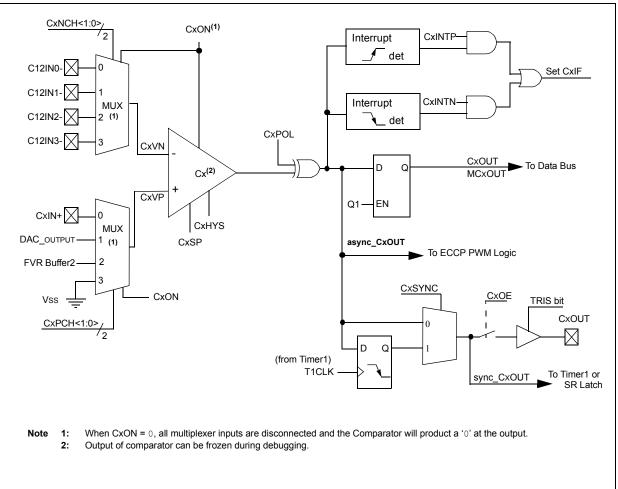

#### FIGURE 18-2: COMPARATOR MODULE SIMPLIFIED BLOCK DIAGRAM

| Name    | Bit 7                                        | Bit 6                                                       | Bit 5        | Bit 4                     | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------------------------------------------|-------------------------------------------------------------|--------------|---------------------------|--------|--------|--------|--------|---------------------|

| CCP2CON | P2M<                                         | P2M<1:0> DC2B<1:0> CCP2M<3:0>                               |              |                           |        |        |        | 214    |                     |

| INTCON  | GIE                                          | IE PEIE TMR0IE INTE IOCIE TMR0IF INTF IOCIF                 |              |                           |        |        | IOCIF  | 82     |                     |

| PIE1    | TMR1GIE                                      | ADIE                                                        | RCIE         | TXIE                      | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 83                  |

| PIE3    | —                                            | CCP5IE                                                      | CCP4IE       | CCP3IE                    | TMR6IE | —      | TMR4IE | —      | 85                  |

| PIR1    | TMR1GIF                                      | ADIF                                                        | RCIF         | TXIF                      | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 86                  |

| PIR3    | _                                            | CCP5IF                                                      | CCP4IF       | CCP3IF                    | TMR6IF | —      | TMR4IF | —      | 88                  |

| PR2     | Timer2 Mod                                   | dule Period                                                 | Register     |                           |        |        |        |        | 187*                |

| PR4     | Timer4 Mod                                   | Timer4 Module Period Register                               |              |                           |        |        |        |        | 187*                |

| PR6     | Timer6 Module Period Register                |                                                             |              |                           |        |        | 187*   |        |                     |

| T2CON   | —                                            |                                                             | T2OUT        | PS<3:0>                   |        | TMR2ON | T2CKP  | S<1:0> | 189                 |

| T4CON   | _                                            |                                                             | T4OUT        | PS<3:0>                   |        | TMR4ON | T4CKP  | S<1:0> | 189                 |

| T6CON   | _                                            |                                                             |              |                           |        |        |        | 189    |                     |

| TMR2    | Holding Register for the 8-bit TMR2 Register |                                                             |              |                           |        |        | 187*   |        |                     |

| TMR4    | Holding Re                                   | Holding Register for the 8-bit TMR4 Register <sup>(1)</sup> |              |                           |        |        |        |        | 187*                |

| TMR6    | Holding Re                                   | gister for the                                              | e 8-bit TMR6 | 6 Register <sup>(1)</sup> |        |        |        |        | 187*                |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

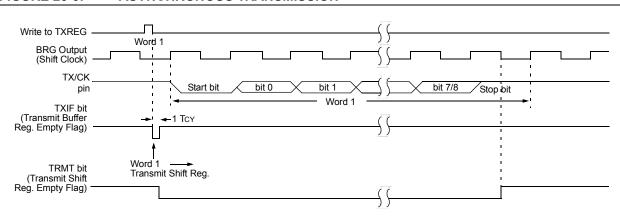

#### 25.1.1.5 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 25.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 25.1.2.7** "Address **Detection**" for more information on the address mode.

- 25.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 25-3: ASYNCHRONOUS TRANSMISSION

| IADLE 21-3. |               |               |               |               |               |               |              |              |                     |

|-------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|---------------------|

| Name        | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1        | Bit 0        | Register<br>on Page |

| INTCON      | GIE           | PEIE          | TMR0IE        | INTE          | IOCIE         | TMR0IF        | INTF         | IOCIF        | 82                  |

| LCDCON      | LCDEN         | SLPEN         | WERR          | —             | CS<           | <1:0>         | LMUX         | (<1:0>       | 315                 |

| LCDCST      | _             | —             | _             | —             | _             | I             | _CDCST<2:0   | >            | 318                 |

| LCDDATA0    | SEG7<br>COM0  | SEG6<br>COM0  | SEG5<br>COM0  | SEG4<br>COM0  | SEG3<br>COM0  | SEG2<br>COM0  | SEG1<br>COM0 | SEG0<br>COM0 | 319                 |

| LCDDATA1    | SEG15<br>COM0 | SEG14<br>COM0 | SEG13<br>COM0 | SEG12<br>COM0 | SEG11<br>COM0 | SEG10<br>COM0 | SEG9<br>COM0 | SEG8<br>COM0 | 319                 |

| LCDDATA3    | SEG7<br>COM1  | SEG6<br>COM1  | SEG5<br>COM1  | SEG4<br>COM1  | SEG3<br>COM1  | SEG2<br>COM1  | SEG1<br>COM1 | SEG0<br>COM1 | 319                 |

| LCDDATA4    | SEG15<br>COM1 | SEG14<br>COM1 | SEG13<br>COM1 | SEG12<br>COM1 | SEG11<br>COM1 | SEG10<br>COM1 | SEG9<br>COM1 | SEG8<br>COM1 | 319                 |

| LCDDATA6    | SEG7<br>COM2  | SEG6<br>COM2  | SEG5<br>COM2  | SEG4<br>COM2  | SEG3<br>COM2  | SEG2<br>COM2  | SEG1<br>COM2 | SEG0<br>COM2 | 319                 |

| LCDDATA7    | SEG15<br>COM2 | SEG14<br>COM2 | SEG13<br>COM2 | SEG12<br>COM2 | SEG11<br>COM2 | SEG10<br>COM2 | SEG9<br>COM2 | SEG8<br>COM2 | 319                 |

| LCDDATA9    | SEG7<br>COM3  | SEG6<br>COM3  | SEG5<br>COM3  | SEG4<br>COM3  | SEG3<br>COM3  | SEG2<br>COM3  | SEG1<br>COM3 | SEG0<br>COM3 | 319                 |

| LCDDATA10   | SEG15<br>COM3 | SEG14<br>COM3 | SEG13<br>COM3 | SEG12<br>COM3 | SEG11<br>COM3 | SEG10<br>COM3 | SEG9<br>COM3 | SEG8<br>COM3 | 319                 |

| LCDPS       | WFT           | BIASMD        | LCDA          | WA            |               | LP<           | <3:0>        |              | 316                 |

| LCDREF      | LCDIRE        | LCDIRS        | LCDIRI        | —             | VLCD3PE       | VLCD2PE       | VLCD1PE      | —            | 317                 |

| LCDRL       | LRLA          | P<1:0>        | LRLBF         | P<1:0>        | _             |               | LRLAT<2:0>   |              | 326                 |

| LCDSE0      |               |               |               | SE            | <7:0>         |               |              |              | 319                 |

| LCDSE1      |               |               |               | SE            | <15:8>        |               |              |              | 319                 |

| PIE2        | OSFIE         | C2IE          | C1IE          | EEIE          | BCLIE         | LCDIE         | —            | CCP2IE       | 84                  |

| PIR2        | OSFIF         | C2IF          | C1IF          | EEIF          | BCLIF         | LCDIF         | _            | CCP2IF       | 87                  |

| T1CON       | TMR1C         | S<1:0>        | T1CKP         | S<1:0>        | T1OSCEN       | T1SYNC        | —            | TMR10N       | 183                 |

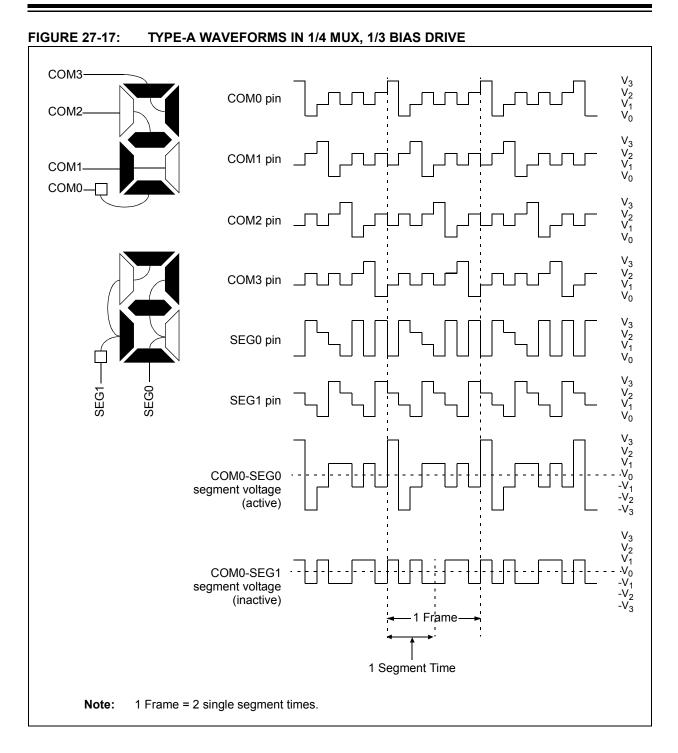

### TABLE 27-9: SUMMARY OF REGISTERS ASSOCIATED WITH LCD OPERATION

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the LCD module.

| TABLE 29-3: | PIC16(L)F1933 INSTRUCTION SET (CONTINUED) |

|-------------|-------------------------------------------|

|-------------|-------------------------------------------|

| Mnemonic,<br>Operands |      | Description C                                 |        |     | 14-Bit  | Opcode | )    | Status   | Notes |

|-----------------------|------|-----------------------------------------------|--------|-----|---------|--------|------|----------|-------|

|                       |      |                                               |        | MSb |         |        | LSb  | Affected | Notes |

|                       |      | CONTROL OPERA                                 | TIONS  |     |         |        |      |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11  | 001k    | kkkk   | kkkk |          |       |

| BRW                   | -    | Relative Branch with W                        | 2      | 00  | 0000    | 0000   | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10  | 0 k k k | kkkk   | kkkk |          |       |

| CALLW                 | -    | Call Subroutine with W                        | 2      | 00  | 0000    | 0000   | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10  | 1kkk    | kkkk   | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00  | 0000    | 0000   | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2      | 11  | 0100    | kkkk   | kkkk |          |       |

| RETURN                | -    | Return from Subroutine                        | 2      | 00  | 0000    | 0000   | 1000 |          |       |

|                       |      | INHERENT OPERA                                | TIONS  |     |         |        |      | •        |       |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1      | 00  | 0000    | 0110   | 0100 | TO, PD   |       |

| NOP                   | -    | No Operation                                  | 1      | 00  | 0000    | 0000   | 0000 |          |       |

| OPTION                | -    | Load OPTION_REG register with W               | 1      | 00  | 0000    | 0110   | 0010 |          |       |

| RESET                 | -    | Software device Reset                         | 1      | 00  | 0000    | 0000   | 0001 |          |       |

| SLEEP                 | -    | Go into Standby mode                          | 1      | 00  | 0000    | 0110   | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1      | 00  | 0000    | 0110   | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED |     |         |        |      | •        |       |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1      | 11  | 0001    | 0nkk   | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000    | 0001   | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |        |     |         |        |      |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111    | Onkk   | kkkk | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000    | 0001   | 1nmm |          | 2, 3  |

|                       |      | modifier, mm                                  |        |     |         |        |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111    | 1nkk   | kkkk |          | 2     |

Note 1:If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

$W<3:0> \le k<3:0>$

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                              |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                       |  |  |  |  |

| SUBLW            | Subtract W                                                                                                                              | / from literal  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| Syntax:          | [label] Sl                                                                                                                              | JBLW k          |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                     |                 |  |  |  |

| Operation:       | $k \operatorname{-} (W) \operatorname{\rightarrow} (W$                                                                                  | /)              |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                |                 |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the eight-bit<br>literal 'k'. The result is placed in the W<br>register. |                 |  |  |  |

|                  | <b>C =</b> 0                                                                                                                            | W > k           |  |  |  |

|                  | <b>C =</b> 1                                                                                                                            | $W \le k$       |  |  |  |

|                  | DC = 0                                                                                                                                  | W<3:0> > k<3:0> |  |  |  |

**DC =** 1

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is cleared. Time-out Status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| SUBWF            | Subtract W from f                  |                              |  |  |  |  |

|------------------|------------------------------------|------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SU                | BWF f,d                      |  |  |  |  |

| oporariaor       | $0 \le f \le 127$<br>$d \in [0,1]$ |                              |  |  |  |  |

| Operation:       | $(f) - (W) \to (d$                 | estination)                  |  |  |  |  |

| Status Affected: | C, DC, Z                           |                              |  |  |  |  |

| ·                | register from<br>result is store   | is '1', the result is stored |  |  |  |  |

|                  | <b>C =</b> 0                       | W > f                        |  |  |  |  |

|                  | <b>C =</b> 1                       | $W \leq f$                   |  |  |  |  |

| 0             | VV > 1              |

|---------------|---------------------|

| <b>C =</b> 1  | $W \leq f$          |

| DC = 0        | W<3:0> > f<3:0>     |

| <b>DC =</b> 1 | $W<3:0> \le f<3:0>$ |

|               |                     |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |  |  |  |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |  |  |  |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |

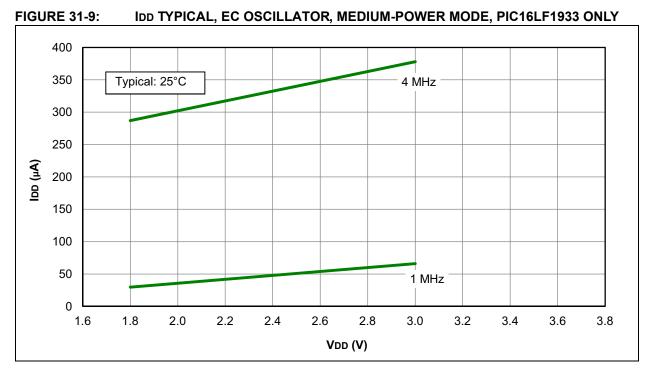

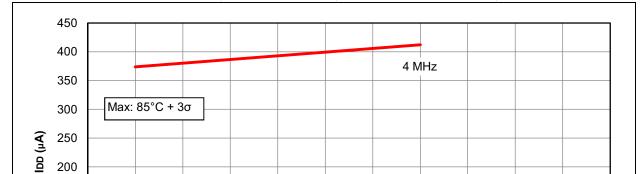

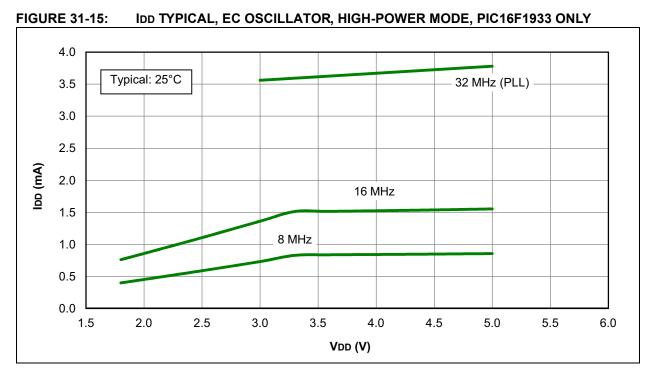

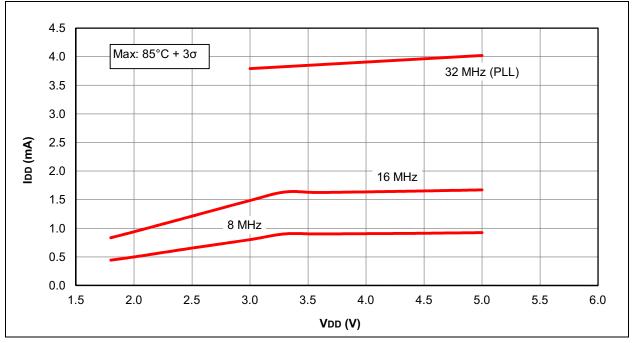

### 30.2 DC Characteristics: Supply Currents (IDD) (Continued)

| PIC16LF           | 1933                                | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |                 |      |       |                              |                                                                               |  |  |

|-------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-------|------------------------------|-------------------------------------------------------------------------------|--|--|

| PIC16F1933        |                                     |                                                                                                                                                                                                                                                                | - F             |      |       |                              | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended |  |  |

| Param Device Min. |                                     |                                                                                                                                                                                                                                                                | Typ† Max. Units |      | Units | Conditions                   |                                                                               |  |  |

| No.               | Characteristics                     |                                                                                                                                                                                                                                                                | IJPI            | max. | Units | VDD                          | Note                                                                          |  |  |

|                   | Supply Current (IDD) <sup>(1,</sup> | 2)                                                                                                                                                                                                                                                             |                 |      |       |                              |                                                                               |  |  |

| D013              |                                     | —                                                                                                                                                                                                                                                              | 60              | 90   | μA    | 1.8                          | Fosc = 500 kHz                                                                |  |  |

|                   |                                     |                                                                                                                                                                                                                                                                | 85              | 135  | μA    | 3.0                          | EC Oscillator Low-Power mode                                                  |  |  |

| D013              |                                     |                                                                                                                                                                                                                                                                | 60              | 137  | μA    | 1.8                          | Fosc = 500 kHz                                                                |  |  |

|                   |                                     |                                                                                                                                                                                                                                                                | 85              | 194  | μA    | 3.0                          | EC Oscillator Low-Power mode (Note 5)                                         |  |  |

|                   |                                     |                                                                                                                                                                                                                                                                | 95              | 230  | μA    | 5.0                          |                                                                               |  |  |

| D014              |                                     |                                                                                                                                                                                                                                                                | 300             | 340  | μA    | 1.8                          | Fosc = 4 MHz                                                                  |  |  |

|                   |                                     | —                                                                                                                                                                                                                                                              | 400             | 650  | μA    | 3.0                          | EC Oscillator mode<br>Medium-Power mode                                       |  |  |

| D014              |                                     |                                                                                                                                                                                                                                                                | 350             | 375  | μA    | 1.8                          | Fosc = 4 MHz                                                                  |  |  |

|                   |                                     |                                                                                                                                                                                                                                                                | 550             | 700  | μA    | 3.0                          | EC Oscillator mode (Note 5)<br>Medium-Power mode                              |  |  |

|                   |                                     | —                                                                                                                                                                                                                                                              | 600             | 900  | μΑ    | 5.0                          |                                                                               |  |  |

| D015              |                                     | _                                                                                                                                                                                                                                                              | 3.7             | 4.2  | mA    | 3.0                          | Fosc = 32 MHz                                                                 |  |  |

|                   |                                     | —                                                                                                                                                                                                                                                              | 4.2             | 5.2  | mA    | 3.6                          | EC Oscillator High-Power mode                                                 |  |  |

| D015              |                                     | _                                                                                                                                                                                                                                                              | 3.7             | 4.2  | mA    | 3.0                          | Fosc = 32 MHz                                                                 |  |  |

|                   |                                     | —                                                                                                                                                                                                                                                              | 3.9             | 4.7  | mA    | 5.0                          | EC Oscillator High-Power mode (Note 5)                                        |  |  |

| D016              |                                     | —                                                                                                                                                                                                                                                              | 4               | 10   | μA    | 1.8                          | Fosc = 32 kHz                                                                 |  |  |

|                   |                                     | —                                                                                                                                                                                                                                                              | 7               | 13   | μA    | 3.0                          | LFINTOSC mode, 85°C                                                           |  |  |

| D016              |                                     | _                                                                                                                                                                                                                                                              | 27              | 61   | μA    | 1.8                          | Fosc = 32 kHz                                                                 |  |  |

|                   | — 33                                | 33                                                                                                                                                                                                                                                             | 74              | μA   | 3.0   | LFINTOSC mode, 85°C (Note 5) |                                                                               |  |  |

|                   |                                     | —                                                                                                                                                                                                                                                              | 34              | 76   | μA    | 5.0                          |                                                                               |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

- 4: FVR and BOR are disabled.

- 5: 0.1  $\mu$ F capacitor on VCAP.

6: 8 MHz crystal oscillator with 4x PLL enabled.

2.6

2.8

VDD (V)

2.2

2.4

1 MHz

3.0

3.2

3.4

3.6

3.8

FIGURE 31-10: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1933 ONLY

150

100

50

0

1.6

1.8

2.0

FIGURE 31-16: IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC16F1933 ONLY

© 2011-2012 Microchip Technology Inc.