Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

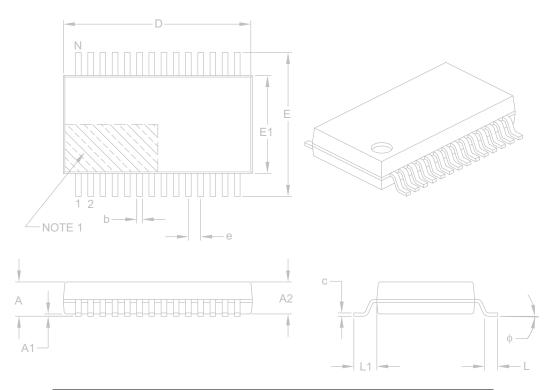

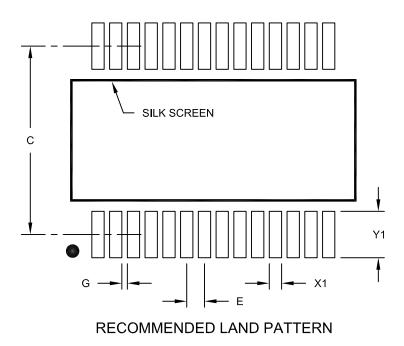

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1933-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

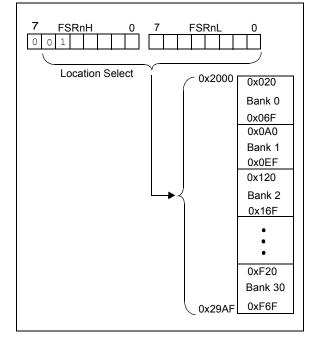

### 3.6.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-10: LINEAR DATA MEMORY MAP

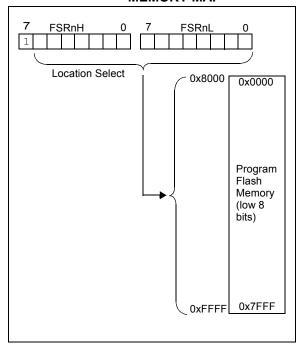

#### 3.6.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower 8 bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-11: PROGRAM FLASH MEMORY MAP

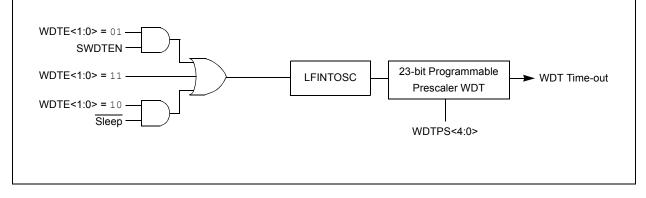

## 10.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

#### FIGURE 10-1: WATCHDOG TIMER BLOCK DIAGRAM

## EXAMPLE 11-2: DATA EEPROM WRITE

|                      | BANKSEL | EEADRL   |       | ;                             |

|----------------------|---------|----------|-------|-------------------------------|

|                      | MOVLW   | DATA_EE  | ADDR  | ;                             |

|                      | MOVWF   | EEADRL   |       | ;Data Memory Address to write |

|                      | MOVLW   | DATA_EE_ | DATA  | ;                             |

|                      | MOVWF   | EEDATL   |       | ;Data Memory Value to write   |

|                      | BCF     | EECON1,  | CFGS  | ;Deselect Configuration space |

|                      | BCF     | EECON1,  | EEPGD | ;Point to DATA memory         |

|                      | BSF     | EECON1,  | WREN  | ;Enable writes                |

|                      |         |          |       |                               |

|                      | BCF     | INTCON,  | GIE   | ;Disable INTs.                |

|                      | MOVLW   | 55h      |       | ;                             |

| ce ed                | MOVWF   | EECON2   |       | ;Write 55h                    |

| luire                | MOVLW   | 0AAh     |       | ;                             |

| Required<br>Sequence | MOVWF   | EECON2   |       | ;Write AAh                    |

| ш о                  | BSF     | EECON1,  | WR    | ;Set WR bit to begin write    |

|                      | BSF     | INTCON,  | GIE   | ;Enable Interrupts            |

|                      | BCF     | EECON1,  | WREN  | ;Disable writes               |

|                      | BTFSC   | EECON1,  | WR    | ;Wait for write to complete   |

|                      | GOTO    | \$-2     |       | ;Done                         |

|                      |         |          |       |                               |

|                              | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash ADDR                   | I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I |

| Flash Data                   | INSTR (PC) INSTR (PC + 1) EEDATH,EEDATL INSTR (PC + 3) INSTR (PC + 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                              | I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                     |

| RD bit                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EEDATH<br>EEDATL<br>Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

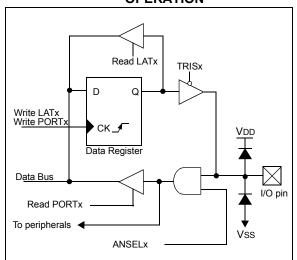

## 12.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- · LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

## TABLE 12-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | PORTA | PORTB | PORTC | PORTE |

|---------------|-------|-------|-------|-------|

| PIC16(L)F1933 | •     | •     | ٠     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

#### EXAMPLE 12-1: INITIALIZING PORTA

| ; | This | code | example | illustrates |  |

|---|------|------|---------|-------------|--|

|---|------|------|---------|-------------|--|

- ; initializing the PORTA register. The

- ; other ports are initialized in the same

- ; manner.

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

## 13.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER**

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------|---------|---------|---------|---------|---------|---------|---------|

| IOCBP7   | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  |

| bit 7    |         |         |         |         |         |         | bit 0   |

|          |         |         |         |         |         |         |         |

| l ogond: |         |         |         |         |         |         |         |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCBP<7:0>:** Interrupt-on-Change Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCBN<7:0>:** Interrupt-on-Change Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0 **IOCBF<7:0>:** Interrupt-on-Change Flag bits

- 1 = An enabled change was detected on the associated pin.

Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

#### 18.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 30.0 "Electrical Specifications"** for more information.

## 18.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 21.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 18.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from either comparator, C1 or C2, can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 18-2) and the Timer1 Block Diagram (Figure 22-1) for more information.

### 18.5 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a Falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

## 18.6 Comparator Positive Input Selection

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC\_output

- DAC FVR Buffer2

- Vss (Ground)

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

# 18.7 Comparator Negative Input Selection

The CxNCH<1:0> bits of the CMxCON0 register direct one of four analog pins to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog     |

|-------|--------------------------------------------|

|       | input, the appropriate bits must be set in |

|       | the ANSEL register and the correspond-     |

|       | ing TRIS bits must also be set to disable  |

|       | the output drivers.                        |

## 18.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference specifications in Section 30.0 "Electrical Specifications" for more details.

## 18.9 Interaction with ECCP Logic

The C1 and C2 comparators can be used as general purpose comparators. Their outputs can be brought out to the C1OUT and C2OUT pins. When the ECCP auto-shutdown is active it can use one or both comparator signals. If auto-restart is also enabled, the comparators can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

Note: When the comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

### 18.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

## 19.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- · Programmable input selection

- SR latch output is available externally

- Separate Q and  $\overline{Q}$  outputs

- · Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

## 19.1 Latch Operation

The latch is a Set-Reset Latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be set or reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync\_C2OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either comparator can be synchronized to the Timer1 clock source. See Section 18.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source is available that can periodically set or reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR latch, respectively.

### 19.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to an I/O pin at the same time. The  $\overline{Q}$  latch output pin function can be moved to an alternate pin using the SRNQSEL bit of the APFCON register.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

## 19.3 Effects of a Reset

Upon any device Reset, the SR latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

# PIC16(L)F1933

| R/W-0/u          | R/W-0/u                                                                                                                                                                                                                                                                                        | R/W-0/u                                                                                                                                                                                                                                                                                             | R/W-0/u                            | R/W/HC-0/u                          | R-x/x            | R/W-0/u          | R/W-0/u      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------|------------------|------------------|--------------|--|--|

| TMR1GE           | T1GPOL                                                                                                                                                                                                                                                                                         | T1GTM                                                                                                                                                                                                                                                                                               | T1GSPM                             | T1GGO/<br>DONE                      | T1GVAL           | T1GS             | S<1:0>       |  |  |

| bit 7            |                                                                                                                                                                                                                                                                                                | ·                                                                                                                                                                                                                                                                                                   |                                    |                                     |                  |                  | bit          |  |  |

| Legend:          |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                     |                                    |                                     |                  |                  |              |  |  |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                          | W = Writable                                                                                                                                                                                                                                                                                        | bit                                | U = Unimplem                        | nented bit, read | d as '0'         |              |  |  |

| u = Bit is unc   | hanged                                                                                                                                                                                                                                                                                         | x = Bit is unki                                                                                                                                                                                                                                                                                     | nown                               | -n/n = Value a                      | t POR and BO     | R/Value at all o | other Resets |  |  |

| '1' = Bit is set | t                                                                                                                                                                                                                                                                                              | '0' = Bit is cle                                                                                                                                                                                                                                                                                    | ared                               | HC = Bit is cle                     | eared by hardw   | are              |              |  |  |

| bit 7            | If TMR1ON =<br>This bit is ign<br>If TMR1ON =<br>1 = Timer1 c                                                                                                                                                                                                                                  | iored<br><u>= 1</u> :<br>counting is cont                                                                                                                                                                                                                                                           | rolled by the T                    | imer1 gate func<br>ate function     | tion             |                  |              |  |  |

| bit 6            | <b>T1GPOL:</b> Tir<br>1 = Timer1 g                                                                                                                                                                                                                                                             | <ul> <li>0 = Timer1 counts regardless of Timer1 gate function</li> <li>T1GPOL: Timer1 Gate Polarity bit</li> <li>1 = Timer1 gate is active-high (Timer1 counts when gate is high)</li> <li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li> </ul>                                |                                    |                                     |                  |                  |              |  |  |

| bit 5            | 1 = Timer1 (<br>0 = Timer1 (                                                                                                                                                                                                                                                                   | er1 Gate Toggle<br>Gate Toggle mo<br>Gate Toggle mo<br>flip-flop toggles                                                                                                                                                                                                                            | de is enabled<br>de is disabled    | and toggle flip-<br>g edge.         | flop is cleared  |                  |              |  |  |

| bit 4            | 1 = Timer1 C                                                                                                                                                                                                                                                                                   | mer1 Gate Sing<br>Gate Single-Pul<br>Gate Single-Pul                                                                                                                                                                                                                                                | se mode is en                      | abled and is co                     | ntrolling Timer  | 1 gate           |              |  |  |

| bit 3            | <b>T1GGO/DON</b><br>1 = Timer1 g                                                                                                                                                                                                                                                               | <b>IE:</b> Timer1 Gat<br>gate single-puls                                                                                                                                                                                                                                                           | e Single-Pulse<br>e acquisition is | Acquisition Sta<br>s ready, waiting | for an edge      | started          |              |  |  |

| bit 2            | T1GVAL: Tin<br>Indicates the                                                                                                                                                                                                                                                                   | <ul> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> <li>T1GVAL: Timer1 Gate Current State bit</li> <li>Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.</li> <li>Unaffected by Timer1 Gate Enable (TMR1GE)</li> </ul> |                                    |                                     |                  |                  |              |  |  |

| bit 1-0          | Unaffected by Timer1 Gate Enable (TMR1GE).<br><b>T1GSS&lt;1:0&gt;:</b> Timer1 Gate Source Select bits<br>11 = Comparator 2 optionally synchronized output (sync_C2OUT)<br>10 = Comparator 1 optionally synchronized output (sync_C1OUT)<br>01 = Timer0 overflow output<br>00 = Timer1 gate pin |                                                                                                                                                                                                                                                                                                     |                                    |                                     |                  |                  |              |  |  |

### REGISTER 21-2: T1GCON: TIMER1 GATE CONTROL REGISTER

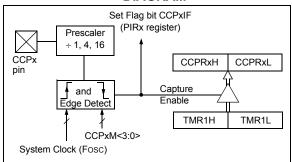

### 23.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, ECCP3, CCP4 and CCP5.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 23-1 shows a simplified diagram of the Capture operation.

#### 23.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON register. Refer to **Section 12.1 "Alternate Pin Function**" for more details.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 23-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 23.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 23.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

#### 23.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 23-1 demonstrates the code to perform this function.

#### EXAMPLE 23-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point<br>;to CCPxCON |

|---------|-------------|----------------------------------------|

| CLRF    | CCPxCON     | ;Turn CCP module off                   |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with                   |

|         |             | ;the new prescaler                     |

|         |             | ;move value and CCP ON                 |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this                |

|         |             | ;value                                 |

|         |             |                                        |

#### 23.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state. Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

| R/W-0/0                 | R/W-0/0                                                                                | R/W-0/0                                                                                | R/W-0/0      | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------|----------------|------------------|------------------|--------------|--|--|--|--|

| C4TSEL<1:0> C3TSEL<1:0> |                                                                                        |                                                                                        | C2TSE        | L<1:0>         | C1TSE            | :L<1:0>          |              |  |  |  |  |

| bit 7                   |                                                                                        |                                                                                        |              |                |                  |                  | bit C        |  |  |  |  |

|                         |                                                                                        |                                                                                        |              |                |                  |                  |              |  |  |  |  |

| Legend:                 |                                                                                        |                                                                                        |              |                |                  |                  |              |  |  |  |  |

| R = Readable            | e bit                                                                                  | W = Writable I                                                                         | oit          | U = Unimplen   | nented bit, read | d as '0'         |              |  |  |  |  |

| u = Bit is unc          | hanged                                                                                 | x = Bit is unkn                                                                        | own          | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is set        |                                                                                        | '0' = Bit is clea                                                                      | ared         |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        |                                                                                        |              |                |                  |                  |              |  |  |  |  |

| bit 7-6                 | C4TSEL<1:0                                                                             | >: CCP4 Timer                                                                          | Selection    |                |                  |                  |              |  |  |  |  |

|                         | 11 = Reserve                                                                           | 11 = Reserved                                                                          |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        | 10 = CCP4 is based off Timer6 in PWM mode                                              |              |                |                  |                  |              |  |  |  |  |

|                         | 01 = CCP4 is based off Timer4 in PWM mode<br>00 = CCP4 is based off Timer2 in PWM mode |                                                                                        |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        |                                                                                        |              | ode            |                  |                  |              |  |  |  |  |

| bit 5-4                 | C3TSEL<1:0                                                                             | C3TSEL<1:0>: CCP3 Timer Selection                                                      |              |                |                  |                  |              |  |  |  |  |

|                         | 11 = Reserved                                                                          |                                                                                        |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        | 10 = CCP3 is based off Timer6 in PWM mode                                              |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        | 01 = CCP3 is based off Timer4 in PWM mode<br>00 = CCP3 is based off Timer2 in PWM mode |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        |                                                                                        |              | ode            |                  |                  |              |  |  |  |  |

| bit 3-2                 |                                                                                        | >: CCP2 Timer                                                                          | Selection    |                |                  |                  |              |  |  |  |  |

|                         | 11 = Reserve                                                                           |                                                                                        |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        | 10 = CCP2 is based off Timer6 in PWM mode                                              |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        | 01 = CCP2 is based off Timer4 in PWM mode<br>00 = CCP2 is based off Timer2 in PWM mode |              |                |                  |                  |              |  |  |  |  |

| bit 1-0                 |                                                                                        |                                                                                        |              | oue            |                  |                  |              |  |  |  |  |

| DIT I-U                 |                                                                                        | CCP1 Timer                                                                             | Selection    |                |                  |                  |              |  |  |  |  |

|                         | 11 = Reserve                                                                           | ed<br>s based off Time                                                                 | re in DW/M m | odo            |                  |                  |              |  |  |  |  |

|                         |                                                                                        | s based off Time                                                                       |              |                |                  |                  |              |  |  |  |  |

|                         |                                                                                        | based off Time                                                                         |              |                |                  |                  |              |  |  |  |  |

## REGISTER 23-2: CCPTMRS0: PWM TIMER SELECTION CONTROL REGISTER 0

#### REGISTER 23-3: CCPTMRS1: PWM TIMER SELECTION CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0     | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|-------------|---------|

| —     | —   | —   | —   | —   | _   | C5TSEL<1:0> |         |

| bit 7 |     |     |     |     |     |             | bit 0   |

| Legend:                                        |          |                      |                                                       |  |  |

|------------------------------------------------|----------|----------------------|-------------------------------------------------------|--|--|

| R = Readable                                   | bit      | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |

| u = Bit is unchanged                           |          | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |  |

| '1' = Bit is set                               |          | '0' = Bit is cleared |                                                       |  |  |

|                                                |          |                      |                                                       |  |  |

| bit 7-2                                        | Unimplem | ented: Read as '0'   |                                                       |  |  |

| bit 1-0 C5TSEL<1:0>: CCP5 Timer Selection bits |          |                      |                                                       |  |  |

11 = Reserved

10 = CCP5 is based off Timer6 in PWM mode

01 = CCP5 is based off Timer4 in PWM mode

00 = CCP5 is based off Timer2 in PWM mode

# PIC16(L)F1933

| U-0            | U-0             | U-0                                                                                  | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0        | R/W-1/1      |  |  |  |  |

|----------------|-----------------|--------------------------------------------------------------------------------------|------------------|-----------------|-------------------|----------------|--------------|--|--|--|--|

| —              | _               | —                                                                                    | STRxSYNC         | STRxD           | STRxC             | STRxB          | STRxA        |  |  |  |  |

| bit 7          |                 |                                                                                      |                  |                 |                   |                | bit (        |  |  |  |  |

|                |                 |                                                                                      |                  |                 |                   |                |              |  |  |  |  |

| Legend:        |                 |                                                                                      |                  |                 |                   |                |              |  |  |  |  |

| R = Readal     |                 | W = Writable                                                                         |                  | •               | mented bit, read  |                |              |  |  |  |  |

| u = Bit is ur  | 0               | x = Bit is unk                                                                       | nown             | -n/n = Value a  | at POR and BC     | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is s | et              | '0' = Bit is cle                                                                     | eared            |                 |                   |                |              |  |  |  |  |

| bit 7-5        | Unimplemer      | nted: Read as                                                                        | <b>'</b> 0'      |                 |                   |                |              |  |  |  |  |

| bit 4          | STRxSYNC:       | Steering Sync                                                                        | ; bit            |                 |                   |                |              |  |  |  |  |

|                | 1 = Output st   | 1 = Output steering update occurs on next PWM period                                 |                  |                 |                   |                |              |  |  |  |  |

|                | 0 = Output st   | 0 = Output steering update occurs at the beginning of the instruction cycle boundary |                  |                 |                   |                |              |  |  |  |  |

| bit 3          | STRxD: Stee     | STRxD: Steering Enable bit D                                                         |                  |                 |                   |                |              |  |  |  |  |

|                | 1 = PxD pin ł   | 1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0>               |                  |                 |                   |                |              |  |  |  |  |

|                | 0 = PxD pin i   | 0 = PxD pin is assigned to port pin                                                  |                  |                 |                   |                |              |  |  |  |  |

| bit 2          |                 | ering Enable bi                                                                      |                  |                 |                   |                |              |  |  |  |  |

|                | 1 = PxC pin I   | 1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0>               |                  |                 |                   |                |              |  |  |  |  |

|                | 0 = PxC pin i   | 0 = PxC pin is assigned to port pin                                                  |                  |                 |                   |                |              |  |  |  |  |

| bit 1          |                 | RxB: Steering Enable bit B                                                           |                  |                 |                   |                |              |  |  |  |  |

|                |                 | 1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0>               |                  |                 |                   |                |              |  |  |  |  |

|                | 0 = PxB pin i   | 0 = PxB pin is assigned to port pin                                                  |                  |                 |                   |                |              |  |  |  |  |

| bit 0          |                 | ering Enable bi                                                                      |                  |                 |                   |                |              |  |  |  |  |

|                | •               |                                                                                      | waveform with p  | olarity control | from CCPxM<       | 1:0>           |              |  |  |  |  |

|                | 0 = PxA pin i   | s assigned to                                                                        | port pin         |                 |                   |                |              |  |  |  |  |

| Note 1:        | The PWM Steerin | a mode is ava                                                                        | ilable only when | the CCPxCO      | N register hits ( | CCPxM<3·2> =   | = 11 and     |  |  |  |  |

## **REGISTER 23-6: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

Note 1: The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

#### REGISTER 24-5: SSPMSK: SSP MASK REGISTER

| R/W-1/1                                 | R/W-1/1                                                          | R/W-1/1                                                                                                                                                             | R/W-1/1 | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |

|-----------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|------------------|------------------|--------------|--|--|

|                                         |                                                                  |                                                                                                                                                                     | MSK     | <7:0>          |                  |                  |              |  |  |

| bit 7                                   |                                                                  |                                                                                                                                                                     |         |                |                  |                  | bit 0        |  |  |

|                                         |                                                                  |                                                                                                                                                                     |         |                |                  |                  |              |  |  |

| Legend:                                 |                                                                  |                                                                                                                                                                     |         |                |                  |                  |              |  |  |

| R = Readable                            | e bit                                                            | W = Writable                                                                                                                                                        | bit     | U = Unimpler   | nented bit, read | l as '0'         |              |  |  |

| u = Bit is unchanged x = Bit is unknown |                                                                  |                                                                                                                                                                     | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is set                        |                                                                  | '0' = Bit is cle                                                                                                                                                    | ared    |                |                  |                  |              |  |  |

|                                         |                                                                  |                                                                                                                                                                     |         |                |                  |                  |              |  |  |

| bit 7-1                                 | MSK<7:1>:                                                        |                                                                                                                                                                     |         |                |                  |                  |              |  |  |

|                                         |                                                                  | eived address b<br>eived address b                                                                                                                                  |         |                |                  | C address mat    | tch          |  |  |

| bit 0                                   | MSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address |                                                                                                                                                                     |         |                |                  |                  |              |  |  |

|                                         |                                                                  | ode, 10-bit addr                                                                                                                                                    |         |                |                  |                  |              |  |  |

|                                         |                                                                  | 1 = The received address bit 0 is compared to SSPADD<0> to detect $I^2C$ address match<br>0 = The received address bit 0 is not used to detect $I^2C$ address match |         |                |                  |                  |              |  |  |

|                                         | •                                                                | ode 7-bit address b                                                                                                                                                 |         |                | address match    |                  |              |  |  |

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

'0' = Bit is cleared

## REGISTER 24-6: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0                                                                                      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0      |

|----------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|--------------|

|                                                                                              |         |         | ADD     | <7:0>   |         |         |              |

| bit 7                                                                                        |         |         |         |         |         |         | bit 0        |

|                                                                                              |         |         |         |         |         |         |              |

| Legend:                                                                                      |         |         |         |         |         |         |              |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                         |         |         |         |         |         |         |              |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset |         |         |         |         |         |         | other Resets |

| Master | mode: |  |

|--------|-------|--|

1' = Bit is set

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCL pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 Not used: Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- Not used: Unused in this mode. Bit state is a "don't care". bit 0

#### <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

| bit 7-1 ADD<7:1>: 7-bit address |

|---------------------------------|

|---------------------------------|

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### REGISTER 27-5: LCDSEn: LCD SEGMENT ENABLE REGISTERS

| R/W-0/0          | R/W-0/0                                 | R/W-0/0           | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------|-----------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| SEn              | SEn                                     | SEn               | SEn                                                   | SEn                                | SEn     | SEn     | SEn     |  |

| bit 7            |                                         |                   |                                                       |                                    |         |         | bit 0   |  |

|                  |                                         |                   |                                                       |                                    |         |         |         |  |

| Legend:          |                                         |                   |                                                       |                                    |         |         |         |  |

| R = Readable     | bit                                     | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

bit 7-0 SEn: Segment Enable bits 1 = Segment function of the pin is enabled 0 = I/O function of the pin is enabled

#### REGISTER 27-6: LCDDATAn: LCD DATA REGISTERS

| R/W-x/u   |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| SEGx-COMy |

| bit 7     |           |           |           |           |           |           | bit 0     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SEGx-COMy: Pixel On bits

1 = Pixel on (dark)

0 = Pixel off (clear)

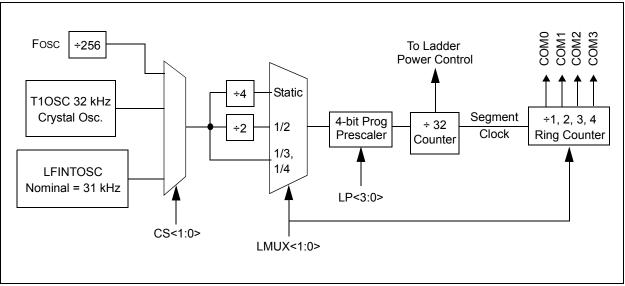

## 27.3 LCD Clock Source Selection

The LCD module has three possible clock sources:

- Fosc/256

- T10SC

- LFINTOSC

The first clock source is the system clock divided by 256 (Fosc/256). This divider ratio is chosen to provide about 1 kHz output when the system clock is 8 MHz. The divider is not programmable. Instead, the LCD prescaler bits LP<3:0> of the LCDPS register are used to set the LCD frame clock rate.

The second clock source is the T1OSC. This also gives about 1 kHz when a 32.768 kHz crystal is used with the Timer1 oscillator. To use the Timer1 oscillator as a clock source, the T1OSCEN bit of the T1CON register should be set.

The third clock source is the 31 kHz LFINTOSC, which provides approximately 1 kHz output.

The second and third clock sources may be used to continue running the LCD while the processor is in Sleep.

Using bits CS<1:0> of the LCDCON register can select any of these clock sources.

#### 27.3.1 LCD PRESCALER

A 4-bit counter is available as a prescaler for the LCD clock. The prescaler is not directly readable or writable; its value is set by the LP<3:0> bits of the LCDPS register, which determine the prescaler assignment and prescale ratio.

The prescale values are selectable from 1:1 through 1:16.

### FIGURE 27-2: LCD CLOCK GENERATION

#### **Instruction Descriptions** 29.2

| ADDFSR           | Add Literal to FSRn                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label]ADDFSR FSRn, k                                                                         |  |  |  |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [0, 1]                                                          |  |  |  |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |  |  |  |

| Status Affected: | None                                                                                          |  |  |  |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |  |  |  |

|                  | FOR is limited to the second OOOOk                                                            |  |  |  |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                                  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |  |  |  |

| Status Affected: | Z                                                                                                                   |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W register. |  |  |  |

| ADDLW            | Add literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                                     |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Description:     | The contents of the W register are<br>added to the eight-bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |