#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1933t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC16(L)F1933 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                    | Function | Input<br>Type | Output<br>Type | Description                                                                                       |

|-------------------------------------------------------------------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------|

| RA6/OSC2/CLKOUT/VCAP <sup>(2)</sup> /                                   | RA6      | TTL           | CMOS           | General purpose I/O.                                                                              |

| SEG1                                                                    | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                             |

|                                                                         | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                    |

|                                                                         | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1933 only).                                         |

|                                                                         | SEG1     | _             | AN             | LCD Analog output.                                                                                |

| RA7/OSC1/CLKIN/SEG2                                                     | RA7      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                                                                         | OSC1     | XTAL          |                | Crystal/Resonator (LP, XT, HS modes).                                                             |

|                                                                         | CLKIN    | CMOS          | _              | External clock input (EC mode).                                                                   |

|                                                                         | SEG2     |               | AN             | LCD Analog output.                                                                                |

| RB0/AN12/CPS0/CCP4/SRI/INT/<br>SEG0                                     | RB0      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                         | AN12     | AN            | —              | A/D Channel input.                                                                                |

|                                                                         | CPS0     | AN            | —              | Capacitive sensing input.                                                                         |

|                                                                         | CCP4     | ST            | CMOS           | Capture/Compare/PWM.                                                                              |

|                                                                         | SRI      | _             | ST             | SR latch input.                                                                                   |

|                                                                         | INT      | ST            |                | External interrupt.                                                                               |

|                                                                         | SEG0     |               | AN             | LCD analog output.                                                                                |

| RB1/AN10/C12IN3-/CPS1/P1C/<br>VLCD1                                     | RB1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                         | AN10     | AN            | _              | A/D Channel input.                                                                                |

|                                                                         | C12IN3-  | AN            | _              | Comparator negative input.                                                                        |

|                                                                         | CPS1     | AN            | _              | Capacitive sensing input.                                                                         |

|                                                                         | P1C      | _             | CMOS           | PWM output.                                                                                       |

|                                                                         | VLCD1    | AN            | _              | LCD analog input.                                                                                 |

| RB2/AN8/CPS2/P1B/VLCD2                                                  | RB2      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                         | AN8      | AN            | _              | A/D Channel input.                                                                                |

|                                                                         | CPS2     | AN            | _              | Capacitive sensing input.                                                                         |

|                                                                         | P1B      | _             | CMOS           | PWM output.                                                                                       |

|                                                                         | VLCD2    | AN            | _              | LCD analog input.                                                                                 |

| RB3/AN9/C12IN2-/CPS3/<br>CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup> /VLCD3 | RB3      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                         | AN9      | AN            | _              | A/D Channel input.                                                                                |

|                                                                         | C12IN2-  | AN            |                | Comparator negative input.                                                                        |

|                                                                         | CPS3     | AN            | _              | Capacitive sensing input.                                                                         |

|                                                                         | CCP2     | ST            | CMOS           | Capture/Compare/PWM.                                                                              |

|                                                                         | P2A      | _             | CMOS           | PWM output.                                                                                       |

|                                                                         | VLCD3    | AN            | _              | LCD analog input.                                                                                 |

| RB4/AN11/CPS4/P1D/COM0                                                  | RB4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                         | AN11     | AN            | —              | A/D Channel input.                                                                                |

|                                                                         | CPS4     | AN            | _              | Capacitive sensing input.                                                                         |

|                                                                         | P1D      | _             | CMOS           | PWM output.                                                                                       |

|                                                                         | COM0     |               | AN             | LCD Analog output.                                                                                |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal

levels

Note 1: Pin function is selectable via the APFCON register.

2: PIC16F1933 devices only.

TABLE 3-7:PIC16(L)F1933 MEMORY MAP,<br/>BANK 15

|               | Bank 15       |                            |

|---------------|---------------|----------------------------|

| 791h          | LCDCON        |                            |

| 792h          | LCDPS         |                            |

| 793h          | LCDREF        |                            |

| 794h          | LCDCST        |                            |

| 795h          | LCDRL         |                            |

| 796h          | _             |                            |

| 797h          | _             |                            |

| 798h          | LCDSE0        |                            |

| 799h          | LCDSE1        |                            |

| 79Ah          | _             |                            |

| 79Ah<br>79Bh  | _             |                            |

| 79Dh          |               |                            |

| 79Ch          |               |                            |

| 79Dh<br>79Eh  |               |                            |

|               |               |                            |

| 79Fh<br>7A0h  | LCDDATA0      |                            |

| 7A011<br>7A1h | LCDDATA0      |                            |

| 7A2h          | _             |                            |

| 7A3h          | LCDDATA3      |                            |

| 7A4h          | LCDDATA4      |                            |

| 7A5h          | —             |                            |

| 7A6h          | LCDDATA6      |                            |

| 7A7h          | LCDDATA7      |                            |

| 7A8h<br>7A9h  | LCDDATA9      |                            |

| 7A91<br>7AAh  | LCDDATA10     |                            |

| 7ABh          | _             |                            |

| 7ACh          | _             |                            |

| 7ADh          | _             |                            |

| 7AEh          | _             |                            |

| 7AFh          | _             |                            |

| 7B0h          |               |                            |

| 7B01<br>7B1h  |               |                            |

| 7B11          |               |                            |

| 7B2H<br>7B3h  | _             |                            |

| 7B3fi<br>7B4h | _             |                            |

|               | _             |                            |

| 7B5h<br>7B6h  |               |                            |

| 7B011<br>7B7h |               |                            |

| 7B7h<br>7B8h  |               |                            |

| 7 0011        |               |                            |

|               | Unimplemented |                            |

|               | Read as '0'   |                            |

|               |               |                            |

| 7EFh          |               |                            |

| Legend:       |               | ata memory locations, read |

| as            | '0'.          |                            |

|               |               |                            |

|               |               |                            |

# TABLE 3-8:PIC16(L)F1933 MEMORY MAP,<br/>BANK 31

|               | Bank 31                      |                        |

|---------------|------------------------------|------------------------|

| F8Ch          |                              |                        |

|               | Unimplemented<br>Read as '0' |                        |

| FE3h          |                              |                        |

| FE4h          | STATUS_SHAD                  |                        |

| FE5h          | WREG_SHAD                    |                        |

| FE6h          | BSR_SHAD                     |                        |

| FE7h          | PCLATH_SHAD                  |                        |

| FE8h          | FSR0L_SHAD                   |                        |

| FE9h          | FSR0H_SHAD                   |                        |

| FEAh          | FSR1L_SHAD                   |                        |

| FEBh          | FSR1H_SHAD                   |                        |

| FECh          | —                            |                        |

| FEDh          | STKPTR                       |                        |

| FEEh          | TOSL                         |                        |

| FEFh          | TOSH                         |                        |

| Legend:<br>as | = Unimplemented data         | memory locations, read |

# 3.3.5 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device        | Bank(s) | Page No. |

|---------------|---------|----------|

|               | 0       | 25       |

|               | 1       | 26       |

|               | 2       | 27       |

|               | 3       | 28       |

|               | 4       | 29       |

|               | 5       | 30       |

| PIC16(L)F1933 | 6       | 31       |

|               | 7       | 32       |

|               | 8       | 33       |

|               | 9-14    | 34       |

|               | 15      | 35       |

|               | 16-30   | 36       |

|               | 31      | 37       |

| Address                | Name   | Bit 7                       | Bit 6                        | Bit 5          | Bit 4           | Bit 3         | Bit 2        | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|-----------------------------|------------------------------|----------------|-----------------|---------------|--------------|-----------|-----------|----------------------|---------------------------------|

| Bank 3                 |        |                             |                              |                |                 |               |              | •         | •         |                      |                                 |

| 180h <sup>(2)</sup>    | INDF0  |                             | this location ical register) | uses contents  | s of FSR0H/F    | SR0L to addre | ess data mei | mory      |           | XXXX XXXX            | XXXX XXXX                       |

| 181h <sup>(2)</sup>    | INDF1  |                             | this location ical register) | uses contents  | s of FSR1H/F    | SR1L to addre | ess data mei | mory      |           | XXXX XXXX            | XXXX XXXX                       |

| 182h <sup>(2)</sup>    | PCL    | Program C                   | ounter (PC) L                | east Significa | nt Byte         |               |              |           |           | 0000 0000            | 0000 0000                       |

| 183h <sup>(2)</sup>    | STATUS | _                           | _                            | _              | TO              | PD            | Z            | DC        | С         | 1 1000               | q quuu                          |

| 184h <sup>(2)</sup>    | FSR0L  | Indirect Dat                | ta Memory Ad                 | dress 0 Low    | Pointer         | •             |              | •         | •         | 0000 0000            | uuuu uuuu                       |

| 185h <sup>(2)</sup>    | FSR0H  | Indirect Dat                | ta Memory Ad                 | dress 0 High   | Pointer         |               |              |           |           | 0000 0000            | 0000 0000                       |

| 186h <sup>(2)</sup>    | FSR1L  | Indirect Dat                | ta Memory Ad                 | dress 1 Low    | Pointer         |               |              |           |           | 0000 0000            | uuuu uuuu                       |

| 187h <sup>(2)</sup>    | FSR1H  | Indirect Dat                | ta Memory Ad                 | dress 1 High   | Pointer         |               |              |           |           | 0000 0000            | 0000 0000                       |

| 188h <sup>(2)</sup>    | BSR    | _                           | _                            | _              |                 |               | BSR<4:0>     |           |           | 0 0000               | 0 0000                          |

| 189h <sup>(2)</sup>    | WREG   | Working Re                  | egister                      |                |                 |               |              |           |           | 0000 0000            | uuuu uuuu                       |

| 18Ah <sup>(1, 2)</sup> | PCLATH | _                           | Write Buffer                 | for the upper  | 7 bits of the F | Program Coun  | iter         |           |           | -000 0000            | -000 0000                       |

| 18Bh <sup>(2)</sup>    | INTCON | GIE                         | PEIE                         | TMR0IE         | INTE            | IOCIE         | TMR0IF       | INTF      | IOCIF     | 0000 0000            | 0000 0000                       |

| 18Ch                   | ANSELA | _                           | _                            | ANSA5          | ANSA4           | ANSA3         | ANSA2        | ANSA1     | ANSA0     | 11 1111              | 11 1111                         |

| 18Dh                   | ANSELB | _                           | _                            | ANSB5          | ANSB4           | ANSB3         | ANSB2        | ANSB1     | ANSB0     | 11 1111              | 11 1111                         |

| 18Eh                   |        | Unimpleme                   | nted                         |                |                 |               |              |           |           | _                    |                                 |

| 18Fh                   | _      | Unimpleme                   | Unimplemented                |                |                 |               |              |           |           | _                    | _                               |

| 190h                   | _      | Unimpleme                   | ented                        |                |                 |               |              |           |           | _                    | _                               |

| 191h                   | EEADRL | EEPROM /                    | Program Me                   | mory Address   | Register Lov    | v Byte        |              |           |           | 0000 0000            | 0000 0000                       |

| 192h                   | EEADRH | (3)                         | EEPROM / F                   | Program Mem    | ory Address I   | Register High | Byte         |           |           | 1000 0000            | 1000 0000                       |

| 193h                   | EEDATL | EEPROM /                    | Program Me                   | mory Read Da   | ata Register L  | .ow Byte      |              |           |           | XXXX XXXX            | uuuu uuuu                       |

| 194h                   | EEDATH | _                           | _                            | ,<br>          | •               | ory Read Dat  | a Register H | ligh Byte |           | xx xxxx              | uu uuuu                         |

| 195h                   | EECON1 | EEPGD                       | CFGS                         | LWLO           | FREE            | WRERR         | WREN         | WR        | RD        |                      | 0000 q000                       |

| 196h                   | EECON2 | EEPROM of                   | EEPROM control register 2    |                |                 |               |              |           |           | 0000 0000            | -                               |

| 197h                   | _      | Unimplemented               |                              |                |                 |               |              |           | _         | _                    |                                 |

| 198h                   | _      | Unimpleme                   | Unimplemented                |                |                 |               |              |           |           | <u> </u>             | _                               |

| 199h                   | RCREG  | USART Receive Data Register |                              |                |                 |               |              |           | 0000 0000 | 0000 0000            |                                 |

| 19Ah                   | TXREG  |                             | USART ransmit Data Register  |                |                 |               |              |           |           | 0000 0000            |                                 |

| 19Bh                   | SPBRGL |                             | BRG<7:0>                     |                |                 |               |              |           |           |                      | 0000 0000                       |

| 19Ch                   | SPBRGH |                             |                              |                | BRG<            |               |              |           |           |                      | 0000 0000                       |

| 19Dh                   | RCSTA  | SPEN                        | RX9                          | SREN           | CREN            | ADDEN         | FERR         | OERR      | RX9D      | 0000 000x            |                                 |

| 19Eh                   | TXSTA  | CSRC                        | TX9                          | TXEN           | SYNC            | SENDB         | BRGH         | TRMT      | TX9D      |                      | 0000 0010                       |

|                        |        | 00110                       |                              |                | 0.110           | 01.00         | 2.1011       |           |           | 2000 0010            |                                 |

### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are

transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: Unimplemented, read as '1'.

| Address                | Name     | Bit 7                                | Bit 6                                | Bit 5          | Bit 4           | Bit 3         | Bit 2        | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|----------|--------------------------------------|--------------------------------------|----------------|-----------------|---------------|--------------|---------|-----------|----------------------|---------------------------------|

| Bank 5                 |          |                                      |                                      |                |                 |               |              |         |           |                      |                                 |

| 280h <sup>(2)</sup>    | INDF0    |                                      | this location ical register)         | uses contents  | s of FSR0H/F    | SR0L to addre | ess data mer | nory    |           | XXXX XXXX            | XXXX XXXX                       |

| 281h <sup>(2)</sup>    | INDF1    |                                      | this location ical register)         | uses contents  | s of FSR1H/F    | SR1L to addre | ess data mer | nory    |           | XXXX XXXX            | XXXX XXXX                       |

| 282h <sup>(2)</sup>    | PCL      | Program Co                           | ounter (PC) L                        | east Significa | nt Byte         |               |              |         |           | 0000 0000            | 0000 0000                       |

| 283h <sup>(2)</sup>    | STATUS   | _                                    | _                                    | _              | TO              | PD            | Z            | DC      | С         | 1 1000               | q quuu                          |

| 284h <sup>(2)</sup>    | FSR0L    | Indirect Dat                         | a Memory Ad                          | dress 0 Low    | Pointer         |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 285h <sup>(2)</sup>    | FSR0H    | Indirect Dat                         | a Memory Ad                          | dress 0 High   | Pointer         |               |              |         |           | 0000 0000            | 0000 0000                       |

| 286h <sup>(2)</sup>    | FSR1L    | Indirect Dat                         | a Memory Ad                          | dress 1 Low    | Pointer         |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(2)</sup>    | FSR1H    | Indirect Dat                         | a Memory Ad                          | dress 1 High   | Pointer         |               |              |         |           | 0000 0000            | 0000 0000                       |

| 288h <sup>(2)</sup>    | BSR      | —                                    | _                                    | —              |                 |               | BSR<4:0>     |         |           | 0 0000               | 0 0000                          |

| 289h <sup>(2)</sup>    | WREG     | Working Re                           | egister                              |                |                 |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 28Ah <sup>(1, 2)</sup> | PCLATH   | _                                    | Write Buffer                         | for the upper  | 7 bits of the F | rogram Coun   | ter          |         |           | -000 0000            | -000 0000                       |

| 28Bh <sup>(2)</sup>    | INTCON   | GIE                                  | PEIE                                 | TMR0IE         | INTE            | IOCIE         | TMR0IF       | INTF    | IOCIF     | 0000 0000            | 0000 0000                       |

| 28Ch                   | _        | Unimpleme                            | nted                                 |                |                 |               |              |         |           | _                    | _                               |

| 28Dh                   | _        | Unimpleme                            | Unimplemented                        |                |                 |               |              |         |           |                      | _                               |

| 28Eh                   | _        | Unimpleme                            | Unimplemented                        |                |                 |               |              |         |           | _                    | _                               |

| 28Fh                   | —        | Unimpleme                            | nted                                 |                |                 |               |              |         |           | _                    | _                               |

| 290h                   | _        | Unimpleme                            | nted                                 |                |                 |               |              |         |           | _                    | _                               |

| 291h                   | CCPR1L   | Capture/Co                           | mpare/PWM                            | Register 1 (L  | SB)             |               |              |         |           | XXXX XXXX            | uuuu uuuu                       |

| 292h                   | CCPR1H   | Capture/Co                           | mpare/PWM                            | Register 1 (M  | ISB)            |               |              |         |           | XXXX XXXX            | uuuu uuuu                       |

| 293h                   | CCP1CON  | P1M                                  | <1:0>                                | DC1E           | <1:0>           |               | CCP1N        | <3:0>   |           | 0000 0000            | 0000 0000                       |

| 294h                   | PWM1CON  | P1RSEN                               |                                      |                | F               | P1DC<6:0>     |              |         |           | 0000 0000            | 0000 0000                       |

| 295h                   | CCP1AS   | CCP1ASE                              | (                                    | CCP1AS<2:0     | >               | PSS1A         | C<1:0>       | PSS1B   | D<1:0>    | 0000 0000            | 0000 0000                       |

| 296h                   | PSTR1CON | _                                    | _                                    | _              | STR1SYNC        | STR1D         | STR1C        | STR1B   | STR1A     | 0 0001               | 0 0001                          |

| 297h                   | —        | Unimplemented                        |                                      |                |                 |               |              |         | _         | _                    |                                 |

| 298h                   | CCPR2L   | Capture/Compare/PWM Register 2 (LSB) |                                      |                |                 |               |              |         | XXXX XXXX | uuuu uuuu            |                                 |

| 299h                   | CCPR2H   | Capture/Co                           | Capture/Compare/PWM Register 2 (MSB) |                |                 |               |              |         |           | XXXX XXXX            | uuuu uuuu                       |

| 29Ah                   | CCP2CON  | P2M                                  | P2M<1:0> DC2B<1:0> CCP2M<3:0>        |                |                 |               |              |         | 0000 0000 | 0000 0000            |                                 |

| 29Bh                   | PWM2CON  | P2RSEN                               |                                      | P2DC<6:0>      |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 29Ch                   | CCP2AS   | CCP2ASE                              | (                                    |                |                 |               |              |         | 0000 0000 | 0000 0000            |                                 |

| 29Dh                   | PSTR2CON | —                                    | _                                    | —              | STR2SYNC        | STR2D         | STR2C        | STR2B   | STR2A     | 0 0001               | 0 0001                          |

| 29Eh                   | CCPTMRS0 | C4TSEL1                              | C4TSEL0                              | C3TSEL1        | C3TSEL0         | C2TSEL1       | C2TSEL0      | C1TSEL1 | C1TSEL0   | 0000 0000            | 0000 0000                       |

| 29Fh                   | CCPTMRS1 |                                      |                                      | _              |                 |               |              | C5TSE   | L<1:0>    | 00                   | 00                              |

#### TABLE 3-9 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

3: Unimplemented, read as '1'.

# 6.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- Stack Overflow Reset (STKOVF)

- Stack Underflow Reset (STKUNF)

- MCLR Reset (RMCLR)

The PCON register bits are shown in Register 6-2.

# 6.13 Register Definitions: Power Control

## REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | U-0 | R/W/HC-1/q  | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|-----|-------------|------------|------------|------------|

| STKOVF     | STKUNF     | —   | _   | RMCLR       | RI         | POR        | BOR        |

| bit 7      | •          |     |     | · · · · · · |            | •          | bit 0      |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | STKOVF: Stack Overflow Flag bit                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = A Stack Overflow occurred                                                                                                     |

|         | 0 = A Stack Overflow has not occurred or set to '0' by firmware                                                                   |

| bit 6   | STKUNF: Stack Underflow Flag bit                                                                                                  |

|         | 1 = A Stack Underflow occurred                                                                                                    |

|         | 0 = A Stack Underflow has not occurred or set to '0' by firmware                                                                  |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                        |

| bit 3   | RMCLR: MCLR Reset Flag bit                                                                                                        |

|         | 1 = A MCLR Reset has not occurred or set to '1' by firmware                                                                       |

|         | 0 = A MCLR Reset has occurred (set to '0' in hardware when a MCLR Reset occurs)                                                   |

| bit 2   | RI: RESET Instruction Flag bit                                                                                                    |

|         | 1 = A RESET instruction has not been executed or set to '1' by firmware                                                           |

|         | 0 = A RESET instruction has been executed (set to '0' in hardware upon executing a RESET instruction)                             |

| bit 1   | POR: Power-on Reset Status bit                                                                                                    |

|         | 1 = No Power-on Reset occurred                                                                                                    |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                   |

|         | 1 = No Brown-out Reset occurred                                                                                                   |

|         | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

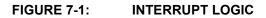

A block diagram of the interrupt logic is shown in Figure 7-1.

# 8.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

The PIC16F193X has an internal Low Dropout Regulator (LDO) which provides operation above 3.6V. The LDO regulates a voltage for the internal device logic while permitting the VDD and I/O pins to operate at a higher voltage. There is no user enable/disable control available for the LDO, it is always active. The PIC16LF193X operates at a maximum VDD of 3.6V and does not incorporate an LDO.

A device I/O pin may be configured as the LDO voltage output, identified as the VCAP pin. Although not required, an external low-ESR capacitor may be connected to the VCAP pin for additional regulator stability.

The VCAPEN<1:0> bits of Configuration Words determines which pin is assigned as the VCAP pin. Refer to Table 8-1.

| TABLE 8-1: VCAPEN<1:0> SELECT BITS |

|------------------------------------|

|------------------------------------|

| VCAPEN<1:0> | Pin     |

|-------------|---------|

| 00          | RA0     |

| 01          | RA5     |

| 10          | RA6     |

| 11          | No Vcap |

On power-up, the external capacitor will load the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information on the constant current rate, refer to the LDO Regulator Characteristics Table in Section 30.0 "Electrical Specifications".

| <b>TABLE 8-2</b> : | SUMMARY OF CONFIGURATION WORD WITH LDO |

|--------------------|----------------------------------------|

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4              | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------------------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         | —       | LVP      | DEBUG                 | —        | BORV     | STVREN  | PLLEN   | 40                  |

| CONFIGZ | 7:0  |         |         | VCAPEN   | \<1:0> <sup>(1)</sup> |          |          | WRT1    | WRT0    | 48                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by LDO.

Note 1: PIC16F1933 only.

# 9.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Timer1 oscillator

- CapSense oscillator

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- · External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or VSS externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

## 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to Section 6.11 "Determining the Cause of a Reset".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### TABLE 15-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) |                             |                             | •                           | uency (Fosc)<br>uency (Fosc) |                             |                             |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|-----------------------------|-----------------------------|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                        | 4 MHz                       | 1 MHz                       |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>        | 500 ns <sup>(2)</sup>       | 2.0 μs                      |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>        | 1.0 μs                      | 4.0 μs                      |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                       | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                       | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                       | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>      |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>        | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>      |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup>  | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

#### FIGURE 15-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| Tcy - Tad    | TAD1   | TAD2     | TAD3   | TAD4   | TAD5   | TAD6     | TAD7    | TAD8     | Tad9               | TAD10    | TAD11      |               |         |

|--------------|--------|----------|--------|--------|--------|----------|---------|----------|--------------------|----------|------------|---------------|---------|

| <b>≜</b> ↑ † |        | b9       | b8     | b7     | b6     | b5       | b4      | b3       | b2                 | b1       | b0         |               |         |

|              | onvers | sion sta | arts   |        |        |          |         |          |                    |          |            |               |         |

| Holding      | capac  | itor is  | discon | nected | from a | inalog i | nput (t | ypically | <sup>,</sup> 100 n | is)      |            |               |         |

| <br>Set GO b | hit    |          |        |        |        |          |         |          |                    |          |            |               |         |

| 5et 60 t     | JIL    |          |        |        | C      | )n tha f |         | g cycle  |                    |          |            |               |         |

|              |        |          |        |        |        |          |         |          |                    | d, GO b  | oit is cle | eared,        |         |

|              |        |          |        |        | A      | DIF bit  | is set, | holding  | g capa             | citor is | connec     | cted to analo | og inpu |

|              |        |          |        |        |        |          |         |          |                    |          |            |               |         |

NOTES:

# 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

- Capacitive Sensing module (CPS)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

# EQUATION 17-1: DAC OUTPUT VOLTAGE

# $\frac{IF DACEN = 1}{VOUT} = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE-$

IF DACEN = 0 and DACLPS = 1 and DACR[4:0] = 11111

VOUT = VSOURCE +

#### IF DACEN = 0 and DACLPS = 0 and DACR[4:0] = 00000

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF+, or FVR BUFFER 2

VSOURCE- = VSS or VREF-

# 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 30.0** "Electrical **Specifications**".

# 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the following equations:

# 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

### 23.4.5 PROGRAMMABLE DEAD-BAND DELAY MODE

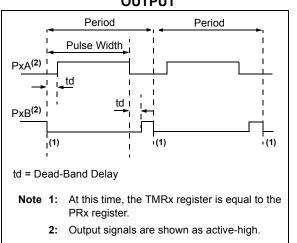

In half-bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

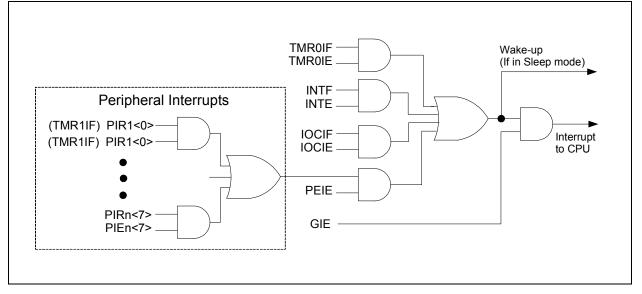

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 23-16 for illustration. The lower seven bits of the associated PWMxCON register (Register 23-5) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 23-16: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 23-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

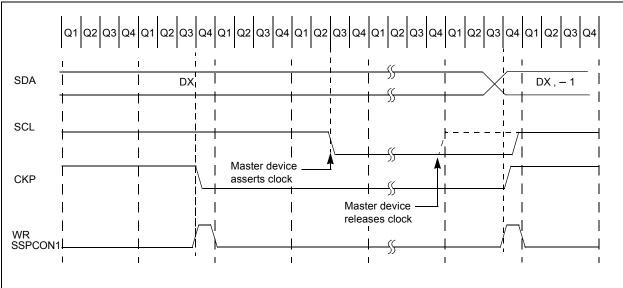

## 24.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

### 24.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the R/ $\overline{W}$  bit of SSPSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPBUF with data to transfer to the master. If the SEN bit of SSPCON2 is set, the slave hardware will always stretch the clock after the  $\overline{ACK}$  sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPBUF was read before the 9th falling edge of SCL.

- Previous versions of the module did not stretch the clock for a transmission if SSPBUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

#### 24.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

#### 24.5.6.3 Byte NACKing

When the AHEN bit of SSPCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCL for a received matching address byte. When the DHEN bit of SSPCON3 is set; CKP is cleared after the 8th falling edge of SCL for received data.

Stretching after the 8th falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

## 24.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 24-23).

#### FIGURE 24-23: CLOCK SYNCHRONIZATION TIMING

## 25.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 25.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 25.5.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 25.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

#### TABLE 25-9: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7    | Bit 6       | Bit 5       | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------|-------------|-------------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF   | RCIDL       | _           | SCKP   | BRG16  | _      | WUE    | ABDEN  | 287                 |

| INTCON  | GIE      | PEIE        | TMR0IE      | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 82                  |

| PIE1    | TMR1GIE  | ADIE        | RCIE        | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 83                  |

| PIR1    | TMR1GIF  | ADIF        | RCIF        | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 86                  |

| RCSTA   | SPEN     | RX9         | SREN        | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 286                 |

| TRISC   | TRISC7   | TRISC6      | TRISC5      | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 125                 |

| TXREG   | EUSART T | ransmit Dat | ta Register |        |        |        |        |        | 277*                |

| TXSTA   | CSRC     | TX9         | TXEN        | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 285                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

\* Page provides register information.

# 30.2 DC Characteristics: Supply Currents (IDD)

| PIC16LF | 1933                                |      |      | d <b>Operati</b><br>g tempera | ature | -40°C ≤ T                                                                                                                      | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended   |  |  |

|---------|-------------------------------------|------|------|-------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| PIC16F1 | 933                                 |      |      | d Operati<br>g tempera        | ature | litions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                 |  |  |

| Param   | Device                              |      |      |                               |       |                                                                                                                                | Conditions                                                                      |  |  |

| No.     | Characteristics                     | Min. | Тур† | Max.                          | Units | VDD                                                                                                                            | Note                                                                            |  |  |

|         | Supply Current (IDD) <sup>(1)</sup> | , 2) |      |                               |       |                                                                                                                                |                                                                                 |  |  |

| D009    | LDO Regulator                       | -    | 350  | —                             | μA    | —                                                                                                                              | HS, EC OR INTOSC/INTOSCIO (8-16 MHz)<br>Clock modes with all VCAP pins disabled |  |  |

|         |                                     |      | 50   | _                             | μA    |                                                                                                                                | All VCAP pins disabled                                                          |  |  |

|         |                                     |      | 30   | —                             | μΑ    |                                                                                                                                | VCAP enabled                                                                    |  |  |

|         |                                     | —    | 5    | —                             | μA    | —                                                                                                                              | LP Clock mode and Sleep<br>(requires FVR and BOR to be disabled)                |  |  |

| D010    |                                     | _    | 8    | 14                            | μA    | 1.8                                                                                                                            | Fosc = 32 kHz                                                                   |  |  |

|         |                                     | -    | 12   | 18                            | μA    | 3.0                                                                                                                            | LP Oscillator mode (Note 4),<br>$-40^{\circ}C \le TA \le +85^{\circ}C$          |  |  |

| D010    |                                     | _    | 23   | 63                            | μA    | 1.8                                                                                                                            | Fosc = 32 kHz                                                                   |  |  |

|         |                                     |      | 28   | 74                            | μA    | 3.0                                                                                                                            | LP Oscillator mode (Note 4, Note 5),                                            |  |  |

|         |                                     | —    | 33   | 79                            | μA    | 5.0                                                                                                                            | $-40^{\circ}C \le TA \le +85^{\circ}C$                                          |  |  |

| D010A   |                                     | _    | 10   | 18                            | μA    | 1.8                                                                                                                            | Fosc = 32 kHz                                                                   |  |  |

|         |                                     | -    | 15   | 20                            | μΑ    | 3.0                                                                                                                            | LP Oscillator mode (Note 4)<br>-40°C $\leq$ TA $\leq$ +125°C                    |  |  |

| D010A   |                                     | —    | 24   | 79                            | μA    | 1.8                                                                                                                            | Fosc = 32 kHz                                                                   |  |  |

|         |                                     | _    | 30   | 93                            | μA    | 3.0                                                                                                                            | LP Oscillator mode (Note 4, Note 5)                                             |  |  |

|         |                                     | —    | 35   | 99                            | μA    | 5.0                                                                                                                            | $-40^{\circ}C \le TA \le +125^{\circ}C$                                         |  |  |

| D011    |                                     | _    | 120  | 160                           | μΑ    | 1.8                                                                                                                            | Fosc = 1 MHz                                                                    |  |  |

|         |                                     |      | 200  | 255                           | μΑ    | 3.0                                                                                                                            | XT Oscillator mode                                                              |  |  |

| D011    |                                     |      | 160  | 195                           | μA    | 1.8                                                                                                                            | Fosc = 1 MHz                                                                    |  |  |

|         |                                     | _    | 230  | 275                           | μA    | 3.0                                                                                                                            | XT Oscillator mode (Note 5)                                                     |  |  |

|         |                                     |      | 280  | 410                           | μA    | 5.0                                                                                                                            |                                                                                 |  |  |

| D012    |                                     |      | 325  | 370                           | μA    | 1.8                                                                                                                            | Fosc = 4 MHz                                                                    |  |  |

|         |                                     | -    | 600  | 710                           | μΑ    | 3.0                                                                                                                            | XT Oscillator mode                                                              |  |  |

| D012    |                                     |      | 350  | 410                           | μΑ    | 1.8                                                                                                                            | Fosc = 4 MHz                                                                    |  |  |

|         |                                     |      | 625  | 765                           | μΑ    | 3.0                                                                                                                            | XT Oscillator mode (Note 5)                                                     |  |  |

|         |                                     | —    | 700  | 850                           | μΑ    | 5.0                                                                                                                            |                                                                                 |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

**5:** 0.1 μF capacitor on VCAP.

6: 8 MHz crystal oscillator with 4x PLL enabled.

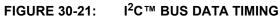

| Param<br>No. | Symbol  | Charac          | teristic     | Min. | Тур | Max. | Units | Conditions                   |

|--------------|---------|-----------------|--------------|------|-----|------|-------|------------------------------|

| NO.          |         |                 |              |      |     |      |       |                              |

| SP90*        | TSU:STA | Start condition | 100 kHz mode | 4700 | —   | —    | ns    | Only relevant for Repeated   |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |       | Start condition              |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | —   | —    | ns    | After this period, the first |

|              |         | Hold time       | 400 kHz mode | 600  | _   | —    |       | clock pulse is generated     |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | —    | ns    |                              |

|              |         | Setup time      | 400 kHz mode | 600  | _   | —    |       |                              |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   |      | ns    |                              |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                              |

# TABLE 30-15: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.

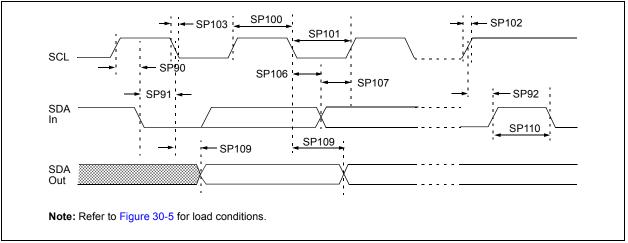

# Package Marking Information (Continued)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                                 | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                              |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

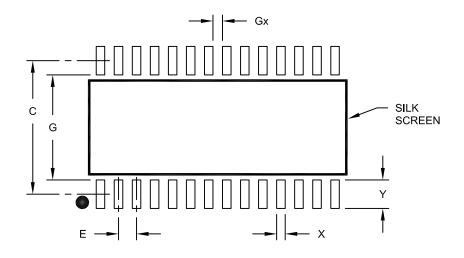

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units    | N    | <b>ILLIMETER</b> | S    |

|--------------------------|----------|------|------------------|------|

| Dimension                | n Limits | MIN  | NOM              | MAX  |

| Contact Pitch            | E        |      | 1.27 BSC         |      |

| Contact Pad Spacing      | С        |      | 9.40             |      |

| Contact Pad Width (X28)  | X        |      |                  | 0.60 |

| Contact Pad Length (X28) | Y        |      |                  | 2.00 |

| Distance Between Pads    | Gx       | 0.67 |                  |      |

| Distance Between Pads    | G        | 7.40 |                  |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

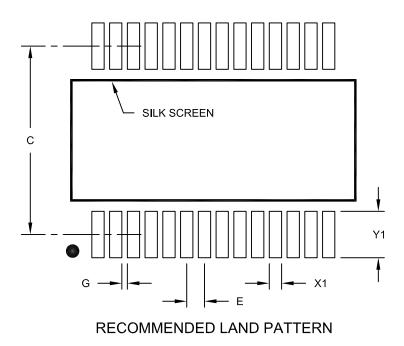

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | Ν    | <b><i>MILLIMETER</i></b> | S    |

|--------------------------|----------|------|--------------------------|------|

| Dimensior                | n Limits | MIN  | NOM                      | MAX  |

| Contact Pitch            | E        |      | 0.65 BSC                 |      |

| Contact Pad Spacing      | С        |      | 7.20                     |      |

| Contact Pad Width (X28)  | X1       |      |                          | 0.45 |

| Contact Pad Length (X28) | Y1       |      |                          | 1.75 |

| Distance Between Pads    | G        | 0.20 |                          |      |

Notes: