Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1933-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See Section 5.3 "Clock Switching" for additional information.

### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

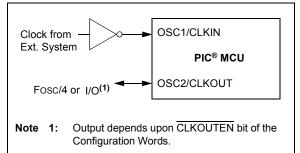

## 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- High power, 4-32 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

## 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

| FIGURE 5-7:            | INTERNAL OSCILLATOR SWITCH TIMING                |

|------------------------|--------------------------------------------------|

| HFINTOSC/-+            | LFINTOSC (FSCM and WDT disabled)                 |

| MFINTOSC               |                                                  |

| HFINTOSC/<br>MFINTOSC  | Start-up Time 2-cycle Sync Running               |

| LFINTOSC               |                                                  |

| IRCF <3:0>             | $\neq 0$ $X = 0$                                 |

| System Clock           |                                                  |

|                        |                                                  |

| HFINTOSC/→<br>MFINTOSC | LFINTOSC (Either FSCM or WDT enabled)            |

| HFINTOSC/<br>MFINTOSC  | 2-cycle Sync Running                             |

| LFINTOSC               |                                                  |

| IRCF <3:0>             | $\neq 0$ $X = 0$                                 |

| System Clock           |                                                  |

|                        |                                                  |

| LFINTOSC →             | HFINTOSC/MFINTOSC                                |

|                        | LFINTOSC turns off unless WDT or FSCM is enabled |

| LFINTOSC               |                                                  |

|                        | Start-up Time 2-cycle Sync Running               |

| HFINTOSC/<br>MFINTOSC  |                                                  |

| IRCF <3:0>             | = 0 X ≠ 0                                        |

| System Clock           |                                                  |

|                        |                                                  |

|                        |                                                  |

## 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 9.0 "Power-Down Mode (Sleep)" for more details.

## 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

## 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the Shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine (ISR), these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding Shadow register should be modified and the value will be restored when exiting the ISR. The Shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

## 12.4 PORTB Registers

## 12.4.1 DATA REGISTER

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-7). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 12-6) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

## 12.4.2 DIRECTION CONTROL

The TRISB register (Register 12-7) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

## 12.4.3 WEAK PULL-UPS

Each of the PORTB pins has an individually configurable internal weak pull-up. Control bits WPUB<7:0> enable or disable each pull-up (see Register 12-10). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the WPUEN bit of the OPTION\_REG register.

## 12.4.4 INTERRUPT-ON-CHANGE

All of the PORTB pins are individually configurable as an interrupt-on-change pin. Control bits IOCB<7:0> enable or disable the interrupt function for each pin. The interrupt-on-change feature is disabled on a Power-on Reset. Reference Section 13.0 "Interrupt-on-Change" for more information.

### 12.4.5 ANALOG CONTROL

The ANSELB register (Register 12-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode

will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

## 15.3 Register Definitions: ADC Control

## REGISTER 15-1: ADCON0: A/D CONTROL REGISTER 0

| U-0                              | R/W-0/0                  | R/W-0/0                            | R/W-0/0        | R/W-0/0            | R/W-0/0         | R/W-0/0            | R/W-0/0      |

|----------------------------------|--------------------------|------------------------------------|----------------|--------------------|-----------------|--------------------|--------------|

|                                  |                          |                                    | CHS<4:0>       |                    |                 | GO/DONE            | ADON         |

| oit 7                            |                          |                                    |                |                    |                 |                    | bit          |

|                                  |                          |                                    |                |                    |                 |                    |              |

| <b>₋egend:</b><br>R = Readabl    | la hit                   | W = Writable                       | hit            | II – Unimplon      | nanted hit rea  | vd oo 'O'          |              |

|                                  |                          | x = Bit is unki                    |                |                    | nented bit, rea | OR/Value at all o  | othor Donata |

| u = Bit is und<br>1' = Bit is se | •                        |                                    |                |                    | at FOR and B    | JR/ value at all t |              |

| I = BIUS SE                      |                          | '0' = Bit is cle                   | ared           |                    |                 |                    |              |

| oit 7                            | Unimpleme                | nted: Read as '                    | 0'             |                    |                 |                    |              |

| oit 6-2                          | CHS<4:0>:                | Analog Channe                      | Select bits    |                    |                 |                    |              |

|                                  |                          | R (Fixed Voltag                    | e Reference)   | Buffer 1 Output    | (2)             |                    |              |

|                                  | 11110 = <b>D</b> A       |                                    | (3)            |                    |                 |                    |              |

|                                  |                          | mperature Indic<br>eserved. No cha |                | d                  |                 |                    |              |

|                                  | • •                      | serveu. No cha                     | mer connecte   | u.                 |                 |                    |              |

|                                  | •                        |                                    |                |                    |                 |                    |              |

|                                  | •                        |                                    |                |                    |                 |                    |              |

|                                  |                          | eserved. No cha                    | nnel connecte  | d.                 |                 |                    |              |

|                                  | 01101 = AN               | -                                  |                |                    |                 |                    |              |

|                                  | 01100 = AN               |                                    |                |                    |                 |                    |              |

|                                  | 01011 = AN<br>01010 = AN |                                    |                |                    |                 |                    |              |

|                                  | 01000 = AN               |                                    |                |                    |                 |                    |              |

|                                  | 01000 = AN               |                                    |                |                    |                 |                    |              |

|                                  |                          | served. No cha                     | nnel connecte  | d.                 |                 |                    |              |

|                                  | 00110 <b>= Re</b>        | eserved. No cha                    | nnel connecte  | d.                 |                 |                    |              |

|                                  | 00101 = Re               | eserved. No cha                    | nnel connecte  | d.                 |                 |                    |              |

|                                  | 00100 = AN               | 14                                 |                |                    |                 |                    |              |

|                                  | 00011 = AN               |                                    |                |                    |                 |                    |              |

|                                  | 00010 = AN               |                                    |                |                    |                 |                    |              |

|                                  | 00001 = AN<br>00000 = AN |                                    |                |                    |                 |                    |              |

| oit 1                            |                          | A/D Conversion                     | Status bit     |                    |                 |                    |              |

|                                  | 1 = A/D conv             | version cycle in                   | progress. Sett | ing this bit start | s an A/D conv   | ersion cycle.      |              |

|                                  | This bit is              | s automatically                    | cleared by har | dware when the     |                 | ion has complet    | ed.          |

|                                  | 0 = A/D conv             | version complet                    | ed/not in prog | ress               |                 |                    |              |

| oit 0                            | ADON: ADC                | Enable bit                         |                |                    |                 |                    |              |

|                                  | 1 = ADC is e             |                                    |                |                    |                 |                    |              |

|                                  | 0 = ADC is c             | lisabled and co                    | nsumes no op   | erating current    |                 |                    |              |

|                                  | ee Section 17.0          | -                                  | -              |                    |                 | information.       |              |

| <b>2</b> : S                     | ee Section 14.0          | 0 "Fixed Voltag                    | e Reference    | (FVR)" for more    | e information.  |                    |              |

| 3: S                             | ee Section 16.0          | ) "Temperature                     | Indicator Mo   | dule" for more     | information     |                    |              |

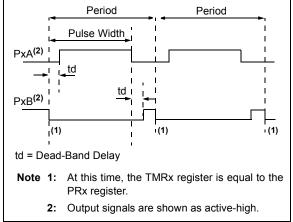

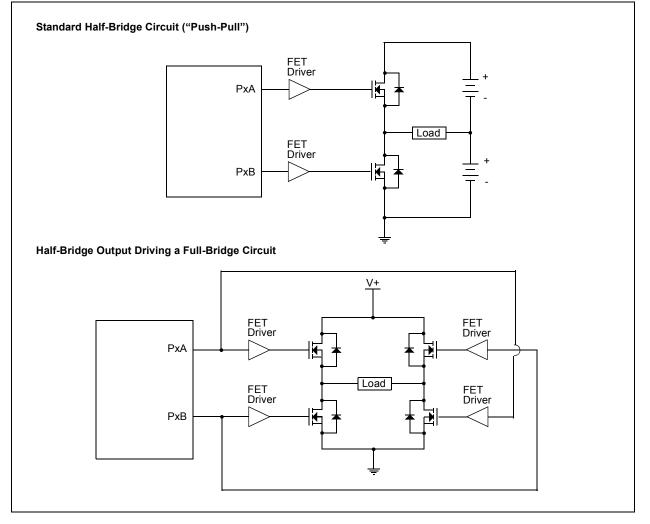

## 23.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 23-9). This mode can be used for Half-Bridge applications, as shown in Figure 23-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See Section 23.4.5 "Programmable Dead-Band Delay Mode" for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

## FIGURE 23-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 23-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

## REGISTER 24-3: SSPCON2: SSP CONTROL REGISTER 2

| R/W-0/0          | R-0/0                                                                                                                                                        | R/W-0/0                                           | R/S/HS-0/0                     | R/S/HS-0/0                   | R/S/HS-0/0        | R/S/HS-0/0       | R/W/HS-0/0   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|------------------------------|-------------------|------------------|--------------|

| GCEN             | ACKSTAT                                                                                                                                                      | ACKDT                                             | ACKEN                          | RCEN                         | PEN               | RSEN             | SEN          |

| bit 7            |                                                                                                                                                              |                                                   |                                |                              |                   |                  | bit C        |

|                  |                                                                                                                                                              |                                                   |                                |                              |                   |                  |              |

| Legend:          |                                                                                                                                                              |                                                   |                                |                              |                   |                  |              |

| R = Readable     | e bit                                                                                                                                                        | W = Writable                                      | bit                            | U = Unimpler                 | mented bit, read  | 1 as '0'         |              |

| u = Bit is unc   | hanged                                                                                                                                                       | x = Bit is unk                                    | nown                           | -n/n = Value a               | at POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is set | t                                                                                                                                                            | '0' = Bit is cle                                  | eared                          | HC = Cleared                 | d by hardware     | S = User set     |              |

| bit 7            | 1 = Enable in                                                                                                                                                | nterrupt when a                                   | •                              | .,                           | or 00h) is receiv | red in the SSPS  | SR           |

|                  |                                                                                                                                                              | call address di                                   |                                |                              |                   |                  |              |

| bit 6            | 1 = Acknowle                                                                                                                                                 | cknowledge Si<br>edge was not r<br>edge was recei |                                | mode only)                   |                   |                  |              |

| bit 5            |                                                                                                                                                              | -                                                 | ı bit (in I <sup>2</sup> C moo | de only)                     |                   |                  |              |

|                  | In Receive m                                                                                                                                                 | i <u>ode:</u><br>iitted when the<br>iowledge      | ·                              | • •                          | le sequence at    | the end of a re  | ceive        |

| bit 4            | ACKEN: Ack                                                                                                                                                   | nowledge Seq                                      | uence Enable                   | bit (in I <sup>2</sup> C Mas | ter mode only)    |                  |              |

|                  | In Master Re                                                                                                                                                 | ceive mode:                                       |                                | ,                            |                   |                  |              |

|                  | Automat                                                                                                                                                      | Acknowledge<br>ically cleared b<br>edge sequenc   | y hardware.                    | SDA and S                    | CL pins, and      | transmit ACF     | KDT data bit |

| bit 3            | RCEN: Rece                                                                                                                                                   | ive Enable bit                                    | (in I <sup>2</sup> C Master i  | mode only)                   |                   |                  |              |

|                  | RCEN: Receive Enable bit (in I <sup>2</sup> C Master mode only)<br>1 = Enables Receive mode for I <sup>2</sup> C<br>0 = Receive idle                         |                                                   |                                |                              |                   |                  |              |

| bit 2            | PEN: Stop Co                                                                                                                                                 | ondition Enabl                                    | e bit (in I <sup>2</sup> C Ma  | ster mode only               | y)                |                  |              |

|                  |                                                                                                                                                              | Release Contro                                    | _                              |                              |                   |                  |              |

|                  | 0 = Stop cond                                                                                                                                                | dition Idle                                       |                                |                              | atically cleared  |                  |              |

| bit 1            |                                                                                                                                                              |                                                   |                                |                              | ster mode only)   |                  |              |

|                  | <ul> <li>1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = Repeated Start condition Idle</li> </ul> |                                                   |                                |                              |                   |                  | nardware.    |

| bit 0            | SEN: Start C                                                                                                                                                 | ondition Enabl                                    | e/Stretch Enab                 | le bit                       |                   |                  |              |

|                  | <u>In Master mo</u><br>1 = Initiate St<br>0 = Start con                                                                                                      | tart condition o                                  | n SDA and SC                   | L pins. Autom                | atically cleared  | by hardware.     |              |

|                  |                                                                                                                                                              |                                                   |                                | ave transmit ar              | nd slave receive  | e (stretch enab  | led)         |

| Note 1: Fo       | or bits ACKEN, F                                                                                                                                             | RCEN, PEN, R                                      | SEN, SEN: If ti                | he I <sup>2</sup> C module   | is not in the IdI | e mode, this bi  | t may not be |

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

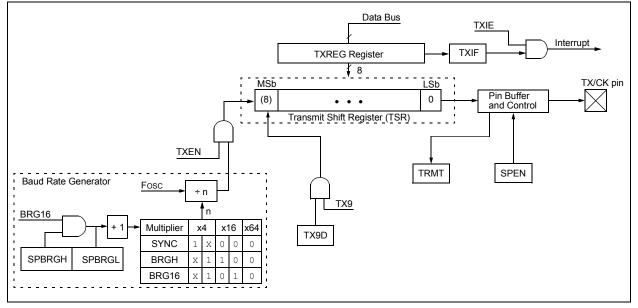

## 25.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 25-1 and Figure 25-2.

## FIGURE 25-1: EUSART TRANSMIT BLOCK DIAGRAM

| Name    | Bit 7     | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------|-------------|------------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF    | RCIDL       | —          | SCKP   | BRG16  | —      | WUE    | ABDEN  | 287                 |

| INTCON  | GIE       | PEIE        | TMR0IE     | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 82                  |

| PIE1    | TMR1GIE   | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 83                  |

| PIR1    | TMR1GIF   | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 86                  |

| RCREG   | EUSART F  | Receive Dat | a Register |        |        |        |        |        | 280*                |

| RCSTA   | SPEN      | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 286                 |

| SPBRGL  |           | BRG<7:0>    |            |        |        |        | 288*   |        |                     |

| SPBRGH  | BRG<15:8> |             |            |        |        | 288*   |        |        |                     |

| TRISC   | TRISC7    | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 125                 |

| TXSTA   | CSRC      | TX9         | TXEN       | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 285                 |

## TABLE 25-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

| FIGURE 25-12:                                      | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                    |

|----------------------------------------------------|------------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)            | bit 0     bit 2     bit 3     bit 4     bit 5     bit 6     bit 7            |

| TX/CK pin                                          |                                                                              |

| SREN bit                                           | <u>'0'</u>                                                                   |

| RCIF bit<br>(Interrupt) ————<br>Read<br>RXREG ———— |                                                                              |

|                                                    | agram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

## TABLE 25-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name    | Bit 7     | Bit 6                                   | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------|-----------------------------------------|------------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF    | RCIDL                                   | _          | SCKP   | BRG16  | _      | WUE    | ABDEN  | 287                 |

| INTCON  | GIE       | PEIE                                    | TMR0IE     | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 82                  |

| PIE1    | TMR1GIE   | ADIE                                    | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 83                  |

| PIR1    | TMR1GIF   | ADIF                                    | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 86                  |

| RCREG   | EUSART R  | eceive Dat                              | a Register |        |        |        |        |        | 280*                |

| RCSTA   | SPEN      | SPEN RX9 SREN CREN ADDEN FERR OERR RX9D |            |        |        |        | 286    |        |                     |

| SPBRGL  |           | BRG<7:0>                                |            |        |        |        | 288*   |        |                     |

| SPBRGH  | BRG<15:8> |                                         |            |        |        | 288*   |        |        |                     |

| TRISC   | TRISC7    | TRISC6                                  | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 125                 |

| TXSTA   | CSRC      | TX9                                     | TXEN       | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 285                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

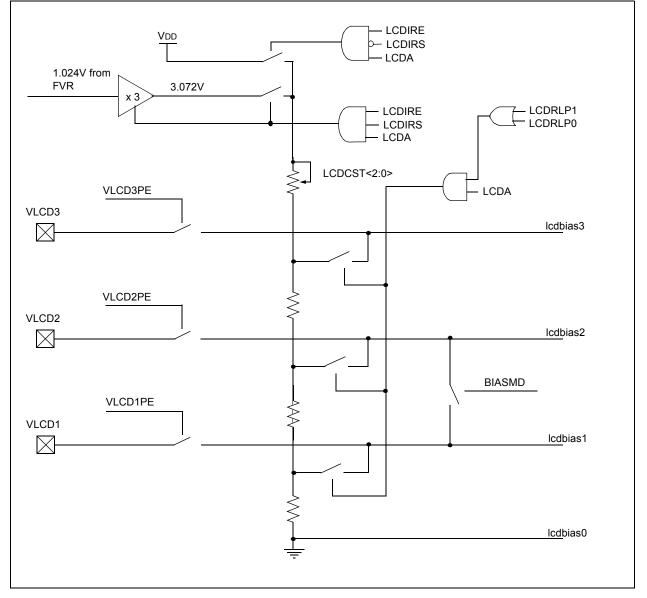

## 27.4 LCD Bias Voltage Generation

The LCD module can be configured for one of three bias types:

- Static Bias (two voltage levels: VSS and VLCD)

- + 1/2 Bias (three voltage levels: Vss, 1/2 VLcD and VLcD)

- 1/3 Bias (four voltage levels: VSS, 1/3 VLCD, 2/3 VLCD and VLCD)

### TABLE 27-2: LCD BIAS VOLTAGES

|            | Static Bias | 1/2 Bias | 1/3 Bias |

|------------|-------------|----------|----------|

| LCD Bias 0 | Vss         | Vss      | Vss      |

| LCD Bias 1 | _           | 1/2 Vdd  | 1/3 Vdd  |

| LCD Bias 2 | _           | 1/2 Vdd  | 2/3 Vdd  |

| LCD Bias 3 | VLCD3       | VLCD3    | VLCD3    |

So that the user is not forced to place external components and use up to three pins for bias voltage generation, internal contrast control and an internal reference ladder are provided internally to the PIC16(L)F1933. Both of these features may be used in conjunction with the external VLCD<3:1> pins, to provide maximum flexibility. Refer to Figure 27-3.

## FIGURE 27-3: LCD BIAS VOLTAGE GENERATION BLOCK DIAGRAM

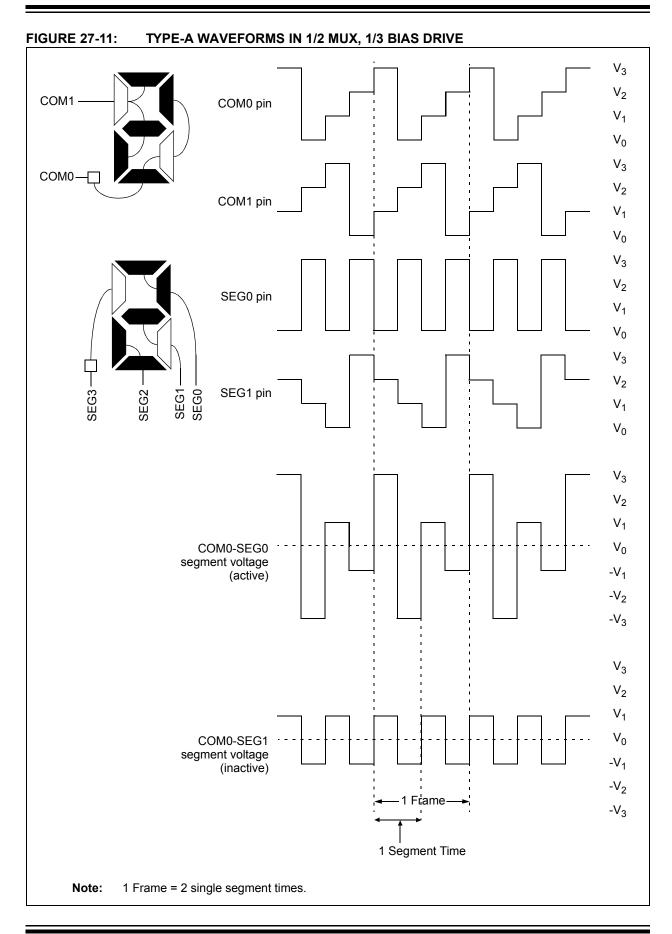

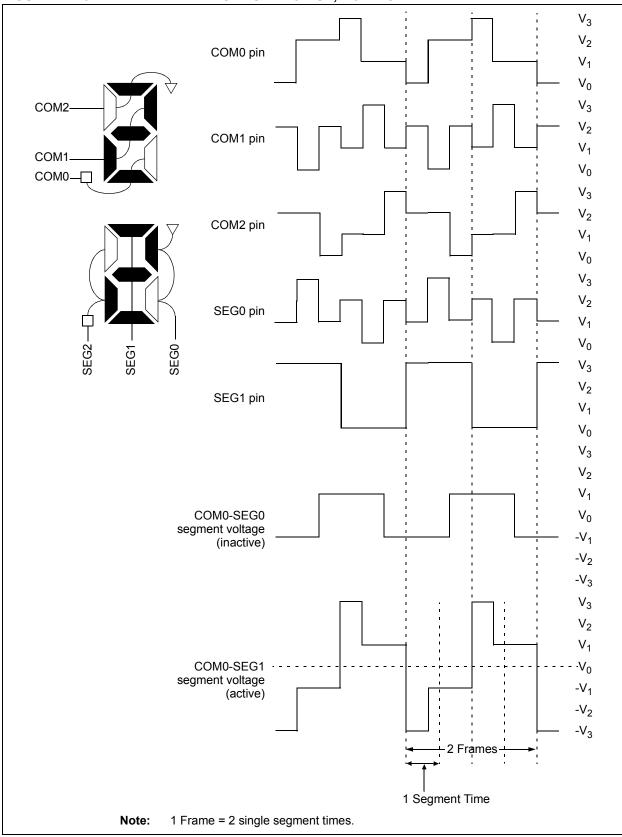

## 27.6 LCD Multiplex Types

The LCD driver module can be configured into one of four multiplex types:

- Static (only COM0 is used)

- 1/2 multiplex (COM<1:0> are used)

- 1/3 multiplex (COM<2:0> are used)

- 1/4 multiplex (COM<3:0> are used)

The LMUX<1:0> bit setting of the LCDCON register decides which of the LCD common pins are used (see Table 27-4 for details).

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. If the pin is a COM drive, then the TRIS setting of that pin is overridden.

| Multiplex | LMUX<br><1:0> | СОМЗ   | COM2   | COM1   |  |  |

|-----------|---------------|--------|--------|--------|--|--|

| Static    | 00            | Unused | Unused | Unused |  |  |

| 1/2       | 01            | Unused | Unused | Active |  |  |

| 1/3       | 10            | Unused | Active | Active |  |  |

| 1/4       | 11            | Active | Active | Active |  |  |

TABLE 27-4: COMMON PIN USAGE

## 27.7 Segment Enables

The LCDSEn registers are used to select the pin function for each segment pin. The selection allows each pin to operate as either an LCD segment driver or as one of the pin's alternate functions. To configure the pin as a segment pin, the corresponding bits in the LCDSEn registers must be set to '1'.

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. Any bit set in the LCDSEn registers overrides any bit settings in the corresponding TRIS register.

Note: On a Power-on Reset, these pins are configured as normal I/O, not LCD pins.

## 27.8 Pixel Control

The LCDDATAx registers contain bits which define the state of each pixel. Each bit defines one unique pixel.

Register 27-6 shows the correlation of each bit in the LCDDATAx registers to the respective common and segment signals.

Any LCD pixel location not being used for display can be used as general purpose RAM.

## 27.9 LCD Frame Frequency

The rate at which the COM and SEG outputs change is called the LCD frame frequency.

## TABLE 27-5: FRAME FREQUENCY FORMULAS

| Multiplex | Frame Frequency =                            |

|-----------|----------------------------------------------|

| Static    | Clock source/(4 x 1 x (LCD Prescaler) x 32)) |

| 1/2       | Clock source/(2 x 2 x (LCD Prescaler) x 32)) |

| 1/3       | Clock source/(1 x 3 x (LCD Prescaler) x 32)) |

| 1/4       | Clock source/(1 x 4 x (LCD Prescaler) x 32)) |

|           |                                              |

Note: Clock source is Fosc/256, T1OSC or LFINTOSC.

#### TABLE 27-6: APPROXIMATE FRAME FREQUENCY (IN Hz) USING Fosc @ 8 MHz, TIMER1 @ 32.768 kHz OR LFINTOSC

| LP<3:0> | Static | 1/2 | 1/3 | 1/4 |

|---------|--------|-----|-----|-----|

| 2       | 122    | 122 | 162 | 122 |

| 3       | 81     | 81  | 108 | 81  |

| 4       | 61     | 61  | 81  | 61  |

| 5       | 49     | 49  | 65  | 49  |

| 6       | 41     | 41  | 54  | 41  |

| 7       | 35     | 35  | 47  | 35  |

## 29.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

## TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| n     | FSR or INDF number. (0-1)                                                                                                                                                            |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                          |

### TABLE 29-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |  |  |  |

|-------|-----------------|--|--|--|

| PC    | Program Counter |  |  |  |

| TO    | Time-out bit    |  |  |  |

| С     | Carry bit       |  |  |  |

| DC    | Digit carry bit |  |  |  |

| Z     | Zero bit        |  |  |  |

| PD    | Power-down bit  |  |  |  |

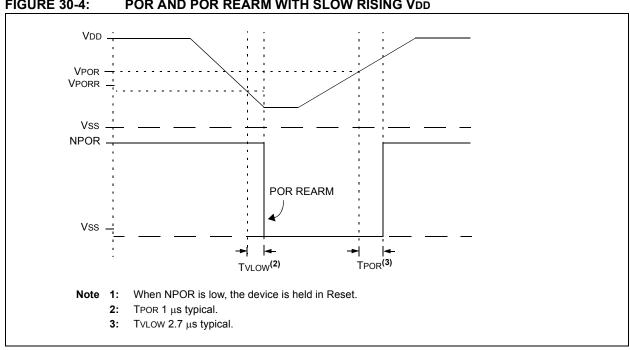

FIGURE 30-4: POR AND POR REARM WITH SLOW RISING VDD

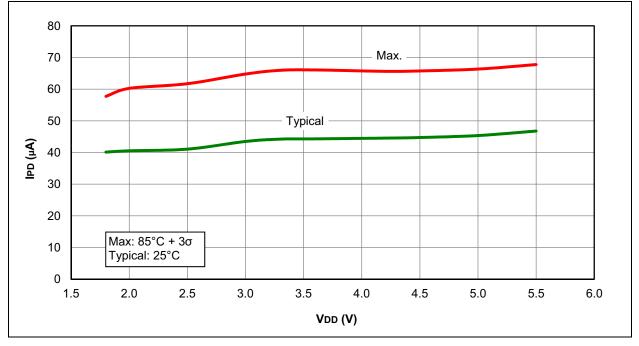

## 30.3 DC Characteristics: Power-Down Currents (IPD) (Continued)

| PIC16LF1933<br>PIC16F1933 |                         |                      |      | Standard Operating Conc<br>Operating temperature |                |                                                                                                                               | ditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                 |  |

|---------------------------|-------------------------|----------------------|------|--------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|

|                           |                         |                      |      | rd Operation<br>ng temper                        | •              | itions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                                                                                    |                                                                 |  |

| Param<br>No.              | Device Characteristics  | Min.                 | Тур† | Max.<br>+85°C                                    | Max.<br>+125°C | Units                                                                                                                         | Conditions                                                                                                                                         |                                                                 |  |

|                           |                         |                      |      |                                                  |                |                                                                                                                               | VDD                                                                                                                                                | Note                                                            |  |

|                           | Power-down Base Current | (IPD) <sup>(2)</sup> |      |                                                  |                |                                                                                                                               |                                                                                                                                                    |                                                                 |  |

| D028                      |                         |                      | 0.1  | 1                                                | 7              | μA                                                                                                                            | 1.8                                                                                                                                                | A/D Current (Note 1, Note 3),                                   |  |

|                           |                         | —                    | 0.1  | 2                                                | 8              | μA                                                                                                                            | 3.0                                                                                                                                                | no conversion in progress                                       |  |

| D028                      |                         |                      | 16   | 56                                               | 70             | μA                                                                                                                            | 1.8                                                                                                                                                | A/D Current (Note 1, Note 3),<br>no conversion in progress      |  |

|                           |                         | _                    | 21   | 58                                               | 78             | μA                                                                                                                            | 3.0                                                                                                                                                |                                                                 |  |

|                           |                         | —                    | 25   | 61                                               | 88             | μA                                                                                                                            | 5.0                                                                                                                                                |                                                                 |  |

| D028A                     |                         | _                    | 250  | _                                                | —              | μA                                                                                                                            | 1.8                                                                                                                                                | A/D Current (Note 1, Note 3),<br>conversion in progress         |  |

|                           |                         | —                    | 250  |                                                  |                | μA                                                                                                                            | 3.0                                                                                                                                                |                                                                 |  |

| D028A                     |                         | _                    | 280  | _                                                | _              | μA                                                                                                                            | 1.8                                                                                                                                                | A/D Current (Note 1, Note 3,<br>Note 4), conversion in progress |  |

|                           |                         | —                    | 280  | _                                                | _              | μA                                                                                                                            | 3.0                                                                                                                                                |                                                                 |  |

|                           |                         | —                    | 280  |                                                  | _              | μA                                                                                                                            | 5.0                                                                                                                                                |                                                                 |  |

| D029                      |                         | —                    | 1.9  | 6                                                | 6              | μA                                                                                                                            | 1.8                                                                                                                                                | Cap Sense, Low-Power mode<br>CPSRM = 0, cpsrng = 01<br>(Note 1) |  |

|                           |                         | —                    | 3.6  | 9                                                | 9              | μΑ                                                                                                                            | 3.0                                                                                                                                                |                                                                 |  |

| D029                      |                         | _                    | 20   | 61                                               | 76             | μA                                                                                                                            | 1.8                                                                                                                                                | Cap Sense, Low-Power mode                                       |  |

|                           |                         | —                    | 24   | 64                                               | 79             | μA                                                                                                                            | 3.0                                                                                                                                                | CPSRM = 0, cpsrng = 01                                          |  |

|                           |                         | —                    | 26   | 66                                               | 83             | μA                                                                                                                            | 5.0                                                                                                                                                | (Note 1)                                                        |  |

| D030                      |                         | —                    | 1    | _                                                | _              | μA                                                                                                                            | 3.0                                                                                                                                                | LCD Bias Ladder, Low-power                                      |  |

|                           |                         | —                    | 10   | _                                                | _              | μA                                                                                                                            | 3.0                                                                                                                                                | LCD Bias Ladder, Medium-power                                   |  |

|                           |                         | —                    | 75   |                                                  | —              | μA                                                                                                                            | 3.0                                                                                                                                                | LCD Bias Ladder, High-power                                     |  |

| D030                      |                         | _                    | 1    |                                                  | —              | μA                                                                                                                            | 5.0                                                                                                                                                | LCD Bias Ladder, Low-power                                      |  |

|                           |                         | _                    | 10   | —                                                | —              | μA                                                                                                                            | 5.0                                                                                                                                                | LCD Bias Ladder, Medium-power                                   |  |

|                           |                         | —                    | 75   | —                                                | _              | μA                                                                                                                            | 5.0                                                                                                                                                | LCD Bias Ladder, High-power                                     |  |

| D031                      |                         |                      | 16   | 18                                               | 18             | μΑ                                                                                                                            | 1.8                                                                                                                                                | Comparator, Low-Power mode                                      |  |

|                           |                         | _                    | 18   | 20                                               | 20             | μA                                                                                                                            | 3.0                                                                                                                                                |                                                                 |  |

| D031                      |                         | _                    | 27   | 65                                               | 81             | μA                                                                                                                            | 1.8                                                                                                                                                | Comparator, Low-Power mode                                      |  |

|                           |                         | _                    | 30   | 75                                               | 94             | μA                                                                                                                            | 3.0                                                                                                                                                |                                                                 |  |

|                           |                         | _                    | 32   | 76                                               | 95             | μA                                                                                                                            | 5.0                                                                                                                                                |                                                                 |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: A/D oscillator source is FRC.

**4:** 0.1 μF capacitor on VCAP.

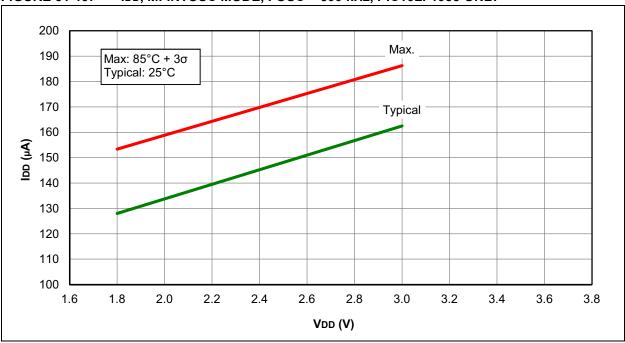

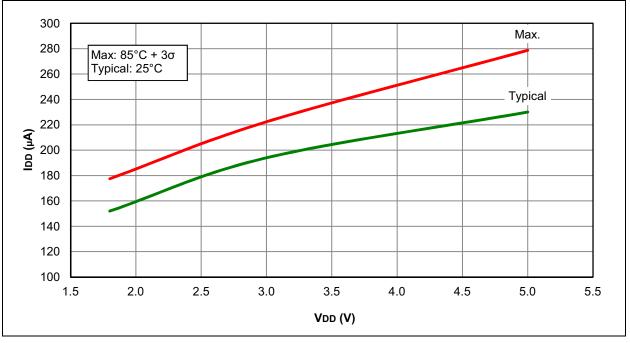

FIGURE 31-19: IDD, MFINTOSC MODE, FOSC = 500 kHz, PIC16LF1933 ONLY

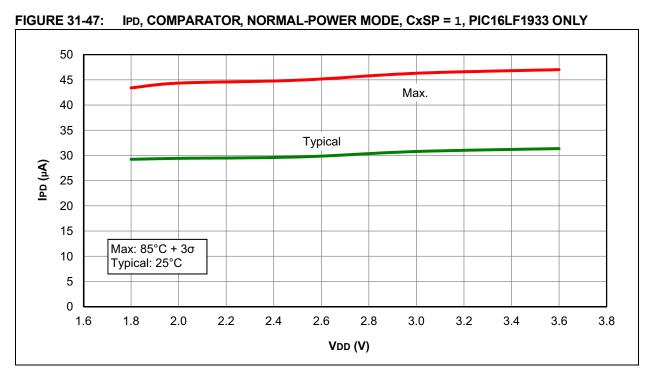

FIGURE 31-48: IPD, COMPARATOR, NORMAL-POWER MODE, CxSP = 1, PIC16F1933 ONLY