Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

|                            |                                                                            |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1933-e-mv |

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000 $\mu$  u1 $\mu$ u' (where  $\mu$  = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

Note 1: The <u>C and DC</u> bits operate as Borrow and <u>Digit Borrow</u> out bits, respectively, in subtraction

# 3.3 Register Definitions: Status

#### **REGISTER 3-1: STATUS: STATUS REGISTER**

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| _     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| hit 7-5 | Unimplemented: Read as '0' |

|---------|----------------------------|

bit 4 TO: Time-Out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

bit 3 **PD:** Power-Down bit

1 = After power-up or by the  ${\tt CLRWDT}$  instruction

0 = By execution of the SLEEP instruction

bit 2 **Z**: Zero bit

1 = The result of an arithmetic or logic operation is zero

$\circ$  = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(1)

1 = A carry-out from the 4th low-order bit of the result occurred

0 = No carry-out from the 4th low-order bit of the result

bit 0 C: Carry/Borrow bit<sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)<sup>(1)</sup>

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

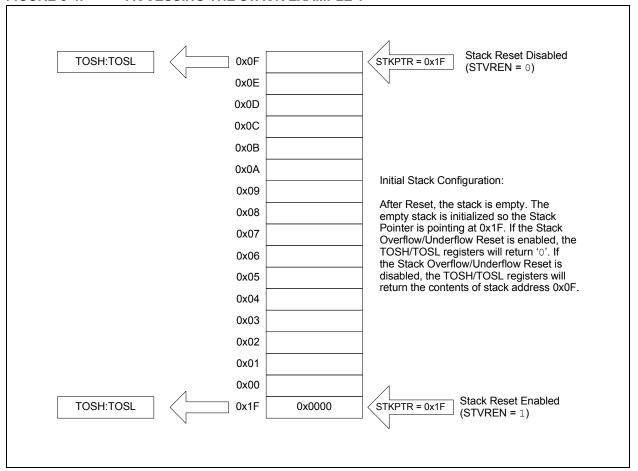

#### 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-4 through 3-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Word 2). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

**Note:** Care should be taken when modifying the STKPTR while interrupts are enabled.

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time, STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

FIGURE 3-4: ACCESSING THE STACK EXAMPLE 1

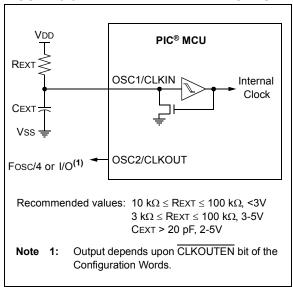

## FIGURE 5-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- · threshold voltage variation

- · component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

# 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

# 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- IRCF<3:0> bits of the OSCCON register are modified.

- If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables in **Section 30.0 "Electrical Specifications"**.

#### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See the Electrical Specifications Chapters for the LFINTOSC tolerances.

### 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

TABLE 10-1: WDT OPERATING MODES

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | X      | Х              | Active      |

| 1.0       | 37     | Awake          | Active      |

| 10        | X      | Sleep          | Disabled    |

| 0.1       | 1      | Х              | Active      |

| 01        | 0      | Х              | Disabled    |

| 00        | X      | Х              | Disabled    |

### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- · Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- · Oscillator Start-up TImer (OST) is running

See Table 10-2 for more information.

### 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register are changed to indicate the event. See Section 3.0 "Memory Organization" and STATUS register (Register 3-1) for more information.

TABLE 10-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                           |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |

| CLRWDT Command                                           | Cleared                      |

| Oscillator Fail Detected                                 |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |

# 11.3.2 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- Load the EEADRH:EEADRL register pair with the address of new row to be erased.

- 2. Clear the CFGS bit of the EECON1 register.

- Set the EEPGD, FREE and WREN bits of the EECON1 register.

- 4. Write 55h, then AAh, to EECON2 (Flash programming unlock sequence).

- Set control bit WR of the EECON1 register to begin the erase operation.

- Poll the FREE bit in the EECON1 register to determine when the row erase has completed.

#### See Example 11-4.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

# 11.3.3 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- Load the starting address of the word(s) to be programmed.

- 2. Load the write latches with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 11-2 (block writes to program memory with eight write latches) for more details. The write latches are aligned to the address boundary defined by EEADRL as shown in Table 11-1. Write operations do not cross these boundaries. At the completion of a program memory write operation, the write latches are reset to contain 0x3FFF.

The following steps should be completed to load the write latches and program a block of program memory. These steps are divided into two parts. First, all write latches are loaded with data except for the last program memory location. Then, the last write latch is loaded and the programming sequence is initiated. A special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. This unlock sequence should not be interrupted.

- Set the EEPGD and WREN bits of the EECON1 register.

- 2. Clear the CFGS bit of the EECON1 register.

- Set the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the EEADRH:EEADRL register pair with the address of the location to be written.

- 5. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The write latch is now loaded.

- 7. Increment the EEADRH:EEADRL register pair to point to the next location.

- Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- 11. Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The entire latch block is now written to Flash program memory.

It is not necessary to load the entire write latch block with user program data. However, the entire write latch block will be written to program memory.

An example of the complete write sequence for eight words is shown in Example 11-5. The initial address is loaded into the EEADRH:EEADRL register pair; the eight words of data are loaded using indirect addressing.

Note: The code sequence provided in Example 11-5 must be repeated multiple times to fully program an erased program memory row.

### 11.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- Load the starting address of the row to be modified.

- Read the existing data from the row into a RAM image.

- Modify the RAM image to contain the new data to be written into program memory.

- Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- Repeat steps 6 and 7 as many times as required to reprogram the erased row.

# 11.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-2.

When read access is initiated on an address outside the parameters listed in Table 11-2, the EEDATH:EEDATL register pair is cleared.

TABLE 11-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### EXAMPLE 11-3: CONFIGURATION WORD AND DEVICE ID ACCESS

```

^{\star} This code block will read 1 word of program memory at the memory address:

PROG ADDR LO (must be 00h-08h) data will be returned in the variables;

PROG DATA HI, PROG DATA LO

BANKSEL EEADRL

; Select correct Bank

MOVLW PROG ADDR LO

; Store LSB of address

MOVWF EEADRL

CLRF

EEADRH

; Clear MSB of address

EECON1, CFGS

BSF

; Select Configuration Space

INTCON, GIE

BCF

; Disable interrupts

EECON1,RD

; Initiate read

BSF

; Executed (See Figure 11-1)

NOP

NOP

; Ignored (See Figure 11-1)

INTCON, GIE

BSF

; Restore interrupts

MOVF

EEDATL, W

; Get LSB of word

PROG DATA LO

; Store in user location

MOVWF

MOVF

EEDATH,W

; Get MSB of word

MOVWF

PROG DATA HI

; Store in user location

```

### 11.7 Register Definitions: Data EEPROM Control

#### REGISTER 11-1: EEDATL: EEPROM DATA LOW BYTE REGISTER

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|--|

|         | EEDAT<7:0> |         |         |         |         |         |         |  |  |

| bit 7   |            |         |         |         |         |         | bit 0   |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **EEDAT<7:0>**: Read/Write Value for EEPROM Data Byte or Least Significant bits of Program Memory

#### REGISTER 11-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|

| _     | _   |         | EEDAT<13:8> |         |         |         |         |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **EEDAT<13:8>**: Read/Write Value for Most Significant bits of Program Memory

#### REGISTER 11-3: EEADRL: EEPROM ADDRESS LOW BYTE REGISTER

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|

| EEADR<7:0>  |         |         |         |         |         |         |         |  |

| bit 7 bit ( |         |         |         |         |         |         |         |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **EEADR<7:0>**: Specifies the Least Significant bits for Program Memory Address or EEPROM Address

### REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | EEADR<14:8> | >       |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 Unimplemented: Read as '1'

bit 6-0 **EEADR<14:8>**: Specifies the Most Significant bits for Program Memory Address or EEPROM Address

Note 1: Unimplemented, read as '1'.

## 12.6 PORTE Registers

#### 12.6.1 DATA REGISTER

RE3 is input only, and also functions as  $\overline{\text{MCLR}}$ . The  $\overline{\text{MCLR}}$  feature can be disabled via a configuration fuse. RE3 also supplies the programming voltage. The TRIS bit for RE3 (TRISE3) always reads '1'.

# 12.6.2 PORTE FUNCTIONS AND OUTPUT PRIORITIES

No output priorities, RE3 is an input only pin.

#### **REGISTER 12-14: PORTE: PORTE REGISTER**

| U-0   | U-0 | U-0 | U-0 | R-x/u | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-------|-----|-----|-------|

| _     | _   | _   | _   | RE3   | _   | _   |       |

| bit 7 |     |     |     |       |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 **Unimplemented**: Read as '0'

bit 3 **RE3**: PORTE Input Pin bit

1 = Port pin is > VIH 0 = Port pin is < VIL

bit 2-0 **Unimplemented**: Read as '0'

#### **REGISTER 12-15: TRISE: PORTE TRI-STATE REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-1 <sup>(1)</sup> | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------------------|-----|-----|-------|

| _     | _   | _   | -   | _                  | _   | _   | _     |

| bit 7 |     |     |     |                    |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 Unimplemented: Read as '0' bit 3 Unimplemented: Read as '1' bit 2-0 Unimplemented: Read as '0'

Note 1: Unimplemented, read as '1'.

### REGISTER 12-16: WPUE: WEAK PULL-UP PORTE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1/1 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------|-----|-----|-------|

| _     | _   | _   | _   | WPUE3   | _   | _   | _     |

| bit 7 |     |     |     |         |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 **Unimplemented:** Read as '0'

bit 3 WPUE3: Weak Pull-up Register bit

1 = Pull-up enabled0 = Pull-up disabled

bit 2-0 **Unimplemented:** Read as '0'

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

TABLE 12-9: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3      | Bit 2   | Bit 1     | Bit 0 | Register on Page |

|---------|-------|-------|-------|----------|------------|---------|-----------|-------|------------------|

| ADCON0  | _     |       |       | CHS<4:0> |            | GO/DONE | ADON      | 143   |                  |

| CCPxCON | PxM<  | <1:0> | DCxB  | <1:0>    | CCPxM<3:0> |         |           | 214   |                  |

| LCDCON  | LCDEN | SLPEN | WERR  | _        | CS<1:0>    |         | LMUX<1:0> |       | 315              |

| LCDSE2  | SE23  | SE22  | SE21  | SE20     | SE19       | SE18    | SE17      | SE16  | 319              |

| PORTE   | _     | _     | _     | _        | RE3        | _       | _         | _     | 127              |

| TRISE   | _     | _     | _     | _        | (3)        | _       | _         | _     | 127              |

| WPUE    | _     | _     | _     | _        | WPUE3      | _       | _         | _     | 128              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by

PORTE.

Note 1: Unimplemented, read as '1'.

### REGISTER 23-2: CCPTMRS0: PWM TIMER SELECTION CONTROL REGISTER 0

| R/W-0/0     | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0     |  |

|-------------|---------|-------------|---------|---------|-------------|---------|-------------|--|

| C4TSEL<1:0> |         | C3TSEL<1:0> |         | C2TSE   | C2TSEL<1:0> |         | C1TSEL<1:0> |  |

| bit 7       |         |             |         |         |             |         | bit 0       |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 C4TSEL<1:0>: CCP4 Timer Selection 11 = Reserved 10 = CCP4 is based off Timer6 in PWM mode 01 = CCP4 is based off Timer4 in PWM mode 00 = CCP4 is based off Timer2 in PWM mode bit 5-4 C3TSEL<1:0>: CCP3 Timer Selection 11 = Reserved 10 = CCP3 is based off Timer6 in PWM mode 01 = CCP3 is based off Timer4 in PWM mode 00 = CCP3 is based off Timer2 in PWM mode bit 3-2 C2TSEL<1:0>: CCP2 Timer Selection 11 = Reserved 10 = CCP2 is based off Timer6 in PWM mode 01 = CCP2 is based off Timer4 in PWM mode 00 = CCP2 is based off Timer2 in PWM mode C1TSEL<1:0>: CCP1 Timer Selection bit 1-0 11 = Reserved 10 = CCP1 is based off Timer6 in PWM mode 01 = CCP1 is based off Timer4 in PWM mode 00 = CCP1 is based off Timer2 in PWM mode

#### REGISTER 23-3: CCPTMRS1: PWM TIMER SELECTION CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| _     | _   | _   | _   | _   | _   | C5TSE   | L<1:0>  |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 **Unimplemented:** Read as '0'

bit 1-0 C5TSEL<1:0>: CCP5 Timer Selection bits

11 = Reserved

10 = CCP5 is based off Timer6 in PWM mode

01 = CCP5 is based off Timer4 in PWM mode

00 = CCP5 is based off Timer2 in PWM mode

TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C™ OPERATION

| Name    | Bit 7     | Bit 6          | Bit 5           | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |

|---------|-----------|----------------|-----------------|--------|--------|--------|--------|--------|-----------------------------|

| INTCON  | GIE       | PEIE           | TMR0IE          | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 82                          |

| PIE1    | TMR1GIE   | ADIE           | RCIE            | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 83                          |

| PIE2    | OSFIE     | C2IE           | C1IE            | EEIE   | BCLIE  | LCDIE  | _      | CCP2IE | 84                          |

| PIR1    | TMR1GIF   | ADIF           | RCIF            | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 86                          |

| PIR2    | OSFIF     | C2IF           | C1IF            | EEIF   | BCLIF  | LCDIF  | _      | CCP2IF | 87                          |

| TRISC   | TRISC7    | TRISC6         | TRISC5          | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 125                         |

| SSPADD  |           |                |                 | ADD<   | :7:0>  |        |        |        | 272                         |

| SSPBUF  | MSSP Rece | ive Buffer/Tra | nsmit Registe   | r      |        |        |        |        | 223*                        |

| SSPCON1 | WCOL      | SSPOV          | SSPEN           | CKP    |        | SSPM   | <3:0>  |        | 268                         |

| SSPCON2 | GCEN      | ACKSTAT        | ACKDT           | ACKEN  | RCEN   | PEN    | RSEN   | SEN    | 270                         |

| SSPCON3 | ACKTIM    | PCIE           | SCIE            | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN   | 271                         |

| SSPMSK  | MSK<7:0>  |                |                 |        |        |        |        |        |                             |

| SSPSTAT | SMP       | CKE            | D/ <del>A</del> | Р      | S      | R/W    | UA     | BF     | 267                         |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

<sup>\*</sup> Page provides register information.

### 25.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a Vol space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 25-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

# 25.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 25-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 25.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note 1:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 25.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one Tcy immediately following the Stop bit transmission. The transmission of the Start bit, data bits and Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 25.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See Section 25.5.1.2 "Clock Polarity".

#### 25.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

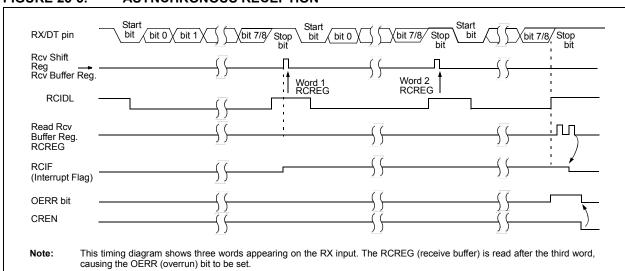

#### 25.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit.

The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit.

The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCSTA register to get the error flags.

The ninth data bit will always be set.

- Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### FIGURE 25-5: ASYNCHRONOUS RECEPTION

#### 27.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 3 LCD Segment Enable registers (LCDSEn)

- Up to 12 LCD data registers (LCDDATAn)

TABLE 27-1: LCD SEGMENT AND DATA REGISTERS

|               | # of LCD Registers |      |  |  |

|---------------|--------------------|------|--|--|

| Device        | Segment<br>Enable  | Data |  |  |

| PIC16(L)F1933 | 2                  | 8    |  |  |

The LCDCON register (Register 27-1) controls the operation of the LCD driver module. The LCDPS register (Register 27-2) configures the LCD clock source prescaler and the type of waveform; Type-A or Type-B. The LCDSEn registers (Register 27-5) configure the functions of the port pins.

The following LCDSEn registers are available:

- LCDSE0 SE<7:0>

- LCDSE1 SE<15:8>

Once the module is initialized for the LCD panel, the individual bits of the LCDDATAn registers are cleared/set to represent a clear/dark pixel, respectively:

- LCDDATA0 SEG<7:0>COM0

- LCDDATA1 SEG<15:8>COM0

- LCDDATA3 SEG<7:0>COM1

- LCDDATA4 SEG<15:8>COM1

- LCDDATA6 SEG<7:0>COM2

- LCDDATA7 SEG<15:8>COM2

- LCDDATA9 SEG<7:0>COM3

- LCDDATA10 SEG<15:8>COM3

As an example, LCDDATAn is detailed in Register 27-6.

Once the module is configured, the LCDEN bit of the LCDCON register is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN bit of the LCDCON register.

### TABLE 30-12: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |          |                                   |                |   |     |    |            |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|----------------|---|-----|----|------------|--|--|--|

| Param.<br>No.                                                                                                                              | Symbol   | Characteristic                    | Characteristic |   |     |    | Conditions |  |  |  |

| US120                                                                                                                                      | TCKH2DTV | SYNC XMIT (Master and Slave)      | 3.0-5.5V       | _ | 80  | ns |            |  |  |  |

|                                                                                                                                            |          | Clock high to data-out valid      | 1.8-5.5V       | _ | 100 | ns |            |  |  |  |

| US121                                                                                                                                      | TCKRF    | Clock out rise time and fall time | 3.0-5.5V       | _ | 45  | ns |            |  |  |  |

|                                                                                                                                            |          | (Master mode)                     | 1.8-5.5V       | _ | 50  | ns |            |  |  |  |

| US122                                                                                                                                      | TDTRF    | Data-out rise time and fall time  | 3.0-5.5V       | _ | 45  | ns |            |  |  |  |

|                                                                                                                                            |          |                                   | 1.8-5.5V       | _ | 50  | ns |            |  |  |  |

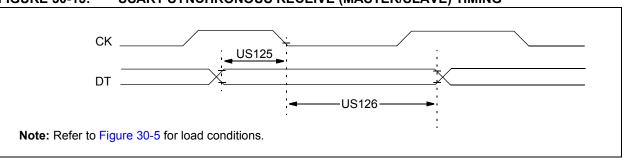

# FIGURE 30-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### **TABLE 30-13: USART SYNCHRONOUS RECEIVE REQUIREMENTS**

|               | Standard Operating Conditions (unless otherwise stated) Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |                                                                  |      |      |       |            |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Symbol                                                                                                                                     | Characteristic                                                   | Min. | Max. | Units | Conditions |  |  |  |  |

| US125         | TDTV2CKL                                                                                                                                   | SYNC RCV (Master and Slave) Data-hold before CK ↓ (DT hold time) | 10   | _    | ns    |            |  |  |  |  |

| US126         | TCKL2DTL                                                                                                                                   | Data-hold after CK ↓ (DT hold time)                              | 15   | _    | ns    |            |  |  |  |  |

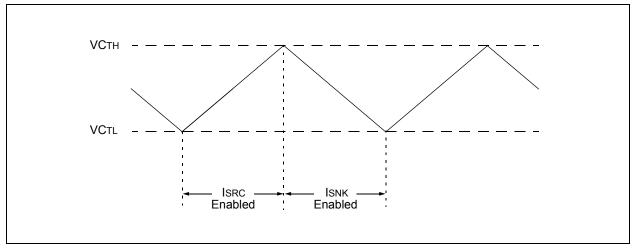

**TABLE 30-17: CAP SENSE OSCILLATOR SPECIFICATIONS**

| Param.<br>No. | Symbol | Characteristic |               | Min. | Typ†       | Max. | Units    | Conditions |

|---------------|--------|----------------|---------------|------|------------|------|----------|------------|

| CS01*         | ISRC   | Current Source | High          | _    | -8         | _    | μΑ       |            |

|               |        |                | Medium        | _    | -1.5       | _    | μА       |            |

|               |        |                | Low           | _    | -0.3       | _    | μА       |            |

| CS02*         | Isnk   | Current Sink   | High          | _    | 7.5        | _    | μΑ       |            |

|               |        |                | Medium        | _    | 1.5        | _    | μΑ       |            |

|               |        |                | Low           | _    | 0.25       | _    | μА       |            |

| CS03*         | VСтн   | Cap Threshold  |               | _    | 0.8        | _    | mV       |            |

| CS04*         | VCTL   | Cap Threshold  |               | _    | 0.4        | _    | mV       |            |

| CS05*         | VCHYST | Cap Hysteresis | High          | _    | 525        | _    | mV       |            |

|               |        | (VCTH-VCTL)    | Medium<br>Low | _    | 375<br>300 | _    | mV<br>mV |            |

<sup>\*</sup> These parameters are characterized but not tested.

FIGURE 30-22: CAP SENSE OSCILLATOR

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

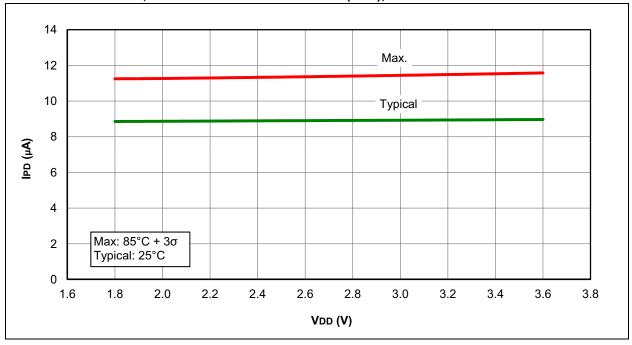

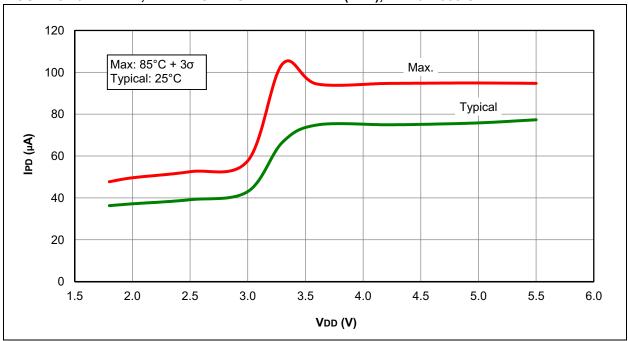

FIGURE 31-34: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC16F1933 ONLY

# 32.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit™ 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 32.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 32.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>TM</sup> and dsPICDEM<sup>TM</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, Keeloq® security ICs, CAN, IrDA®, PowerSmart battery management, Seevaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou

Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka

Tel: 81-66-152-7160 Fax: 81-66-152-9310

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-330-9305

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351

Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/11