Welcome to E-XFL.COM

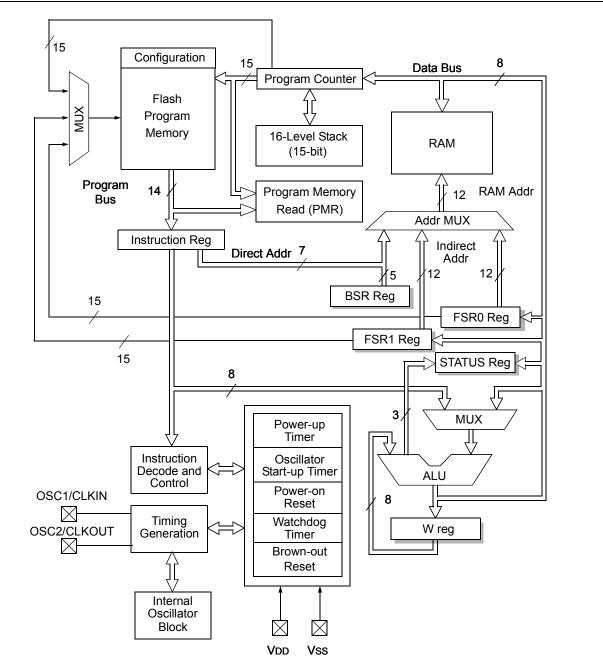

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1933-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Peripheral Features (Continued):

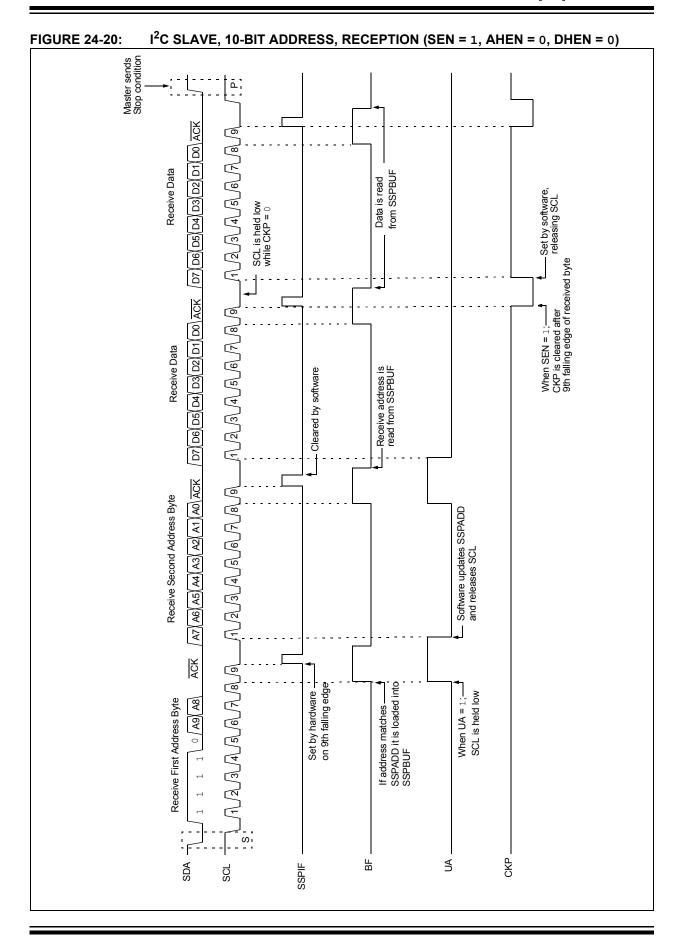

- Master Synchronous Serial Port (MSSP) with SPI and I<sup>2</sup>C<sup>™</sup> with:

- 7-bit address masking

- SMBus/PMBus<sup>™</sup> compatibility

- Auto-wake-up on start

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)

- RS-232, RS-485 and LIN compatible

- Auto-Baud Detect

- SR Latch (555 Timer):

- Multiple Set/Reset input options

- Emulates 555 Timer applications

- 2 Comparators:

- Rail-to-rail inputs/outputs

- Power mode control

- Software enable hysteresis

- Voltage Reference module:

- Fixed Voltage Reference (FVR) with 1.024V, 2.048V and 4.096V output levels

- 5-bit rail-to-rail resistive DAC with positive and negative reference selection

### PIC16(L)F193X/194X Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | Data SRAM<br>(bytes) | ا/O's <sup>(2)</sup> | 10-bit ADC (ch) | CapSense (ch) | Comparators | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C <sup>TM</sup> /SPI) | ECCP | ССР | LCD<br>(Com/Seg/Total) | Debug <sup>(1)</sup> | ХГР |

|---------------|------------------|---------------------------------|------------------------|----------------------|----------------------|-----------------|---------------|-------------|----------------------|--------|--------------------------------------------|------|-----|------------------------|----------------------|-----|

| PIC16(L)F1933 | (1)              | 4096                            | 256                    | 256                  | 25                   | 11              | 8             | 2           | 4/1                  | 1      | 1                                          | 3    | 2   | 4/16/60 <sup>(3)</sup> | I/H                  | Y   |

| PIC16(L)F1934 | (2)              | 4096                            | 256                    | 256                  | 36                   | 14              | 16            | 2           | 4/1                  | 1      | 1                                          | 3    | 2   | 4/24/96                | I/H                  | Y   |

| PIC16(L)F1936 | (2)              | 8192                            | 256                    | 512                  | 25                   | 11              | 8             | 2           | 4/1                  | 1      | 1                                          | 3    | 2   | 4/16/60 <sup>(3)</sup> | I/H                  | Y   |

| PIC16(L)F1937 | (2)              | 8192                            | 256                    | 512                  | 36                   | 14              | 16            | 2           | 4/1                  | 1      | 1                                          | 3    | 2   | 4/24/96                | I/H                  | Y   |

| PIC16(L)F1938 | (3)              | 16384                           | 256                    | 1024                 | 25                   | 11              | 8             | 2           | 4/1                  | 1      | 1                                          | 3    | 2   | 4/16/60 <sup>(3)</sup> | I/H                  | Y   |

| PIC16(L)F1939 | (3)              | 16384                           | 256                    | 1024                 | 36                   | 14              | 16            | 2           | 4/1                  | 1      | 1                                          | 3    | 2   | 4/24/96                | I/H                  | Y   |

| PIC16(L)F1946 | (4)              | 8192                            | 256                    | 512                  | 54                   | 17              | 17            | 3           | 4/1                  | 2      | 2                                          | 3    | 2   | 4/46/184               | I                    | Y   |

| PIC16(L)F1947 | (4)              | 16384                           | 256                    | 1024                 | 54                   | 17              | 17            | 3           | 4/1                  | 2      | 2                                          | 3    | 2   | 4/46/184               | I                    | Y   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

- **2:** One pin is input-only.

- **3:** COM3 and SEG15 share the same physical pin, therefore SEG15 is not available when using 1/4 multiplex displays.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41575 PIC16(L)F1933 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- 2: DS41364 PIC16(L)F1934/6/7 Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers.

- 3: DS41574 PIC16(L)F1938/9 Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers.

- 4: DS41414 PIC16(L)F1946/1947 Data Sheet, 64-Pin Flash, 8-bit Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### 3.3 Register Definitions: Status

**REGISTER 3-1:** STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

**Note 1:** The <u>C</u> and <u>DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

| U-0              | U-0                                                                 | U-0             | R-1/q | R-1/q R/W-0/u                                         |   | R/W-0/u           | R/W-0/u          |  |  |  |

|------------------|---------------------------------------------------------------------|-----------------|-------|-------------------------------------------------------|---|-------------------|------------------|--|--|--|

| —                | _                                                                   | _               | TO    | PD                                                    | Z | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |

| bit 7            |                                                                     |                 |       |                                                       |   |                   | bit 0            |  |  |  |

|                  |                                                                     |                 |       |                                                       |   |                   |                  |  |  |  |

| Legend:          |                                                                     |                 |       |                                                       |   |                   |                  |  |  |  |

| R = Readable b   | oit                                                                 | W = Writable I  | bit   | U = Unimplemented bit, read as '0'                    |   |                   |                  |  |  |  |

| u = Bit is uncha | anged                                                               | x = Bit is unkn | iown  | -n/n = Value at POR and BOR/Value at all other Resets |   |                   |                  |  |  |  |

| '1' = Bit is set | 1' = Bit is set '0' = Bit is cleared q = Value depends on condition |                 |       |                                                       |   |                   |                  |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

| Address                | Name    | Bit 7                                                    | Bit 6                        | Bit 5          | Bit 4         | Bit 3        | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|----------------------------------------------------------|------------------------------|----------------|---------------|--------------|-------------|-------|-------|----------------------|---------------------------------|

| Bank 4                 |         |                                                          |                              |                |               |              |             |       |       |                      |                                 |

| 200h <sup>(2)</sup>    | INDF0   | 0                                                        | this location ical register) | uses contents  | s of FSR0H/F  | SR0L to addr | ess data me | mory  |       | XXXX XXXX            | **** ****                       |

| 201h <sup>(2)</sup>    | INDF1   |                                                          | this location ical register) | uses contents  | s of FSR1H/F  | SR1L to addr | ess data me | mory  |       | XXXX XXXX            | **** ****                       |

| 202h <sup>(2)</sup>    | PCL     | Program C                                                | ounter (PC) L                | east Significa | nt Byte       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 203h <sup>(2)</sup>    | STATUS  | _                                                        | _                            | _              | TO            | PD           | Z           | DC    | С     | 1 1000               | q quuu                          |

| 204h <sup>(2)</sup>    | FSR0L   | Indirect Dat                                             | ta Memory Ac                 | dress 0 Low    | Pointer       |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 205h <sup>(2)</sup>    | FSR0H   | Indirect Dat                                             | ta Memory Ac                 | dress 0 High   | Pointer       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 206h <sup>(2)</sup>    | FSR1L   | Indirect Dat                                             | ta Memory Ac                 | dress 1 Low    | Pointer       |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 207h <sup>(2)</sup>    | FSR1H   | Indirect Dat                                             | ta Memory Ac                 | dress 1 High   | Pointer       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 208h <sup>(2)</sup>    | BSR     | _                                                        | _                            | _              |               |              | BSR<4:0>    |       |       | 0 0000               | 0 0000                          |

| 209h <sup>(2)</sup>    | WREG    | Working Re                                               | Working Register             |                |               |              |             |       |       |                      |                                 |

| 20Ah <sup>(1, 2)</sup> | PCLATH  | Write Buffer for the upper 7 bits of the Program Counter |                              |                |               |              |             |       |       |                      | -000 0000                       |

| 20Bh <sup>(2)</sup>    | INTCON  | GIE                                                      | PEIE                         | TMR0IE         | INTE          | IOCIE        | TMR0IF      | INTF  | IOCIF | 0000 0000            | 0000 0000                       |

| 20Ch                   | _       | Unimpleme                                                | Unimplemented                |                |               |              |             |       |       |                      |                                 |

| 20Dh                   | WPUB    | WPUB7                                                    | WPUB6                        | WPUB5          | WPUB4         | WPUB3        | WPUB2       | WPUB1 | WPUB0 | 1111 1111            | 1111 1111                       |

| 20Eh                   | _       | Unimpleme                                                | nted                         |                |               |              |             |       |       | _                    | _                               |

| 20Fh                   | _       | Unimpleme                                                | ented                        |                |               |              |             |       |       | _                    | _                               |

| 210h                   | WPUE    | _                                                        | _                            | _              | _             | WPUE3        | _           | _     | _     | 1                    | 1                               |

| 211h                   | SSPBUF  | Synchrono                                                | us Serial Port               | Receive Buff   | er/Transmit R | Register     |             |       |       | XXXX XXXX            | uuuu uuuu                       |

| 212h                   | SSPADD  |                                                          |                              |                | ADD<          | :7:0>        |             |       |       | 0000 0000            | 0000 0000                       |

| 213h                   | SSPMSK  |                                                          |                              |                | MSK<          | :7:0>        |             |       |       | 1111 1111            | 1111 1111                       |

| 214h                   | SSPSTAT | SMP                                                      | CKE                          | D/A            | Р             | S            | R/W         | UA    | BF    | 0000 0000            | 0000 0000                       |

| 215h                   | SSPCON1 | WCOL                                                     | SSPOV                        | SSPEN          | СКР           |              | SSPM        | <3:0> |       | 0000 0000            | 0000 0000                       |

| 216h                   | SSPCON2 | GCEN                                                     | ACKSTAT                      | ACKDT          | ACKEN         | RCEN         | PEN         | RSEN  | SEN   | 0000 0000            | 0000 0000                       |

| 217h                   | SSPCON3 | ACKTIM                                                   | PCIE                         | SCIE           | BOEN          | SDAHT        | SBCDE       | AHEN  | DHEN  | 0000 0000            | 0000 0000                       |

| 218h                   | _       | Unimpleme                                                | nted                         |                |               |              | •           |       | •     | _                    | _                               |

| 219h                   | _       | Unimpleme                                                | ented                        |                |               |              |             |       |       | _                    | _                               |

| 21Ah                   | —       | Unimpleme                                                | nted                         |                |               |              |             |       |       | _                    | _                               |

| 21Bh                   | —       | Unimpleme                                                | ented                        |                |               |              |             |       |       | _                    | _                               |

| 21Ch                   | —       | Unimpleme                                                | ented                        |                |               |              |             |       |       | _                    | _                               |

| 21Dh                   | —       | Unimpleme                                                | ented                        |                |               |              |             |       |       | _                    | _                               |

| 21Eh                   | —       | Unimpleme                                                | nted                         |                |               |              |             |       |       | _                    | _                               |

| 21Fh                   |         | Unimplemented                                            |                              |                |               |              |             |       |       | _                    | _                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-9**:

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter. Note 1: 2:

These registers can be addressed from any bank.

3: Unimplemented, read as '1'.

#### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

#### 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables in Section 30.0 "Electrical Specifications".

#### 7.6.4 PIR1 REGISTER

#### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0              | ) R/W-0/0                             | R-0/0                        | R-0/0           | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|----------------------|---------------------------------------|------------------------------|-----------------|-------------------|------------------|------------------|-------------|

| TMR1GI               | F ADIF                                | RCIF                         | TXIF            | SSPIF             | CCP1IF           | TMR2IF           | TMR1IF      |

| bit 7                |                                       |                              |                 |                   |                  | •                | bit (       |

|                      |                                       |                              |                 |                   |                  |                  |             |

| Legend:<br>R = Reada | ble bit                               | W = Writable                 | hit             | II – I Inimpler   | nented bit, read | 1 as 'O'         |             |

| u = Bit is u         |                                       | x = Bit is unk               |                 |                   |                  | R/Value at all c | thar Pasata |

| '1' = Bit is s       | •                                     | '0' = Bit is cle             |                 |                   | at FOR and BO    |                  |             |

| 1 - Dit 13 (         | 501                                   |                              |                 |                   |                  |                  |             |

| bit 7                | TMR1GIF: ⊤                            | imer1 Gate Inte              | errupt Flag bit |                   |                  |                  |             |

|                      | 1 = Interrupt                         |                              |                 |                   |                  |                  |             |

|                      | -                                     | is not pending               |                 |                   |                  |                  |             |

| bit 6                |                                       | onverter Interru             | upt Flag bit    |                   |                  |                  |             |

|                      | 1 = Interrupt<br>0 = Interrupt        | is penaing<br>is not pending |                 |                   |                  |                  |             |

| bit 5                |                                       | T Receive Inte               | rrupt Flag bit  |                   |                  |                  |             |

|                      | 1 = Interrupt                         |                              |                 |                   |                  |                  |             |

|                      | 0 = Interrupt                         | is not pending               |                 |                   |                  |                  |             |

| bit 4                |                                       | T Transmit Inte              | rrupt Flag bit  |                   |                  |                  |             |

|                      | 1 = Interrupt                         | is pending<br>is not pending |                 |                   |                  |                  |             |

| bit 3                | -                                     |                              | Port (MSSP)     | Interrupt Flag b  | sit              |                  |             |

| DIL J                | 1 = Interrupt                         |                              |                 | interrupt i lag i | Л                |                  |             |

|                      |                                       | is not pending               |                 |                   |                  |                  |             |

| bit 2                | CCP1IF: CC                            | P1 Interrupt Fla             | ag bit          |                   |                  |                  |             |

|                      | 1 = Interrupt                         |                              |                 |                   |                  |                  |             |

|                      | -                                     | is not pending               |                 |                   |                  |                  |             |

| bit 1                |                                       | er2 to PR2 Int               | errupt Flag bit |                   |                  |                  |             |

|                      | 1 = Interrupt                         | is pending<br>is not pending |                 |                   |                  |                  |             |

| bit 0                | -                                     | er1 Overflow I               | nterrunt Elan k | hit               |                  |                  |             |

| bit o                | 1 = Interrupt                         |                              | incirupt ridg i |                   |                  |                  |             |

|                      |                                       | is not pending               |                 |                   |                  |                  |             |

| Note:                | Interrupt flag bits a                 | are set when ar              | n interrupt     |                   |                  |                  |             |

|                      | condition occurs,                     |                              |                 |                   |                  |                  |             |

|                      | its corresponding<br>Enable bit, GIE, |                              |                 |                   |                  |                  |             |

|                      | User software                         | should ens                   |                 |                   |                  |                  |             |

|                      | appropriate interru                   | pt flag bits are             |                 |                   |                  |                  |             |

|                      | to enabling an inte                   | errupt.                      |                 |                   |                  |                  |             |

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4:TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                        |

|-------|---------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                           |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |

#### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see Section 18.4.1 "Comparator Output Synchronization".

#### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see Section 18.4.1 "Comparator Output Synchronization".

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |  |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |  |  |  |  |  |

#### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 21-6 for timing details.

#### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

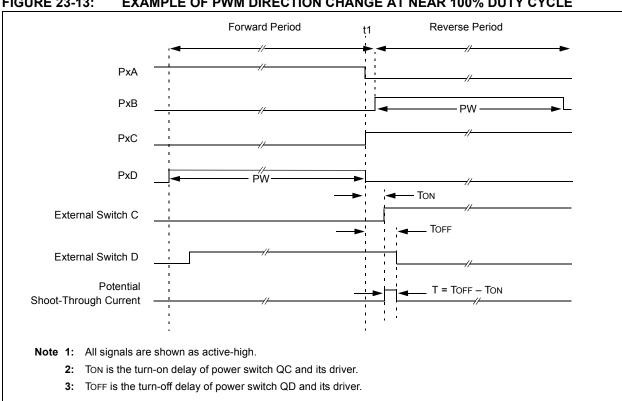

#### 23.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains three Enhanced Capture/Compare/PWM modules (ECCP1, ECCP2, and ECCP3) and two standard Capture/Compare/PWM modules (CCP4 and CCP5).

The Capture and Compare functions are identical for all five CCP modules (ECCP1, ECCP2, ECCP3, CCP4, and CCP5). The only differences between CCP modules are in the Pulse-Width Modulation (PWM) function. The standard PWM function is identical in modules CCP4 and CCP5. In CCP modules ECCP1, ECCP2 and ECCP3, the Enhanced PWM function has slight variations from one another. Full-Bridge ECCP modules have four available I/O pins while Half-Bridge ECCP modules only have two available I/O pins. See Table 23-1 for more information.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to ECCP1, ECCP2, ECCP3, CCP4 and CCP5. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

| TABLE 23-1: | <b>PWM RESOURCES</b> |

|-------------|----------------------|

|             |                      |

| Device Name   | ECCP1                       | ECCP2                       | ECCP3                       | CCP4         | CCP5         |

|---------------|-----------------------------|-----------------------------|-----------------------------|--------------|--------------|

| PIC16(L)F1933 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM | Standard PWM |

#### FIGURE 23-13: **EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE**

#### 25.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See Section 5.2.2 "Internal Clock Sources" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section 25.4.1 "Auto-Baud Detect"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |            |                             |                |            |                             |                    |            |                             |  |  |

|--------|-------------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Foso           | : = 20.00  | 0 MHz                       | Foso           | : = 18.43  | 2 MHz                       | Fosc = 11.0592 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    |                   |                               |                             | _              |            |                             | _              |            | _                           | _                  |            |                             |  |  |

| 1200   | —                 |                               | —                           | 1221           | 1.73       | 255                         | 1200           | 0.00       | 239                         | 1200               | 0.00       | 143                         |  |  |

| 2400   | 2404              | 0.16                          | 207                         | 2404           | 0.16       | 129                         | 2400           | 0.00       | 119                         | 2400               | 0.00       | 71                          |  |  |

| 9600   | 9615              | 0.16                          | 51                          | 9470           | -1.36      | 32                          | 9600           | 0.00       | 29                          | 9600               | 0.00       | 17                          |  |  |

| 10417  | 10417             | 0.00                          | 47                          | 10417          | 0.00       | 29                          | 10286          | -1.26      | 27                          | 10165              | -2.42      | 16                          |  |  |

| 19.2k  | 19.23k            | 0.16                          | 25                          | 19.53k         | 1.73       | 15                          | 19.20k         | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |  |  |

| 57.6k  | 55.55k            | -3.55                         | 3                           | —              | —          | _                           | 57.60k         | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |  |  |

| 115.2k | —                 | _                             | _                           | —              | _          | _                           | —              | _          | _                           | —                  |            | _                           |  |  |

#### TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                  |            |                             |                |            |                             |                  |            |                             |  |  |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Foso           | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |  |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | _                | _                             | _                           | 300              | 0.16       | 207                         | 300            | 0.00       | 191                         | 300              | 0.16       | 51                          |  |  |  |

| 1200   | 1202             | 0.16                          | 103                         | 1202             | 0.16       | 51                          | 1200           | 0.00       | 47                          | 1202             | 0.16       | 12                          |  |  |  |

| 2400   | 2404             | 0.16                          | 51                          | 2404             | 0.16       | 25                          | 2400           | 0.00       | 23                          | —                | _          | —                           |  |  |  |

| 9600   | 9615             | 0.16                          | 12                          | _                | _          | _                           | 9600           | 0.00       | 5                           | —                | _          | —                           |  |  |  |

| 10417  | 10417            | 0.00                          | 11                          | 10417            | 0.00       | 5                           | _              | _          | _                           | —                | _          | _                           |  |  |  |

| 19.2k  | _                | _                             | _                           | _                | _          | _                           | 19.20k         | 0.00       | 2                           | _                | _          | _                           |  |  |  |

| 57.6k  | —                | _                             | _                           | —                | _          | —                           | 57.60k         | 0.00       | 0                           | —                | _          | _                           |  |  |  |

| 115.2k |                  | _                             | —                           | —                | _          | —                           | —              | _          | —                           | —                | _          | _                           |  |  |  |

|              | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 32.000 MHz             |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

|              | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300          | —                             | —          | —                           | _                 |            | —                           |                   | —          | —                           |                    |            |                             |

| 1200         | —                             | —          | —                           | —                 |            | —                           | —                 | —          | —                           | —                  | —          | —                           |

| 2400         | _                             | _          | _                           | —                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |

| 9600         | 9615                          | 0.16       | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417        | 10417                         | 0.00       | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k        | 19.23k                        | 0.16       | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k        | 57.14k                        | -0.79      | 34                          | 56.82k            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k       | 117.64k                       | 2.12       | 16                          | 113.64k           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

#### 27.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 3 LCD Segment Enable registers (LCDSEn)

- Up to 12 LCD data registers (LCDDATAn)

### TABLE 27-1: LCD SEGMENT AND DATA REGISTERS

|               | # of LCD Registers |      |  |  |  |

|---------------|--------------------|------|--|--|--|

| Device        | Segment<br>Enable  | Data |  |  |  |

| PIC16(L)F1933 | 2                  | 8    |  |  |  |

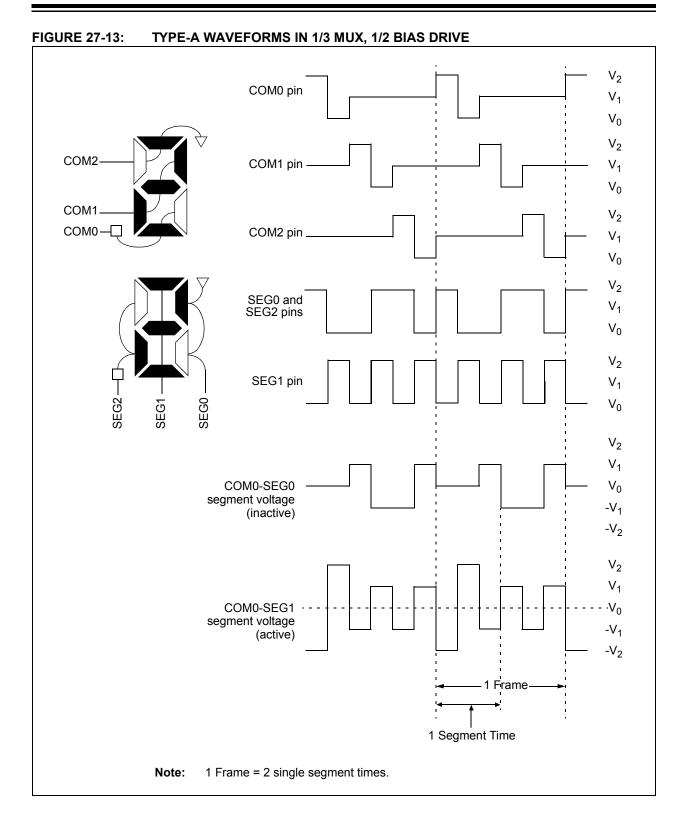

The LCDCON register (Register 27-1) controls the operation of the LCD driver module. The LCDPS register (Register 27-2) configures the LCD clock source prescaler and the type of waveform; Type-A or Type-B. The LCDSEn registers (Register 27-5) configure the functions of the port pins.

The following LCDSEn registers are available:

- LCDSE0 SE<7:0>

- LCDSE1 SE<15:8>

Once the module is initialized for the LCD panel, the individual bits of the LCDDATAn registers are cleared/set to represent a clear/dark pixel, respectively:

- LCDDATA0 SEG<7:0>COM0

- LCDDATA1 SEG<15:8>COM0

- LCDDATA3 SEG<7:0>COM1

- LCDDATA4 SEG<15:8>COM1

- LCDDATA6 SEG<7:0>COM2

- LCDDATA7 SEG<15:8>COM2

- LCDDATA9 SEG<7:0>COM3

- LCDDATA10 SEG<15:8>COM3

As an example, LCDDATAn is detailed in Register 27-6.

Once the module is configured, the LCDEN bit of the LCDCON register is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN bit of the LCDCON register.

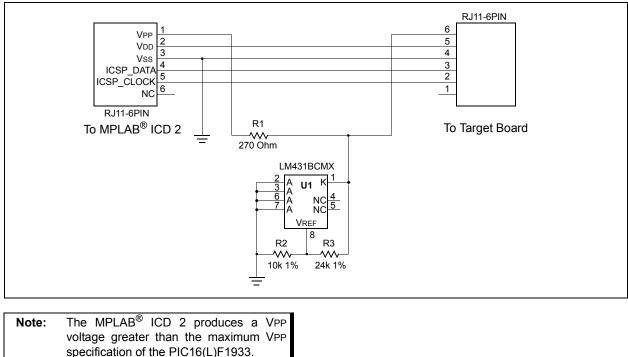

#### 28.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>™</sup> refer to the "PIC16193X/PIC16LF193X Memory Programming Specification" (DS41360A).

#### 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

Some programmers produce VPP greater than VIHH (9.0V), an external circuit is required to limit the VPP voltage. See Figure 28-1 for example circuit.

FIGURE 28-1: VPP LIMITER EXAMPLE CIRCUIT

### FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations<br>13 8 7 6 0                                  |  |

|---------------------------------------------------------------------------------------|--|

| OPCODE d f (FILE #)                                                                   |  |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |  |

| Bit-oriented file register operations                                                 |  |

| OPCODE b (BIT #) f (FILE #)                                                           |  |

| b = 3-bit bit address<br>f = 7-bit file register address                              |  |

| Literal and control operations                                                        |  |

| General                                                                               |  |

|                                                                                       |  |

| OPCODE k (literal)                                                                    |  |

| k = 8-bit immediate value                                                             |  |

| CALL and GOTO instructions only                                                       |  |

| 13 11 10 0                                                                            |  |

| OPCODE k (literal)                                                                    |  |

| k = 11-bit immediate value                                                            |  |

| MOVLP instruction only<br>13 7 6 0                                                    |  |

| OPCODE k (literal)                                                                    |  |

| k = 7-bit immediate value                                                             |  |

|                                                                                       |  |

| MOVLB instruction only                                                                |  |

| 13 5 4 0<br>OPCODE k (literal)                                                        |  |

| k = 5-bit immediate value                                                             |  |

|                                                                                       |  |

| BRA instruction only<br>13 9 8 0                                                      |  |

| OPCODE k (literal)                                                                    |  |

| k = 9-bit immediate value                                                             |  |

|                                                                                       |  |

| FSR Offset instructions                                                               |  |

| 13 7 6 5 0<br>OPCODE n k (literal)                                                    |  |

|                                                                                       |  |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |  |

| FSR Increment instructions                                                            |  |

| 13 3 2 1 0<br>OPCODE n m (mode)                                                       |  |

| n = appropriate FSR<br>m = 2-bit mode value                                           |  |

|                                                                                       |  |

| OPCODE only                                                                           |  |

| 13 0<br>OPCODE                                                                        |  |

|                                                                                       |  |

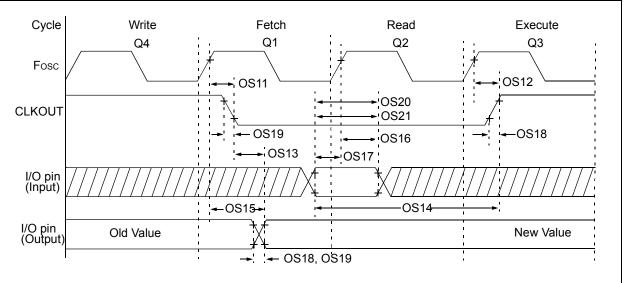

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |          |                                                              |               |      |      |       |                |

|----------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|---------------|------|------|-------|----------------|

| Param<br>No.                                                                                                   | Sym.     | Characteristic                                               | Min.          | Тур† | Max. | Units | Conditions     |

| OS11                                                                                                           | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              | —             | _    | 70   | ns    | VDD = 3.3-5.0V |

| OS12                                                                                                           | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                              | —             | _    | 72   | ns    | VDD = 3.3-5.0V |

| OS13                                                                                                           | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | —             | _    | 20   | ns    |                |

| OS14                                                                                                           | TioV2ckH | Port input valid before CLKOUT↑ <sup>(1)</sup>               | Tosc + 200 ns | _    | _    | ns    |                |

| OS15                                                                                                           | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50   | 70*  | ns    | VDD = 3.3-5.0V |

| OS16                                                                                                           | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            |      |      | ns    | VDD = 3.3-5.0V |

| OS17                                                                                                           | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            |      |      | ns    |                |

| OS18                                                                                                           | TioR     | Port output rise time                                        | _             | 40   | 72   | ns    | VDD = 1.8V     |

|                                                                                                                |          |                                                              | —             | 15   | 32   |       | VDD = 3.3-5.0V |

| OS19                                                                                                           | TioF     | Port output fall time                                        | —             | 28   | 55   | ns    | VDD = 1.8V     |

|                                                                                                                |          |                                                              | —             | 15   | 30   |       | VDD = 3.3-5.0V |

| OS20*                                                                                                          | Tinp     | INT pin input high or low time                               | 25            | —    | —    | ns    |                |

| OS21*                                                                                                          | Tioc     | Interrupt-on-change new input level time                     | 25            | _    | _    | ns    |                |

| * These parameters are characterized but not tested.                                                           |          |                                                              |               |      |      |       |                |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

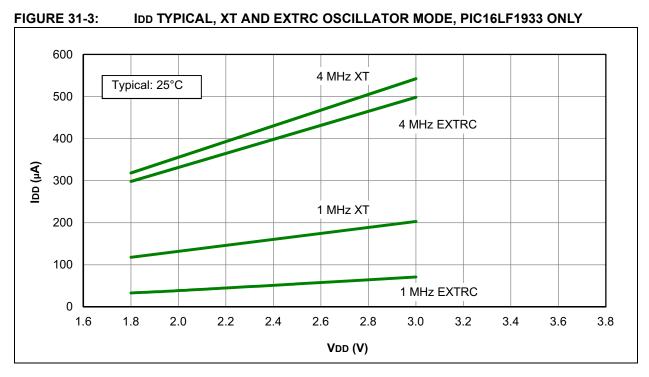

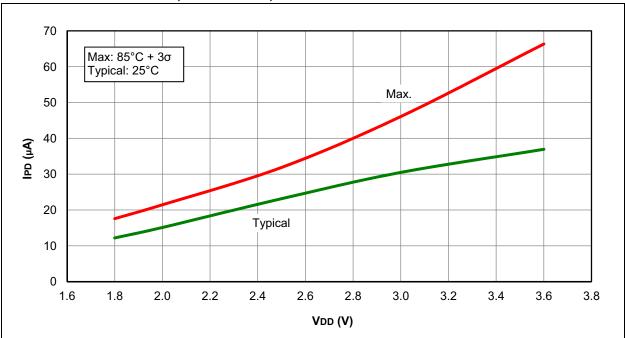

FIGURE 31-43: IPD, CAPACITIVE SENSING (CPS) MODULE, HIGH-CURRENT RANGE, CPSRM = 0, CPSRNG = 11, PIC16LF1933 ONLY

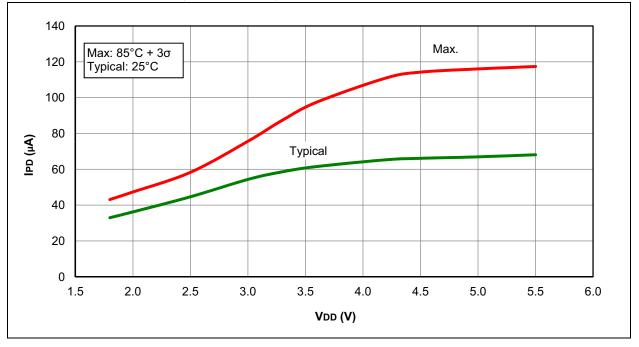

FIGURE 31-44: IPD, CAPACITIVE SENSING (CPS) MODULE, HIGH-CURRENT RANGE, CPSRM = 0, CPSRNG = 11, PIC16F1933 ONLY

NOTES: