Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1933-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                | Name     | Bit 7                                                                                                         | Bit 6                                | Bit 5          | Bit 4           | Bit 3         | Bit 2        | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|----------|---------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-----------------|---------------|--------------|---------|-----------|----------------------|---------------------------------|

| Bank 5                 |          |                                                                                                               |                                      |                |                 |               |              |         |           |                      |                                 |

| 280h <sup>(2)</sup>    | INDF0    | 0F0 Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                                      |                |                 |               |              |         |           |                      | XXXX XXXX                       |

| 281h <sup>(2)</sup>    | INDF1    |                                                                                                               | this location ical register)         | uses contents  | s of FSR1H/F    | SR1L to addre | ess data mer | nory    |           | XXXX XXXX            | XXXX XXXX                       |

| 282h <sup>(2)</sup>    | PCL      | Program Co                                                                                                    | ounter (PC) L                        | east Significa | nt Byte         |               |              |         |           | 0000 0000            | 0000 0000                       |

| 283h <sup>(2)</sup>    | STATUS   | _                                                                                                             | _                                    | _              | TO              | PD            | Z            | DC      | С         | 1 1000               | q quuu                          |

| 284h <sup>(2)</sup>    | FSR0L    | Indirect Dat                                                                                                  | a Memory Ad                          | dress 0 Low    | Pointer         |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 285h <sup>(2)</sup>    | FSR0H    | Indirect Dat                                                                                                  | a Memory Ad                          | dress 0 High   | Pointer         |               |              |         |           | 0000 0000            | 0000 0000                       |

| 286h <sup>(2)</sup>    | FSR1L    | Indirect Dat                                                                                                  | a Memory Ad                          | dress 1 Low    | Pointer         |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(2)</sup>    | FSR1H    | Indirect Dat                                                                                                  | a Memory Ad                          | dress 1 High   | Pointer         |               |              |         |           | 0000 0000            | 0000 0000                       |

| 288h <sup>(2)</sup>    | BSR      | —                                                                                                             | _                                    | —              |                 |               | BSR<4:0>     |         |           | 0 0000               | 0 0000                          |

| 289h <sup>(2)</sup>    | WREG     | Working Re                                                                                                    | egister                              |                |                 |               |              |         |           | 0000 0000            | uuuu uuuu                       |

| 28Ah <sup>(1, 2)</sup> | PCLATH   | _                                                                                                             | Write Buffer                         | for the upper  | 7 bits of the F | rogram Coun   | ter          |         |           | -000 0000            | -000 0000                       |

| 28Bh <sup>(2)</sup>    | INTCON   | GIE                                                                                                           | PEIE                                 | TMR0IE         | INTE            | IOCIE         | TMR0IF       | INTF    | IOCIF     | 0000 0000            | 0000 0000                       |

| 28Ch                   | _        | Unimpleme                                                                                                     | Unimplemented                        |                |                 |               |              |         |           |                      |                                 |

| 28Dh                   | _        | Unimpleme                                                                                                     | Unimplemented                        |                |                 |               |              |         |           |                      |                                 |

| 28Eh                   | _        | Unimpleme                                                                                                     | Unimplemented                        |                |                 |               |              |         |           |                      |                                 |

| 28Fh                   | —        | Unimpleme                                                                                                     | nted                                 |                |                 |               |              |         |           | _                    | _                               |

| 290h                   | _        | Unimpleme                                                                                                     | nted                                 |                |                 |               |              |         |           | _                    | _                               |

| 291h                   | CCPR1L   | Capture/Co                                                                                                    | mpare/PWM                            | Register 1 (L  | SB)             |               |              |         |           | XXXX XXXX            | uuuu uuuu                       |

| 292h                   | CCPR1H   | Capture/Co                                                                                                    | mpare/PWM                            | Register 1 (M  | ISB)            |               |              |         |           | XXXX XXXX            | uuuu uuuu                       |

| 293h                   | CCP1CON  | P1M                                                                                                           | <1:0>                                | DC1E           | <1:0>           |               | CCP1N        | <3:0>   |           | 0000 0000            | 0000 0000                       |

| 294h                   | PWM1CON  | P1RSEN                                                                                                        |                                      |                | F               | P1DC<6:0>     |              |         |           | 0000 0000            | 0000 0000                       |

| 295h                   | CCP1AS   | CCP1ASE                                                                                                       | (                                    | CCP1AS<2:0     | >               | PSS1A         | C<1:0>       | PSS1B   | D<1:0>    | 0000 0000            | 0000 0000                       |

| 296h                   | PSTR1CON | _                                                                                                             | _                                    | _              | STR1SYNC        | STR1D         | STR1C        | STR1B   | STR1A     | 0 0001               | 0 0001                          |

| 297h                   | —        | Unimpleme                                                                                                     | Unimplemented                        |                |                 |               |              |         |           |                      | _                               |

| 298h                   | CCPR2L   | Capture/Co                                                                                                    | Capture/Compare/PWM Register 2 (LSB) |                |                 |               |              |         |           |                      | uuuu uuuu                       |

| 299h                   | CCPR2H   | Capture/Compare/PWM Register 2 (MSB)                                                                          |                                      |                |                 |               |              |         |           | XXXX XXXX            | uuuu uuuu                       |

| 29Ah                   | CCP2CON  | P2M<1:0> DC2B<1:0> CCP2M<3:0>                                                                                 |                                      |                |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 29Bh                   | PWM2CON  | P2RSEN                                                                                                        | N P2DC<6:0>                          |                |                 |               |              |         |           | 0000 0000            | 0000 0000                       |

| 29Ch                   | CCP2AS   | CCP2ASE                                                                                                       | (                                    |                |                 |               |              |         | 0000 0000 | 0000 0000            |                                 |

| 29Dh                   | PSTR2CON | —                                                                                                             | _                                    | —              | STR2SYNC        | STR2D         | STR2C        | STR2B   | STR2A     | 0 0001               | 0 0001                          |

| 29Eh                   | CCPTMRS0 | C4TSEL1                                                                                                       | C4TSEL0                              | C3TSEL1        | C3TSEL0         | C2TSEL1       | C2TSEL0      | C1TSEL1 | C1TSEL0   | 0000 0000            | 0000 0000                       |

| 29Fh                   | CCPTMRS1 |                                                                                                               |                                      | _              |                 |               |              | C5TSE   | L<1:0>    | 00                   | 00                              |

#### TABLE 3-9 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

3: Unimplemented, read as '1'.

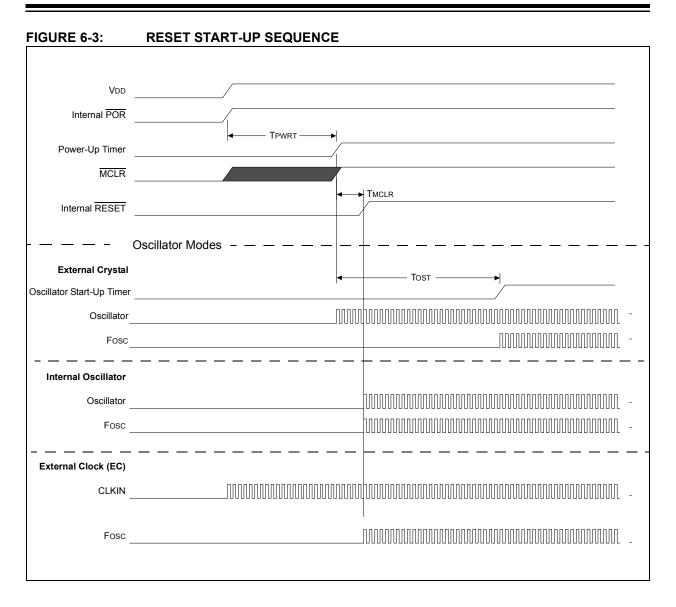

## 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

#### 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

Note: When FSCM is enabled, Two-Speed Start-Up will automatically be enabled.

| TABLE 5-1: | OSCILLATOR SWITCHING DELAYS |

|------------|-----------------------------|

|------------|-----------------------------|

| Switch From                                                         | Switch To                                                                     | Frequency                                       | Oscillator Delay        |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------|-------------------------|

| Sleep/POR                                                           | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | 2 cycles                |

| Sleep/POR                                                           | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                |

| LFINTOSC                                                            | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each         |

| Sleep/POR Timer1 Osci<br>LP, XT, HS <sup>(1</sup>                   |                                                                               | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST) |

| Any clock source MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> |                                                                               | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)          |

| Any clock source                                                    | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each         |

| Any clock source                                                    | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST) |

| PLL inactive PLL active                                             |                                                                               | 16-32 MHz                                       | 2 ms (approx.)          |

Note 1: PLL inactive.

## 9.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Timer1 oscillator

- CapSense oscillator

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- · External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or VSS externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to Section 6.11 "Determining the Cause of a Reset".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

|                      | LE 11-5:    |                    |                                                            |

|----------------------|-------------|--------------------|------------------------------------------------------------|

|                      |             | tine assumes the f |                                                            |

|                      | -           |                    | ded, starting at the address in DATA_ADDR                  |

|                      |             |                    | ten is made up of two adjacent bytes in DATA_ADDR,         |

|                      |             | ittle endian forma |                                                            |

|                      |             | -                  | e least significant bits = 000) is loaded in ADDRH:ADDRL   |

| ; 4. Al              | DDRH and AI | DDRL are located 1 | in shared data memory 0x70 - 0x7F (common RAM)             |

| ,                    | BCF         | INTCON, GIE        | ; Disable ints so required sequences will execute properly |

|                      | BANKSEL     | EEADRH             | ; Bank 3                                                   |

|                      | MOVF        | ADDRH,W            | ; Load initial address                                     |

|                      | MOVWF       | EEADRH             | ;                                                          |

|                      | MOVF        | ADDRL,W            | ;                                                          |

|                      | MOVWF       | EEADRL             | ;                                                          |

|                      | MOVLW       | LOW DATA ADDR      | ; Load initial data address                                |

|                      | MOVWF       | FSROL              | ;                                                          |

|                      | MOVLW       | HIGH DATA_ADDR     | ; Load initial data address                                |

|                      | MOVWF       | FSROH              | ;                                                          |

|                      | BSF         |                    | ; Point to program memory                                  |

|                      | BCF         |                    | ; Not configuration space                                  |

|                      | BSF         |                    | ; Enable writes                                            |

|                      | BSF         | EECON1,LWLO        | ; Only Load Write Latches                                  |

| LOOP                 | MOUTE       |                    |                                                            |

|                      | MOVIW       | FSR0++             | ; Load first data byte into lower                          |

|                      | MOVWF       | EEDATL             | ;                                                          |

|                      | MOVIW       | FSR0++             | ; Load second data byte into upper                         |

|                      | MOVWF       | EEDATH             | ;                                                          |

|                      | MOVF        | EEADRL,W           | ; Check if lower bits of address are '000'                 |

|                      | XORLW       | 0x07               | ; Check if we're on the last of 8 addresses                |

|                      | ANDLW       | 0x07               | ;                                                          |

|                      | BTFSC       | STATUS,Z           | ; Exit if last of eight words,                             |

|                      | GOTO        | START_WRITE        | ;                                                          |

|                      | MOVLW       | 55h                | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2             | ; Write 55h                                                |

| _ 0                  | MOVLW       | 0AAh               | ;                                                          |

| red                  | MOVWF       | EECON2             | ; Write AAh                                                |

| Required<br>Sequence | BSF         | EECON1,WR          | ; Set WR bit to begin write                                |

| Sec                  | NOP         |                    | ; Any instructions here are ignored as processor           |

|                      |             |                    | ; halts to begin write sequence                            |

|                      | NOP         |                    | ; Processor will stop here and wait for write to complete. |

|                      |             |                    | ; After write processor continues with 3rd instruction.    |

|                      | INCF        | EEADRL,F           | ; Still loading latches Increment address                  |

|                      | GOTO        | LOOP               | ; Write next latches                                       |

|                      | ייח ד מני   |                    |                                                            |

| START_V              | BCF         | EECON1,LWLO        | ; No more loading latches - Actually start Flash program   |

|                      | DOI         | LICONT, INIO       | ; memory write                                             |

|                      |             |                    | ,                                                          |

|                      | MOVLW       | 55h                | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2             | ; Write 55h                                                |

| 8 9                  | MOVLW       | 0AAh               | ;                                                          |

| Required<br>Sequence | MOVWF       | EECON2             | ; Write AAh                                                |

| ibe:                 | BSF         | EECON1,WR          | ; Set WR bit to begin write                                |

| ч                    | NOP         |                    | ; Any instructions here are ignored as processor           |

|                      |             |                    | ; halts to begin write sequence                            |

|                      | NOP         |                    | ; Processor will stop here and wait for write complete.    |

|                      |             |                    | ; after write processor continues with 3rd instruction     |

|                      | BCF         | EECON1,WREN        | ; Disable writes                                           |

|                      | BSF         | INTCON, GIE        | ; Enable interrupts                                        |

|                      |             |                    |                                                            |

## 12.5 PORTC Registers

#### 12.5.1 DATA REGISTER

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 12-12). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 12-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

#### 12.5.2 DIRECTION CONTROL

The TRISC register (Register 12-12) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.5.3 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

| Pin Name | Function Priority <sup>(1)</sup>                             |

|----------|--------------------------------------------------------------|

| RC0      | T1OSO (Timer1 Oscillator)<br>CCP2/P2B<br>RC0                 |

| RC1      | T1OSI (Timer1 Oscillator)<br>CCP2/P2A<br>RC1                 |

| RC2      | SEG3 (LCD)<br>CCP1/P1A<br>RC2                                |

| RC3      | SEG6 (LCD)<br>SCL (MSSP)<br>SCK (MSSP)<br>RC3                |

| RC4      | SEG11 (LCD)<br>SDA (MSSP)<br>RC4                             |

| RC5      | SEG10 (LCD)<br>SDO (MSSP)<br>RC5                             |

| RC6      | ISEG9 (LCD)<br>TX (EUSART)<br>CK (EUSART)<br>CCP3/P3A<br>RC6 |

| RC7      | SEG8 (LCD)<br>DT (EUSART)<br>CCP3/P3B<br>RC7                 |

#### TABLE 12-7: PORTC OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

## 18.7 Comparator Negative Input Selection

The CxNCH<1:0> bits of the CMxCON0 register direct one of four analog pins to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog     |

|-------|--------------------------------------------|

|       | input, the appropriate bits must be set in |

|       | the ANSEL register and the correspond-     |

|       | ing TRIS bits must also be set to disable  |

|       | the output drivers.                        |

## 18.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference specifications in Section 30.0 "Electrical Specifications" for more details.

## 18.9 Interaction with ECCP Logic

The C1 and C2 comparators can be used as general purpose comparators. Their outputs can be brought out to the C1OUT and C2OUT pins. When the ECCP auto-shutdown is active it can use one or both comparator signals. If auto-restart is also enabled, the comparators can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

Note: When the comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

## 18.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| TADLE 23- |              |                 |                                 |          |           |         |                |         |                     |

|-----------|--------------|-----------------|---------------------------------|----------|-----------|---------|----------------|---------|---------------------|

| Name      | Bit 7        | Bit 6           | Bit 5                           | Bit 4    | Bit 3     | Bit 2   | Bit 1          | Bit 0   | Register<br>on Page |

| CCPxCON   | PxM<         | 1:0> <b>(1)</b> | DCxE                            | 3<1:0>   |           | CCPx    | <b>/</b> <3:0> |         | 214                 |

| CCPxAS    | CCPxASE      | (               | CCPxAS<2:0                      | >        | PSSxA     | .C<1:0> | PSSxB          | D<1:0>  | 216                 |

| CCPTMRS0  | C4TSE        | L<1:0>          | C3TSE                           | EL<1:0>  | C2TSE     | EL<1:0> | C1TSE          | L<1:0>  | 215                 |

| CCPTMRS1  | —            | —               | —                               | —        | _         | —       | C5TSE          | :L<1:0> | 215                 |

| INTCON    | GIE          | PEIE            | TMR0IE                          | INTE     | IOCIE     | TMR0IF  | INTF           | IOCIF   | 82                  |

| PIE1      | TMR1GIE      | ADIE            | RCIE                            | TXIE     | SSPIE     | CCP1IE  | TMR2IE         | TMR1IE  | 83                  |

| PIE2      | OSFIE        | C2IE            | C1IE                            | EEIE     | BCLIE     | LCDIE   | _              | CCP2IE  | 84                  |

| PIE3      | _            | CCP5IE          | CCP4IE                          | CCP3IE   | TMR6IE    | _       | TMR4IE         | —       | 85                  |

| PIR1      | TMR1GIF      | ADIF            | RCIF                            | TXIF     | SSPIF     | CCP1IF  | TMR2IF         | TMR1IF  | 86                  |

| PIR2      | OSFIF        | C2IF            | C1IF                            | EEIF     | BCLIF     | LCDIF   | _              | CCP2IF  | 87                  |

| PIR3      | —            | CCP5IF          | CCP4IF                          | CCP3IF   | TMR6IF    | —       | TMR4IF         | —       | 88                  |

| PRx       | Timer2/4/6 P | Period Registe  | er                              |          |           |         |                |         | 187*                |

| PSTRxCON  | —            | —               | —                               | STRxSYNC | STRxD     | STRxC   | STRxB          | STRxA   | 218                 |

| PWMxCON   | PxRSEN       |                 |                                 |          | PxDC<6:0> |         |                |         | 217                 |

| TxCON     | —            |                 | TxOUTPS<3:0> TMRxON TxCKPS<:0>1 |          |           |         |                |         |                     |

| TMRx      | Timer2/4/6 M | Iodule Regist   | odule Register                  |          |           |         |                |         | 187                 |

| TRISA     | TRISA7       | TRISA6          | TRISA5                          | TRISA4   | TRISA3    | TRISA2  | TRISA1         | TRISA0  | 116                 |

| TRISB     | TRISB7       | TRISB6          | TRISB5                          | TRISB4   | TRISB3    | TRISB2  | TRISB1         | TRISB0  | 121                 |

| TRISC     | TRISC7       | TRISC6          | TRISC5                          | TRISC4   | TRISC3    | TRISC2  | TRISC1         | TRISC0  | 125                 |

#### TABLE 23-10: SUMMARY OF REGISTERS ASSOCIATED WITH ENHANCED PWM

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM.

**Note 1:** Applies to ECCP modules only.

\* Page provides register information.

### 24.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

| Name    | Bit 7       | Bit 6         | Bit 5         | Bit 4             | Bit 3            | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-------------|---------------|---------------|-------------------|------------------|--------|--------|---------|---------------------|

| ANSELA  | —           | _             | ANSA5         | ANSA4             | ANSA3            | ANSA2  | ANSA1  | ANSA0   | 117                 |

| APFCON  | _           | CCP3SEL       | T1GSEL        | P2BSEL            | SRNQSEL C2OUTSEL |        | SSSEL  | CCP2SEL | 114                 |

| INTCON  | GIE         | PEIE          | TMR0IE        | INTE IOCIE TMR0IF |                  | INTF   | IOCIF  | 82      |                     |

| PIE1    | TMR1GIE     | ADIE          | RCIE          | TXIE              | SSP1IE           | CCP1IE | TMR2IE | TMR1IE  | 83                  |

| PIR1    | TMR1GIF     | ADIF          | RCIF          | TXIF              | SSP1IF           | CCP1IF | TMR2IF | TMR1IF  | 86                  |

| SSPBUF  | Synchronous | Serial Port F | Receive Buffe | r/Transmit Re     | egister          |        |        |         | 223*                |

| SSPCON1 | WCOL        | SSPOV         | SSPEN         | CKP               |                  | SSPM   | <3:0>  |         | 268                 |

| SSPCON3 | ACKTIM      | PCIE          | SCIE          | BOEN              | SDAHT            | SBCDE  | AHEN   | DHEN    | 271                 |

| SSPSTAT | SMP         | CKE           | D/A           | Р                 | S                | R/W    | UA     | BF      | 267                 |

| TRISA   | TRISA7      | TRISA6        | TRISA5        | TRISA4            | TRISA3           | TRISA2 | TRISA1 | TRISA0  | 116                 |

| TRISC   | TRISC7      | TRISC6        | TRISC5        | TRISC4            | TRISC3           | TRISB2 | TRISC1 | TRISC0  | 125                 |

#### TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Page provides register information.

### REGISTER 24-2: SSPCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/0        | R/C/HS-0/0                                                                                                                                                                                                      | R/W-0/0                                                                                                           | R/W-0/0                                                                                       | R/W-0/0                                                                                                                      | R/W-0/0                                                      | R/W-0/0                                                              | R/W-0/0                                            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------|

| WCOL              | SSPOV                                                                                                                                                                                                           | SSPEN                                                                                                             | CKP                                                                                           |                                                                                                                              | SSPN                                                         | /<3:0>                                                               |                                                    |

| bit 7             |                                                                                                                                                                                                                 |                                                                                                                   |                                                                                               |                                                                                                                              |                                                              |                                                                      | bit                                                |

|                   |                                                                                                                                                                                                                 |                                                                                                                   |                                                                                               |                                                                                                                              |                                                              |                                                                      |                                                    |

| Legend:           |                                                                                                                                                                                                                 |                                                                                                                   |                                                                                               |                                                                                                                              |                                                              |                                                                      |                                                    |

| R = Readable b    |                                                                                                                                                                                                                 | W = Writable bi                                                                                                   |                                                                                               | •                                                                                                                            | nted bit, read as                                            |                                                                      | <b>.</b> .                                         |

| u = Bit is unchar | nged                                                                                                                                                                                                            | x = Bit is unkno                                                                                                  |                                                                                               |                                                                                                                              |                                                              | /alue at all other F                                                 |                                                    |

| '1' = Bit is set  |                                                                                                                                                                                                                 | '0' = Bit is clear                                                                                                | ed                                                                                            | HS = Bit is set I                                                                                                            | by hardware                                                  | C = User cleare                                                      | d                                                  |

| bit 7             | Master mode:<br>1 = A write to a<br>started<br>0 = No collision                                                                                                                                                 | -                                                                                                                 |                                                                                               | pted while the I <sup>2</sup> C                                                                                              | conditions were                                              | not valid for a tra                                                  | nsmission to b                                     |

|                   | 0 = No collisio                                                                                                                                                                                                 | on                                                                                                                |                                                                                               | ll transmitting the p                                                                                                        | revious word (mu                                             | st be cleared in sof                                                 | tware)                                             |

| bit 6             | $\frac{\text{In SPI mode:}}{1 = \text{A new byte}}$ $\frac{1 = \text{A new byte}}{\text{SSPSR is}}$ only transmition (and tr<br>0 = No overflo<br>$\frac{\text{In } 1^2 \text{C mode:}}{1 = \text{A byte is }}$ | lost. Overflow can<br>mitting data, to av<br>ransmission) is ini<br>w<br>received while th<br>node (must be cl    | e the SSPBUF r<br>n only occur in s<br>oid setting over<br>titated by writing<br>ne SSPBUF re | egister is still holdir<br>Slave mode. In Sla<br>flow. In Master mo<br>g to the SSPBUF re<br>gister is still holdin<br>are). | ve mode, the use<br>de, the overflow b<br>egister (must be o | er must read the S<br>bit is not set since of<br>cleared in software | SPBUF, even if<br>each new rece <sub>l</sub><br>). |

| bit 5             | In both modes,<br>In SPI mode:<br>1 = Enables se<br>0 = Disables se<br>In I <sup>2</sup> C mode:<br>1 = Enables th                                                                                              | erial port and cont<br>serial port and co<br>e serial port and c                                                  | hese pins mus<br>figures SCK, SI<br>nfigures these<br>configures the S                        | t be properly conf<br>DO, SDI and SS as<br>pins as I/O port p<br>DA and SCL pins a<br>pins as I/O port p                     | the source of the<br>ins<br>as the source of t               | e serial port pins <sup>(2)</sup>                                    |                                                    |

| bit 4             | 0 = Idle state for<br>$\frac{\ln l^2C}{SCL}$ so $\frac{1}{1}$ = Enable close                                                                                                                                    | or clock is a high<br>or clock is a low l<br>o <u>ode:</u><br>ontrol<br>ck<br>k low (clock streto<br><u>node:</u> | evel                                                                                          | nsure data setup t                                                                                                           | ime.)                                                        |                                                                      |                                                    |

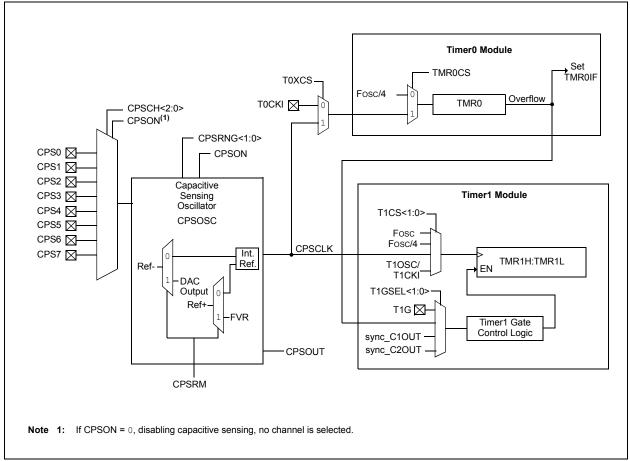

## 26.0 CAPACITIVE SENSING (CPS) MODULE

The Capacitive Sensing (CPS) module allows for an interaction with an end user without a mechanical interface. In a typical application, the CPS module is attached to a pad on a Printed Circuit Board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the CPS module. The CPS module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- · Multiple current ranges

- Multiple voltage reference modes

- Multiple timer resources

- · Software control

- · Operation during Sleep

### FIGURE 26-1: CAPACITIVE SENSING BLOCK DIAGRAM

© 2011-2012 Microchip Technology Inc.

DS41575C-page 331

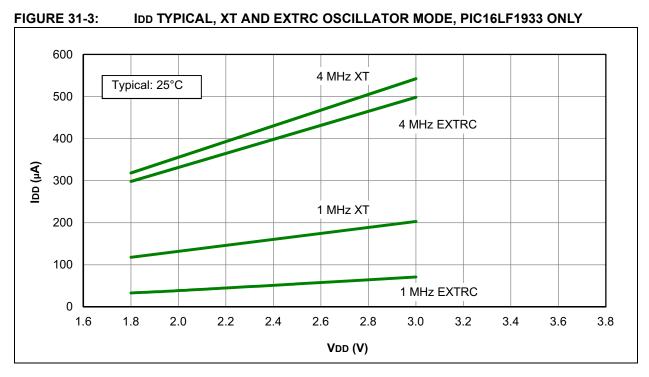

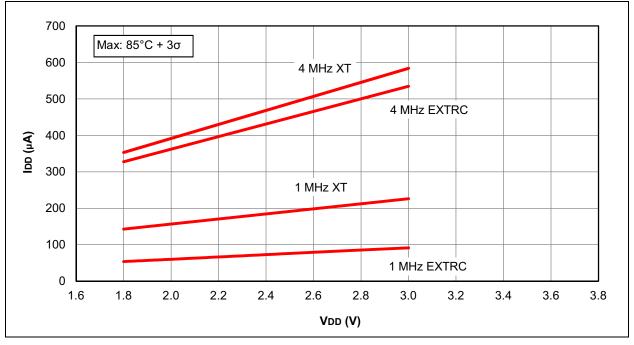

| PIC16LF1 | 933                     |                      | rd Operating temper                                                                                                                                                                     | •     | -40°C ≤ | TA ≤ +85° | n <b>erwise stated)</b><br>C for industrial<br>5°C for extended |                                    |  |

|----------|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-----------|-----------------------------------------------------------------|------------------------------------|--|

| PIC16F19 | 33                      |                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |         |           |                                                                 |                                    |  |

| Param    | Device Characteristics  | Min.                 | Тур†                                                                                                                                                                                    | Max.  | Max.    | Units     |                                                                 | Conditions                         |  |

| No.      |                         |                      | .141                                                                                                                                                                                    | +85°C | +125°C  | ••••••    | VDD                                                             | Note                               |  |

|          | Power-down Base Current | (IPD) <sup>(2)</sup> |                                                                                                                                                                                         |       |         |           |                                                                 |                                    |  |

| D023     |                         | —                    | 0.06                                                                                                                                                                                    | 1     | 7       | μA        | 1.8                                                             | WDT, BOR, FVR, and T1OSC           |  |

|          |                         | —                    | 0.08                                                                                                                                                                                    | 2     | 8       | μA        | 3.0                                                             | disabled, all Peripherals Inactive |  |

| D023     |                         |                      | 20                                                                                                                                                                                      | 55    | 69      | μA        | 1.8                                                             | WDT, BOR, FVR, and T1OSC           |  |

|          |                         |                      | 24                                                                                                                                                                                      | 58    | 72      | μA        | 3.0                                                             | disabled, all Peripherals Inactive |  |

|          |                         | —                    | 26                                                                                                                                                                                      | 60    | 75      | μA        | 5.0                                                             |                                    |  |

| D024     |                         |                      | 0.5                                                                                                                                                                                     | 6     | 8       | μA        | 1.8                                                             | LPWDT Current (Note 1)             |  |

|          |                         | —                    | 0.8                                                                                                                                                                                     | 7     | 9       | μA        | 3.0                                                             |                                    |  |

| D024     |                         |                      | 20                                                                                                                                                                                      | 56    | 70      | μA        | 1.8                                                             | LPWDT Current (Note 1)             |  |

|          |                         |                      | 25                                                                                                                                                                                      | 59    | 73      | μA        | 3.0                                                             |                                    |  |

|          |                         | —                    | 26                                                                                                                                                                                      | 61    | 76      | μA        | 5.0                                                             |                                    |  |

| D025     |                         |                      | 9                                                                                                                                                                                       | 20    | 20      | μA        | 1.8                                                             | FVR current                        |  |

|          |                         | —                    | 9                                                                                                                                                                                       | 23    | 23      | μA        | 3.0                                                             |                                    |  |

| D025     |                         |                      | 36                                                                                                                                                                                      | 96    | 120     | μA        | 1.8                                                             | FVR current (Note 4)               |  |

|          |                         |                      | 43                                                                                                                                                                                      | 110   | 140     | μA        | 3.0                                                             |                                    |  |

|          |                         | —                    | 75                                                                                                                                                                                      | 140   | 170     | μA        | 5.0                                                             |                                    |  |

| D026     |                         |                      | 8                                                                                                                                                                                       | 17    | 17      | μΑ        | 3.0                                                             | BOR Current (Note 1)               |  |

| D026     |                         | _                    | 28                                                                                                                                                                                      | 96    | 120     | μA        | 3.0                                                             | BOR Current (Note 1, Note 4)       |  |

|          |                         | —                    | 30                                                                                                                                                                                      | 130   | 170     | μA        | 5.0                                                             |                                    |  |

| D027     |                         | _                    | 0.6                                                                                                                                                                                     | 5     | 5       | μA        | 1.8                                                             | T1OSC Current (Note 1)             |  |

|          |                         |                      | 3.9                                                                                                                                                                                     | 9     | 9.5     | μA        | 3.0                                                             |                                    |  |

| D027     |                         | _                    | 22                                                                                                                                                                                      | 57    | 71      | μA        | 1.8                                                             | T1OSC Current (Note 1)             |  |

|          |                         | _                    | 28                                                                                                                                                                                      | 62    | 78      | μA        | 3.0                                                             | -                                  |  |

|          |                         | —                    | 33                                                                                                                                                                                      | 66    | 83      | μA        | 5.0                                                             |                                    |  |

#### 30.3 DC Characteristics: Power-Down Currents (IPD)

t Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

**3:** A/D oscillator source is FRC.

4: 0.1 μF capacitor on VCAP.

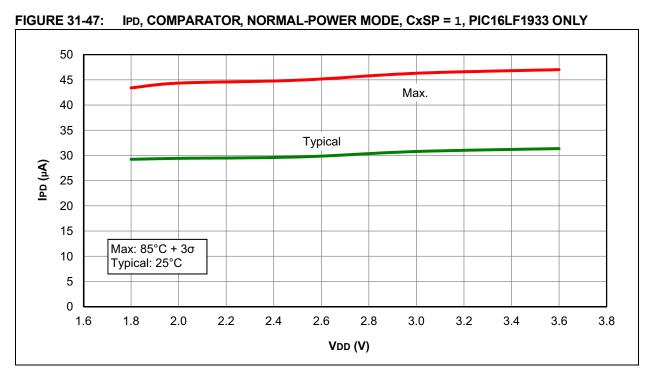

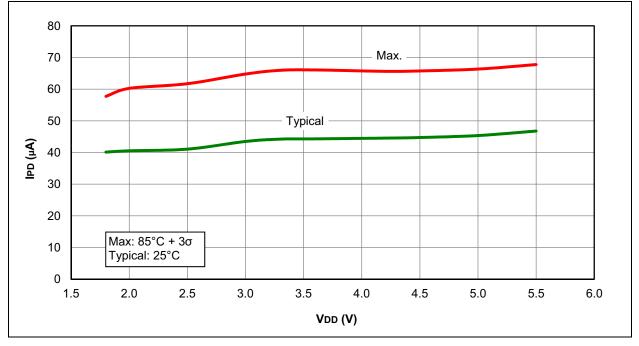

FIGURE 31-48: IPD, COMPARATOR, NORMAL-POWER MODE, CxSP = 1, PIC16F1933 ONLY

## 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 32.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

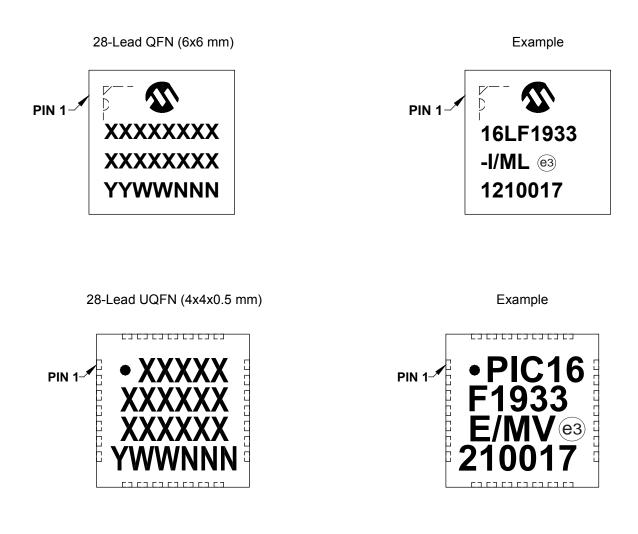

## Package Marking Information (Continued)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                    | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support