#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

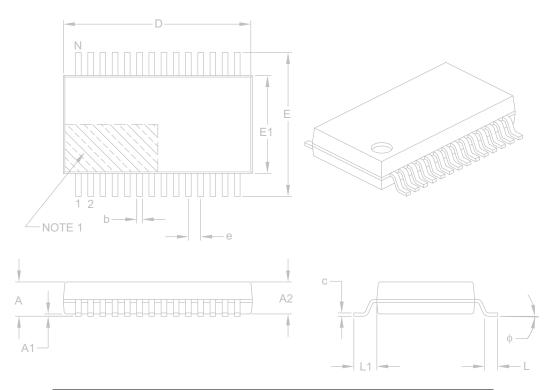

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1933-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1933

| REGISTE                   | R 4-2: CON                                                                                   | FIG2: CONF                                                | IGURATION                                                                     |                                    |                 |                                       |       |

|---------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------|-----------------|---------------------------------------|-------|

|                           |                                                                                              | R/P-1                                                     | R/P-1                                                                         | U-1                                | R/P-1           | R/P-1                                 | R/P-1 |

|                           |                                                                                              | LVP <sup>(1)</sup>                                        | DEBUG <sup>(3)</sup>                                                          | _                                  | BORV            | STVREN                                | PLLEN |

|                           |                                                                                              | bit 13                                                    |                                                                               |                                    |                 | · · · · · · · · · · · · · · · · · · · | bit 8 |

| U-1                       | U-1                                                                                          | R/P-1                                                     | R/P-1                                                                         | U-1                                | U-1             | R/P-1                                 | R/P-1 |

|                           | _                                                                                            | VCAPE                                                     | N<1:0> <sup>(2)</sup>                                                         | —                                  | _               | WRT                                   | <1:0> |

| bit 7                     |                                                                                              |                                                           |                                                                               |                                    |                 |                                       | bit 0 |

| Legend:                   |                                                                                              |                                                           |                                                                               |                                    |                 |                                       |       |

| R = Reada                 | able bit                                                                                     | P = Program                                               | mable bit                                                                     | U = Unimplen                       | nented bit, rea | d as '1'                              |       |

| '0' = Bit is              | cleared                                                                                      | '1' = Bit is se                                           |                                                                               | -n = Value wh                      | en blank or af  | ter Bulk Erase                        |       |

| bit 13                    | 1 = Low-volta                                                                                | age programm                                              | iming Enable bi<br>ing enabled<br>must be used fe                             |                                    | 3               |                                       |       |

| bit 12                    | <b>DEBUG:</b> In-O<br>1 = In-Circuit                                                         | Circuit Debugg<br>Debugger dis                            | er Mode bit <sup>(3)</sup><br>abled, ICSPCLł                                  | K and ICSPDAT                      | are general p   | ourpose I/O pins<br>I to the debugge  |       |

| bit 11                    |                                                                                              | nted: Read as                                             |                                                                               |                                    |                 |                                       |       |

| bit 10                    | 1 = Brown-ou                                                                                 | ut Reset voltag                                           | oltage Selection<br>le (Vbor), low tri<br>le (Vbor), high t                   | ip point selected                  |                 |                                       |       |

| bit 9                     | 1 = Stack Ov                                                                                 | erflow or Unde                                            | Inderflow Rese<br>orflow will cause<br>orflow will not ca                     | e a Reset                          |                 |                                       |       |

| bit 8                     | <b>PLLEN:</b> PLL<br>1 = 4xPLL er<br>0 = 4xPLL di                                            | nabled                                                    |                                                                               |                                    |                 |                                       |       |

| bit 7-5                   | Unimplemer                                                                                   | nted: Read as                                             | '1'                                                                           |                                    |                 |                                       |       |

| bit 4                     | VCAPEN: VC<br>00 = VCAP ft<br>01 = VCAP ft<br>10 = VCAP ft                                   | oltage Regulate<br>unctionality is e<br>unctionality is e | or Capacitor En<br>enabled on RA0<br>enabled on RA5<br>enabled on RA6         |                                    |                 |                                       |       |

| bit 3-2                   | Unimplemer                                                                                   | nted: Read as                                             | '1'                                                                           |                                    |                 |                                       |       |

| bit 1-0                   | 00 = VCAP fu<br>01 = VCAP fu<br>10 = VCAP fu                                                 | unctionality is e<br>unctionality is e                    | Self-Write Prote<br>enabled on RA0<br>enabled on RA5<br>enabled on RA6<br>pin |                                    |                 |                                       |       |

| Note 1:<br>2:<br>3:<br>4: | The LVP bit can<br>Reads as '11' or<br>The DEBUG bit i<br>debuggers and p<br>See Vbor parame | n PIC16LF1932<br>n Configuratio<br>programmers. I         | K only.<br>n Words is man<br>For normal devi                                  | aged automatic<br>ce operation, th | cally by device | development to                        |       |

# REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

### EXAMPLE 11-3: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG ADDR HI: PROG ADDR LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELEEADRL; Select Bank for EEPROM registersMOVLWPROG_ADDR_LO;MOVWFEEADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWLEEADRH; Store MSB of address

EECON1,CFGS ; Do not select Configuration Space

EECON1,EEPGD ; Select Program Memory

BCF

EECON1,CFGS

BSF

INTCON,GIE ; Disable interrupts

BCF

; Initiate read

BSF

EECON1,RD

NOP

; Executed (Figure 11-1)

NOP

; Ignored (Figure 11-1)

BSF

INTCON, GIE

; Restore interrupts

EEDATL,W

MOVF

; Get LSB of word

MOVWF

PROG_DATA_LO ; Store in user location

EEDATH,W ; Get MSB of word

PROG_DATA_HI ; Store in user location

MOVE

MOVWF

```

#### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

|                      | LE 11-5:    |                    |                                                            |

|----------------------|-------------|--------------------|------------------------------------------------------------|

|                      |             | tine assumes the f |                                                            |

|                      | -           |                    | ded, starting at the address in DATA_ADDR                  |

|                      |             |                    | ten is made up of two adjacent bytes in DATA_ADDR,         |

|                      |             | ittle endian forma |                                                            |

|                      |             | -                  | e least significant bits = 000) is loaded in ADDRH:ADDRL   |

| ; 4. Al              | DDRH and AI | DDRL are located 1 | in shared data memory 0x70 - 0x7F (common RAM)             |

| ,                    | BCF         | INTCON, GIE        | ; Disable ints so required sequences will execute properly |

|                      | BANKSEL     | EEADRH             | ; Bank 3                                                   |

|                      | MOVF        | ADDRH,W            | ; Load initial address                                     |

|                      | MOVWF       | EEADRH             | ;                                                          |

|                      | MOVF        | ADDRL,W            | ;                                                          |

|                      | MOVWF       | EEADRL             | ;                                                          |

|                      | MOVLW       | LOW DATA ADDR      | ; Load initial data address                                |

|                      | MOVWF       | FSROL              | ;                                                          |

|                      | MOVLW       | HIGH DATA_ADDR     | ; Load initial data address                                |

|                      | MOVWF       | FSROH              | ;                                                          |

|                      | BSF         |                    | ; Point to program memory                                  |

|                      | BCF         |                    | ; Not configuration space                                  |

|                      | BSF         |                    | ; Enable writes                                            |

|                      | BSF         | EECON1,LWLO        | ; Only Load Write Latches                                  |

| LOOP                 | MOUTE       |                    |                                                            |

|                      | MOVIW       | FSR0++             | ; Load first data byte into lower                          |

|                      | MOVWF       | EEDATL             | ;                                                          |

|                      | MOVIW       | FSR0++             | ; Load second data byte into upper                         |

|                      | MOVWF       | EEDATH             | ;                                                          |

|                      | MOVF        | EEADRL,W           | ; Check if lower bits of address are '000'                 |

|                      | XORLW       | 0x07               | ; Check if we're on the last of 8 addresses                |

|                      | ANDLW       | 0x07               | ;                                                          |

|                      | BTFSC       | STATUS,Z           | ; Exit if last of eight words,                             |

|                      | GOTO        | START_WRITE        | ;                                                          |

|                      | MOVLW       | 55h                | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2             | ; Write 55h                                                |

| _ 0                  | MOVLW       | 0AAh               | ;                                                          |

| red                  | MOVWF       | EECON2             | ; Write AAh                                                |

| Required<br>Sequence | BSF         | EECON1,WR          | ; Set WR bit to begin write                                |

| Sec                  | NOP         |                    | ; Any instructions here are ignored as processor           |

|                      |             |                    | ; halts to begin write sequence                            |

|                      | NOP         |                    | ; Processor will stop here and wait for write to complete. |

|                      |             |                    | ; After write processor continues with 3rd instruction.    |

|                      | INCF        | EEADRL,F           | ; Still loading latches Increment address                  |

|                      | GOTO        | LOOP               | ; Write next latches                                       |

|                      | ייח ד מני   |                    |                                                            |

| START_V              | BCF         | EECON1,LWLO        | ; No more loading latches - Actually start Flash program   |

|                      | DOI         | LICONT, INIO       | ; memory write                                             |

|                      |             |                    | ,                                                          |

|                      | MOVLW       | 55h                | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2             | ; Write 55h                                                |

| 8 9                  | MOVLW       | 0AAh               | ;                                                          |

| Required<br>Sequence | MOVWF       | EECON2             | ; Write AAh                                                |

| ibe:                 | BSF         | EECON1,WR          | ; Set WR bit to begin write                                |

| ч                    | NOP         |                    | ; Any instructions here are ignored as processor           |

|                      |             |                    | ; halts to begin write sequence                            |

|                      | NOP         |                    | ; Processor will stop here and wait for write complete.    |

|                      |             |                    | ; after write processor continues with 3rd instruction     |

|                      | BCF         | EECON1,WREN        | ; Disable writes                                           |

|                      | BSF         | INTCON, GIE        | ; Enable interrupts                                        |

|                      |             |                    |                                                            |

# 11.7 Register Definitions: Data EEPROM Control

# REGISTER 11-1: EEDATL: EEPROM DATA LOW BYTE REGISTER

| R/W-x/u              | R/W-x/u | R/W-x/u                                             | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|---------|-----------------------------------------------------|-------------------------------------------------------|---------|---------|---------|---------|

|                      |         |                                                     | EEDA                                                  | T<7:0>  |         |         |         |

| bit 7                |         |                                                     |                                                       |         |         |         | bit 0   |

|                      |         |                                                     |                                                       |         |         |         |         |

| Legend:              |         |                                                     |                                                       |         |         |         |         |

| R = Readable bit     |         | W = Writable bit U = Unimplemented bit, read as '0' |                                                       |         |         |         |         |

| u = Bit is unchanged | d       | x = Bit is unknown                                  | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         | esets   |

| '1' = Bit is set     |         | '0' = Bit is cleared                                |                                                       |         |         |         |         |

bit 7-0 EEDAT<7:0>: Read/Write Value for EEPROM Data Byte or Least Significant bits of Program Memory

## REGISTER 11-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|--|

| —     | —   |         | EEDAT<13:8> |         |         |         |         |  |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: | Read as '0' |

|---------|----------------|-------------|

|         |                |             |

bit 5-0 EEDAT<13:8>: Read/Write Value for Most Significant bits of Program Memory

### REGISTER 11-3: EEADRL: EEPROM ADDRESS LOW BYTE REGISTER

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| EEADR<7:0>  |         |         |         |         |         |         |         |  |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**EEADR<7:0>**: Specifies the Least Significant bits for Program Memory Address or EEPROM Address

# REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | EEADR<14:8> | >       |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for Program Memory Address or EEPROM Address

Note 1: Unimplemented, read as '1'.

# 23.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

### 23.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

### 23.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# 23.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see Section 12.1 "Alternate Pin Function" for more information.

| Name     | Bit 7        | Bit 6               | Bit 5  | Bit 4   | Bit 3   | Bit 2    | Bit 1  | Bit 0   | Register<br>on Page |

|----------|--------------|---------------------|--------|---------|---------|----------|--------|---------|---------------------|

| APFCON   | —            | CCP3SEL             | T1GSEL | P2BSEL  | SRNQSEL | C2OUTSEL | SSSEL  | CCP2SEL | 114                 |

| CCPxCON  | PxM<         | 1:0> <sup>(1)</sup> | DCxB   | <1:0>   |         | CCPxN    | /<3:0> |         | 214                 |

| CCPTMRS0 | C4TSE        | L<1:0>              | C3TSE  | L<1:0>  | C2TSE   | EL<1:0>  | C1TSE  | EL<1:0> | 215                 |

| CCPTMRS1 | —            | —                   | —      | —       | —       | —        | C5TSE  | :L<1:0> | 215                 |

| INTCON   | GIE          | PEIE                | TMR0IE | INTE    | IOCIE   | TMR0IF   | INTF   | IOCIF   | 82                  |

| PIE1     | TMR1GIE      | ADIE                | RCIE   | TXIE    | SSPIE   | CCP1IE   | TMR2IE | TMR1IE  | 83                  |

| PIE2     | OSFIE        | C2IE                | C1IE   | EEIE    | BCLIE   | LCDIE    | —      | CCP2IE  | 84                  |

| PIE3     | _            | CCP5IE              | CCP4IE | CCP3IE  | TMR6IE  | _        | TMR4IE | —       | 85                  |

| PIR1     | TMR1GIF      | ADIF                | RCIF   | TXIF    | SSPIF   | CCP1IF   | TMR2IF | TMR1IF  | 86                  |

| PIR2     | OSFIF        | C2IF                | C1IF   | EEIF    | BCLIF   | LCDIF    | —      | CCP2IF  | 87                  |

| PIR3     | —            | CCP5IF              | CCP4IF | CCP3IF  | TMR6IF  | —        | TMR4IF | —       | 88                  |

| PRx      | Timer2/4/6 P | eriod Registe       | er     |         |         |          |        |         | 187*                |

| TxCON    | —            |                     | TxOUT  | PS<3:0> |         | TMRxON   | TxCKP  | 'S<:0>1 | 189                 |

| TMRx     | Timer2/4/6 M | Iodule Regist       | er     |         |         |          |        |         | 187                 |

| TRISA    | TRISA7       | TRISA6              | TRISA5 | TRISA4  | TRISA3  | TRISA2   | TRISA1 | TRISA0  | 116                 |

| TRISB    | TRISB7       | TRISB6              | TRISB5 | TRISB4  | TRISB3  | TRISB2   | TRISB1 | TRISB0  | 121                 |

| TRISC    | TRISC7       | TRISC6              | TRISC5 | TRISC4  | TRISC3  | TRISC2   | TRISC1 | TRISC0  | 125                 |

### TABLE 23-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM.

Note 1: Applies to ECCP modules only.

Page provides register information.

| R/W-0/0                 | R/W-0/0                                   | R/W-0/0                                                                                | R/W-0/0      | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|-------------------------|-------------------------------------------|----------------------------------------------------------------------------------------|--------------|----------------|------------------|------------------|--------------|--|

| C4TSEL<1:0> C3TSEL<1:0> |                                           | L<1:0>                                                                                 | C2TSE        | L<1:0>         | C1TSE            | :L<1:0>          |              |  |

| bit 7                   |                                           |                                                                                        |              |                |                  |                  | bit C        |  |

|                         |                                           |                                                                                        |              |                |                  |                  |              |  |

| Legend:                 |                                           |                                                                                        |              |                |                  |                  |              |  |

| R = Readable            | e bit                                     | W = Writable I                                                                         | oit          | U = Unimplen   | nented bit, read | d as '0'         |              |  |

| u = Bit is unc          | hanged                                    | x = Bit is unkn                                                                        | own          | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |  |

| '1' = Bit is set        |                                           | '0' = Bit is clea                                                                      | ared         |                |                  |                  |              |  |

|                         |                                           |                                                                                        |              |                |                  |                  |              |  |

| bit 7-6                 | C4TSEL<1:0                                | >: CCP4 Timer                                                                          | Selection    |                |                  |                  |              |  |

|                         | 11 = Reserve                              | Reserved                                                                               |              |                |                  |                  |              |  |

|                         |                                           | 10 = CCP4 is based off Timer6 in PWM mode                                              |              |                |                  |                  |              |  |

|                         |                                           | based off Timer4 in PWM mode                                                           |              |                |                  |                  |              |  |

|                         |                                           | based off Time                                                                         |              | ode            |                  |                  |              |  |

| bit 5-4                 | C3TSEL<1:0                                | CCP3 Timer                                                                             | Selection    |                |                  |                  |              |  |

|                         |                                           | 11 = Reserved                                                                          |              |                |                  |                  |              |  |

|                         |                                           | is based off Timer6 in PWM mode                                                        |              |                |                  |                  |              |  |

|                         |                                           | based off Time                                                                         |              |                |                  |                  |              |  |

|                         |                                           | s based off Time                                                                       |              | ode            |                  |                  |              |  |

| bit 3-2                 |                                           | >: CCP2 Timer                                                                          | Selection    |                |                  |                  |              |  |

|                         | 11 = Reserve                              |                                                                                        |              |                |                  |                  |              |  |

|                         | 10 = CCP2 is based off Timer6 in PWM mode |                                                                                        |              |                |                  |                  |              |  |

|                         |                                           | 01 = CCP2 is based off Timer4 in PWM mode<br>00 = CCP2 is based off Timer2 in PWM mode |              |                |                  |                  |              |  |

|                         |                                           |                                                                                        | oue          |                |                  |                  |              |  |

| bit 1-0                 |                                           |                                                                                        | Selection    |                |                  |                  |              |  |

|                         | 11 = Reserve                              | ed<br>s based off Time                                                                 | re in DW/M m | odo            |                  |                  |              |  |

|                         |                                           | s based off Time                                                                       |              |                |                  |                  |              |  |

|                         |                                           | based off Time                                                                         |              |                |                  |                  |              |  |

# REGISTER 23-2: CCPTMRS0: PWM TIMER SELECTION CONTROL REGISTER 0

#### REGISTER 23-3: CCPTMRS1: PWM TIMER SELECTION CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | —   | —   | _   | C5TSE   | L<1:0>  |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:                            |          |                            |                                                       |

|------------------------------------|----------|----------------------------|-------------------------------------------------------|

| R = Readable                       | bit      | W = Writable bit           | U = Unimplemented bit, read as '0'                    |

| u = Bit is unch                    | nanged   | x = Bit is unknown         | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set                   |          | '0' = Bit is cleared       |                                                       |

|                                    |          |                            |                                                       |

| bit 7-2 Unimplemented: Read as '0' |          |                            |                                                       |

| bit 1-0                            | C5TSEL<1 | I:0>: CCP5 Timer Selection | bits                                                  |

11 = Reserved

10 = CCP5 is based off Timer6 in PWM mode

01 = CCP5 is based off Timer4 in PWM mode

00 = CCP5 is based off Timer2 in PWM mode

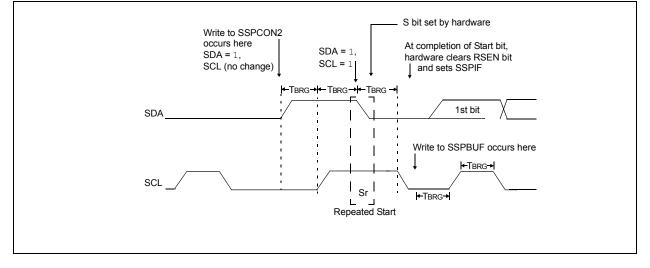

# 24.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 24-27) occurs when the RSEN bit of the SSPCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPSTAT register will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

# FIGURE 24-27: REPEAT START CONDITION WAVEFORM

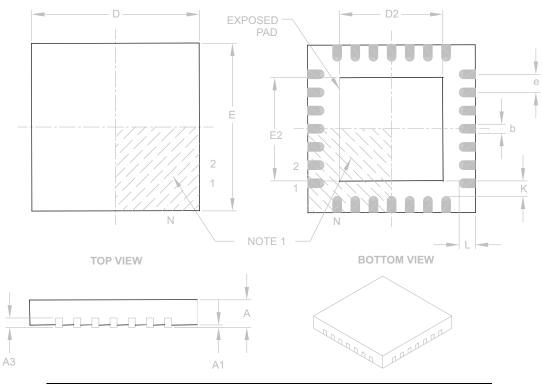

| FIGURE 25-12:                                      | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                    |

|----------------------------------------------------|------------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)            | bit 0     bit 2     bit 3     bit 4     bit 5     bit 6     bit 7            |

| TX/CK pin                                          |                                                                              |

| SREN bit                                           | <u>'0'</u>                                                                   |

| RCIF bit<br>(Interrupt) ————<br>Read<br>RXREG ———— |                                                                              |

|                                                    | agram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

# TABLE 25-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name    | Bit 7    | Bit 6                        | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------|------------------------------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF   | RCIDL                        | _      | SCKP   | BRG16  | _      | WUE    | ABDEN  | 287                 |

| INTCON  | GIE      | PEIE                         | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 82                  |

| PIE1    | TMR1GIE  | ADIE                         | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 83                  |

| PIR1    | TMR1GIF  | ADIF                         | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 86                  |

| RCREG   | EUSART R | EUSART Receive Data Register |        |        |        |        | 280*   |        |                     |

| RCSTA   | SPEN     | RX9                          | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 286                 |

| SPBRGL  | BRG<7:0> |                              |        |        |        | 288*   |        |        |                     |

| SPBRGH  |          |                              |        | BRG<   | :15:8> |        |        |        | 288*                |

| TRISC   | TRISC7   | TRISC6                       | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 125                 |

| TXSTA   | CSRC     | TX9                          | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 285                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

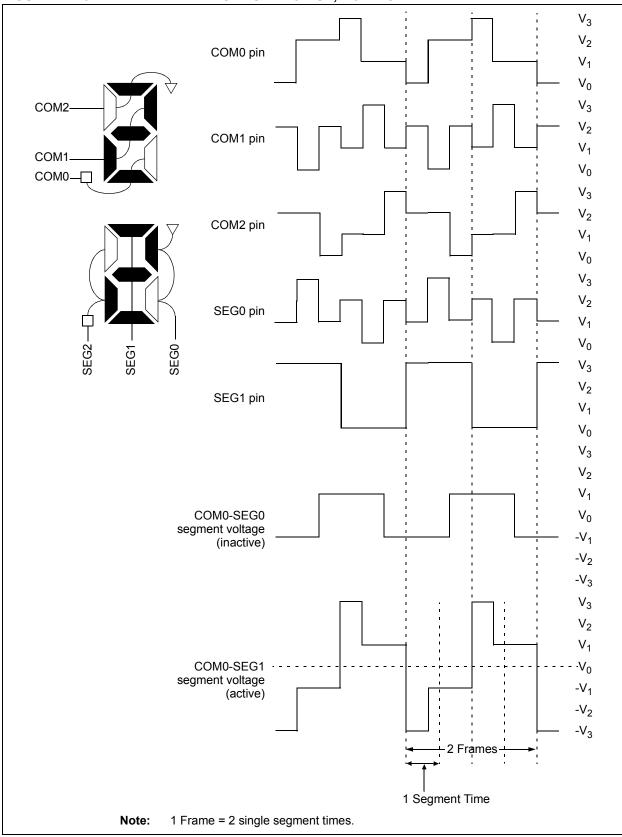

# 27.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 3 LCD Segment Enable registers (LCDSEn)

- Up to 12 LCD data registers (LCDDATAn)

# TABLE 27-1: LCD SEGMENT AND DATA REGISTERS

|               | # of LCD          | Registers |

|---------------|-------------------|-----------|

| Device        | Segment<br>Enable | Data      |

| PIC16(L)F1933 | 2                 | 8         |

The LCDCON register (Register 27-1) controls the operation of the LCD driver module. The LCDPS register (Register 27-2) configures the LCD clock source prescaler and the type of waveform; Type-A or Type-B. The LCDSEn registers (Register 27-5) configure the functions of the port pins.

The following LCDSEn registers are available:

- LCDSE0 SE<7:0>

- LCDSE1 SE<15:8>

Once the module is initialized for the LCD panel, the individual bits of the LCDDATAn registers are cleared/set to represent a clear/dark pixel, respectively:

- LCDDATA0 SEG<7:0>COM0

- LCDDATA1 SEG<15:8>COM0

- LCDDATA3 SEG<7:0>COM1

- LCDDATA4 SEG<15:8>COM1

- LCDDATA6 SEG<7:0>COM2

- LCDDATA7 SEG<15:8>COM2

- LCDDATA9 SEG<7:0>COM3

- LCDDATA10 SEG<15:8>COM3

As an example, LCDDATAn is detailed in Register 27-6.

Once the module is configured, the LCDEN bit of the LCDCON register is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN bit of the LCDCON register.

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                         | R/W-0/0                               | U-0            | R/W-0/0                             | R/W-0/0           | R/W-0/0           | U-0        |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|-------------------------------------|-------------------|-------------------|------------|--|

| LCDIRE           | LCDIRS                                                                                                                                                                                                                                                                          | LCDIRI                                |                | VLCD3PE                             | VLCD2PE           | VLCD1PE           | _          |  |

| bit 7            |                                                                                                                                                                                                                                                                                 |                                       |                |                                     |                   |                   | bit (      |  |

|                  |                                                                                                                                                                                                                                                                                 |                                       |                |                                     |                   |                   |            |  |

| Legend:          |                                                                                                                                                                                                                                                                                 |                                       |                |                                     |                   |                   |            |  |

| R = Readable     |                                                                                                                                                                                                                                                                                 | W = Writable                          |                | •                                   | nented bit, read  |                   |            |  |

| u = Bit is unch  | nanged                                                                                                                                                                                                                                                                          | x = Bit is unkr                       |                |                                     |                   | R/Value at all ot | her Resets |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                 | '0' = Bit is clea                     | ared           | C = Only clea                       | rable bit         |                   |            |  |

| bit 7            | -                                                                                                                                                                                                                                                                               | D Internal Refe                       |                |                                     |                   |                   |            |  |

|                  |                                                                                                                                                                                                                                                                                 | LCD Reference<br>LCD Reference        |                | and connected to                    | the Internal Co   | ontrast Control o | circuit    |  |

| bit 6            |                                                                                                                                                                                                                                                                                 | D Internal Refe                       | rence Source   | e bit                               |                   |                   |            |  |

|                  | <u>If LCDIRE =</u>                                                                                                                                                                                                                                                              |                                       | aat Control is | nowarad by Va                       |                   |                   |            |  |

|                  |                                                                                                                                                                                                                                                                                 |                                       |                | s powered by VD<br>s powered by a 3 |                   | f the FVR         |            |  |

|                  | If LCDIRE =                                                                                                                                                                                                                                                                     | 0:                                    |                |                                     |                   |                   |            |  |

|                  |                                                                                                                                                                                                                                                                                 |                                       |                | ected. LCD banc                     | lgap buffer is di | sabled.           |            |  |

| bit 5            | _                                                                                                                                                                                                                                                                               | D Internal Refere                     |                |                                     |                   |                   |            |  |

|                  | Allows the Internal FVR buffer to shut down when the LCD Reference Ladder is in power mode 'B'<br>1 = When the LCD Reference Ladder is in power mode 'B', the LCD Internal FVR buffer is disable<br>0 = The LCD Internal FVR Buffer ignores the LCD Reference Ladder power mode |                                       |                |                                     |                   |                   |            |  |

| bit 4            | Unimplemer                                                                                                                                                                                                                                                                      | nted: Read as '                       | 0'             |                                     |                   |                   |            |  |

| bit 3            | VLCD3PE: V                                                                                                                                                                                                                                                                      | /LCD3 Pin Enat                        | ole bit        |                                     |                   |                   |            |  |

|                  |                                                                                                                                                                                                                                                                                 | CD3 pin is conne<br>CD3 pin is not ce |                | nternal bias volt                   | age LCDBIAS3      | (1)               |            |  |

| bit 2            | VLCD2PE: VLCD2 Pin Enable bit                                                                                                                                                                                                                                                   |                                       |                |                                     |                   |                   |            |  |

|                  |                                                                                                                                                                                                                                                                                 | CD2 pin is conne<br>CD2 pin is not ce |                | nternal bias volt                   | age LCDBIAS2      | (1)               |            |  |

| bit 1            | VLCD1PE: V                                                                                                                                                                                                                                                                      | LCD1 Pin Enat                         | ole bit        |                                     |                   |                   |            |  |

|                  |                                                                                                                                                                                                                                                                                 | CD1 pin is conne                      | ected to the i | nternal bias volt                   | age LCDBIAS1      | (1)               |            |  |

|                  | 0 = The VLC                                                                                                                                                                                                                                                                     | CD1 pin is not c                      | onnected       |                                     |                   |                   |            |  |

# REGISTER 27-3: LCDREF: LCD REFERENCE VOLTAGE CONTROL REGISTER

Note 1: Normal pin controls of TRISx and ANSELx are unaffected.

# PIC16(L)F1933

# 27.12 Operation During Sleep

The LCD module can operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Setting the SLPEN bit allows the LCD module to go to Sleep. Clearing the SLPEN bit allows the module to continue to operate during Sleep.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will cease all functions and go into a very low-current consumption mode. The module will stop operation immediately and drive the minimum LCD voltage on both segment and common lines. Figure 27-20 shows this operation.

The LCD module can be configured to operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Clearing SLPEN and correctly configuring the LCD module clock will allow the LCD module to operate during Sleep. Setting SLPEN and correctly executing the LCD module shutdown will disable the LCD module during Sleep and save power.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will immediately cease all functions, drive the outputs to Vss and go into a very low-current mode. The SLEEP instruction should only be executed after the LCD module has been disabled and the current cycle completed, thus ensuring that there are no DC voltages on the glass. To disable the LCD module, clear the LCDEN bit. The LCD module will complete the disabling process after the current frame, clear the LCDA bit and optionally cause an interrupt.

The steps required to properly enter Sleep with the LCD disabled are:

- Clear LCDEN

- Wait for LCDA = 0 either by polling or by interrupt

- Execute SLEEP

If SLPEN = 0 and SLEEP is executed while the LCD module clock source is FOSC/4, then the LCD module will halt with the pin driving the last LCD voltage pattern. Prolonged exposure to a fixed LCD voltage pattern will cause damage to the LCD glass. To prevent LCD glass damage, either perform the proper LCD module shutdown prior to Sleep, or change the LCD module clock to allow the LCD module to continue operation during Sleep.

If a SLEEP instruction is executed and SLPEN = 0 and the LCD module clock is either T1OSC or LFINTOSC, the module will continue to display the current contents of the LCDDATA registers. While in Sleep, the LCD data cannot be changed. If the LCDIE bit is set, the device will wake from Sleep on the next LCD frame boundary. The LCD module current consumption will not decrease in this mode; however, the overall device power consumption will be lower due to the shutdown of the CPU and other peripherals. Table 27-8 shows the status of the LCD module during a Sleep while using each of the three available clock sources.

| Note: | When the LCDEN bit is cleared, the LCD       |

|-------|----------------------------------------------|

|       | module will be disabled at the completion    |

|       | of frame. At this time, the port pins will   |

|       | revert to digital functionality. To minimize |

|       | power consumption due to floating digital    |

|       | inputs, the LCD pins should be driven low    |

|       | using the PORT and TRIS registers.           |

If a SLEEP instruction is executed and SLPEN = 0, the module will continue to display the current contents of the LCDDATA registers. To allow the module to continue operation while in Sleep, the clock source must be either the LFINTOSC or T1OSC external oscillator. While in Sleep, the LCD data cannot be changed. The LCD module current consumption will not decrease in this mode; however, the overall consumption of the device will be lower due to shut down of the core and other peripheral functions.

Table 27-8 shows the status of the LCD module during Sleep while using each of the three available clock sources:

| TABLE 27-8: | LCD MODULE STATUS |

|-------------|-------------------|

|             | DURING SLEEP      |

| Clock Source | SLPEN | Operational<br>During Sleep |

|--------------|-------|-----------------------------|

| T1OSC        | 0     | Yes                         |

| 11030        | 1     | No                          |

| LFINTOSC     | 0     | Yes                         |

| LEINTOSC     | 1     | No                          |

| Fosc/4       | 0     | No                          |

| F05C/4       | 1     | No                          |

Note: The LFINTOSC or external T1OSC oscillator must be used to operate the LCD module during Sleep.

If LCD interrupts are being generated (Type-B waveform with a multiplex mode not static) and LCDIE = 1, the device will awaken from Sleep on the next frame boundary.

#### **Instruction Descriptions** 29.2

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [label]ADDFSR FSRn, k                                                                         |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [0, 1]                                                          |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  | FOR is limited to the second OOOOk                                                            |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                                       |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                     |  |

| Operation:       | $(W) + k \to (W)$                                                                                                       |  |

| Status Affected: | C, DC, Z                                                                                                                |  |

| Description:     | The contents of the W register are<br>added to the eight-bit literal 'k' and the<br>result is placed in the W register. |  |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                     |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                       |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                                 |

| Status Affected: | C, Z                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in reg- |

ister 'f'.

| ► | register f | → | С |  |

|---|------------|---|---|--|

| ADDWFC           | ADD W and CARRY bit to f                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

# PIC16(L)F1933

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                              |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01,10,11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                            |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

# No Operation

| Syntax:          | [label] NOP   |

|------------------|---------------|

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                            |

| Operands:        | None                                                                                                      |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to<br>OPTION_REG register.                                                      |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | OPTION                                                                                                    |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| RESET            | Software Reset                                                                   |

|------------------|----------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                    |

| Operands:        | None                                                                             |

| Operation:       | Execute a device Reset. Resets the $\overline{RI}$ flag of the PCON register.    |

| Status Affected: | None                                                                             |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |

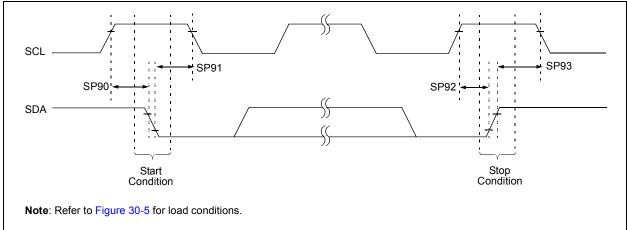

# 30.8 AC Characteristics: PIC16(L)F1933-I/E

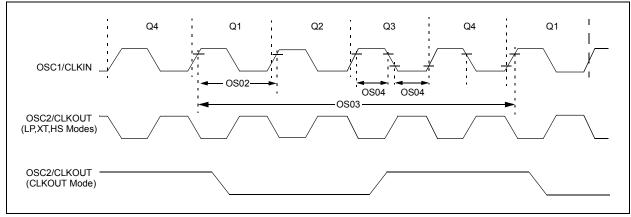

# FIGURE 30-6: CLOCK TIMING

## TABLE 30-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                         |      |                    |          |       |                                |  |

|----------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------|------|--------------------|----------|-------|--------------------------------|--|

| Param<br>No.                                                                                                         | Sym.     | Characteristic                          | Min. | Тур†               | Max.     | Units | Conditions                     |  |

| OS01                                                                                                                 | Fosc     | External CLKIN Frequency <sup>(1)</sup> | DC   | —                  | 0.5      | MHz   | EC Oscillator mode (low)       |  |

|                                                                                                                      |          |                                         | DC   | _                  | 4        | MHz   | EC Oscillator mode (medium)    |  |

|                                                                                                                      |          |                                         | DC   | —                  | 20       | MHz   | EC Oscillator mode (high)      |  |

|                                                                                                                      |          | Oscillator Frequency <sup>(1)</sup>     | —    | 32.768             | _        | kHz   | LP Oscillator mode             |  |

|                                                                                                                      |          |                                         | 0.1  | _                  | 4        | MHz   | XT Oscillator mode             |  |

|                                                                                                                      | 1 — 4 MH |                                         | MHz  | HS Oscillator mode |          |       |                                |  |

|                                                                                                                      |          |                                         | 1    | _                  | 20       | MHz   | HS Oscillator mode, VDD > 2.7V |  |

|                                                                                                                      |          |                                         | DC   | _                  | 4        | MHz   | RC Oscillator mode, VDD > 2.0V |  |

| OS02                                                                                                                 | Tosc     | External CLKIN Period <sup>(1)</sup>    | 27   | _                  | ~        | μs    | LP Oscillator mode             |  |

|                                                                                                                      |          |                                         | 250  | —                  | $\infty$ | ns    | XT Oscillator mode             |  |