#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1933t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### 3.3 Register Definitions: Status

**REGISTER 3-1:** STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

**Note 1:** The <u>C</u> and <u>DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

| U-0              | U-0   | U-0                  | R-1/q | R-1/q          | R/W-0/u                        | R/W-0/u           | R/W-0/u          |  |  |

|------------------|-------|----------------------|-------|----------------|--------------------------------|-------------------|------------------|--|--|

| —                | _     | —                    | TO    | PD             | Z                              | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |

| bit 7            |       |                      |       |                |                                |                   | bit 0            |  |  |

|                  |       |                      |       |                |                                |                   |                  |  |  |

| Legend:          |       |                      |       |                |                                |                   |                  |  |  |

| R = Readable b   | oit   | W = Writable I       | bit   | U = Unimpler   | mented bit, read               | as '0'            |                  |  |  |

| u = Bit is uncha | anged | x = Bit is unkn      | iown  | -n/n = Value a | at POR and BO                  | R/Value at all o  | ther Resets      |  |  |

| '1' = Bit is set |       | '0' = Bit is cleared |       |                | q = Value depends on condition |                   |                  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

| Address                | Name   | Bit 7        | Bit 6                           | Bit 5          | Bit 4           | Bit 3        | Bit 2        | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|--------------|---------------------------------|----------------|-----------------|--------------|--------------|--------|--------|----------------------|---------------------------------|

| Bank 7                 |        |              |                                 |                |                 |              |              |        | •      |                      |                                 |

| 380h <sup>(2)</sup>    | INDF0  |              | this location ical register)    | uses contents  | s of FSR0H/F    | SR0L to addr | ess data mer | nory   |        | ****                 | XXXX XXXX                       |

| 381h <sup>(2)</sup>    | INDF1  |              | this location<br>ical register) | uses contents  | s of FSR1H/F    | SR1L to addr | ess data mer | mory   |        | XXXX XXXX            | XXXX XXXX                       |

| 382h <sup>(2)</sup>    | PCL    | Program Co   | ounter (PC) L                   | east Significa | nt Byte         |              |              |        |        | 0000 0000            | 0000 0000                       |

| 383h <sup>(2)</sup>    | STATUS | _            | _                               | _              | TO              | PD           | Z            | DC     | С      | 1 1000               | q quuu                          |

| 384h <sup>(2)</sup>    | FSR0L  | Indirect Dat | a Memory Ac                     | dress 0 Low    | Pointer         |              |              |        | •      | 0000 0000            | uuuu uuuu                       |

| 385h <sup>(2)</sup>    | FSR0H  | Indirect Dat | a Memory Ac                     | ldress 0 High  | Pointer         |              |              |        |        | 0000 0000            | 0000 0000                       |

| 386h <sup>(2)</sup>    | FSR1L  | Indirect Dat | a Memory Ac                     | dress 1 Low    | Pointer         |              |              |        |        | 0000 0000            | uuuu uuuu                       |

| 387h <sup>(2)</sup>    | FSR1H  | Indirect Dat | a Memory Ac                     | ldress 1 High  | Pointer         |              |              |        |        | 0000 0000            | 0000 0000                       |

| 388h <sup>(2)</sup>    | BSR    | _            | _                               | _              |                 |              | BSR<4:0>     |        |        | 0 0000               | 0 0000                          |

| 389h <sup>(2)</sup>    | WREG   | Working Re   | Working Register                |                |                 |              |              |        |        | 0000 0000            | uuuu uuuu                       |

| 38Ah <sup>(1, 2)</sup> | PCLATH | _            | Write Buffer                    | for the upper  | 7 bits of the F | Program Cour | iter         |        |        | -000 0000            | -000 0000                       |

| 38Bh <sup>(2)</sup>    | INTCON | GIE          | PEIE                            | TMR0IE         | INTE            | IOCIE        | TMR0IF       | INTF   | IOCIF  | 0000 0000            | 0000 0000                       |

| 38Ch                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        |        | _                    | _                               |

| 38Dh                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        |        | _                    | _                               |

| 38Eh                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        |        | _                    | _                               |

| 38Fh                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        |        | _                    | _                               |

| 390h                   | _      | Unimpleme    | nted                            |                |                 |              |              |        |        | _                    | _                               |

| 391h                   | _      | Unimpleme    | nted                            |                |                 |              |              |        |        | _                    | _                               |

| 392h                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        | _      | _                    |                                 |

| 393h                   | _      | Unimpleme    | nted                            |                |                 |              |              |        |        | _                    | _                               |

| 394h                   | IOCBP  | IOCBP7       | IOCBP6                          | IOCBP5         | IOCBP4          | IOCBP3       | IOCBP2       | IOCBP1 | IOCBP0 | 0000 0000            | 0000 0000                       |

| 395h                   | IOCBN  | IOCBN7       | IOCBN6                          | IOCBN5         | IOCBN4          | IOCBN3       | IOCBN2       | IOCBN1 | IOCBN0 | 0000 0000            | 0000 0000                       |

| 396h                   | IOCBF  | IOCBF7       | IOCBF6                          | IOCBF5         | IOCBF4          | IOCBF3       | IOCBF2       | IOCBF1 | IOCBF0 | 0000 0000            | 0000 0000                       |

| 397h                   | _      | Unimpleme    |                                 |                |                 |              |              |        | _      | _                    |                                 |

| 398h                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        | _      | _                    |                                 |

| 399h                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        | _      | _                    |                                 |

| 39Ah                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        | _      | _                    |                                 |

| 39Bh                   | _      | Unimpleme    | Unimplemented                   |                |                 |              |              |        | _      | _                    |                                 |

| 39Ch                   | _      | Unimpleme    |                                 |                |                 |              |              |        | _      | _                    |                                 |

| 39Dh                   | _      | - ·          | Unimplemented —                 |                |                 |              |              |        | _      |                      |                                 |

| 39Eh                   | _      | Unimpleme    |                                 |                |                 |              |              |        |        | _                    | _                               |

| 39Fh                   | _      | Unimpleme    |                                 |                |                 |              |              |        |        | _                    | _                               |

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: Unimplemented, read as '1'.

| Address                 | Name            | Bit 7        | Bit 6                                                               | Bit 5          | Bit 4         | Bit 3        | Bit 2        | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|-------------------------|-----------------|--------------|---------------------------------------------------------------------|----------------|---------------|--------------|--------------|-----------|-----------|----------------------|---------------------------------|

| Bank 31                 |                 |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| F80h <sup>(2)</sup>     | INDF0           |              | this location ical register)                                        | uses contents  | s of FSR0H/F  | SR0L to addr | ess data me  | mory      |           | XXXX XXXX            | XXXX XXXX                       |

| F81h <sup>(2)</sup>     | INDF1           |              | this location ical register)                                        | uses contents  | s of FSR1H/F  | SR1L to addr | ess data me  | mory      |           | XXXX XXXX            | XXXX XXXX                       |

| F82h <sup>(2)</sup>     | PCL             | Program C    | ounter (PC) L                                                       | east Significa | ant Byte      |              |              |           |           | 0000 0000            | 0000 0000                       |

| F83h <sup>(2)</sup>     | STATUS          | —            | _                                                                   | _              | TO            | PD           | Z            | DC        | С         | 1 1000               | q quuu                          |

| F84h <sup>(2)</sup>     | FSR0L           | Indirect Dat | ta Memory Ad                                                        | dress 0 Low    | Pointer       |              |              |           |           | 0000 0000            | uuuu uuuu                       |

| F85h <sup>(2)</sup>     | FSR0H           | Indirect Dat | ta Memory Ad                                                        | dress 0 High   | Pointer       |              |              |           |           | 0000 0000            | 0000 0000                       |

| F86h <sup>(2)</sup>     | FSR1L           | Indirect Dat | ta Memory Ad                                                        | dress 1 Low    | Pointer       |              |              |           |           | 0000 0000            | uuuu uuuu                       |

| F87h <sup>(2)</sup>     | FSR1H           | Indirect Dat | ta Memory Ad                                                        | dress 1 High   | Pointer       |              |              |           |           | 0000 0000            | 0000 0000                       |

| F88h <sup>(2)</sup>     | BSR             | _            | _                                                                   | _              |               |              | BSR<4:0>     |           |           | 0 0000               | 0 0000                          |

| F89h <sup>(2)</sup>     | WREG            | Working Re   | egister                                                             |                |               |              |              |           |           | 0000 0000            | uuuu uuuu                       |

| F8Ah <sup>(1),(2)</sup> | PCLATH          | _            | Write Buffer for the upper 7 bits of the Program Counter            |                |               |              |              | -000 0000 | -000 0000 |                      |                                 |

| F8Bh <sup>(2)</sup>     | INTCON          | GIE          | PEIE                                                                | TMR0IE         | INTE          | IOCIE        | TMR0IF       | INTF      | IOCIF     | 0000 0000            | 0000 0000                       |

| F8Ch                    | _               | Unimpleme    | Unimplemented                                                       |                |               |              |              | _         | _         |                      |                                 |

|                         |                 |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| FE3h                    | 0747110         |              |                                                                     |                | 1             | T            | -            |           | 0.0000    |                      |                                 |

| FE4h                    | STATUS_<br>SHAD |              |                                                                     |                |               |              | Z_SHAD       | DC_SHAD   | C_SHAD    | xxx                  | uuu                             |

| FE5h                    | WREG            | Working Re   | Working Register Normal (Non-ICD) Shadow                            |                |               |              |              | XXXX XXXX | uuuu uuuu |                      |                                 |

|                         | SHAD            |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| FE6h                    | BSR_            |              |                                                                     |                | Bank Select   | Register Nor | mal (Non-ICI | D) Shadow |           | x xxxx               | u uuuu                          |

|                         | SHAD            |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| FE7h                    | PCLATH_         |              | Program Counter Latch High Register Normal (Non-ICD) Shadow         |                |               |              |              | -xxx xxxx | uuuu uuuu |                      |                                 |

|                         | SHAD            |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| FE8h                    | FSR0L_          | Indirect Dat | ta Memory Ad                                                        | dress 0 Low    | Pointer Norm  | al (Non-ICD) | Shadow       |           |           | XXXX XXXX            | uuuu uuuu                       |

|                         | SHAD            |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| FE9h                    | FSR0H_          | Indirect Dat | ndirect Data Memory Address 0 High Pointer Normal (Non-ICD) Shadow  |                |               |              |              | XXXX XXXX | uuuu uuuu |                      |                                 |

|                         | SHAD            |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| FEAh                    | FSR1L_          | Indirect Dat | ndirect Data Memory Address 1 Low Pointer Normal (Non-ICD) Shadow   |                |               |              |              | XXXX XXXX | uuuu uuuu |                      |                                 |

|                         | SHAD            |              |                                                                     |                |               |              |              |           |           |                      |                                 |

| FEBh                    | FSR1H_<br>SHAD  | Indirect Dat | Indirect Data Memory Address 1 High Pointer Normal (Non-ICD) Shadow |                |               |              |              | XXXX XXXX | uuuu uuuu |                      |                                 |

| FECh                    | —               | Unimpleme    | ented                                                               |                |               |              |              |           |           | _                    | _                               |

| FEDh                    | STKPTR          | _            | _                                                                   | _              | Current Stat  | k pointer    |              |           |           | 1 1111               | 1 1111                          |

| FEEh                    | TOSL            | Top of Stac  | Top of Stack Low byte                                               |                |               |              |              |           | XXXX XXXX | uuuu uuuu            |                                 |

| FEFh                    | TOSH            | · _ ·        | Top of Stack                                                        | Hiah byte      |               |              |              |           |           | -xxx xxxx            |                                 |

| Legend                  |                 |              | •                                                                   | • •            | n condition - |              |              |           |           |                      | and adda                        |

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

3: Unimplemented, read as '1'.

### PIC16(L)F193X

| -      |                                   |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7  | Bit 6                             | Bit 5                                                                                                                                  | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 3                                                   | Bit 2                                                                                                                           | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Register<br>on Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| _      |                                   | ANSB5                                                                                                                                  | ANSB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ANSB3                                                   | ANSB2                                                                                                                           | ANSB1                                                                                                                                                                                                                                                                                                                                                                                                                             | ANSB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GIE    | PEIE                              | TMR0IE                                                                                                                                 | INTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IOCIE                                                   | TMR0IF                                                                                                                          | INTF                                                                                                                                                                                                                                                                                                                                                                                                                              | IOCIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IOCBF7 | IOCBF6                            | IOCBF5                                                                                                                                 | IOCBF4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IOCBF3                                                  | IOCBF2                                                                                                                          | IOCBF1                                                                                                                                                                                                                                                                                                                                                                                                                            | IOCBF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IOCBN7 | IOCBN6                            | IOCBN5                                                                                                                                 | IOCBN4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IOCBN3                                                  | IOCBN2                                                                                                                          | IOCBN1                                                                                                                                                                                                                                                                                                                                                                                                                            | IOCBN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IOCBP7 | IOCBP6                            | IOCBP5                                                                                                                                 | IOCBP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IOCBP3                                                  | IOCBP2                                                                                                                          | IOCBP1                                                                                                                                                                                                                                                                                                                                                                                                                            | IOCBP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TRISB7 | TRISB6                            | TRISB5                                                                                                                                 | TRISB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TRISB3                                                  | TRISB2                                                                                                                          | TRISB1                                                                                                                                                                                                                                                                                                                                                                                                                            | TRISB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | GIE<br>IOCBF7<br>IOCBN7<br>IOCBP7 | —         —           GIE         PEIE           IOCBF7         IOCBF6           IOCBN7         IOCBN6           IOCBP7         IOCBP6 | Image: marked with a state with a | Image: marked bit with with with with with with with wi | ANSB5ANSB4ANSB3GIEPEIETMR0IEINTEIOCIEIOCBF7IOCBF6IOCBF5IOCBF4IOCBF3IOCBN7IOCBN6IOCBN5IOCBN4IOCBN3IOCBP7IOCBP6IOCBP5IOCBP4IOCBP3 | —         ANSB5         ANSB4         ANSB3         ANSB2           GIE         PEIE         TMR0IE         INTE         IOCIE         TMR0IF           IOCBF7         IOCBF6         IOCBF5         IOCBF4         IOCBF3         IOCBF2           IOCBN7         IOCBN6         IOCBN5         IOCBN4         IOCBN3         IOCBN2           IOCBP7         IOCBP6         IOCBP5         IOCBN4         IOCBN3         IOCBN2 | —         ANSB5         ANSB4         ANSB3         ANSB2         ANSB1           GIE         PEIE         TMR0IE         INTE         IOCIE         TMR0IF         INTF           IOCBF7         IOCBF6         IOCBF5         IOCBF4         IOCBF3         IOCBF2         IOCBF1           IOCBN7         IOCBN6         IOCBN5         IOCBP4         IOCBN3         IOCBN2         IOCBN1           IOCBP7         IOCBP6         IOCBN5         IOCBN4         IOCBN3         IOCBN2         IOCBN1 | —         ANSB5         ANSB4         ANSB3         ANSB2         ANSB1         ANSB0           GIE         PEIE         TMR0IE         INTE         IOCIE         TMR0IF         INTF         IOCIF           IOCBF7         IOCBF6         IOCBF5         IOCBF4         IOCBF3         IOCBF2         IOCBF1         IOCBF0           IOCBN7         IOCB6         IOCBF5         IOCBP4         IOCBP3         IOCBN2         IOCBN1         IOCBN0           IOCBP7         IOCBF6         IOCBP5         IOCBP4         IOCBP3         IOCBP2         IOCBN1         IOCBN0 |

#### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

#### 16.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, "Use and Calibration of the Internal Temperature Indicator" (DS01333) for more details regarding the calibration process.

#### 16.1 Circuit Operation

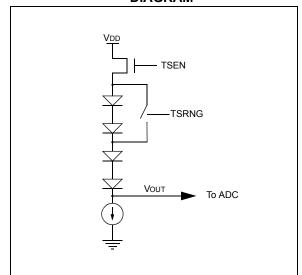

Figure 16-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 16-1 describes the output characteristics of the temperature indicator.

#### EQUATION 16-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 16-1: TEMPERATURE CIRCUIT DIAGRAM

#### 16.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 16-1 shows the recommended minimum VDD vs. range setting.

#### TABLE 16-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

#### 16.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 15.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

#### 16.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

#### REGISTER 24-2: SSPCON1: SSP CONTROL REGISTER 1 (CONTINUED)

- bit 3-0 SS

- SSPM<3:0>: Synchronous Serial Port Mode Select bits

- 1111 =  $I^2C$  Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- 1110 =  $I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled

- 1101 = Reserved

- 1100 = Reserved

- 1011 = I<sup>2</sup>C firmware controlled Master mode (slave idle)

- 1010 = SPI Master mode, clock = Fosc/(4 \* (SSPADD+1))<sup>(5)</sup>

- 1001 = Reserved

- 1000 =  $I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))<sup>(4)</sup>

- 0111 =  $I^2C$  Slave mode, 10-bit address

- 0110 = I<sup>2</sup>C Slave mode, 7-bit address

- 0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin

- 0100 = SPI Slave mode, clock = SCK pin, SS pin control enabled

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0010 = SPI Master mode, clock = Fosc/64

- 0001 = SPI Master mode, clock = Fosc/16

- 0000 = SPI Master mode, clock = Fosc/4

- **Note 1:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

- 2: When enabled, these pins must be properly configured as input or output.

- **3:** When enabled, the SDA and SCL pins must be configured as inputs.

- 4: SSPADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

- 5: SSPADD value of '0' is not supported. Use SSPM = 0000 instead.

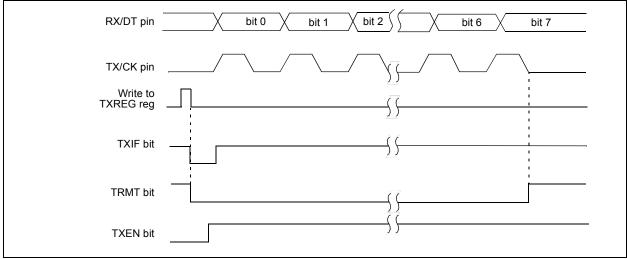

#### 25.5.1.5 Synchronous Master Reception

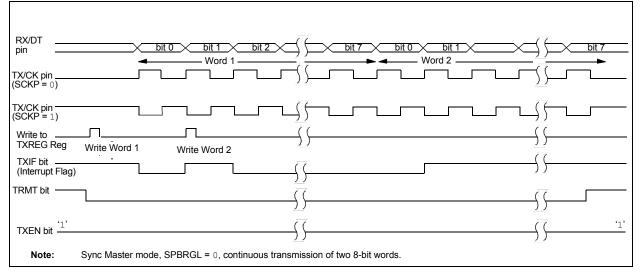

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

#### 25.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 25.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens, the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is

set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 25.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 25.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 27.11 LCD Interrupts

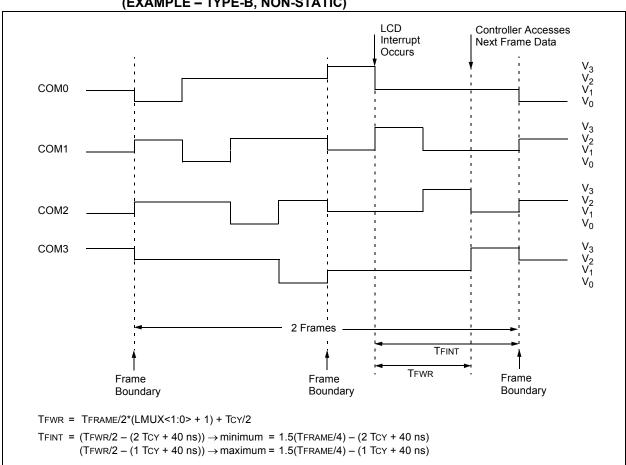

The LCD module provides an interrupt in two cases. An interrupt when the LCD controller goes from active to inactive controller. An interrupt also provides unframe boundaries for Type B waveform. The LCD timing generation provides an interrupt that defines the LCD frame timing.

#### 27.11.1 LCD INTERRUPT ON MODULE SHUTDOWN

An LCD interrupt is generated when the module completes shutting down (LCDA goes from '1' to '0').

#### 27.11.2 LCD FRAME INTERRUPTS

A new frame is defined to begin at the leading edge of the COM0 common signal. The interrupt will be set immediately after the LCD controller completes accessing all pixel data required for a frame. This will occur at a fixed interval before the frame boundary (TFINT), as shown in Figure 27-19. The LCD controller will begin to access data for the next frame within the interval from the interrupt to when the controller begins to access data after the interrupt (TFWR). New data must be written within TFWR, as this is when the LCD controller will begin to access the data for the next frame.

When the LCD driver is running with Type-B waveforms and the LMUX<1:0> bits are not equal to '00' (static drive), there are some additional issues that must be addressed. Since the DC voltage on the pixel takes two frames to maintain zero volts, the pixel data must not change between subsequent frames. If the pixel data were allowed to change, the waveform for the odd frames would not necessarily be the complement of the waveform generated in the even frames and a DC component would be introduced into the panel. Therefore, when using Type-B waveforms, the user must synchronize the LCD pixel updates to occur within a subframe after the frame interrupt.

To correctly sequence writing while in Type-B, the interrupt will only occur on complete phase intervals. If the user attempts to write when the write is disabled, the WERR bit of the LCDCON register is set and the write does not occur.

| Note: | The LCD frame interrupt is not generated |

|-------|------------------------------------------|

|       | when the Type-A waveform is selected     |

|       | and when the Type-B with no multiplex    |

|       | (static) is selected.                    |

### FIGURE 27-19: WAVEFORMS AND INTERRUPT TIMING IN QUARTER-DUTY CYCLE DRIVE (EXAMPLE – TYPE-B, NON-STATIC)

#### 27.12 Operation During Sleep

The LCD module can operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Setting the SLPEN bit allows the LCD module to go to Sleep. Clearing the SLPEN bit allows the module to continue to operate during Sleep.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will cease all functions and go into a very low-current consumption mode. The module will stop operation immediately and drive the minimum LCD voltage on both segment and common lines. Figure 27-20 shows this operation.

The LCD module can be configured to operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Clearing SLPEN and correctly configuring the LCD module clock will allow the LCD module to operate during Sleep. Setting SLPEN and correctly executing the LCD module shutdown will disable the LCD module during Sleep and save power.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will immediately cease all functions, drive the outputs to Vss and go into a very low-current mode. The SLEEP instruction should only be executed after the LCD module has been disabled and the current cycle completed, thus ensuring that there are no DC voltages on the glass. To disable the LCD module, clear the LCDEN bit. The LCD module will complete the disabling process after the current frame, clear the LCDA bit and optionally cause an interrupt.

The steps required to properly enter Sleep with the LCD disabled are:

- Clear LCDEN

- Wait for LCDA = 0 either by polling or by interrupt

- Execute SLEEP

If SLPEN = 0 and SLEEP is executed while the LCD module clock source is FOSC/4, then the LCD module will halt with the pin driving the last LCD voltage pattern. Prolonged exposure to a fixed LCD voltage pattern will cause damage to the LCD glass. To prevent LCD glass damage, either perform the proper LCD module shutdown prior to Sleep, or change the LCD module clock to allow the LCD module to continue operation during Sleep.

If a SLEEP instruction is executed and SLPEN = 0 and the LCD module clock is either T1OSC or LFINTOSC, the module will continue to display the current contents of the LCDDATA registers. While in Sleep, the LCD data cannot be changed. If the LCDIE bit is set, the device will wake from Sleep on the next LCD frame boundary. The LCD module current consumption will not decrease in this mode; however, the overall device power consumption will be lower due to the shutdown of the CPU and other peripherals. Table 27-8 shows the status of the LCD module during a Sleep while using each of the three available clock sources.