Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1933t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-3: PIC16(L)F1933 MEMORY MAP, BANKS 0-7

|      | BANK 0                                     | ``   | ,<br>BANK 1                                |      | BANK 2                                     |      | BANK 3                       |      | BANK 4                       |      | BANK 5                       |      | BANK 6                       |      | BANK 7                       |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|

| 000h | INDF0                                      | 080h | INDF0                                      | 100h | INDF0                                      | 180h | INDF0                        | 200h | INDF0                        | 280h | INDF0                        | 300h | INDF0                        | 380h | INDF0                        |

| 001h | INDF1                                      | 081h | INDF1                                      | 101h | INDF1                                      | 181h | INDF1                        | 201h | INDF1                        | 281h | INDF1                        | 301h | INDF1                        | 381h | INDF1                        |

| 002h | PCL                                        | 082h | PCL                                        | 102h | PCL                                        | 182h | PCL                          | 202h | PCL                          | 282h | PCL                          | 302h | PCL                          | 382h | PCL                          |

| 003h | STATUS                                     | 083h | STATUS                                     | 103h | STATUS                                     | 183h | STATUS                       | 203h | STATUS                       | 283h | STATUS                       | 303h | STATUS                       | 383h | STATUS                       |

| 004h | FSR0L                                      | 084h | FSR0L                                      | 104h | FSR0L                                      | 184h | FSR0L                        | 204h | FSR0L                        | 284h | FSR0L                        | 304h | FSR0L                        | 384h | FSR0L                        |

| 005h | FSR0H                                      | 085h | FSR0H                                      | 105h | FSR0H                                      | 185h | FSR0H                        | 205h | FSR0H                        | 285h | FSR0H                        | 305h | FSR0H                        | 385h | FSR0H                        |

| 006h | FSR1L                                      | 086h | FSR1L                                      | 106h | FSR1L                                      | 186h | FSR1L                        | 206h | FSR1L                        | 286h | FSR1L                        | 306h | FSR1L                        | 386h | FSR1L                        |

| 007h | FSR1H                                      | 087h | FSR1H                                      | 107h | FSR1H                                      | 187h | FSR1H                        | 207h | FSR1H                        | 287h | FSR1H                        | 307h | FSR1H                        | 387h | FSR1H                        |

| 008h | BSR                                        | 088h | BSR                                        | 108h | BSR                                        | 188h | BSR                          | 208h | BSR                          | 288h | BSR                          | 308h | BSR                          | 388h | BSR                          |

| 009h | WREG                                       | 089h | WREG                                       | 109h | WREG                                       | 189h | WREG                         | 209h | WREG                         | 289h | WREG                         | 309h | WREG                         | 389h | WREG                         |

| 00Ah | PCLATH                                     | 08Ah | PCLATH                                     | 10Ah | PCLATH                                     | 18Ah | PCLATH                       | 20Ah | PCLATH                       | 28Ah | PCLATH                       | 30Ah | PCLATH                       | 38Ah | PCLATH                       |

| 00Bh | INTCON                                     | 08Bh | INTCON                                     | 10Bh | INTCON                                     | 18Bh | INTCON                       | 20Bh | INTCON                       | 28Bh | INTCON                       | 30Bh | INTCON                       | 38Bh | INTCON                       |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                       | 20Ch | —                            | 28Ch | —                            | 30Ch | —                            | 38Ch | —                            |

| 00Dh | PORTB                                      | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                       | 20Dh | WPUB                         | 28Dh | —                            | 30Dh | _                            | 38Dh | —                            |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | —                            | 20Eh |                              | 28Eh | —                            | 30Eh | —                            | 38Eh | —                            |

| 00Fh |                                            | 08Fh | —                                          | 10Fh | _                                          | 18Fh | —                            | 20Fh |                              | 28Fh | —                            | 30Fh | —                            | 38Fh | —                            |

| 010h | PORTE                                      | 090h | TRISE                                      | 110h | —                                          | 190h | —                            | 210h | WPUE                         | 290h | —                            | 310h | —                            | 390h | —                            |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | EEADRL                       | 211h | SSPBUF                       | 291h | CCPR1L                       | 311h | CCPR3L                       | 391h | —                            |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | EEADRH                       | 212h | SSPADD                       | 292h | CCPR1H                       | 312h | CCPR3H                       | 392h |                              |

| 013h | PIR3                                       | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | EEDATL                       | 213h | SSPMSK                       | 293h | CCP1CON                      | 313h | CCP3CON                      | 393h | —                            |

| 014h |                                            | 094h | —                                          | 114h | CM2CON1                                    | 194h | EEDATH                       | 214h | SSPSTAT                      | 294h | PWM1CON                      | 314h | PWM3CON                      | 394h | IOCBP                        |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | EECON1                       | 215h | SSPCON1                      | 295h | CCP1AS                       | 315h | CCP3AS                       | 395h | IOCBN                        |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | EECON2                       | 216h | SSPCON2                      | 296h | PSTR1CON                     | 316h | PSTR3CON                     | 396h | IOCBF                        |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | —                            | 217h | SSPCON3                      | 297h | —                            | 317h | —                            | 397h | —                            |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h | DACCON0                                    | 198h | —                            | 218h | —                            | 298h | CCPR2L                       | 318h | CCPR4L                       | 398h | —                            |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | DACCON1                                    | 199h | RCREG                        | 219h |                              | 299h | CCPR2H                       | 319h | CCPR4H                       | 399h | —                            |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | SRCON0                                     | 19Ah | TXREG                        | 21Ah |                              | 29Ah | CCP2CON                      | 31Ah | CCP4CON                      | 39Ah | —                            |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh | SRCON1                                     | 19Bh | SPBRGL                       | 21Bh | _                            | 29Bh | PWM2CON                      | 31Bh | —                            | 39Bh | —                            |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | _                                          | 19Ch | SPBRGH                       | 21Ch | —                            | 29Ch | CCP2AS                       | 31Ch | CCPR5L                       | 39Ch | —                            |

| 01Dh | _                                          | 09Dh | ADCON0                                     | 11Dh | APFCON                                     | 19Dh | RCSTA                        | 21Dh |                              | 29Dh | PSTR2CON                     | 31Dh | CCPR5H                       | 39Dh | —                            |

| 01Eh | CPSCON0                                    | 09Eh | ADCON1                                     | 11Eh | _                                          | 19Eh | TXSTA                        | 21Eh |                              | 29Eh | CCPTMRS0                     | 31Eh | CCP5CON                      | 39Eh | —                            |

| 01Fh | CPSCON1                                    | 09Fh | —                                          | 11Fh | _                                          | 19Fh | BAUDCTR                      | 21Fh | _                            | 29Fh | CCPTMRS1                     | 31Fh | _                            | 39Fh | —                            |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                              | 220h |                              | 2A0h |                              | 320h |                              | 3A0h |                              |

|      | General<br>Purpose<br>Register<br>80 Bytes |      | General<br>Purpose<br>Register<br>80 Bytes |      | General<br>Purpose<br>Register<br>80 Bytes |      | Unimplemented<br>Read as '0' |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                              | 26Fh |                              | 2EFh |                              | 36Fh |                              | 3EFh |                              |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                              | 270h |                              | 2F0h |                              | 370h |                              | 3F0h |                              |

|      | Common RAM                                 |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh)       |      | Accesses<br>70h – 7Fh        |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                              | 27Fh |                              | 2FFh |                              | 37Fh |                              | 3FFh |                              |

**Legend:** = Unimplemented data memory locations, read as '0'.

| Address                | Name    | Bit 7        | Bit 6                                                    | Bit 5          | Bit 4           | Bit 3                   | Bit 2        | Bit 1      | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|--------------|----------------------------------------------------------|----------------|-----------------|-------------------------|--------------|------------|--------|----------------------|---------------------------------|

| Bank 0                 |         |              |                                                          |                |                 |                         |              |            |        | -                    |                                 |

| 000h <sup>(2)</sup>    | INDF0   |              | this location ical register)                             | uses contents  | s of FSR0H/F    | SR0L to addr            | ess data mer | mory       |        | XXXX XXXX            | XXXX XXXX                       |

| 001h <sup>(2)</sup>    | INDF1   |              | this location ical register)                             | uses contents  | s of FSR1H/F    | SR1L to addr            | ess data mer | mory       |        | XXXX XXXX            | XXXX XXXX                       |

| 002h <sup>(2)</sup>    | PCL     | Program Co   | ounter (PC) L                                            | east Significa | nt Byte         |                         |              |            |        | 0000 0000            | 0000 0000                       |

| 003h <sup>(2)</sup>    | STATUS  | _            | _                                                        | _              | TO              | PD                      | Z            | DC         | С      | 1 1000               | q quuu                          |

| 004h <sup>(2)</sup>    | FSR0L   | Indirect Dat | a Memory Ac                                              | dress 0 Low    | Pointer         | •                       |              | •          | •      | 0000 0000            | uuuu uuuu                       |

| 005h <sup>(2)</sup>    | FSR0H   | Indirect Dat | a Memory Ac                                              | ldress 0 High  | Pointer         |                         |              |            |        | 0000 0000            | 0000 0000                       |

| 006h <sup>(2)</sup>    | FSR1L   | Indirect Dat | a Memory Ac                                              | ldress 1 Low   | Pointer         |                         |              |            |        | 0000 0000            | uuuu uuuu                       |

| 007h <sup>(2)</sup>    | FSR1H   | Indirect Dat | a Memory Ac                                              | ldress 1 High  | Pointer         |                         |              |            |        | 0000 0000            | 0000 0000                       |

| 008h <sup>(2)</sup>    | BSR     | _            | — — — BSR<4:0>                                           |                |                 |                         |              |            |        | 0 0000               | 0 0000                          |

| 009h <sup>(2)</sup>    | WREG    | Working Re   | Working Register                                         |                |                 |                         |              |            |        |                      | uuuu uuuu                       |

| 00Ah <sup>(1, 2)</sup> | PCLATH  | _            | Write Buffer for the upper 7 bits of the Program Counter |                |                 |                         |              |            |        | -000 0000            | -000 0000                       |

| 00Bh <sup>(2)</sup>    | INTCON  | GIE          | PEIE                                                     | TMR0IE         | INTE            | IOCIE                   | TMR0IF       | INTF       | IOCIF  | 0000 0000            | 0000 0000                       |

| 00Ch                   | PORTA   | PORTA Dat    | PORTA Data Latch when written: PORTA pins when read      |                |                 |                         |              |            |        |                      |                                 |

| 00Dh                   | PORTB   | PORTB Da     | PORTB Data Latch when written: PORTB pins when read      |                |                 |                         |              |            |        |                      | uuuu uuuu                       |

| 00Eh                   | PORTC   | PORTC Da     | ta Latch whe                                             | n written: POF | RTC pins whe    | en read                 |              |            |        | XXXX XXXX            | uuuu uuuu                       |

| 00Fh                   | —       | Unimpleme    | nted                                                     |                |                 |                         |              |            |        | _                    | _                               |

| 010h                   | PORTE   | _            | _                                                        | —              | _               | RE3                     | _            | _          | _      | x                    | u                               |

| 011h                   | PIR1    | TMR1GIF      | ADIF                                                     | RCIF           | TXIF            | SSPIF                   | CCP1IF       | TMR2IF     | TMR1IF | 0000 0000            | 0000 0000                       |

| 012h                   | PIR2    | OSFIF        | C2IF                                                     | C1IF           | EEIF            | BCLIF                   | LCDIF        | —          | CCP2IF | 0000 00-0            | 0000 00-0                       |

| 013h                   | PIR3    | _            | CCP5IF                                                   | CCP4IF         | CCP3IF          | TMR6IF                  | _            | TMR4IF     | —      | -000 0-0-            | -000 0-0-                       |

| 014h                   | —       | Unimpleme    | nted                                                     |                |                 |                         |              |            |        | _                    | _                               |

| 015h                   | TMR0    | Timer0 Mod   | lule Register                                            |                |                 |                         |              |            |        | XXXX XXXX            | uuuu uuuu                       |

| 016h                   | TMR1L   | Holding Re   | gister for the                                           | Least Signific | ant Byte of th  | e 16-bit TMR            | 1 Register   |            |        | XXXX XXXX            | uuuu uuuu                       |

| 017h                   | TMR1H   | Holding Re   | gister for the                                           | Most Significa | ant Byte of the | e 16-bit TMR1           | Register     |            |        | XXXX XXXX            | uuuu uuuu                       |

| 018h                   | T1CON   | TMR10        | CS<1:0>                                                  | T1CKP          | S<1:0>          | T10SCEN                 | T1SYNC       | _          | TMR10N | 0000 00-0            | uuuu uu-u                       |

| 019h                   | T1GCON  | TMR1GE       | T1GPOL                                                   | T1GTM          | T1GSPM          | T <u>1GGO</u> /<br>DONE | T1GVAL       | T1GS       | S<1:0> | 0000 0x00            | uuuu uxuu                       |

| 01Ah                   | TMR2    | Timer 2 Mo   | dule Register                                            |                |                 |                         |              |            |        | 0000 0000            | 0000 0000                       |

| 01Bh                   | PR2     | Timer 2 Per  | riod Register                                            |                |                 |                         |              |            |        | 1111 1111            | 1111 1111                       |

| 01Ch                   | T2CON   | —            |                                                          | T2OUTI         | PS<3:0>         |                         | TMR2ON       | T2CKP      | S<1:0> | -000 0000            | -000 0000                       |

| 01Dh                   | —       | Unimpleme    | nted                                                     |                |                 |                         |              |            |        | _                    | _                               |

| 01Eh                   | CPSCON0 | CPSON        | CPSRM                                                    | _              | —               | CPSRNG1                 | CPSRNG0      | CPSOUT     | T0XCS  | 00 0000              | 00 0000                         |

| 01Fh                   | CPSCON1 | _            | —                                                        | _              | _               | _                       | (            | CPSCH<2:0> | >      | 000                  | 000                             |

| TABLE 3-9: | SPECIAL FUNCTION REGISTER SUMMARY  |

|------------|------------------------------------|

| IADLE 3-9. | SPECIAL FUNCTION REGISTER SUMIMART |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are 1: transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

3: Unimplemented, read as '1'.

#### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 4-3 **WDTE<1:0>:** Watchdog Timer Enable bit

- 11 = WDT enabled

- 10 = WDT enabled while running and disabled in Sleep

- 01 = WDT controlled by the SWDTEN bit in the WDTCON register

- 00 = WDT disabled

bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire data EEPROM will be erased when the code protection is turned off during

- 3: The entire program memory will be erased when the code protection is turned off.

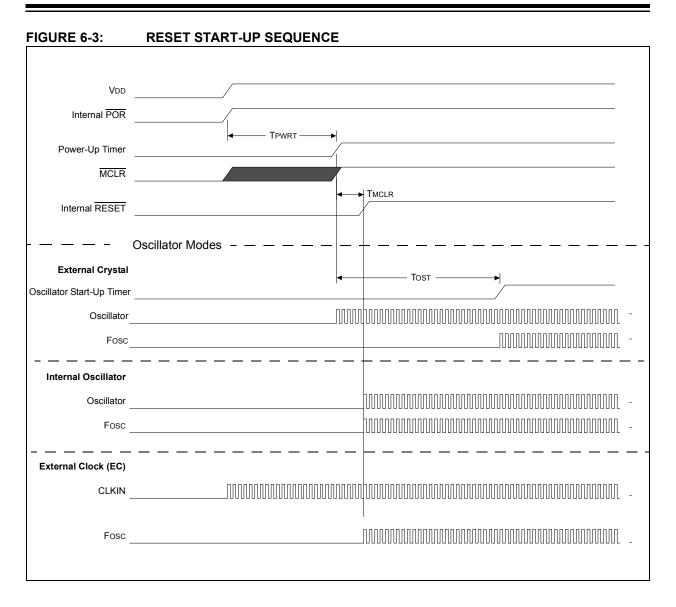

## 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 6-3 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 1.0        | Х      | Awake       | Active   | White for BOD ready (BODDDY = 1)                                    |

| 10         |        | Sleep       | Disabled | Waits for BOR ready (BORRDY = 1)                                    |

| 0.1        | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 01         | 0      | х           | Disabled | Regine immediately (RORDDY =)                                       |

| 00         | 00 X   |             | Disabled | Begins immediately (BORRDY = x)                                     |

#### TABLE 6-1: BOR OPERATING MODES

**Note 1:** In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

## 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

## 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

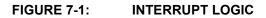

## 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

NOTES:

## 10.6 Register Definitions: Watchdog Control

| U-0             | U-0                       | R/W-0/0                                                                                                                | R/W-1/1        | R/W-0/0          | R/W-1/1      | R/W-1/1         | R/W-0/0      |  |  |  |  |  |

|-----------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------------|-----------------|--------------|--|--|--|--|--|

| —               |                           |                                                                                                                        |                | WDTPS<4:0>       |              |                 | SWDTEN       |  |  |  |  |  |

| oit 7           |                           |                                                                                                                        |                |                  |              |                 | bit          |  |  |  |  |  |

|                 |                           |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

| Legend:         |                           |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

| R = Readab      | le bit                    | W = Writable                                                                                                           | bit            | U = Unimpleme    |              |                 |              |  |  |  |  |  |

| u = Bit is un   | changed                   | x = Bit is unkr                                                                                                        | nown           | -m/n = Value a   | t POR and BO | OR/Value at all | other Resets |  |  |  |  |  |

| '1' = Bit is se | et                        | '0' = Bit is clea                                                                                                      | ared           |                  |              |                 |              |  |  |  |  |  |

| bit 7-6         | Unimpleme                 | nted: Read as '                                                                                                        | 0'             |                  |              |                 |              |  |  |  |  |  |

| bit 5-1         | -                         | Unimplemented: Read as '0'<br>WDTPS<4:0>: Watchdog Timer Period Select bits                                            |                |                  |              |                 |              |  |  |  |  |  |

|                 | Bit Value = Prescale Rate |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | eserved. Results                                                                                                       | s in minimum   | interval (1:32)  |              |                 |              |  |  |  |  |  |

|                 | •                         |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 | •                         |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 | •                         |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 | 10011 <b>= R</b>          | 10011 = Reserved. Results in minimum interval (1:32)                                                                   |                |                  |              |                 |              |  |  |  |  |  |

|                 | 10010 = <b>1</b> :        | 8388608 (2 <sup>23</sup> ) (                                                                                           | Interval 256s  | nominal)         |              |                 |              |  |  |  |  |  |

|                 | 10001 = <b>1</b> :        | 4194304 (2 <sup>22</sup> ) (<br>2097152 (2 <sup>21</sup> ) (                                                           | Interval 128s  | nominal)         |              |                 |              |  |  |  |  |  |

|                 | 10000 <b>= 1</b> :        | 2097152 (2 <sup>21</sup> ) (                                                                                           | Interval 64s r | iominal)         |              |                 |              |  |  |  |  |  |

|                 | 01111 <b>= 1</b> :        | $01111 = 1:1048576 (2^{20})$ (Interval 32s nominal)                                                                    |                |                  |              |                 |              |  |  |  |  |  |

|                 | 01110 = 1:                | $01110 = 1:524288 (2^{19}) (Interval 16s nominal)$<br>$01101 = 1:262144 (2^{18}) (Interval 8s nominal)$                |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 01101 = 1:262144 (2 <sup>18</sup> ) (Interval 8s nominal)<br>01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal) |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 01011 = 1:65536 (Interval 2s nominal) (Reset value)                                                                    |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 01010 = 1:32768 (Interval 1s nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)                                     |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 1 = 1.10304 (interval 512 fits forminal)<br>0 = 1.8192 (interval 256 ms nominal)                                       |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 1111 = 1:4096 (Interval 128 ms nominal)                                                                                |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 2048 (Interval 6                                                                                                       |                |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 1024 (Interval 3                                                                                                       |                | ,                |              |                 |              |  |  |  |  |  |

|                 |                           | 512 (Interval 16                                                                                                       |                |                  |              |                 |              |  |  |  |  |  |

|                 | 00011 = <b>1</b> :        | 256 (Interval 8 r                                                                                                      | ns nominal)    |                  |              |                 |              |  |  |  |  |  |

|                 |                           | 128 (Interval 4 r                                                                                                      |                |                  |              |                 |              |  |  |  |  |  |

|                 | 00001 = <b>1</b> :        | 64 (Interval 2 m                                                                                                       | s nominal)     |                  |              |                 |              |  |  |  |  |  |

|                 | 00000 = 1:                | 32 (Interval 1 m                                                                                                       | s nominal)     |                  |              |                 |              |  |  |  |  |  |

| bit 0           | SWDTEN: S                 | Software Enable/                                                                                                       | Disable for V  | /atchdog Timer b | it           |                 |              |  |  |  |  |  |

|                 | <u>If WDTE&lt;1:</u>      | <u> 00 = &lt;0</u> :                                                                                                   |                |                  |              |                 |              |  |  |  |  |  |

|                 | This bit is ig            |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 | If WDTE<1:0               |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 | 1 = WDT is                |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 | 0 = WDT is                |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

|                 | <u>If WDTE&lt;1:</u>      | 0 > = 1x                                                                                                               |                |                  |              |                 |              |  |  |  |  |  |

|                 | This bit is ig            |                                                                                                                        |                |                  |              |                 |              |  |  |  |  |  |

## REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| W-0/0            | W-0/0                      | W-0/0             | W-0/0     | W-0/0                                               | W-0/0 | W-0/0 | W-0/0 |  |  |

|------------------|----------------------------|-------------------|-----------|-----------------------------------------------------|-------|-------|-------|--|--|

|                  |                            |                   | EEPROM Co | ontrol Register 2                                   |       |       |       |  |  |

| bit 7            |                            |                   |           |                                                     |       |       | bit 0 |  |  |

|                  |                            |                   |           |                                                     |       |       |       |  |  |

| Legend:          |                            |                   |           |                                                     |       |       |       |  |  |

| R = Readable I   | lable bit W = Writable bit |                   |           | U = Unimplemented bit, read as '0'                  |       |       |       |  |  |

| S = Bit can only | y be set                   | x = Bit is unkr   | nown      | -n/n = Value at POR and BOR/Value at all other Rese |       |       |       |  |  |

| '1' = Bit is set |                            | '0' = Bit is clea | ared      |                                                     |       |       |       |  |  |

#### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to Section 11.2.2 "Writing to the Data EEPROM Memory" for more information.

## TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7       | Bit 6                                               | Bit 5  | Bit 4 | Bit 3               | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|--------|-------------|-----------------------------------------------------|--------|-------|---------------------|--------|-------|--------|---------------------|

| EECON1 | EEPGD       | CFGS                                                | LWLO   | FREE  | WRERR               | WREN   | WR    | RD     | 111                 |

| EECON2 |             | EEPROM Control Register 2 (not a physical register) |        |       |                     |        |       |        |                     |

| EEADRL | EEADRL<7:0> |                                                     |        |       |                     |        |       |        | 110                 |

| EEADRH | (1)         |                                                     |        | E     | EADRH<6:            | 0      |       |        | 110                 |

| EEDATL |             |                                                     |        | EEDAT | <sup>-</sup> L<7:0> |        |       |        | 110                 |

| EEDATH | _           | _                                                   |        |       | EEDAT               | H<5:0> |       |        | 110                 |

| INTCON | GIE         | PEIE                                                | TMR0IE | INTE  | IOCIE               | TMR0IF | INTF  | IOCIF  | 82                  |

| PIE2   | OSFIE       | C2IE                                                | C1IE   | EEIE  | BCLIE               | LCDIE  | —     | CCP2IE | 84                  |

| PIR2   | OSFIF       | C2IF                                                | C1IF   | EEIF  | BCLIF               | LCDIF  | _     | CCP2IF | 87                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Data EEPROM module. \* Page provides register information.

Note 1: Unimplemented, read as '1'.

## REGISTER 12-16: WPUE: WEAK PULL-UP PORTE REGISTER

| U-0              | U-0                                | U-0                       | U-0      | R/W-1/1                                               | U-0 | U-0 | U-0   |  |  |  |

|------------------|------------------------------------|---------------------------|----------|-------------------------------------------------------|-----|-----|-------|--|--|--|

| _                | _                                  | _                         | _        | WPUE3                                                 | _   | _   | —     |  |  |  |

| bit 7            |                                    | ·                         |          | •                                                     |     |     | bit 0 |  |  |  |

|                  |                                    |                           |          |                                                       |     |     |       |  |  |  |

| Legend:          |                                    |                           |          |                                                       |     |     |       |  |  |  |

| R = Readable bit |                                    | W = Writable              | bit      | U = Unimplemented bit, read as '0'                    |     |     |       |  |  |  |

| u = Bit is ur    | nchanged                           | x = Bit is unkr           | nown     | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |  |  |

| '1' = Bit is s   | et                                 | '0' = Bit is clea         | ared     |                                                       |     |     |       |  |  |  |

|                  |                                    |                           |          |                                                       |     |     |       |  |  |  |

| bit 7-4          | Unimplemer                         | nted: Read as '           | כי       |                                                       |     |     |       |  |  |  |

| bit 3            | <b>WPUE3:</b> Wea<br>1 = Pull-up e | ak Pull-up Regi<br>nabled | ster bit |                                                       |     |     |       |  |  |  |

0 = Pull-up disabled

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

## TABLE 12-9: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name    | Bit 7 | Bit 6 | Bit 5                 | Bit 4 | Bit 3      | Bit 2   | Bit 1 | Bit 0     | Register<br>on Page |

|---------|-------|-------|-----------------------|-------|------------|---------|-------|-----------|---------------------|

| ADCON0  |       |       | CHS<4:0> GO/DONE ADON |       |            |         |       | 143       |                     |

| CCPxCON | PxM<  | <1:0> | DCxB<1:0>             |       | CCPxM<3:0> |         |       |           | 214                 |

| LCDCON  | LCDEN | SLPEN | WERR                  | _     | CS<        | CS<1:0> |       | LMUX<1:0> |                     |

| LCDSE2  | SE23  | SE22  | SE21                  | SE20  | SE19       | SE18    | SE17  | SE16      | 319                 |

| PORTE   | _     | _     | _                     | _     | RE3        | —       | _     | _         | 127                 |

| TRISE   | _     | _     | _                     | _     | (3)        | _       | _     |           | 127                 |

| WPUE    | _     | _     |                       |       | WPUE3      | _       | _     | _         | 128                 |

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Unimplemented, read as '1'.

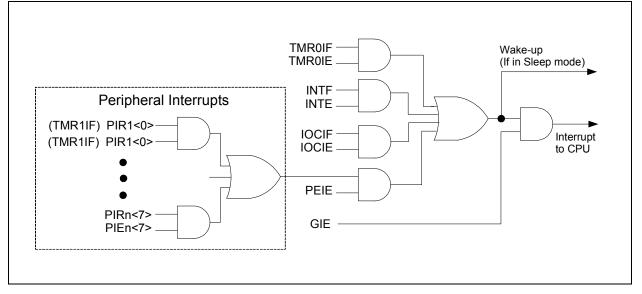

## 17.4 Low-Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSOURCE+), or the negative voltage source, (VSOURCE-) can be disabled.

The negative voltage source is disabled by setting the DACLPS bit in the DACCON0 register. Clearing the DACLPS bit in the DACCON0 register disables the positive voltage source.

#### 17.4.1 OUTPUT CLAMPED TO POSITIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE+ with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- Setting the DACLPS bit in the DACCON0 register.

- Configuring the DACPSS bits to the proper positive source.

- Configuring the DACR<4:0> bits to '11111' in the DACCON1 register.

This is also the method used to output the voltage level from the FVR to an output pin. See **Section 17.5 "Operation During Sleep"** for more information.

Reference Figure 17-3 for output clamping examples.

## 17.4.2 OUTPUT CLAMPED TO NEGATIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE- with the least amount of power consumption by performing the following:

- Clearing the DACEN bit in the DACCON0 register.

- Clearing the DACLPS bit in the DACCON0 register.

- Configuring the DACNSS bits to the proper negative source.

- Configuring the DACR<4:0> bits to '00000' in the DACCON1 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

Reference Figure 17-3 for output clamping examples.

## FIGURE 17-3: OUTPUT VOLTAGE CLAMPING EXAMPLES

## 17.5 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 17.6 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DACOUT pin.

- The DACR<4:0> range select bits are cleared.

- © 2011-2012 Microchip Technology Inc.

## 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

## 21.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

## 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |  |

|------------|--------|-----|------------------|--|

| $\uparrow$ | 0      | 0   | Counts           |  |

| $\uparrow$ | 0      | 1   | Holds Count      |  |

| $\uparrow$ | 1      | 0   | Holds Count      |  |

| 1          | 1      | 1   | Counts           |  |

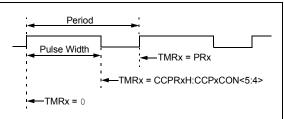

## 23.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 23-3 shows a typical waveform of the PWM signal.

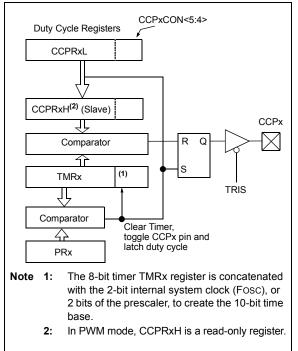

#### 23.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for CCP modules ECCP1, ECCP2, ECCP3, CCP4 and CCP5.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- CCPRxL registers

- · CCPxCON registers

Figure 23-4 shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- **2:** Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### FIGURE 23-3: CCP PWM OUTPUT SIGNAL

SIMPLIFIED PWM BLOCK DIAGRAM

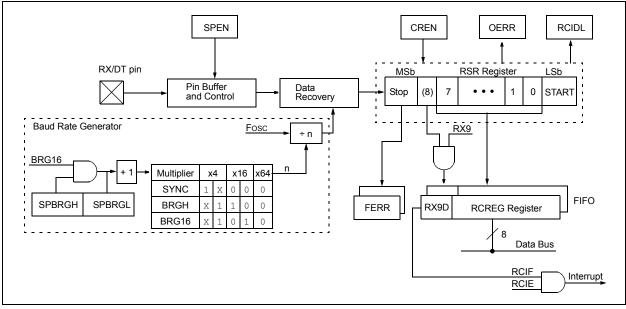

## FIGURE 25-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 25-1, Register 25-2 and Register 25-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

### REGISTER 27-5: LCDSEn: LCD SEGMENT ENABLE REGISTERS

| R/W-0/0                                 | R/W-0/0 | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------------------------|---------|-------------------------------------------------------|------------------------------------|---------|---------|---------|---------|

| SEn                                     | SEn     | SEn                                                   | SEn                                | SEn     | SEn     | SEn     | SEn     |

| bit 7                                   |         |                                                       |                                    |         |         |         | bit 0   |

|                                         |         |                                                       |                                    |         |         |         |         |

| Legend:                                 |         |                                                       |                                    |         |         |         |         |

| R = Readable bit W = Writable bit       |         |                                                       | U = Unimplemented bit, read as '0' |         |         |         |         |

| u = Bit is unchanged x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |         |

| '1' = Bit is set                        |         | '0' = Bit is clea                                     | ared                               |         |         |         |         |

bit 7-0 SEn: Segment Enable bits 1 = Segment function of the pin is enabled 0 = I/O function of the pin is enabled

#### REGISTER 27-6: LCDDATAn: LCD DATA REGISTERS

| R/W-x/u     | R/W-x/u   | R/W-x/u   | R/W-x/u   | R/W-x/u   | R/W-x/u   | R/W-x/u   | R/W-x/u   |

|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| SEGx-COMy   | SEGx-COMy | SEGx-COMy | SEGx-COMy | SEGx-COMy | SEGx-COMy | SEGx-COMy | SEGx-COMy |

| bit 7 bit 0 |           |           |           |           |           |           |           |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SEGx-COMy: Pixel On bits

1 = Pixel on (dark)

0 = Pixel off (clear)

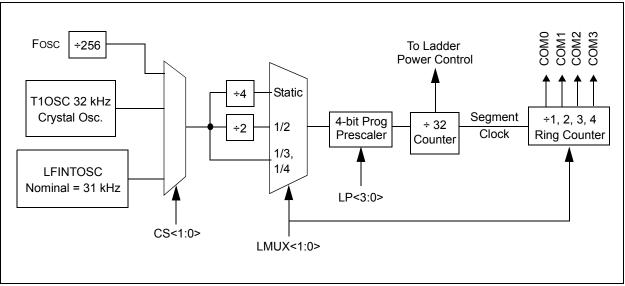

## 27.3 LCD Clock Source Selection

The LCD module has three possible clock sources:

- Fosc/256

- T10SC

- LFINTOSC

The first clock source is the system clock divided by 256 (Fosc/256). This divider ratio is chosen to provide about 1 kHz output when the system clock is 8 MHz. The divider is not programmable. Instead, the LCD prescaler bits LP<3:0> of the LCDPS register are used to set the LCD frame clock rate.

The second clock source is the T1OSC. This also gives about 1 kHz when a 32.768 kHz crystal is used with the Timer1 oscillator. To use the Timer1 oscillator as a clock source, the T1OSCEN bit of the T1CON register should be set.

The third clock source is the 31 kHz LFINTOSC, which provides approximately 1 kHz output.

The second and third clock sources may be used to continue running the LCD while the processor is in Sleep.

Using bits CS<1:0> of the LCDCON register can select any of these clock sources.

#### 27.3.1 LCD PRESCALER

A 4-bit counter is available as a prescaler for the LCD clock. The prescaler is not directly readable or writable; its value is set by the LP<3:0> bits of the LCDPS register, which determine the prescaler assignment and prescale ratio.

The prescale values are selectable from 1:1 through 1:16.

## FIGURE 27-2: LCD CLOCK GENERATION

## 32.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 32.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 32.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 32.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

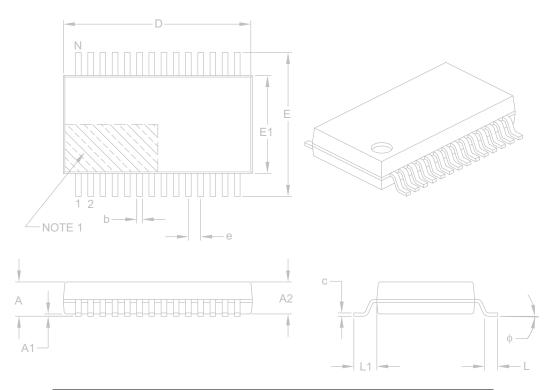

For the most current package drawings, please see the Microchip Packaging Specification located at

### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS | 6     |  |

|--------------------------|------------------|----------|-------------|-------|--|

| Dimensio                 | Dimension Limits |          | NOM         | MAX   |  |

| Number of Pins           | Ν                | 28       |             |       |  |

| Pitch                    | е                |          | 0.65 BSC    |       |  |

| Overall Height           | Α                | -        | -           | 2.00  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85  |  |

| Standoff                 | A1               | 0.05     | -           | _     |  |

| Overall Width            | E                | 7.40     | 7.80        | 8.20  |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60  |  |

| Overall Length           | D                | 9.90     | 10.20       | 10.50 |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95  |  |

| Footprint                | L1               | 1.25 REF |             |       |  |

| Lead Thickness           | с                | 0.09     | -           | 0.25  |  |

| Foot Angle               | ф                | 0°       | 4°          | 8°    |  |

| Lead Width               | b                | 0.22     | -           | 0.38  |  |

## Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- $\label{eq:BSC:Basic Dimension.} Theoretically exact value shown without tolerances.$

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B