Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | e200z4                                                       |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 150MHz                                                       |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                            |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | 84                                                           |

| Program Memory Size        | 4MB (4M x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 192K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                |

| Data Converters            | A/D 40x12b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 176-LQFP                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5644af0mlu1r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.3 Device comparison

Table 1 summarizes the MPC5644A and compares it to the MPC5634M.

Table 1. MPC5644A, MPC5634M and MPC5642A comparison

| Feature                      | MPC5644A                   | MPC5634M                 | MPC5642A                   |  |  |  |  |  |  |  |

|------------------------------|----------------------------|--------------------------|----------------------------|--|--|--|--|--|--|--|

| Process                      |                            | 90 nm                    |                            |  |  |  |  |  |  |  |

| Core                         | e200z4                     | e200z3                   | e200z4                     |  |  |  |  |  |  |  |

| SIMD                         |                            | Yes                      |                            |  |  |  |  |  |  |  |

| VLE                          | Yes                        |                          |                            |  |  |  |  |  |  |  |

| Cache                        | 8 KB instruction           | No                       | 8 KB instruction           |  |  |  |  |  |  |  |

| Non-Maskable Interrupt (NMI) |                            | NMI & Critical Interrupt |                            |  |  |  |  |  |  |  |

| MMU                          | 24 entry                   | 16 entry                 | 24 entry                   |  |  |  |  |  |  |  |

| MPU                          | 16 entry                   | No                       | 16 entry                   |  |  |  |  |  |  |  |

| Crossbar switch              | 5 × 4                      | 3 × 4                    | 4 × 4                      |  |  |  |  |  |  |  |

| Core performance             | 0–150 MHz                  | 0–80 MHz                 | 0–150 MHz                  |  |  |  |  |  |  |  |

| Windowing software watchdog  | Yes                        |                          |                            |  |  |  |  |  |  |  |

| Core Nexus                   | Class 3+                   | Class 2+                 | Class 3+                   |  |  |  |  |  |  |  |

| SRAM                         | 192 KB                     | 94 KB                    | 128 KB                     |  |  |  |  |  |  |  |

| Flash                        | 4 MB                       | 1.5 MB                   | 2 MB                       |  |  |  |  |  |  |  |

| Flash fetch accelerator      | 4 × 256-bit                | 4 × 256-bit 4 × 128-bit  |                            |  |  |  |  |  |  |  |

| External bus                 | 16-bit (incl 32-bit muxed) | None                     |                            |  |  |  |  |  |  |  |

| Calibration bus              | 16-bit (incl 32-bit muxed) | 16-bit                   | 16-bit (incl 32-bit muxed) |  |  |  |  |  |  |  |

| DMA                          | 64 ch.                     | 32 ch.                   | 64 ch.                     |  |  |  |  |  |  |  |

| DMA Nexus                    |                            | None                     |                            |  |  |  |  |  |  |  |

| Serial                       | 3                          | 2                        | 3                          |  |  |  |  |  |  |  |

| eSCI_A                       |                            | Yes (MSC Uplink)         |                            |  |  |  |  |  |  |  |

| eSCI_B                       |                            | Yes (MSC Uplink)         |                            |  |  |  |  |  |  |  |

| eSCI_C                       | Yes                        | No                       | Yes                        |  |  |  |  |  |  |  |

| CAN                          | 3                          | 2                        | 3                          |  |  |  |  |  |  |  |

| CAN_A                        |                            | 64 buf                   | •                          |  |  |  |  |  |  |  |

| CAN_B                        | 64 buf                     | No                       | 64 buf                     |  |  |  |  |  |  |  |

| CAN_C                        | 64 buf                     | 32 buf                   | 64 buf                     |  |  |  |  |  |  |  |

| SPI                          | 3                          | 2                        | 3                          |  |  |  |  |  |  |  |

# 1.4.3 eDMA

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 64 programmable channels, with minimal intervention from the host processor. The hardware micro-architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is utilized to minimize the overall block size. The eDMA module provides the following features:

- All data movement via dual-address transfers: read from source, write to destination

- · Programmable source and destination addresses, transfer size, plus support for enhanced addressing modes

- Transfer control descriptor organized to support two-deep, nested transfer operations

- An inner data transfer loop defined by a "minor" byte transfer count

- An outer data transfer loop defined by a "major" iteration count

- Channel activation via one of three methods:

- Explicit software initiation

- Initiation via a channel-to-channel linking mechanism for continuous transfers

- Peripheral-paced hardware requests (one per channel)

- Support for fixed-priority and round-robin channel arbitration

- Channel completion reported via optional interrupt requests

- One interrupt per channel, optionally asserted at completion of major iteration count

- Error termination interrupts optionally enabled

- Support for scatter/gather DMA processing

- Ability to suspend channel transfers by a higher priority channel

## 1.4.4 Interrupt controller

The INTC (interrupt controller) provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource cannot preempt each other.

The INTC provides the following features:

- 9-bit vector addresses

- Unique vector for each interrupt request source

- · Hardware connection to processor or read from register

- Each interrupt source can assigned a specific priority by software

- · Preemptive prioritized interrupt requests to processor

- ISR at a higher priority preempts executing ISRs or tasks at lower priorities

- Automatic pushing or popping of preempted priority to or from a LIFO

- Ability to modify the ISR or task priority to implement the priority ceiling protocol for accessing shared resources

- · Low latency-three clocks from receipt of interrupt request from peripheral to interrupt request to processor

This device also includes a non-maskable interrupt (NMI) pin that bypasses the INTC and multiplexing logic.

#### MPC5644A Microcontroller Data Sheet, Rev. 7

and 128- and 256-bit read data interfaces to flash memory. The module contains a prefetch controller which prefetches sequential lines of data from the flash array into the buffers. Prefetch buffer hits allow no-wait responses.

The flash memory provides the following features:

- Supports a 64-bit data bus for instruction fetch, CPU loads and DMA access. Byte, halfword, word and doubleword reads are supported. Only aligned word and doubleword writes are supported.

- Fetch Accelerator

- Architected to optimize the performance of the flash

- Configurable read buffering and line prefetch support

- Four-entry 256-bit wide line read buffer

- Prefetch controller

- Hardware and software configurable read and write access protections on a per-master basis

- Interface to the flash array controller pipelined with a depth of one, allowing overlapped accesses to proceed in parallel for interleaved or pipelined flash array designs

- Configurable access timing usable in a wide range of system frequencies

- Multiple-mapping support and mapping-based block access timing (0-31 additional cycles) usable for emulation of other memory types

- Software programmable block program/erase restriction control

- Erase of selected block(s)

- Read page size of 128 bits (four words)

- ECC with single-bit correction, double-bit detection

- Program page size of 128 bits (four words) to accelerate programming

- ECC single-bit error corrections are visible to software

- Minimum program size is two consecutive 32-bit words, aligned on a 0-modulo-8 byte address, due to ECC

- Embedded hardware program and erase algorithm

- Erase suspend, program suspend and erase-suspended program

- Shadow information stored in non-volatile shadow block

- Independent program/erase of the shadow block

# 1.4.9 BAM

The BAM (Boot Assist Module) is a block of read-only memory that is programmed once by Freescale and is identical for all MPC5644A MCUs. The BAM program is executed every time the MCU is powered-on or reset in normal mode. The BAM supports different modes of booting. They are:

- Booting from internal flash memory

- Serial boot loading (A program is downloaded into RAM via eSCI or the FlexCAN and then executed)

- Booting from external memory on external bus

The BAM also reads the reset configuration half word (RCHW) from internal flash memory and configures the MPC5644A hardware accordingly. The BAM provides the following features:

- Sets up MMU to cover all resources and mapping of all physical addresses to logical addresses with minimum address translation

- Sets up MMU to allow user boot code to execute as either Power Architecture embedded category (default) or as Freescale VLE code

- Location and detection of user boot code

- Automatic switch to serial boot mode if internal flash is blank or invalid

- Supports user programmable 64-bit password protection for serial boot mode

- Supports serial bootloading via FlexCAN bus and eSCI using Freescale protocol

#### MPC5644A Microcontroller Data Sheet, Rev. 7

- 64-bit Censorship password register

- If the external tool writes a 64-bit password that matches the Serial Boot password stored in the internal flash shadow row, Censorship is disabled until the next system reset.

# 1.4.27 Development Trigger Semaphore (DTS)

MPC5644A devices include a system development feature, the Development Trigger Semaphore (DTS) module, that enables software to signal an external tool by driving a persistent (affected only by reset or an external tool) signal on an external device pin. There is a variety of ways this module can be used, including as a component of an external real-time data acquisition system

# 1.5 MPC5644A series architecture

## 1.5.1 Block diagram

Figure 1 shows a top-level block diagram of the MPC5644A series.

# 2 Pinout and signal description

This section contains the pinouts for all production packages for the MPC5644A family of devices.

### CAUTION

Any pins labeled "NC" are to be left unconnected. Any connection to an external circuit or voltage may cause unpredictable device behavior or damage.

|                    |                                                    | Р                   | PCR                      |                   | 1/2         | Valte 5 /                                       | St           | atus <sup>7</sup>  |     | Packag | je pin # |  |

|--------------------|----------------------------------------------------|---------------------|--------------------------|-------------------|-------------|-------------------------------------------------|--------------|--------------------|-----|--------|----------|--|

| Name               | Function <sup>1</sup>                              | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup>  | l/O<br>Type | Voltage <sup>5</sup> /<br>Pad Type <sup>6</sup> | During Reset | After<br>Reset     | 176 | 208    | 324      |  |

| CAL_WE[1]/BE[1]    | Calibration write/byte enable                      | Р                   | 01                       | 342               | 0           | VDDE12<br>Fast                                  |              | _/_                | —   | -      | _        |  |

| CAL_OE             | Calibration output enable                          | Р                   | 01                       | 342               | 0           | VDDE12<br>Fast                                  |              | _/_                | —   | _      | _        |  |

| CAL_TS<br>CAL_ALE  | Calibration transfer start<br>Address Latch Enable | P<br>A              | 01<br>10                 | 343               | 0<br>0      | VDDE12<br>Fast                                  |              | _/_                | —   | _      | _        |  |

| CAL_MDO[4]         | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | —                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[4] / —     | —   | -      | _        |  |

| CAL_MDO[5]         | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | —                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[5] / —     | —   | -      | _        |  |

| CAL_MDO[6]         | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | —                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[6] /       | —   |        |          |  |

| CAL_MDO[7]         | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | —                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[7] / —     | —   |        |          |  |

| CAL_MDO[8]         | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | _                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[8] /       | —   |        |          |  |

| CAL_MDO[9]         | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | _                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[9] /       | —   | _      | _        |  |

| CAL_MDO[10]        | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | —                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[10] /<br>  | —   | -      | _        |  |

| CAL_MDO[11]        | Calibration Nexus Message<br>Data Out              | Р                   | 01                       | —                 | 0           | VDDE12<br>Fast                                  | —            | CAL_MDO[11] /<br>— | —   | -      | _        |  |

|                    |                                                    | •                   |                          |                   | NE          | xus                                             |              | ·                  | •   |        |          |  |

| EVTI               | Nexus event in                                     | Р                   | 01                       | 231               | I           | VDDEH7<br>MultiV <sup>12,14</sup>               | — / Up       | EVTI / Up          | 116 | E15    | H20      |  |

| EVTO               | Nexus event out                                    | Р                   | 01                       | 227               | 0           | VDDEH7<br>MultiV <sup>12,14,15</sup>            | —            | EVTO / —           | 120 | D15    | 5 G20    |  |

| МСКО               | Nexus message clock out                            | Р                   | -                        | 219 <sup>11</sup> | 0           | VRC33<br>Fast                                   | _            | МСКО / —           | 14  | F15    | F15 F1   |  |

| MDO0 <sup>16</sup> | Nexus message data out                             | Р                   | 01                       | 220               | 0           | VRC33<br>Fast                                   | —            | MDO[0] / —         | 17  | A14    | A14 F3   |  |

| MDO1 <sup>16</sup> | Nexus message data out                             | Р                   | 01                       | 221               | 0           | VRC33<br>Fast                                   | —            | MDO[1] /           | 18  | B14    | G2       |  |

39

|                                                           |                                                                                                        | Р                   | PCR                      |                                   | I/O           | Voltage <sup>5</sup> /            | Sta          | tus <sup>7</sup> | Package pin # |     |     |  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-----------------------------------|---------------|-----------------------------------|--------------|------------------|---------------|-----|-----|--|

| Name                                                      | Function <sup>1</sup>                                                                                  | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup>                  | 1/О<br>Туре   | Pad Type <sup>6</sup>             | During Reset | After<br>Reset   | 176           | 208 | 324 |  |

| MDO2 <sup>16</sup>                                        | Nexus message data out                                                                                 | Ρ                   | 01                       | 222                               | 0             | VRC33<br>Fast                     | —            | MDO[2] / —       | 19            | A13 | G3  |  |

| MDO3 <sup>16</sup>                                        | Nexus message data out                                                                                 | Р                   | 01                       | 223                               | 0             | VRC33<br>Fast                     | —            | MDO[3] / —       | 20            | B13 | G4  |  |

| MDO4 <sup>16</sup><br>ETPUA2_O <sup>8</sup><br>GPIO[75]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO[                                        | P<br>A1<br>G        | 01<br>10<br>00           | 75                                | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>         | 126           | P10 | B19 |  |

| MDO5 <sup>16</sup><br>ETPUA4_O <sup>8</sup><br>GPIO[76]   | Nexus message data out<br>eTPU A channel (output only)P0176OVDDEH7<br>O———GPIOG00I/OI/OI/OI/OI/OI/OI/O |                     |                          | <i>_/_</i>                        | 129           | T10                               | B20          |                  |               |     |     |  |

| MDO6 <sup>16</sup><br>ETPUA13_O <sup>8</sup><br>GPIO[77]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                         | P<br>A1<br>G        | 01<br>10<br>00           | 77                                | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>         | 135           | T11 | C18 |  |

| MDO7 <sup>16</sup><br>ETPUA19_O <sup>8</sup><br>GPIO[78]  | eTPU A channel (output only) A1 10 0                                                                   |                     | 0<br>0<br>I/0            | VDDEH7<br>MultiV <sup>12,14</sup> | —             | <i>/</i>                          | 136          | N11              | B18           |     |     |  |

| MDO8 <sup>16</sup><br>ETPUA21_O <sup>8</sup><br>GPIO[79]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                         | P<br>A1<br>G        | 01<br>10<br>00           | 79                                | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>         | 137           | P11 | A18 |  |

| MDO9 <sup>16</sup><br>ETPUA25_O <sup>8</sup><br>GPIO[80]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                         | P<br>A1<br>G        | 01<br>10<br>00           | 80                                | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>         | 139           | Τ7  | D18 |  |

| MDO10 <sup>16</sup><br>ETPUA27_O <sup>8</sup><br>GPIO[81] | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                         | P<br>A1<br>G        | 01<br>10<br>00           | 81                                | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>         | 134           | R10 | A19 |  |

| MDO11 <sup>16</sup><br>ETPUA29_O <sup>8</sup><br>GPIO[82] | Nexus message data out<br>eTPU A channel (output only)<br>GPIO[82]                                     | P<br>A1<br>G        | 01<br>10<br>00           | 82                                | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>         | 124           | P9  | C19 |  |

| MSEO[0] <sup>16</sup>                                     | Nexus message start/end out                                                                            | Р                   | 01                       | 224                               | 0             | VDDEH7<br>MultiV <sup>12,14</sup> | —            | MSEO[0] / —      | 118           | C15 | G21 |  |

| MSEO[1] <sup>16</sup>                                     | Nexus message start/end out                                                                            | Р                   | 01                       | 225                               | 0             | VDDEH7<br>MultiV <sup>12,14</sup> | —            | MSEO[1] /        | 117           | E16 | G22 |  |

| RDY                                                       | Nexus ready output                                                                                     | Р                   | 01                       | 226                               | 0             | VDDEH7<br>MultiV <sup>12,14</sup> | —            | _                | —             | -   | G19 |  |

|                                                                                                                                          |                                                                        | Р            | PCR                      |                  | I/O             | Voltage <sup>5</sup> / | Stat         | us <sup>7</sup> | Package pin # |     |     |  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|--------------------------|------------------|-----------------|------------------------|--------------|-----------------|---------------|-----|-----|--|

| Name                                                                                                                                     | Function <sup>1</sup>                                                  |              | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | Туре            | Pad Type <sup>6</sup>  | During Reset | After<br>Reset  | 176           | 208 | 324 |  |

| CS[3]<br>DSPI_D_SIN<br>GPIO[99]                                                                                                          | —<br>DSPI D data input<br>GPIO                                         | —<br>A1<br>G |                          | 99               | —<br>I<br>I/O   | VDDEH7<br>Medium       | — / Up       | — / Up          | 142           | H13 | B15 |  |

| DSPI_A_PCS[4] <sup>17</sup><br>DSPI_D_SOUT<br>GPIO[100]                                                                                  | —<br>DSPI D data output<br>GPIO                                        | —<br>A1<br>G | —<br>10<br>00            | 100              | 0<br>I/O        | VDDEH7<br>Medium       | — / Up       | — / Up          | —             | _   | B16 |  |

| DSPI_A_PCS[5] <sup>17</sup><br>DSPI_B_PCS[3]<br>GPIO[101]                                                                                | —<br>DSPI B peripheral chip select<br>GPIO                             | —<br>A1<br>G | —<br>10<br>00            | 101              | 0<br>I/O        | VDDEH7<br>Medium       | — / Up       | — / Up          | —             | _   | A16 |  |

| DSPI_B_SCK<br>DSPI_C_PCS[1]<br>GPIO[102]                                                                                                 | SPI_C_PCS[1] DSPI C peripheral chip select                             |              | 01<br>10<br>00           | 102              | I/O<br>O<br>I/O | VDDEH6<br>Medium       | — / Up       | — / Up          | 106           | J16 | K21 |  |

| DSPI_B_SIN     DSPI B data input       DSPI_C_PCS[2]     DSPI C peripheral chip select       GPI0[103]     GPIO                          |                                                                        | P<br>A1<br>G | 01<br>10<br>00           | 103              | <br>0<br> /0    | VDDEH6<br>Medium       | — / Up       | — / Up          | 112           | G15 | H22 |  |

| DSPI_B_SOUT<br>DSPI_C_PCS[5]<br>GPIO[104]                                                                                                | DSPI B data output<br>DSPI C peripheral chip select<br>GPIO            | P<br>A1<br>G | 01<br>10<br>00           | 104              | 0<br>0<br>I/O   | VDDEH6<br>Medium       | — / Up       | — / Up          | 113           | G13 | J19 |  |

| DSPI_B_PCS[0]<br>DSPI_D_PCS[2]<br>GPIO[105]                                                                                              | DSPI B peripheral chip select<br>DSPI D peripheral chip select<br>GPIO | P<br>A1<br>G | 01<br>10<br>00           | 105              | I/O<br>O<br>I/O | VDDEH6<br>Medium       | — / Up       | — / Up          | 111           | G16 | J21 |  |

| DSPI_B_PCS[1]<br>DSPI_D_PCS[0]<br>GPIO[106]                                                                                              | DSPI B peripheral chip select<br>DSPI D peripheral chip select<br>GPIO | P<br>A1<br>G | 01<br>10<br>00           | 106              | 0<br>I/O<br>I/O | VDDEH6<br>Medium       | — / Up       | — / Up          | 109           | H16 | J22 |  |

| DSPI_B_PCS[2]<br>DSPI_C_SOUT<br>GPIO[107]                                                                                                | DSPI B peripheral chip select<br>DSPI C data output<br>GPIO            | P<br>A1<br>G | 01<br>10<br>00           | 107              | 0<br>0<br>I/O   | VDDEH6<br>Medium       | — / Up       | — / Up          | 107           | H15 | K22 |  |

| DSPI_B_PCS[3]<br>DSPI_C_SIN<br>GPIO[108]                                                                                                 | DSPI B peripheral chip select<br>DSPI C data input<br>GPIO             | P<br>A1<br>G | 01<br>10<br>00           | 108              | 0<br> <br> /0   | VDDEH6<br>Medium       | — / Up       | — / Up          | 114           | G14 | J20 |  |

| DSPI_B_PCS[4]<br>DSPI_C_SCK<br>GPIO[109]                                                                                                 | DSPI B peripheral chip select<br>SPI clock pin for DSPI module<br>GPIO | P<br>A1<br>G | 01<br>10<br>00           | 109              | 0<br>I/O<br>I/O | VDDEH6<br>Medium       | — / Up       | — / Up          | 105           | H14 | K20 |  |

| DSPI_B_PCS[5]       DSPI B peripheral chip select         DSPI_C_PCS[0]       DSPI C peripheral chip select         GPIO[110]       GPIO |                                                                        | P<br>A1<br>G | 01<br>10<br>00           | 110              | 0<br>I/O<br>I/O | VDDEH6<br>Medium       | — / Up       | — / Up          | 104           | J13 | L19 |  |

|                                |                                                        | Р                    | PCR                      |                  | 1/0          | Voltage <sup>5</sup> /<br>Pad Type <sup>6</sup><br>VDDA<br>Analog | Sta          | tus <sup>7</sup> | Package pin # |        |      |  |

|--------------------------------|--------------------------------------------------------|----------------------|--------------------------|------------------|--------------|-------------------------------------------------------------------|--------------|------------------|---------------|--------|------|--|

| Name                           | Function <sup>1</sup>                                  | A<br>G <sup>2</sup>  | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | l/O<br>Type  |                                                                   | During Reset | After<br>Reset   | 176           | 208    | 324  |  |

| AN29                           | Single-ended Analog Input                              | Р                    | _                        | —                | I            |                                                                   | I / —        | AN[29] / —       | —             | —      | C11  |  |

| AN30                           | Single-ended Analog Input                              | Ρ                    | _                        | _                | I            | VDDA<br>Analog                                                    | 1/—          | AN[30] / —       | 155           | D9     | B11  |  |

| AN31                           | Single-ended Analog Input                              | Р                    |                          | _                | I            | VDDA<br>Analog                                                    | 1/—          | AN[31] / —       | 154           | D10    | D12  |  |

| AN32                           | Single-ended Analog Input                              | Ρ                    | _                        | _                | I            | VDDA<br>Analog                                                    | 1/—          | AN[32] / —       | 153           | C10    | C12  |  |

| AN33                           | Single-ended Analog Input                              | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I / —        | AN[33] / —       | 152           | C11    | B12  |  |

| AN34                           | Single-ended Analog Input                              | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I/—          | AN[34] / —       | 151           | C5     | A12  |  |

| AN35                           | Single-ended Analog Input                              | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I / —        | AN[35] / —       | 150           | D11    | D13  |  |

| AN36                           | Single-ended Analog Input                              | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I / —        | AN[36] / —       | 174           | F4     | B5   |  |

| AN37                           | Single-ended Analog Input                              | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I / —        | AN[37] / —       | 175           | E3     | A5   |  |

| AN38                           | Single-ended Analog Input                              | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I / —        | AN[38] / —       | -             | —      | D3   |  |

| AN39                           | Single-ended Analog Input                              | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I / —        | AN[39] / —       | 8             | D2     | D2   |  |

| VRH                            | Voltage Reference High                                 | Р                    | —                        | _                | I            | VDDA<br>—                                                         | 1/—          | VRH              | 163 A8        |        | A10  |  |

| VRL                            | Voltage Reference Low                                  | P — — I VDDA I/— VRL |                          | VRL              | 162          | A9                                                                | A11          |                  |               |        |      |  |

| REFBYBC                        | Reference Bypass Capacitor<br>Input                    | Р                    | —                        | —                | I            | VDDA<br>Analog                                                    | I / —        | REFBYPC          | 164           | B7 B10 |      |  |

|                                |                                                        |                      |                          |                  | eTI          | PU2                                                               |              |                  |               |        |      |  |

| TCRCLKA<br>IRQ[7]<br>GPIO[113] | eTPU A TCR clock<br>External interrupt request<br>GPIO | P<br>A1<br>G         | 01<br>10<br>00           | 113              | <br> <br> /O | VDDEH4<br>Slow                                                    | — / Up       | — / Up           |               | L4     | AB12 |  |

|         |                  | Р                     | PCR          |                | I/O | Voltage <sup>5</sup> / | Sta | itus <sup>7</sup> |                                                                                             | Packag                                                                                                                                                                         | e pin #                                                                                                                                                                                                                                                                                                                    |

|---------|------------------|-----------------------|--------------|----------------|-----|------------------------|-----|-------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    |                  | Pad Type <sup>6</sup> | During Reset | After<br>Reset | 176 | 208                    | 324 |                   |                                                                                             |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                            |

| VDDEH7  | I/O Supply Input | _                     |              | _              | I   | 3.3 V - 5.0 V          | 1/— | VDDEH7            | -                                                                                           | D12                                                                                                                                                                            | B22, C21,<br>D15, D20,<br>E19, F19,<br>H19, J14                                                                                                                                                                                                                                                                            |

| VDDEH7A | I/O Supply Input | -                     |              | —              | I   | 3.3 V - 5.0 V          | 1/— | VDDEH7A           | 125                                                                                         | -                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                          |

| VDDEH7B | I/O Supply Input | _                     |              | _              | I   | 3.3 V - 5.0 V          | I/— | VDDEH7B           | 138                                                                                         | —                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                          |

| VSS     | Ground           |                       |              |                | 1   |                        | 1/  | VSS               | 15,<br>29,<br>43,<br>57,<br>72,<br>90,<br>94,<br>96,<br>108,<br>115,<br>127,<br>133,<br>140 | B2, B15,<br>C3, C14,<br>D4, D13,<br>G7, G8,<br>G9,<br>G10,<br>H7, H8,<br>H9, H10,<br>J7, J8,<br>J9, J10,<br>K7,<br>K8, K9,<br>K10,<br>M16,<br>N4, N13,<br>P3, P14,<br>R2, R15, | A1, A22, B2,<br>B21, C3, C20,<br>D4, D17, D19,<br>F21, H21, J9,<br>J10, J11, J12,<br>J13, K9, K10,<br>K11, K12,<br>K13, K14, L9,<br>L10, L11, L12,<br>L13, L14, L21,<br>M11, M12,<br>M13, M14,<br>N9, N10, N12,<br>N13, N14,<br>N21, P9, P10,<br>P12, P13,<br>P14, T19,<br>T21, T22, W4,<br>Y3, Y20,<br>AA21, AB1,<br>AB22 |

<sup>1</sup> For each pin in the table, each line in the Function column is a separate function of the pin. For all I/O pins the selection of primary pin function or secondary function or GPIO is done in the SIU except where explicitly noted. See the Signal details table for a description of each signal.

<sup>2</sup> The P/A/G column indicates the position a signal occupies in the muxing order for a pin—Primary, Alternate 1, Alternate 2, Alternate 3, or GPIO. Signals are selected by setting the PA field value in the appropriate PCR register in the SIU module. The PA field values are as follows: P - 0b0001, A1 - 0b0010, A2 - 0b0100, A3 - 0b1000, or G - 0b0000. Depending on the register, the PA field size can vary in length. For PA fields having fewer than four bits, remove the appropriate number of leading zeroes from these values.

<sup>3</sup> The Pad Configuration Register (PCR) PA field is used by software to select pin function.

<sup>4</sup> Values in the PCR No. column refer to registers in the System Integration Unit (SIU). The actual register name is "SIU\_PCR" suffixed by the PCR number. For example, PCR[190] refers to the SIU register named SIU\_PCR190.

| Signal                                 | Module or Function | Description                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSPI_C_SOUT_LVDS-<br>DSPI_C_SOUT_LVDS+ | DSPI               | LVDS pair used for DSPI_C TSB mode transmission                                                                                                                                                                                                                                                                                                                   |

| PCS_B[0]<br>PCS_C[0]<br>PCS_D[0]       | DSPI_B - DSPI_D    | Peripheral chip select when device is in master mode—slave select when used in slave mode                                                                                                                                                                                                                                                                         |

| PCS_B[1:5]<br>PCS_C[1:5]<br>PCS_D[1:5] | DSPI_B - DSPI_D    | Peripheral chip select when device is in master mode—not used in slave mode                                                                                                                                                                                                                                                                                       |

| SCK_B<br>SCK_C<br>SCK_D                | DSPI_B - DSPI_D    | DSPI clock—output when device is in master mode; input when in slave mode                                                                                                                                                                                                                                                                                         |

| SIN_B<br>SIN_C<br>SIN_D                | DSPI_B - DSPI_D    | DSPI data in                                                                                                                                                                                                                                                                                                                                                      |

| SOUT_B<br>SOUT_C<br>SOUT_D             | DSPI_B - DSPI_D    | DSPI data out                                                                                                                                                                                                                                                                                                                                                     |

| ADDR[10:31]                            | EBI                | The ADDR[10:31] signals specify the physical address of the bus transaction.<br>The 26 address lines correspond to bits 3-31 of the EBI's 32-bit internal address bus.<br>ADDR[15:31] can be used as Address and Data signals when configured appropriately for a multiplexed external bus. This allows 32-bit data operations, or 16-bit data operations without |

| ALE                                    | EBI                | The Address Latch Enable (ALE) signal is used to demultiplex<br>the address from the data bus. It is asserted while the least<br>significant 16 bits of the address are present in the multiplexed<br>address/data bus.                                                                                                                                           |

| BDIP                                   | EBI                | BDIP is asserted to indicate that the master is requesting another data beat following the current one.                                                                                                                                                                                                                                                           |

| <u>CS[0:3]</u>                         | ЕВІ                | CSx is asserted by the master to indicate that this transaction is targeted for a particular memory bank on the Primary external bus.                                                                                                                                                                                                                             |

| DATA[0:31]                             | EBI                | The DATA[0:31] signals contain the data to be transferred for the current transaction.                                                                                                                                                                                                                                                                            |

| OE                                     | ЕВІ                | $\overline{\text{OE}}$ is used to indicate when an external memory is permitted to drive back read data. External memories must have their data output buffers off when $\overline{\text{OE}}$ is negated. $\overline{\text{OE}}$ is only asserted for chip-select accesses.                                                                                      |

| RD_WR                                  | EBI                | $RD_{\overline{WR}}$ indicates whether the current transaction is a read access or a write access.                                                                                                                                                                                                                                                                |

| Signal                      | Module or Function        | Description                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOTCFG[0:1]                | SIU - Configuration       | Two BOOTCFG signals are implemented in MPC5644A MCUs.                                                                                                                                                                                                                                                                                 |

|                             |                           | The BAM program uses the BOOTCFG0 bit to determine where to read the reset configuration word, and whether to initiate a FlexCAN or eSCI boot.                                                                                                                                                                                        |

|                             |                           | The BOOTCFG1 pin is sampled during the assertion of the RSTOUT signal, and the value is used to update the RSR and the BAM boot mode                                                                                                                                                                                                  |

|                             |                           | See the <i>MPC5644A Microcontroller Reference Manual</i> for more information.                                                                                                                                                                                                                                                        |

|                             |                           | The following values are for BOOTCFG[0:1]:<br>00:Boot from internal flash memory<br>01:FlexCAN/eSCI boot<br>10:Boot from external memory using EBI<br>11:Reserved                                                                                                                                                                     |

|                             |                           | Note: For the 176-pin QFP and 208-ball BGA packages<br>BOOTCFG[0] is always 0 since the EBI interface is not available.                                                                                                                                                                                                               |

| WKPCFG                      | SIU - Configuration       | The WKPCFG pin is applied at the assertion of the internal reset signal (assertion of RSTOUT), and is sampled 4 clock cycles before the negation of the RSTOUT pin.                                                                                                                                                                   |

|                             |                           | The value is used to configure whether the eTPU and eMIOS pins are connected to internal weak pull up or weak pull down devices after reset. The value latched on the WKPCFG pin at reset is stored in the Reset Status Register (RSR), and is updated for all reset sources except the Debug Port Reset and Software External Reset. |

|                             |                           | 0: Weak pulldown applied to eTPU and eMIOS pins at reset<br>1: Weak pullup applied to eTPU and eMIOS pins at reset.                                                                                                                                                                                                                   |

| ETRIG[2:3]                  | SIU - eQADC Triggers      | External signal eTRIGx triggers eQADC CFIFOx                                                                                                                                                                                                                                                                                          |

| GPIO[206] ETRIG0<br>(Input) | SIU - eQADC Triggers      | External signal eTRIGx triggers eQADC CFIFOx                                                                                                                                                                                                                                                                                          |

| GPIO[207] ETRIG1<br>(Input) | SIU - eQADC Triggers      | External signal eTRIGx triggers eQADC CFIFOx                                                                                                                                                                                                                                                                                          |

| IRQ[0:5]<br>IRQ[7:15]       | SIU - External Interrupts | The $\overline{IRQ}$ [0:15] pins connect to the SIU IRQ inputs. IMUX Select Register 1 is used to select the $\overline{IRQ}$ [0:15] pins as inputs to the IRQs.                                                                                                                                                                      |

|                             |                           | See the <i>MPC5644A Microcontroller Reference Manual</i> for more information.                                                                                                                                                                                                                                                        |

| NMI                         | SIU - External Interrupts | Non-Maskable Interrupt                                                                                                                                                                                                                                                                                                                |

#### Table 5. Signal details (continued)

- $^{6}$  All functional non-supply I/O pins are clamped to V\_{SS} and V\_{DDE}, or V\_{DDEH}.

- <sup>7</sup> AC signal overshoot and undershoot of up to 2.0 V of the input voltages is permitted for an accumulative duration of 60 hours over the complete lifetime of the device (injection current not limited for this duration).

- <sup>8</sup> Internal structures hold the voltage greater than –1.0 V if the injection current limit of 2 mA is met.

- <sup>9</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDEH</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDEH</sub> is within the operating voltage specifications.

- <sup>10</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDE</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDE</sub> is within the operating voltage specifications.

- <sup>11</sup> Total injection current for all pins (including both digital and analog) must not exceed 25 mA.

- <sup>12</sup> Total injection current for all analog input pins must not exceed 15 mA.

- <sup>13</sup> Solder profile per IPC/JEDEC J-STD-020D.

- <sup>14</sup> Moisture sensitivity per JEDEC test method A112.

# 3.3 Thermal characteristics

#### С Conditions Symbol Parameter Value Unit Junction-to-Ambient, Natural Convection<sup>2</sup> Single layer board - 1s $R_{\theta JA}$ CC D °C/W 38 CC D Junction-to-Ambient, Natural Convection<sup>2</sup> Four layer board - 2s2p 31 °C/W $R_{\theta JA}$ Junction-to-Moving-Air, Ambient<sup>2</sup> CC 200 ft./min., single layer °C/W $R_{\theta,IMA}$ D 30 board - 1s Junction-to-Moving-Air, Ambient<sup>2</sup> $R_{\theta JMA}$ CC D at 200 ft./min., four layer °C/W 25 board - 2s2p Junction-to-Board<sup>3</sup> CC D 20 °C/W $R_{\theta,IB}$ CC D Junction-to-Case<sup>4</sup> 5 °C/W $R_{\theta JCtop}$ СС Junction-to-Package Top, Natural 2 °C/W D $\Psi_{JT}$ Convection<sup>5</sup>

#### Table 9. Thermal characteristics for 176-pin QFP<sup>1</sup>

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

- <sup>3</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- <sup>4</sup> Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>5</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

<sup>&</sup>lt;sup>2</sup> Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>5</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 3.3.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>I</sub>, can be obtained from the equation:

$$T_{J} = T_{A} + (R_{\theta JA} * P_{D}) \qquad \qquad Eqn. 1$$

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal resistance values used are based on the JEDEC JESD51 series of standards to provide consistent values for estimations and comparisons. The difference between the values determined for the single-layer (1s) board compared to a four-layer board that has two signal layers, a power and a ground plane (2s2p), demonstrate that the effective thermal resistance is not a constant. The thermal resistance depends on the:

- Construction of the application board (number of planes)

- Effective size of the board which cools the component

- Quality of the thermal and electrical connections to the planes

- Power dissipated by adjacent components

Connect all the ground and power balls to the respective planes with one via per ball. Using fewer vias to connect the package to the planes reduces the thermal performance. Thinner planes also reduce the thermal performance. When the clearance between the vias leave the planes virtually disconnected, the thermal performance is also greatly reduced.

As a general rule, the value obtained on a single-layer board is within the normal range for the tightly packed printed circuit board. The value obtained on a board with the internal planes is usually within the normal range if the application board has:

- One oz. (35 micron nominal thickness) internal planes

- Components are well separated

- Overall power dissipation on the board is less than 0.02 W/cm<sup>2</sup>

The thermal performance of any component depends on the power dissipation of the surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$$T_{J} = T_{B} + (R_{\theta JB} * P_{D}) \qquad \qquad Eqn. 2$$

where:

$T_{B}$  = board temperature for the package perimeter (°C)

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W) per JESD51-8S

$P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air does not factor into the calculation, an acceptable value for the junction temperature is predictable. Ensure the application board is similar to the thermal test condition, with the component soldered to a board with internal planes.

The thermal resistance is expressed as the sum of a junction-to-case thermal resistance plus a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \qquad \qquad Eqn. 3$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\Theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and is not affected by other factors. The thermal environment can be controlled to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For example, change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This description is most useful for packages with heat sinks where 90% of the heat flow is through the case to heat sink to ambient. For most packages, a better model is required.

A more accurate two-resistor thermal model can be constructed from the junction-to-board thermal resistance and the junction-to-case thermal resistance. The junction-to-case thermal resistance describes when using a heat sink or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. This model can be used to generate simple estimations and for computational fluid dynamics (CFD) thermal models.

To determine the junction temperature of the device in the application on a prototype board, use the thermal characterization parameter ( $\Psi_{JT}$ ) to determine the junction temperature by measuring the temperature at the top center of the package case using the following equation:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D}) \qquad \qquad Eqn. 4$$

where:

$T_T$  = thermocouple temperature on top of the package (<sup>o</sup>C)

$\Psi_{JT}$  = thermal characterization parameter (<sup>o</sup>C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured in compliance with the JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. Position the thermocouple so that the thermocouple junction rests on the package. Place a small amount of epoxy on the thermocouple junction and approximately 1 mm of wire extending from the junction. Place the thermocouple wire flat against the package case to avoid measurement errors caused by the cooling effects of the thermocouple wire.

References:

Semiconductor Equipment and Materials International

3081 Zanker Road San Jose, CA 95134 USA (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at http://www.jedec.org.

- C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

- G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications", Electronic Packaging and Production, pp. 53-58, March 1998.

| ID | Name       | e  |   | Parameter                                                                                            | Min               | Тур       | Max                | Unit | Notes                                                                    |

|----|------------|----|---|------------------------------------------------------------------------------------------------------|-------------------|-----------|--------------------|------|--------------------------------------------------------------------------|

| 5  | Vdd33      | CC | С | Nominal 3.3 V supply<br>internal regulator DC output<br>voltage                                      | _                 | 3.39      | _                  | V    |                                                                          |

| 5a | _          | СС | Ρ | Nominal 3.3 V supply<br>internal regulator DC output<br>voltage variation at<br>power-on reset       | Vdd33 -<br>8.5%   | Vdd33     | Vdd3 + 7%          | V    | See note <sup>5</sup>                                                    |

| 5b | _          | CC | Ρ | Nominal 3.3 V supply<br>internal regulator DC output<br>voltage variation power-on<br>reset          | Vdd33 -<br>7.5%   | Vdd33     | Vdd33 +<br>7%      | V    | With internal<br>load up<br>to ldd3p3                                    |

| 5c | _          | СС | D | Voltage regulator 3.3 V<br>output impedance at<br>maximum DC load                                    | _                 | _         | 2                  | Ω    |                                                                          |

| 5d | ldd3p3     | CC | Ρ | Voltage regulator 3.3 V<br>maximum DC output<br>current (internal regulator<br>enabled) <sup>6</sup> | 80 <sup>7</sup>   | _         | _                  | mA   |                                                                          |

| 5e | Vdd33 ILim | СС | С | Voltage regulator 3.3 V DC current limit                                                             | _                 | 130       | —                  | mA   |                                                                          |

| 6  | Lvi3p3     | CC | С | Nominal LVI for rising 3.3 V supply                                                                  | _                 | 3.090     | _                  | V    | The Lvi3p3<br>specs are also<br>valid for the<br>Vddeh LVI               |

| 6a | _          | СС | С | Variation of LVI for rising<br>3.3 V supply at power-on<br>reset                                     | Lvi3p3 -<br>6%    | Lvi3p3    | Lvi3p3 +<br>6%     | V    | See note <sup>8</sup>                                                    |

| 6b | _          | СС | С | Variation of LVI for rising<br>3.3 V supply after power-on<br>reset                                  | Lvi3p3 -<br>3%    | Lvi3p3    | Lvi3p3 +<br>3%     | V    | See note 8                                                               |

| 6c |            | СС | С | Trimming step LVI 3.3 V                                                                              | —                 | 20        | —                  | mV   |                                                                          |

| 6d | Lvi3p3_h   | СС | С | LVI 3.3 V hysteresis                                                                                 | —                 | 60        | _                  | mV   |                                                                          |

| 7  | Por3.3V_r  | СС | С | Nominal POR for rising<br>3.3 V supply                                                               | _                 | 2.07      | _                  | V    | The 3.3V POR<br>specs are also<br>valid for the<br>V <sub>DDEH</sub> POR |

| 7a | —          | СС | С | Variation of POR for rising 3.3 V supply                                                             | Por3.3V_r-<br>35% | Por3.3V_r | Por3.3V_r<br>+ 35% | V    |                                                                          |

| 7b | Por3.3V_f  | СС | С | Nominal POR for falling<br>3.3 V supply                                                              |                   | 1.95      | _                  | V    |                                                                          |

| 7c |            | СС | С | Variation of POR for falling 3.3 V supply                                                            | Por3.3V_f-<br>35% | Por3.3V_f | Por3.3V_f+<br>35%  | V    |                                                                          |

| 8  | Lvi5p0     | СС | С | Nominal LVI for rising 5 V<br>V <sub>DDREG</sub> supply                                              | —                 | 4.290     | —                  | V    |                                                                          |

| Table 15. PMC Electrical Cha | racteristics (continued) |

|------------------------------|--------------------------|

|------------------------------|--------------------------|

| Symbol                                  |    |   |                                                               | •                      |                        |     |                        |      |  |

|-----------------------------------------|----|---|---------------------------------------------------------------|------------------------|------------------------|-----|------------------------|------|--|

|                                         |    | С | Parameter                                                     | Conditions             | min                    | typ | max                    | Unit |  |

| V <sub>DDREG</sub>                      | SR | — | Voltage regulator supply voltage                              | _                      | 4.75                   | _   | 5.25                   | V    |  |

| V <sub>DDPLL</sub>                      | SR | — | Clock synthesizer operating voltage                           | _                      | 1.14                   |     | 1.32                   | V    |  |

| V <sub>SSPLL</sub> –<br>V <sub>SS</sub> | SR | _ | V <sub>SSPLL</sub> to V <sub>SS</sub><br>differential voltage | _                      | -100                   | _   | 100                    | mV   |  |

| $V_{IL_S}$                              | CC | С | Slow/medium I/O pad<br>input low voltage                      | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _   | 0.35*V <sub>DDEH</sub> | V    |  |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _   | 0.40*V <sub>DDEH</sub> |      |  |

| $V_{IL_F}$                              | CC | С | Fast pad I/O input low voltage                                | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _   | 0.35*V <sub>DDE</sub>  | V    |  |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _   | 0.40*V <sub>DDE</sub>  |      |  |

| $V_{IL\_LS}$                            | СС | С | Multi-voltage I/O pad<br>input low voltage in                 | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _   | 0.8                    | V    |  |

|                                         |    | Ρ | Low-swing-mode <sup>5,6,7,</sup><br>8                         | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _   | 1.1                    |      |  |

| $V_{IL_{HS}}$                           | СС | С | Multi-voltage pad I/O<br>input low voltage in                 | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _   | 0.35 V <sub>DDEH</sub> | V    |  |

|                                         |    | Ρ | high-swing-mode                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | —   | 0.4 V <sub>DDEH</sub>  |      |  |

| V <sub>IH_S</sub>                       | СС | С | Slow/medium pad I/O<br>input high voltage <sup>9</sup>        | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> | _   | V <sub>DDEH</sub> +0.3 | V    |  |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | _   | V <sub>DDEH</sub> +0.3 |      |  |

| $V_{\text{IH}_{\text{F}}}$              | CC | С | Fast I/O input high voltage                                   | Hysteresis<br>enabled  | 0.65 V <sub>DDE</sub>  | _   | V <sub>DDE</sub> +0.3  | V    |  |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | 0.58 V <sub>DDE</sub>  | _   | V <sub>DDE</sub> +0.3  |      |  |

| V <sub>IH_LS</sub>                      | СС | С | Multi-voltage pad I/O input high voltage in                   | Hysteresis<br>enabled  | 2.5                    | _   | V <sub>DDEH</sub> +0.3 | V    |  |

|                                         |    | Ρ | low-swing-mode <sup>5,6,7,8</sup>                             | Hysteresis<br>disabled | 2.2                    | _   | V <sub>DDEH</sub> +0.3 | 1    |  |

| V <sub>IH_HS</sub>                      | СС | С | Multi-voltage I/O input<br>high voltage in                    | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> | _   | V <sub>DDEH</sub> +0.3 | V    |  |

|                                         |    | Ρ | high-swing-mode                                               | Hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | _   | V <sub>DDEH</sub> +0.3 |      |  |

| Table 21. DC electrical specifications (co | ontinued) |

|--------------------------------------------|-----------|

|--------------------------------------------|-----------|

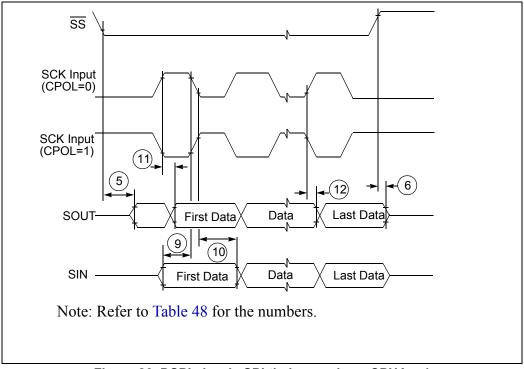

Figure 26. DSPI classic SPI timing — slave, CPHA = 1

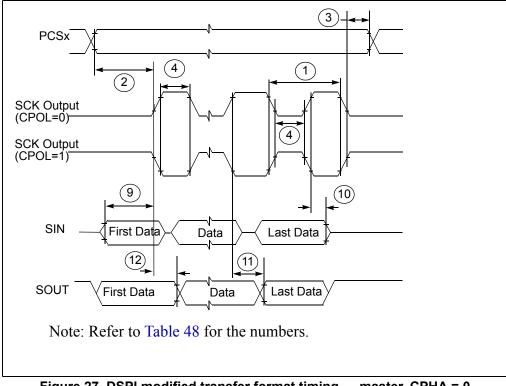

Figure 27. DSPI modified transfer format timing — master, CPHA = 0

MPC5644A Microcontroller Data Sheet, Rev. 7

|                                                                                                                                                                                                                                                                                                                                                                 | NOTES:                                       |        |           |        |       |             |                           |         |      |               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------|-----------|--------|-------|-------------|---------------------------|---------|------|---------------|